JP5696331B2 - チップ抵抗器およびその製造方法 - Google Patents

チップ抵抗器およびその製造方法 Download PDFInfo

- Publication number

- JP5696331B2 JP5696331B2 JP2011052637A JP2011052637A JP5696331B2 JP 5696331 B2 JP5696331 B2 JP 5696331B2 JP 2011052637 A JP2011052637 A JP 2011052637A JP 2011052637 A JP2011052637 A JP 2011052637A JP 5696331 B2 JP5696331 B2 JP 5696331B2

- Authority

- JP

- Japan

- Prior art keywords

- resistor

- protective film

- surface electrode

- electrode

- cut groove

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Details Of Resistors (AREA)

- Apparatuses And Processes For Manufacturing Resistors (AREA)

- Non-Adjustable Resistors (AREA)

Description

Claims (6)

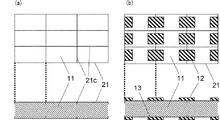

- 絶縁性基板と、

該絶縁性基板の表面両端部に配置される一対の第1表電極と、

該第1表電極に接続する抵抗体と、

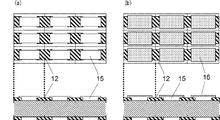

該抵抗体を被覆する第1保護膜と、

該第1保護膜上に前記第1表電極と一部が接続するように配置される一対の第2表電極と、

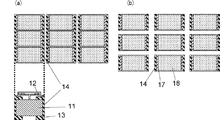

前記第1保護膜とともに前記抵抗体上に設けられる切り込み溝と、

前記第2表電極の一部と、前記第1保護膜および前記切り込み溝を被覆する第2保護膜とを備え、

前記第1保護膜と前記第2保護膜の間に形成される一対の前記第2表電極は、前記切り込み溝を被覆せず、

前記抵抗体および前記第1保護膜上において該切り込み溝により狭くなる前記狭小部を被覆するように、少なくとも一方の第2表電極がチップ端から延びて前記切り込み溝を避けて、L字状をなすことを特徴とするチップ抵抗器。 - 前記切り込み溝は、前記抵抗体および前記第1保護膜上に形成される、前記第2表電極に覆われない領域の範囲内に収まることを特徴とする請求項1記載のチップ抵抗器。

- 前記切り込み溝は、前記抵抗体の長手方向に対して略垂直に前記抵抗体の内側に向かって形成される第1切り込み部と、その終端から前記抵抗体の長手方向に、前記第2表電極のうち前記狭小部を被覆するように延長される電極に向けて形成される第2切り込み部とからなることを特徴とする請求項1または2に記載のチップ抵抗器。

- 絶縁性基板に一対の第1表電極および該第1表電極に接続される抵抗体を形成する工程と、

前記抵抗体を被覆する第1保護膜を形成する工程と、

該第1保護膜とともに前記抵抗体に切り込み溝を形成する工程と、

前記第1表電極と一端を接続し、前記切り込み溝を設けることにより前記抵抗体上に形成される狭小部を覆う第2表電極を形成する工程と、

該第2表電極と、前記第1保護膜および前記切り込み溝を被覆する第2保護膜を形成する工程と、を有し、

前記第2表電極は、一対の電極からなり、少なくとも一方の電極がチップ端から延びて前記切り込み溝を避けて、前記狭小部を被覆するようにL字状をなすことを特徴とするチップ抵抗器の製造方法。 - 前記切り込み溝は、前記抵抗体および前記第1保護膜上に形成される、前記第2表電極に覆われない領域の範囲内に収まるように形成することを特徴とする請求項4に記載のチップ抵抗器の製造方法。

- 前記切り込み溝は、前記抵抗体の長手方向に対して略垂直に前記抵抗体の内側に向かって形成される第1切り込み部と、該第1切り込み部の終端から前記抵抗体の長手方向に、前記第2表電極のうち前記狭小部を被覆するように延長される電極に向けて形成される第2切り込み部の順に形成されることを特徴とする請求項4または5に記載のチップ抵抗器の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011052637A JP5696331B2 (ja) | 2011-03-10 | 2011-03-10 | チップ抵抗器およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011052637A JP5696331B2 (ja) | 2011-03-10 | 2011-03-10 | チップ抵抗器およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012190965A JP2012190965A (ja) | 2012-10-04 |

| JP5696331B2 true JP5696331B2 (ja) | 2015-04-08 |

Family

ID=47083821

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011052637A Expired - Fee Related JP5696331B2 (ja) | 2011-03-10 | 2011-03-10 | チップ抵抗器およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5696331B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015079872A (ja) * | 2013-10-17 | 2015-04-23 | コーア株式会社 | チップ抵抗器 |

| JP6371080B2 (ja) * | 2014-03-04 | 2018-08-08 | Koa株式会社 | チップ抵抗器の製造方法 |

| US10083781B2 (en) * | 2015-10-30 | 2018-09-25 | Vishay Dale Electronics, Llc | Surface mount resistors and methods of manufacturing same |

| CN112837872B (zh) * | 2021-01-05 | 2025-08-22 | 广东风华高新科技股份有限公司 | 一种片式薄膜电阻器及其制备方法 |

| CN115995319B (zh) * | 2022-12-09 | 2025-08-26 | 珠海格力电器股份有限公司 | 电阻结构 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0366103A (ja) * | 1989-08-04 | 1991-03-20 | Fujitsu Ltd | 膜抵抗体の形成方法 |

| JP2002025802A (ja) * | 2000-07-10 | 2002-01-25 | Rohm Co Ltd | チップ抵抗器 |

| JP2002110401A (ja) * | 2000-09-29 | 2002-04-12 | Matsushita Electric Ind Co Ltd | 抵抗器およびその製造方法 |

-

2011

- 2011-03-10 JP JP2011052637A patent/JP5696331B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012190965A (ja) | 2012-10-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7093382B2 (ja) | チップ抵抗器 | |

| JP5696331B2 (ja) | チップ抵抗器およびその製造方法 | |

| JP6822947B2 (ja) | 角形チップ抵抗器及びその製造法 | |

| JPH1126204A (ja) | 抵抗器およびその製造方法 | |

| CN107615410A (zh) | 芯片电阻器 | |

| CN101681702A (zh) | 片式电阻器 | |

| US11164688B2 (en) | Chip resistor | |

| US10109398B2 (en) | Chip resistor and method for producing same | |

| WO2019082523A1 (ja) | チップ抵抗器およびチップ抵抗器の製造方法 | |

| JP2015079872A (ja) | チップ抵抗器 | |

| JP6371080B2 (ja) | チップ抵抗器の製造方法 | |

| US8854175B2 (en) | Chip resistor device and method for fabricating the same | |

| CN109830351B (zh) | 一种贴片电阻器及其加工方法 | |

| JP2015230922A (ja) | チップ抵抗器の製造方法 | |

| JP2008244211A (ja) | 薄膜チップ抵抗器の製造方法 | |

| JP6453599B2 (ja) | チップ抵抗器の製造方法 | |

| JP4693001B2 (ja) | チップ型回路保護素子 | |

| JP6453598B2 (ja) | チップ抵抗器 | |

| WO2018061961A1 (ja) | チップ抵抗器 | |

| JP5157178B2 (ja) | 角形チップ抵抗器 | |

| JP4512004B2 (ja) | チップ抵抗器 | |

| JP2016139661A (ja) | チップ抵抗器 | |

| JP4729398B2 (ja) | チップ抵抗器 | |

| JP2007142165A (ja) | チップ抵抗器とその製造方法 | |

| JP7636965B2 (ja) | チップ抵抗器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140117 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140922 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140930 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141119 |

|

| TRDD | Decision of grant or rejection written | ||

| RD13 | Notification of appointment of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7433 Effective date: 20150108 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150113 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150120 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5696331 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |