JP5624792B2 - 電力変換装置 - Google Patents

電力変換装置 Download PDFInfo

- Publication number

- JP5624792B2 JP5624792B2 JP2010090016A JP2010090016A JP5624792B2 JP 5624792 B2 JP5624792 B2 JP 5624792B2 JP 2010090016 A JP2010090016 A JP 2010090016A JP 2010090016 A JP2010090016 A JP 2010090016A JP 5624792 B2 JP5624792 B2 JP 5624792B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- command value

- phase

- unit cell

- voltage command

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/42—Conversion of dc power input into ac power output without possibility of reversal

- H02M7/44—Conversion of dc power input into ac power output without possibility of reversal by static converters

- H02M7/48—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/483—Converters with outputs that each can have more than two voltages levels

- H02M7/4835—Converters with outputs that each can have more than two voltages levels comprising two or more cells, each including a switchable capacitor, the capacitors having a nominal charge voltage which corresponds to a given fraction of the input voltage, and the capacitors being selectively connected in series to determine the instantaneous output voltage

Description

各制御周期内でPWMパルス803と元の電圧指令値正弦波802が同じ電圧になるので、制御周波数が基本波周波数の整数倍であれば、PWMパルスの正弦波基本波成分804と正弦波電圧指令値802は大略等しくなり、各単位セル120の直流コンデンサ電圧のアンバランスの発生を抑制できる。

101 電力変換器システム

102 連系変圧器

102C 可変電圧変圧器

105 電力変換器

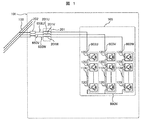

113Up,113Vp,113Wp,113Un,113Vn,113Wn カスケードレッグ

120 単位セル

121C 双方向チョッパ

121F フルブリッジ回路

201Up,201Vp,201Wp,201Un,201Vn,201Wn アームリアクトル

202 遮断機

250 可変直流電圧源

251 コンタクタ

252 初充電回路

400P,400N,400L,400R 単位セル出力端子

402P,402N IGBT並列体

406 直流コンデンサ

411,411L,411R IGBTレッグ

451 IGBT

452 ダイオード

600U カスケードレッグ113Upの高圧側端子

600V カスケードレッグ113Vpの高圧側端子

600W カスケードレッグ113Wpの高圧側端子

602U カスケードレッグ113Upの低圧側端子

602V カスケードレッグ113Vpの低圧側端子

602W カスケードレッグ113Wpの低圧側端子

603U カスケードレッグ113Unの高圧側端子

603V カスケードレッグ113Vnの高圧側端子

603W カスケードレッグ113Wnの高圧側端子

604U カスケードレッグ113Unの低圧側端子

604V カスケードレッグ113Vnの低圧側端子

604W カスケードレッグ113Wnの低圧側端子

650U,650V,650W 電力変換器105のU相入出力端子

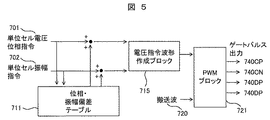

701 単位セル電圧位相指令値

702 単位セル電圧振幅指令値

719 制御周期内電圧指令値平均値演算ブロック

720 搬送波

721 PWMブロック

740CP,740CN,740DP,740DN ゲートパルス出力

Claims (1)

- 単位セルをカスケードに接続した構成を有する電力変換システムにおいて、前記単位セルはスイッチング素子とコンデンサを有し、前記単位セルは、電圧指令値と搬送波を比較してPWMパルスを生成して前記スイッチング素子をオン/オフすることで前記コンデンサを充放電するものであって、電圧指令値の変調率及び電圧指令値と搬送波の位相差に応じた変調率補正値と位相補正値を記憶したテーブルと、電圧指令値の変調率及び搬送波との位相差に応じて前記テーブルを参照して前記電圧指令値の振幅と位相をフィードフォアードで修正する修正手段を有し、前記テーブルには、修正後の電圧指令値に基づいて生成されるPWMパルスの基本波成分の位相と振幅が、前記修正の対象となった電圧指令値の位相と振幅に近づくように前記変調率補正値と位相補正値が格納されていることを特徴としたカスケードマルチレベル電力変換システム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010090016A JP5624792B2 (ja) | 2010-04-09 | 2010-04-09 | 電力変換装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010090016A JP5624792B2 (ja) | 2010-04-09 | 2010-04-09 | 電力変換装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011223734A JP2011223734A (ja) | 2011-11-04 |

| JP2011223734A5 JP2011223734A5 (ja) | 2013-05-16 |

| JP5624792B2 true JP5624792B2 (ja) | 2014-11-12 |

Family

ID=45039954

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010090016A Active JP5624792B2 (ja) | 2010-04-09 | 2010-04-09 | 電力変換装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5624792B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5752580B2 (ja) * | 2011-12-12 | 2015-07-22 | 株式会社東芝 | 電力変換装置 |

| WO2013104418A1 (en) * | 2012-01-11 | 2013-07-18 | Bombardier Transportation Gmbh | Generation of switching sequence for a cascaded multilevel converter |

| CN102664418B (zh) * | 2012-04-19 | 2014-07-02 | 威凡智能电气高科技有限公司 | 基于plc在高压statcom中在线监控方法 |

| KR101791290B1 (ko) | 2013-07-02 | 2017-11-20 | 엘에스산전 주식회사 | 멀티레벨 고압 인버터 |

| CN104065062B (zh) * | 2014-06-23 | 2016-08-24 | 许继电气股份有限公司 | Statcom正常运行调制控制方法 |

| JP2016067124A (ja) * | 2014-09-25 | 2016-04-28 | 株式会社日立製作所 | 電力補償装置及び電力補償方法 |

| JP6614704B2 (ja) * | 2016-12-06 | 2019-12-04 | 東芝三菱電機産業システム株式会社 | 電力変換装置 |

| JP6704864B2 (ja) * | 2017-01-16 | 2020-06-03 | 株式会社日立製作所 | 電力変換装置 |

| JP6892812B2 (ja) * | 2017-10-12 | 2021-06-23 | 株式会社日立製作所 | 電力変換装置 |

| US11437816B2 (en) | 2018-11-27 | 2022-09-06 | Hitachi Energy Switzerland Ag | STATCOM arrangement without phase reactors |

| WO2020111513A1 (ko) * | 2018-11-29 | 2020-06-04 | 중앙제어 주식회사 | 상회전 방향에 무관한 3상 전력변환장치 |

| JP7375553B2 (ja) | 2020-01-06 | 2023-11-08 | 富士電機株式会社 | 電力変換装置 |

| JP7305594B2 (ja) | 2020-04-06 | 2023-07-10 | 東芝キヤリア株式会社 | 電力変換装置 |

| KR102549613B1 (ko) * | 2021-01-28 | 2023-06-29 | 부경대학교 산학협력단 | 모듈형 컨버터의 직류단 전압 균형제어를 위한 장치 및 방법 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0928083A (ja) * | 1995-07-11 | 1997-01-28 | Hitachi Ltd | パルス幅変調制御装置 |

| JP2000287453A (ja) * | 1999-03-31 | 2000-10-13 | Mitsubishi Electric Corp | 多重電力変換装置 |

| CN101427455B (zh) * | 2006-06-16 | 2012-05-30 | 三菱电机株式会社 | 电力变换器的控制装置 |

-

2010

- 2010-04-09 JP JP2010090016A patent/JP5624792B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011223734A (ja) | 2011-11-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5624792B2 (ja) | 電力変換装置 | |

| US10263535B2 (en) | Method and device for voltage balancing of DC bus capacitors of neutral-point clamped four-level inverter | |

| JP4969614B2 (ja) | 電力変換装置 | |

| Moosavi et al. | A voltage balancing strategy with extended operating region for cascaded H-bridge converters | |

| US10734884B2 (en) | Modular multilevel converter harmonic injection systems and methods | |

| US10236793B2 (en) | Grid connection power conversion device and output current control method thereof | |

| JP6289675B2 (ja) | 電力変換装置 | |

| JP6178433B2 (ja) | 電力変換装置 | |

| JP6538544B2 (ja) | 自励式無効電力補償装置 | |

| JP2009201248A (ja) | クランプ式電力変換装置 | |

| JP6538542B2 (ja) | 自励式無効電力補償装置 | |

| CN111030497B (zh) | 三相四桥臂逆变器并联系统及其控制方法、电能治理设备 | |

| JP2016063687A (ja) | 電力変換装置 | |

| CN111133670A (zh) | 控制dc系统中的电压源变流器 | |

| Zhang et al. | DC-link capacitor voltage balancing for a five-level diode-clamped active power filter using redundant vectors | |

| Mei et al. | Quasi-fixed-frequency hysteresis current tracking control strategy for modular multilevel converters | |

| Bashi et al. | Generation of triggering signals for multilevel converter | |

| EP4220931A1 (en) | Power conversion device | |

| Kitidet et al. | A CB-SVPWM control strategy for neutral-poin voltage balancing in three-level NPC inverters | |

| Shen et al. | Investigation of capacitor voltage regulation in modular multilevel converters with staircase modulation | |

| JP2017153277A (ja) | 自励式無効電力補償装置 | |

| JP5277096B2 (ja) | 電力変換装置 | |

| KR101728019B1 (ko) | 독립형 마이크로그리드용 3상 인버터 전압 제어 장치 및 그 방법 | |

| JP5652593B2 (ja) | 電力変換装置 | |

| JP2015015778A (ja) | 系統連系用電力変換システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130329 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131128 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131224 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140902 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140929 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5624792 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |