JP5478787B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP5478787B2 JP5478787B2 JP2008059749A JP2008059749A JP5478787B2 JP 5478787 B2 JP5478787 B2 JP 5478787B2 JP 2008059749 A JP2008059749 A JP 2008059749A JP 2008059749 A JP2008059749 A JP 2008059749A JP 5478787 B2 JP5478787 B2 JP 5478787B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- film

- electrode

- insulating film

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 129

- 238000000034 method Methods 0.000 title claims description 33

- 238000004519 manufacturing process Methods 0.000 title claims description 23

- 238000006243 chemical reaction Methods 0.000 claims description 49

- 239000000758 substrate Substances 0.000 claims description 49

- 229910052751 metal Inorganic materials 0.000 claims description 40

- 239000002184 metal Substances 0.000 claims description 40

- 239000010936 titanium Substances 0.000 claims description 13

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 12

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 claims description 9

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 9

- 229910052721 tungsten Inorganic materials 0.000 claims description 9

- 239000010937 tungsten Substances 0.000 claims description 9

- 229910044991 metal oxide Inorganic materials 0.000 claims description 8

- 150000004706 metal oxides Chemical class 0.000 claims description 8

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 7

- 229910052719 titanium Inorganic materials 0.000 claims description 7

- 239000011651 chromium Substances 0.000 claims description 6

- 239000010955 niobium Substances 0.000 claims description 6

- 230000001590 oxidative effect Effects 0.000 claims description 6

- 239000010948 rhodium Substances 0.000 claims description 6

- 229910052759 nickel Inorganic materials 0.000 claims description 4

- 229910052762 osmium Inorganic materials 0.000 claims description 4

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 claims description 4

- 229910052715 tantalum Inorganic materials 0.000 claims description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 claims description 3

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 claims description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 claims description 3

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 claims description 3

- 229910052804 chromium Inorganic materials 0.000 claims description 3

- 229910017052 cobalt Inorganic materials 0.000 claims description 3

- 239000010941 cobalt Substances 0.000 claims description 3

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 3

- 229910052735 hafnium Inorganic materials 0.000 claims description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 3

- 229910052741 iridium Inorganic materials 0.000 claims description 3

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 claims description 3

- 229910052750 molybdenum Inorganic materials 0.000 claims description 3

- 239000011733 molybdenum Substances 0.000 claims description 3

- 229910052758 niobium Inorganic materials 0.000 claims description 3

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 claims description 3

- 229910052763 palladium Inorganic materials 0.000 claims description 3

- 229910052702 rhenium Inorganic materials 0.000 claims description 3

- WUAPFZMCVAUBPE-UHFFFAOYSA-N rhenium atom Chemical compound [Re] WUAPFZMCVAUBPE-UHFFFAOYSA-N 0.000 claims description 3

- 229910052703 rhodium Inorganic materials 0.000 claims description 3

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 claims description 3

- 229910052707 ruthenium Inorganic materials 0.000 claims description 3

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 claims description 3

- 229910052713 technetium Inorganic materials 0.000 claims description 3

- GKLVYJBZJHMRIY-UHFFFAOYSA-N technetium atom Chemical compound [Tc] GKLVYJBZJHMRIY-UHFFFAOYSA-N 0.000 claims description 3

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 claims description 3

- 239000010408 film Substances 0.000 description 195

- 239000010410 layer Substances 0.000 description 105

- 239000011229 interlayer Substances 0.000 description 25

- 239000000463 material Substances 0.000 description 17

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 16

- 239000000853 adhesive Substances 0.000 description 15

- 230000001070 adhesive effect Effects 0.000 description 15

- 230000001681 protective effect Effects 0.000 description 12

- 239000007789 gas Substances 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 238000000926 separation method Methods 0.000 description 9

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 8

- 229910052757 nitrogen Inorganic materials 0.000 description 8

- 239000001301 oxygen Substances 0.000 description 8

- 229910052760 oxygen Inorganic materials 0.000 description 8

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 7

- 239000004973 liquid crystal related substance Substances 0.000 description 7

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 230000002411 adverse Effects 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 4

- 239000013078 crystal Substances 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 230000003321 amplification Effects 0.000 description 3

- 230000001413 cellular effect Effects 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- 230000010287 polarization Effects 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 238000007639 printing Methods 0.000 description 3

- SBEQWOXEGHQIMW-UHFFFAOYSA-N silicon Chemical compound [Si].[Si] SBEQWOXEGHQIMW-UHFFFAOYSA-N 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- UQSXHKLRYXJYBZ-UHFFFAOYSA-N Iron oxide Chemical compound [Fe]=O UQSXHKLRYXJYBZ-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 239000001055 blue pigment Substances 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 238000004070 electrodeposition Methods 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 239000001056 green pigment Substances 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 2

- 229960001730 nitrous oxide Drugs 0.000 description 2

- 235000013842 nitrous oxide Nutrition 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 239000001054 red pigment Substances 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 238000001237 Raman spectrum Methods 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- XHCLAFWTIXFWPH-UHFFFAOYSA-N [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] XHCLAFWTIXFWPH-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 229910000423 chromium oxide Inorganic materials 0.000 description 1

- 229910000428 cobalt oxide Inorganic materials 0.000 description 1

- IVMYJDGYRUAWML-UHFFFAOYSA-N cobalt(ii) oxide Chemical compound [Co]=O IVMYJDGYRUAWML-UHFFFAOYSA-N 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- HTXDPTMKBJXEOW-UHFFFAOYSA-N dioxoiridium Chemical compound O=[Ir]=O HTXDPTMKBJXEOW-UHFFFAOYSA-N 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000004043 dyeing Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005868 electrolysis reaction Methods 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 229910000457 iridium oxide Inorganic materials 0.000 description 1

- 239000000693 micelle Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 1

- 229910000480 nickel oxide Inorganic materials 0.000 description 1

- 229910000484 niobium oxide Inorganic materials 0.000 description 1

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 1

- GNRSAWUEBMWBQH-UHFFFAOYSA-N oxonickel Chemical compound [Ni]=O GNRSAWUEBMWBQH-UHFFFAOYSA-N 0.000 description 1

- HBEQXAKJSGXAIQ-UHFFFAOYSA-N oxopalladium Chemical compound [Pd]=O HBEQXAKJSGXAIQ-UHFFFAOYSA-N 0.000 description 1

- DYIZHKNUQPHNJY-UHFFFAOYSA-N oxorhenium Chemical compound [Re]=O DYIZHKNUQPHNJY-UHFFFAOYSA-N 0.000 description 1

- SJLOMQIUPFZJAN-UHFFFAOYSA-N oxorhodium Chemical compound [Rh]=O SJLOMQIUPFZJAN-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 229910003445 palladium oxide Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910003449 rhenium oxide Inorganic materials 0.000 description 1

- 229910003450 rhodium oxide Inorganic materials 0.000 description 1

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 1

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- GGCZERPQGJTIQP-UHFFFAOYSA-N sodium;9,10-dioxoanthracene-2-sulfonic acid Chemical compound [Na+].C1=CC=C2C(=O)C3=CC(S(=O)(=O)O)=CC=C3C(=O)C2=C1 GGCZERPQGJTIQP-UHFFFAOYSA-N 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- IOWOAQVVLHHFTL-UHFFFAOYSA-N technetium(vii) oxide Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[Tc+7].[Tc+7] IOWOAQVVLHHFTL-UHFFFAOYSA-N 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 238000011282 treatment Methods 0.000 description 1

- 229910001935 vanadium oxide Inorganic materials 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by potential barriers, e.g. phototransistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14665—Imagers using a photoconductor layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/04—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements with semiconductor devices only

- H03F3/08—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements with semiconductor devices only controlled by light

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1262—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate

- H01L27/1266—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate the substrate on which the devices are formed not being the final device substrate, e.g. using a temporary substrate

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Liquid Crystal (AREA)

- Light Receiving Elements (AREA)

Description

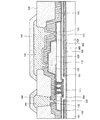

本実施の形態を、図1、図2、図3、図4(A)〜図4(C)、図5(A)〜図5(C)、図6(A)〜図6(C)、図7(A)〜図7(B)、図8(A)〜図8(B)、図9、図10(A)〜図10(B)、図11、図12、図13、図14(A)〜図14(B)、図15を用いて以下に説明する。

本実施の形態では、実施の形態1とは異なる構成の半導体装置を、図16、図17を用いて説明する。

本実施の形態では、実施の形態1及び実施の形態2とは異なる半導体装置について、図18を用いて説明する。

本実施の形態では、本発明により得られた光電変換素子を有する半導体装置を様々な電子機器に組み込んだ例について説明する。本発明が適用される電子機器として、コンピュータ、ディスプレイ、携帯電話、テレビなどが挙げられる。それらの電子機器の具体例を、図19、図20(A)〜図20(B)、図21(A)〜図21(B)、図22及び図23(A)〜図23(B)に示す。

101 基板

102 絶縁膜

103 金属膜

104 絶縁膜

105 絶縁膜

107 ゲート絶縁膜

109 剥離層

111 TFT

112 層間絶縁膜

121 電極

122 電極

123 電極

125 光電変換層

125i i型半導体層

125n n型半導体層

125p p型半導体層

129 保護膜

131 層間絶縁膜

132 電極

133 電極

135 層間絶縁膜

139 基板

141 電極

142 電極

143 電極

144 電極

145 ゲート電極

151 領域

152 領域

161 レーザビーム

162 接続電極

163 接続電極

205 島状半導体膜

207 下層ゲート電極

208 上層ゲート電極

211 ゲート配線

212 ソース電極

213 ドレイン電極

218a 回路

218b 回路

218i 回路

219a 端子

219b 端子

219i 端子

220a 端子

220b 端子

220i 端子

221a 端子

221b 端子

221i 端子

255a TFT

255b TFT

255i TFT

231 カレントミラー回路

234 pチャネル型TFT

234 pチャネル型TFT

235 pチャネル型TFT

244 配線

245 配線

246 ゲート電極

253 フォトダイオード

254 TFT

255 TFT

261 カレントミラー回路

330 剥離層

331 基板

332 絶縁膜

333 金属膜

334 絶縁膜

335 カラーフィルタ

336 オーバーコート層

337 接着材

338 カラーフィルム

339 基板

701 本体(A)

702 本体(B)

703 筐体

704 操作キー

705 音声入力部

706 音声出力部

707 回路基板

708 表示パネル(A)

709 表示パネル(B)

710 蝶番

711 透光性材料部

712 光電変換素子

721 本体

722 筐体

723 表示パネル

724 操作キー

725 音声出力部

726 音声入力部

727 光電変換素子

728 光電変換素子

731 本体

732 筐体

733 表示部

734 キーボード

735 外部接続ポート

736 ポインティングデバイス

741 筐体

742 支持台

743 表示部

751a 基板

751b 基板

752 液晶層

753 バックライト

754 光電変換素子形成領域

755a 偏光フィルタ

755b 偏光フィルタ

761 筐体

762 液晶パネル

801 リリースボタン

802 メインスイッチ

803 ファインダ窓

804 フラッシュ

805 レンズ

806 鏡胴

807 筺体

811 ファインダ接眼窓

812 モニタ

813 操作ボタン

Claims (4)

- 基板上に、開口部を有する金属層を形成し、

前記金属層の表面を酸化させ、金属酸化物層を形成し、

前記金属酸化物層及び前記開口部の上に絶縁層を形成し、

前記絶縁層の上であって、前記開口部と重なる領域内に、トランジスタを形成し、

前記トランジスタに電気的に接続される光電変換素子を形成し、

前記金属酸化物層にレーザビームを照射して、前記光電変換素子及び前記トランジスタ及び前記絶縁層を、前記基板から剥離することを特徴とする半導体装置の作製方法。 - 基板上に、開口部を有する金属層を形成し、

前記金属層の表面を酸化させ、金属酸化物層を形成し、

前記金属酸化物層及び前記開口部の上に絶縁層を形成し、

前記絶縁層の上であって、前記開口部と重なる領域内に、トランジスタを有する回路を形成し、

前記回路に電気的に接続される光電変換素子を形成し、

前記金属酸化物層にレーザビームを照射して、前記光電変換素子及び前記トランジスタ及び前記絶縁層を、前記基板から剥離することを特徴とする半導体装置の作製方法。 - 請求項2において、

前記回路は、カレントミラー回路であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項3のいずれか一項において、

前記金属層は、チタン(Ti)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、タンタル(Ta)、ニオブ(Nb)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、テクネチウム(Tc)、レニウム(Re)、鉄(Fe)、ルテニウム(Ru)、オスミウム(Os)、コバルト(Co)、ロジウム(Rh)、イリジウム(Ir)、ニッケル(Ni)、パラジウム(Pd)のいずれか1つを用いて形成されることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008059749A JP5478787B2 (ja) | 2007-03-20 | 2008-03-10 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007073186 | 2007-03-20 | ||

| JP2007073186 | 2007-03-20 | ||

| JP2008059749A JP5478787B2 (ja) | 2007-03-20 | 2008-03-10 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008263182A JP2008263182A (ja) | 2008-10-30 |

| JP2008263182A5 JP2008263182A5 (ja) | 2011-04-14 |

| JP5478787B2 true JP5478787B2 (ja) | 2014-04-23 |

Family

ID=39773744

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008059749A Expired - Fee Related JP5478787B2 (ja) | 2007-03-20 | 2008-03-10 | 半導体装置の作製方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7759629B2 (ja) |

| JP (1) | JP5478787B2 (ja) |

| KR (1) | KR101406768B1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7923800B2 (en) * | 2006-12-27 | 2011-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| JP2010091482A (ja) | 2008-10-09 | 2010-04-22 | Toshiba Corp | 半導体集積回路装置及びその遅延故障テスト方法 |

| JP5581106B2 (ja) * | 2009-04-27 | 2014-08-27 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5700073B2 (ja) * | 2013-06-13 | 2015-04-15 | セイコーエプソン株式会社 | 光電変換装置、電気光学装置、電子機器 |

| US9443872B2 (en) | 2014-03-07 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9397001B2 (en) * | 2014-12-11 | 2016-07-19 | Panasonic Intellectual Property Management Co., Ltd. | Method for manufacturing electronic device comprising a resin substrate and an electronic component |

| JP6917700B2 (ja) | 2015-12-02 | 2021-08-11 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US10923350B2 (en) * | 2016-08-31 | 2021-02-16 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| US11177373B2 (en) * | 2016-11-03 | 2021-11-16 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5306648A (en) * | 1986-01-24 | 1994-04-26 | Canon Kabushiki Kaisha | Method of making photoelectric conversion device |

| JPS63269570A (ja) | 1987-04-27 | 1988-11-07 | Seiko Epson Corp | カラ−イメ−ジセンサ |

| JP3268369B2 (ja) | 1993-02-23 | 2002-03-25 | 株式会社河合楽器製作所 | 高精度板厚の圧延金属板の製造装置 |

| JP3173750B2 (ja) * | 1993-05-21 | 2001-06-04 | 株式会社半導体エネルギー研究所 | 電気光学装置の作製方法 |

| JPH11243209A (ja) * | 1998-02-25 | 1999-09-07 | Seiko Epson Corp | 薄膜デバイスの転写方法、薄膜デバイス、薄膜集積回路装置、アクティブマトリクス基板、液晶表示装置および電子機器 |

| JP2001343668A (ja) * | 2000-05-30 | 2001-12-14 | Toshiba Corp | 表示装置用電極基板 |

| US7024662B2 (en) * | 2001-03-14 | 2006-04-04 | Microsoft Corporation | Executing dynamically assigned functions while providing services |

| JP2003109773A (ja) * | 2001-07-27 | 2003-04-11 | Semiconductor Energy Lab Co Ltd | 発光装置、半導体装置およびそれらの作製方法 |

| JP4472238B2 (ja) | 2001-08-10 | 2010-06-02 | 株式会社半導体エネルギー研究所 | 剥離方法および半導体装置の作製方法 |

| TW554398B (en) * | 2001-08-10 | 2003-09-21 | Semiconductor Energy Lab | Method of peeling off and method of manufacturing semiconductor device |

| TWI264121B (en) * | 2001-11-30 | 2006-10-11 | Semiconductor Energy Lab | A display device, a method of manufacturing a semiconductor device, and a method of manufacturing a display device |

| KR101079757B1 (ko) * | 2002-10-30 | 2011-11-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 반도체장치의 제작방법 |

| EP1434264A3 (en) * | 2002-12-27 | 2017-01-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method using the transfer technique |

| JP4408042B2 (ja) | 2002-12-27 | 2010-02-03 | 株式会社半導体エネルギー研究所 | 半導体装置及びその作製方法 |

| KR101026644B1 (ko) * | 2003-01-08 | 2011-04-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US7495272B2 (en) * | 2003-10-06 | 2009-02-24 | Semiconductor Energy Labortaory Co., Ltd. | Semiconductor device having photo sensor element and amplifier circuit |

| JP4827396B2 (ja) * | 2003-10-06 | 2011-11-30 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4939742B2 (ja) * | 2003-10-28 | 2012-05-30 | 株式会社半導体エネルギー研究所 | 光学フィルムの作製方法 |

| EP1727120B1 (en) * | 2005-05-23 | 2008-07-09 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and manufacturing method thereof |

| KR101281991B1 (ko) | 2005-07-27 | 2013-07-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP5683059B2 (ja) * | 2007-09-28 | 2015-03-11 | 富士フイルム株式会社 | 撮像素子 |

-

2008

- 2008-03-06 US US12/043,640 patent/US7759629B2/en not_active Expired - Fee Related

- 2008-03-10 JP JP2008059749A patent/JP5478787B2/ja not_active Expired - Fee Related

- 2008-03-20 KR KR1020080025690A patent/KR101406768B1/ko active IP Right Grant

-

2010

- 2010-07-14 US US12/836,142 patent/US8035077B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8035077B2 (en) | 2011-10-11 |

| KR101406768B1 (ko) | 2014-06-12 |

| US7759629B2 (en) | 2010-07-20 |

| KR20080085778A (ko) | 2008-09-24 |

| JP2008263182A (ja) | 2008-10-30 |

| US20080230682A1 (en) | 2008-09-25 |

| US20100282947A1 (en) | 2010-11-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5478787B2 (ja) | 半導体装置の作製方法 | |

| JP5326027B2 (ja) | 半導体装置 | |

| KR101389808B1 (ko) | 광전변환장치 | |

| KR101387370B1 (ko) | 반도체 장치 | |

| JP5070030B2 (ja) | 半導体装置 | |

| JP5667273B2 (ja) | 光電変換装置 | |

| TWI423431B (zh) | 光電轉換裝置和其製造方法 | |

| JP2014187395A (ja) | 半導体装置および電子機器 | |

| JP4809715B2 (ja) | 光電変換装置及びその作製方法、並びに半導体装置 | |

| JP2007165865A (ja) | 光電変換装置 | |

| JP4750070B2 (ja) | 半導体装置及びそれを用いた電子機器 | |

| JP5355915B2 (ja) | 半導体装置 | |

| JP4532418B2 (ja) | 光センサ及びその作製方法 | |

| JP5137418B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110301 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110301 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120627 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130402 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130517 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140211 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5478787 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |