JP5441208B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP5441208B2 JP5441208B2 JP2009146809A JP2009146809A JP5441208B2 JP 5441208 B2 JP5441208 B2 JP 5441208B2 JP 2009146809 A JP2009146809 A JP 2009146809A JP 2009146809 A JP2009146809 A JP 2009146809A JP 5441208 B2 JP5441208 B2 JP 5441208B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- clock signal

- signal

- buffer

- internal clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

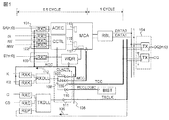

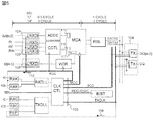

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/222—Clock generating, synchronizing or distributing circuits within memory device

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/22—Control and timing of internal memory operations

- G11C2207/2272—Latency related aspects

Landscapes

- Dram (AREA)

- Static Random-Access Memory (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009146809A JP5441208B2 (ja) | 2009-06-19 | 2009-06-19 | 半導体記憶装置 |

| US12/814,478 US8351283B2 (en) | 2009-06-19 | 2010-06-13 | Semiconductor storage device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009146809A JP5441208B2 (ja) | 2009-06-19 | 2009-06-19 | 半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011003250A JP2011003250A (ja) | 2011-01-06 |

| JP2011003250A5 JP2011003250A5 (enExample) | 2012-04-12 |

| JP5441208B2 true JP5441208B2 (ja) | 2014-03-12 |

Family

ID=43354241

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009146809A Active JP5441208B2 (ja) | 2009-06-19 | 2009-06-19 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8351283B2 (enExample) |

| JP (1) | JP5441208B2 (enExample) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101998750B1 (ko) * | 2012-07-16 | 2019-10-01 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| KR102041471B1 (ko) * | 2012-12-24 | 2019-11-07 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| US9053768B2 (en) * | 2013-03-14 | 2015-06-09 | Gsi Technology, Inc. | Systems and methods of pipelined output latching involving synchronous memory arrays |

| CN103440880A (zh) * | 2013-09-03 | 2013-12-11 | 苏州宽温电子科技有限公司 | 一种sram存储器以及位单元追踪方法 |

| KR102130611B1 (ko) | 2013-12-31 | 2020-07-06 | 삼성전자주식회사 | 아날로그-디지털 변환 회로, 이를 포함하는 이미지 센서 및 이미지 센서의 동작 방법 |

| US11227653B1 (en) | 2016-12-06 | 2022-01-18 | Gsi Technology, Inc. | Storage array circuits and methods for computational memory cells |

| US10891076B1 (en) | 2016-12-06 | 2021-01-12 | Gsi Technology, Inc. | Results processing circuits and methods associated with computational memory cells |

| US10770133B1 (en) | 2016-12-06 | 2020-09-08 | Gsi Technology, Inc. | Read and write data processing circuits and methods associated with computational memory cells that provides write inhibits and read bit line pre-charge inhibits |

| US10847213B1 (en) | 2016-12-06 | 2020-11-24 | Gsi Technology, Inc. | Write data processing circuits and methods associated with computational memory cells |

| US10854284B1 (en) | 2016-12-06 | 2020-12-01 | Gsi Technology, Inc. | Computational memory cell and processing array device with ratioless write port |

| US10777262B1 (en) | 2016-12-06 | 2020-09-15 | Gsi Technology, Inc. | Read data processing circuits and methods associated memory cells |

| US10847212B1 (en) | 2016-12-06 | 2020-11-24 | Gsi Technology, Inc. | Read and write data processing circuits and methods associated with computational memory cells using two read multiplexers |

| US10860320B1 (en) | 2016-12-06 | 2020-12-08 | Gsi Technology, Inc. | Orthogonal data transposition system and method during data transfers to/from a processing array |

| US10725777B2 (en) | 2016-12-06 | 2020-07-28 | Gsi Technology, Inc. | Computational memory cell and processing array device using memory cells |

| US10943648B1 (en) | 2016-12-06 | 2021-03-09 | Gsi Technology, Inc. | Ultra low VDD memory cell with ratioless write port |

| US10998040B2 (en) | 2016-12-06 | 2021-05-04 | Gsi Technology, Inc. | Computational memory cell and processing array device using the memory cells for XOR and XNOR computations |

| KR20190000663A (ko) * | 2017-06-23 | 2019-01-03 | 에스케이하이닉스 주식회사 | 메모리 장치 및 그 동작 방법 |

| US10877731B1 (en) | 2019-06-18 | 2020-12-29 | Gsi Technology, Inc. | Processing array device that performs one cycle full adder operation and bit line read/write logic features |

| US10958272B2 (en) | 2019-06-18 | 2021-03-23 | Gsi Technology, Inc. | Computational memory cell and processing array device using complementary exclusive or memory cells |

| US10930341B1 (en) | 2019-06-18 | 2021-02-23 | Gsi Technology, Inc. | Processing array device that performs one cycle full adder operation and bit line read/write logic features |

| US11955971B2 (en) * | 2021-02-08 | 2024-04-09 | Rambus Inc. | Integrated transmitter slew rate calibration |

| US11909404B1 (en) * | 2022-12-12 | 2024-02-20 | Advanced Micro Devices, Inc. | Delay-locked loop offset calibration and correction |

| US11916558B1 (en) * | 2022-12-13 | 2024-02-27 | Qualcomm Incorporated | DDR phy parallel clock paths architecture |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1011966A (ja) * | 1996-06-27 | 1998-01-16 | Mitsubishi Electric Corp | 同期型半導体記憶装置および同期型メモリモジュール |

| JP3549751B2 (ja) * | 1998-11-30 | 2004-08-04 | 富士通株式会社 | 半導体集積回路装置 |

| JP2001068650A (ja) * | 1999-08-30 | 2001-03-16 | Hitachi Ltd | 半導体集積回路装置 |

| JP2002100980A (ja) | 2000-09-21 | 2002-04-05 | Ricoh Co Ltd | Dll回路 |

| KR100422572B1 (ko) * | 2001-06-30 | 2004-03-12 | 주식회사 하이닉스반도체 | 레지스터 제어 지연고정루프 및 그를 구비한 반도체 소자 |

| KR100560644B1 (ko) * | 2002-01-09 | 2006-03-16 | 삼성전자주식회사 | 클럭 동기회로를 구비하는 집적회로장치 |

| JP4426277B2 (ja) * | 2003-12-24 | 2010-03-03 | 株式会社リコー | 半導体集積回路及びその半導体集積回路を使用した光ディスク記録装置 |

| US7116143B2 (en) * | 2004-12-30 | 2006-10-03 | Micron Technology, Inc. | Synchronous clock generator including duty cycle correction |

| KR100834400B1 (ko) | 2005-09-28 | 2008-06-04 | 주식회사 하이닉스반도체 | Dram의 동작 주파수를 높이기 위한 지연고정루프 및 그의 출력드라이버 |

| US7449930B2 (en) * | 2005-09-29 | 2008-11-11 | Hynix Semiconductor Inc. | Delay locked loop circuit |

| KR100722775B1 (ko) * | 2006-01-02 | 2007-05-30 | 삼성전자주식회사 | 반도체 장치의 지연동기루프 회로 및 지연동기루프제어방법 |

-

2009

- 2009-06-19 JP JP2009146809A patent/JP5441208B2/ja active Active

-

2010

- 2010-06-13 US US12/814,478 patent/US8351283B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20100322022A1 (en) | 2010-12-23 |

| US8351283B2 (en) | 2013-01-08 |

| JP2011003250A (ja) | 2011-01-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5441208B2 (ja) | 半導体記憶装置 | |

| US11226925B2 (en) | Scalable 2.5D interface circuitry | |

| US7514955B2 (en) | Semiconductor memory device with ability to effectively adjust operation time for on-die termination | |

| US6816991B2 (en) | Built-in self-testing for double data rate input/output | |

| US7793174B2 (en) | Semiconductor apparatus and test method therefor | |

| US20080205170A1 (en) | Ddr-sdram interface circuitry, and method and system for testing the interface circuitry | |

| US7965568B2 (en) | Semiconductor integrated circuit device and method of testing same | |

| US10270445B2 (en) | Half-frequency command path | |

| US20230401008A1 (en) | Command address input buffer bias current reduction | |

| JP2012008881A (ja) | メモリシステム及びその制御方法 | |

| US8321607B2 (en) | Semiconductor memory device and multilayered chip semiconductor device | |

| KR20090071893A (ko) | 반도체 메모리 장치의 데이터 입력 회로 및 그 제어 방법 | |

| CN110782929B (zh) | 每个通路的占空比校正 | |

| US12488818B2 (en) | Circuit for aligning command input data and semiconducter device including the same | |

| EP1745486A1 (en) | Multiple data rate ram memory controller | |

| CN103903643B (zh) | 半导体装置的数据写入电路 | |

| JP2012058997A (ja) | 半導体集積回路 | |

| US10310743B2 (en) | Latency improvements between sub-blocks | |

| JP2006065470A (ja) | メモリ制御方法および装置 | |

| JP2014164776A (ja) | 半導体装置及びその制御方法 | |

| JP2010097660A (ja) | 半導体装置 | |

| US7385872B2 (en) | Method and apparatus for increasing clock frequency and data rate for semiconductor devices | |

| Bhatti et al. | Data strobe timing of DDR2 using a statistical random sampling technique | |

| JP2011008844A (ja) | 半導体装置 | |

| KR20070074342A (ko) | 싱글 데이터 레이트 쓰기 모드시 더블 데이터 레이트방식으로 기입하는 반도체 메모리 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120227 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120227 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130311 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130328 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130513 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130822 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131002 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131213 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5441208 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |