JP5431992B2 - トランスミッションゲート及び半導体装置 - Google Patents

トランスミッションゲート及び半導体装置 Download PDFInfo

- Publication number

- JP5431992B2 JP5431992B2 JP2010026931A JP2010026931A JP5431992B2 JP 5431992 B2 JP5431992 B2 JP 5431992B2 JP 2010026931 A JP2010026931 A JP 2010026931A JP 2010026931 A JP2010026931 A JP 2010026931A JP 5431992 B2 JP5431992 B2 JP 5431992B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- gate

- input

- output terminal

- level shifter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/161—Modifications for eliminating interference voltages or currents in field-effect transistor switches

- H03K17/162—Modifications for eliminating interference voltages or currents in field-effect transistor switches without feedback from the output circuit to the control circuit

- H03K17/163—Soft switching

- H03K17/164—Soft switching using parallel switching arrangements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0054—Gating switches, e.g. pass gates

Description

(V5−Vout−Vtp)・Cgsp/(Cgsp+Ch)

=(V4−Vout−Vtn)・Cgsn/(Cgsn+Ch)・・・(11)

入力端子INの入力電圧Vinは、第一レベルシフタ13の入力端子と第二レベルシフタ14の入力端子に入力される。

Vtp=Vtn・・・(1)

Vo1=Vo2・・・(2)

Vs1=Vtp+Vo1=Vs2=Vtn+Vo2・・・(3)

ここで、制御端子CNTにハイレベルの電圧Vcが入力されているとすると、電圧/Vcはローレベルになる。すると、スイッチ42及び43がオンし、スイッチ41及びスイッチ44がオフする。よって、ゲート電圧選択回路15は、第二入力端子IN2の電圧(Vin−Vs2)つまり電圧(Vin−Vs1)を第一出力端子OUT1から出力する。また、ゲート電圧選択回路15は、第一入力端子IN1の電圧(Vin+Vs1)を第二出力端子OUT2から出力する。

Vgsp=−Vs1=−(Vtp+Vo1)・・・(4)

PMOSトランジスタ11のゲート・ソース間電圧Vgspは閾値電圧(−Vtp)よりも低くなるので、PMOSトランジスタ11はオンする。

Vgsn=Vs2=Vtn+Vo2=Vs1=Vtp+Vo1・・・(5)

NMOSトランジスタ12のゲート・ソース間電圧Vgsnは閾値電圧Vtnよりも高くなるので、NMOSトランジスタ12はオンする。

Vgsp=Vs1=Vtp+Vo1・・・(6)

PMOSトランジスタ11のゲート・ソース間電圧Vgspは閾値電圧(−Vtp)よりも高くなるので、PMOSトランジスタ11はオフする。

Vgsn=−Vs2=−(Vtn+Vo2)=−Vs1=−(Vtp+Vo1)・・・(7)

NMOSトランジスタ12のゲート・ソース間電圧Vgsnは閾値電圧Vtnよりも低くなるので、NMOSトランジスタ12はオフする。

(|Vgsp|−|Vtp|)・Cgsp/(Cgsp+Ch)

=(Vgsn−Vtn)・Cgsn/(Cgsn+Ch)・・・(8)

CgspはPMOSトランジスタ11のゲート・ソース間容量、CgsnはNMOSトランジスタ12のゲート・ソース間容量、Chは出力端子寄生容量である。

Cgsp/(Cgsp+Ch)=Cgsn/(Cgsn+Ch)・・・(9)

この式(9)は入力電圧Vinに依存しない。すなわち、トランスミッションゲート10は、入力電圧Vinの電圧値に関係なくクロックフィードスルーの影響が低減し、高S/N特性が実現される。

11 PMOSトランジスタ

12 NMOSトランジスタ

13 第一レベルシフタ

14 第二レベルシフタ

15 ゲート電圧選択回路

71 アンプ

Claims (3)

- 入力端子から入力された入力電圧を出力端子から出力するトランスミッションゲートであって、

前記入力電圧に所定電圧が加算された第一電圧を出力する第一レベルシフタと、

前記入力電圧から前記所定電圧が減算された第二電圧を出力する第二レベルシフタと、

前記第一電圧と前記第二電圧が入力され、前記第一電圧と前記第二電圧を切替えて相補的に出力する第一出力端子と第二出力端子を有するゲート電圧選択回路と、

前記第一出力端子がゲートに接続されたPMOSトランジスタと、

前記第二出力端子がゲートに接続されたNMOSトランジスタと、を備え、

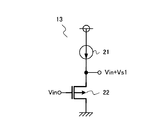

前記PMOSトランジスタと前記NMOSトランジスタは、ゲート長とゲート幅とゲート酸化膜厚と閾値電圧の絶対値とが等しい、ことを特徴とするトランスミッションゲート。 - 前記第一レベルシフタは、前記入力電圧がゲートに入力された第二のPMOSトランジスタを有し、

前記第二レベルシフタは、前記入力電圧がゲートに入力された第二のNMOSトランジスタを有し、

前記第二のPMOSトランジスタと前記第二のNMOSトランジスタは、閾値電圧の絶対値とオーバードライブ電圧が等しく、

前記所定電圧は、該閾値電圧の絶対値と該オーバードライブ電圧の和である、ことを特徴とする請求項1記載のトランスミッションゲート。 - 請求項1または2に記載のトランスミッションゲートを備えた半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010026931A JP5431992B2 (ja) | 2010-02-09 | 2010-02-09 | トランスミッションゲート及び半導体装置 |

| TW100103453A TWI530096B (zh) | 2010-02-09 | 2011-01-28 | Transmission and semiconductor devices |

| US13/022,338 US8354873B2 (en) | 2010-02-09 | 2011-02-07 | Transmission gate and semiconductor device |

| KR1020110010961A KR101727752B1 (ko) | 2010-02-09 | 2011-02-08 | 트랜스미션 게이트 및 반도체 장치 |

| CN201110039437.2A CN102195637B (zh) | 2010-02-09 | 2011-02-09 | 传输门电路及半导体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010026931A JP5431992B2 (ja) | 2010-02-09 | 2010-02-09 | トランスミッションゲート及び半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011166449A JP2011166449A (ja) | 2011-08-25 |

| JP2011166449A5 JP2011166449A5 (ja) | 2013-02-07 |

| JP5431992B2 true JP5431992B2 (ja) | 2014-03-05 |

Family

ID=44353216

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010026931A Expired - Fee Related JP5431992B2 (ja) | 2010-02-09 | 2010-02-09 | トランスミッションゲート及び半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8354873B2 (ja) |

| JP (1) | JP5431992B2 (ja) |

| KR (1) | KR101727752B1 (ja) |

| CN (1) | CN102195637B (ja) |

| TW (1) | TWI530096B (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010080889A1 (en) * | 2009-01-07 | 2010-07-15 | Zentrum Mikroelektronik Dresden Ag | Adaptive bootstrap circuit for controlling cmos switch(es) |

| JP5923919B2 (ja) * | 2011-10-11 | 2016-05-25 | 株式会社ソシオネクスト | 半導体装置及びアナログスイッチの制御方法 |

| TWI473072B (zh) * | 2013-06-24 | 2015-02-11 | Orise Technology Co Ltd | 減少閂鎖元件數量的源極驅動裝置 |

| CN104426528B (zh) * | 2013-09-11 | 2019-05-07 | 台湾积体电路制造股份有限公司 | 多电压输入缓冲器及其相关方法 |

| JP2016139390A (ja) * | 2015-01-23 | 2016-08-04 | エスアイアイ・セミコンダクタ株式会社 | 検出回路 |

| US9843322B2 (en) * | 2016-03-11 | 2017-12-12 | Texas Instruments Incorporated | Integrated high-side driver for P-N bimodal power device |

| KR101675573B1 (ko) * | 2016-03-21 | 2016-11-11 | 주식회사 이노액시스 | 레벨 시프터, 디지털 아날로그 변환기, 버퍼 증폭기 및 이를 포함하는 소스 드라이버와 전자 장치 |

| TWI653732B (zh) | 2017-09-19 | 2019-03-11 | 世界先進積體電路股份有限公司 | 控制電路及操作電路 |

| CN109560536B (zh) * | 2017-09-26 | 2021-01-05 | 世界先进积体电路股份有限公司 | 控制电路及操作电路 |

| US10818653B2 (en) | 2017-12-12 | 2020-10-27 | Vanguard International Semiconductor Corporation | Control circuit and operating circuit utilizing the same |

| CN108199701B (zh) * | 2017-12-28 | 2021-05-07 | 清华大学 | 一种高速的cmos传输门开关电路 |

| US10763846B1 (en) * | 2019-08-23 | 2020-09-01 | Nxp Usa, Inc. | High voltage tolerant analog switch |

| EP3799309A1 (en) | 2019-09-26 | 2021-03-31 | Ams Ag | Electric circuitry for signal transmission |

| US20220311439A1 (en) * | 2021-03-24 | 2022-09-29 | Stmicroelectronics International N.V. | Multiplexer circuit using a transmission gate circuit with a selectively boosted switch control signal |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4740717A (en) * | 1986-11-25 | 1988-04-26 | North American Philips Corporation, Signetics Division | Switching device with dynamic hysteresis |

| JPH01175410A (ja) * | 1987-12-29 | 1989-07-11 | Sharp Corp | 半導体アナログ・スイッチ |

| JPH0595262A (ja) * | 1991-03-30 | 1993-04-16 | Nec Corp | アナログ入力回路 |

| US5194768A (en) * | 1992-03-27 | 1993-03-16 | Advanced Micro Devices, Inc. | Apparatus for filtering noise from a periodic signal |

| JPH06208423A (ja) * | 1993-01-12 | 1994-07-26 | Mitsubishi Electric Corp | 電源回路 |

| JPH07169292A (ja) | 1993-12-13 | 1995-07-04 | Matsushita Electron Corp | Cmosサンプルホールド回路 |

| JPH07221642A (ja) * | 1994-02-02 | 1995-08-18 | Hitachi Ltd | 半導体集積回路 |

| US6433613B1 (en) * | 2000-12-15 | 2002-08-13 | Fairchild Semiconductor Corporation | Translating switch circuit with disabling option |

| US6693479B1 (en) * | 2002-06-06 | 2004-02-17 | Analog Devices, Inc. | Boost structures for switched-capacitor systems |

| JP3949027B2 (ja) * | 2002-08-06 | 2007-07-25 | 富士通株式会社 | アナログスイッチ回路 |

| FR2894373B1 (fr) * | 2005-12-07 | 2008-01-04 | Atmel Corp | Cellule anti-fusible autonome |

| JP4828343B2 (ja) * | 2006-07-28 | 2011-11-30 | 三菱電機株式会社 | アナログスイッチ回路 |

| JP5018245B2 (ja) * | 2007-05-31 | 2012-09-05 | 株式会社日立製作所 | アナログスイッチ |

| JP2009017276A (ja) * | 2007-07-05 | 2009-01-22 | Nec Electronics Corp | 半導体装置 |

| JP2009108911A (ja) * | 2007-10-29 | 2009-05-21 | Akira Koyama | ネジ固定機構およびネジ固定方法 |

-

2010

- 2010-02-09 JP JP2010026931A patent/JP5431992B2/ja not_active Expired - Fee Related

-

2011

- 2011-01-28 TW TW100103453A patent/TWI530096B/zh not_active IP Right Cessation

- 2011-02-07 US US13/022,338 patent/US8354873B2/en active Active

- 2011-02-08 KR KR1020110010961A patent/KR101727752B1/ko active IP Right Grant

- 2011-02-09 CN CN201110039437.2A patent/CN102195637B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN102195637A (zh) | 2011-09-21 |

| TW201212537A (en) | 2012-03-16 |

| KR20110093661A (ko) | 2011-08-18 |

| TWI530096B (zh) | 2016-04-11 |

| CN102195637B (zh) | 2015-07-01 |

| JP2011166449A (ja) | 2011-08-25 |

| KR101727752B1 (ko) | 2017-04-17 |

| US20110193615A1 (en) | 2011-08-11 |

| US8354873B2 (en) | 2013-01-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5431992B2 (ja) | トランスミッションゲート及び半導体装置 | |

| KR101355684B1 (ko) | 기준 전압 회로 및 전자 기기 | |

| JP4128545B2 (ja) | サンプリングスイッチ | |

| WO2009081619A1 (ja) | バッファおよび表示装置 | |

| JP2011060876A (ja) | 半導体装置及びその耐圧制御方法 | |

| US7492210B2 (en) | Voltage selection circuit | |

| US6924702B2 (en) | Low supply voltage and self-biased high speed receiver | |

| US8159301B1 (en) | Differential amplifier with hysteresis | |

| US7355450B1 (en) | Differential input buffers for low power supply | |

| JP6399938B2 (ja) | 差動出力バッファ | |

| US20120068755A1 (en) | Level shifter | |

| JP2007067819A (ja) | 遅延調整回路及び該回路を備えた同期型半導体装置 | |

| JP6363891B2 (ja) | アナログスイッチ回路およびセレクタ回路 | |

| JP5290015B2 (ja) | バッファ回路 | |

| JP2012114610A (ja) | 電子回路 | |

| US9374047B2 (en) | Buffer circuit | |

| KR102613131B1 (ko) | Cmos 인버터 회로 | |

| US20060181313A1 (en) | Transistor logic circuit | |

| US8723581B1 (en) | Input buffers | |

| JP5203809B2 (ja) | 電流ミラー回路 | |

| JP6610223B2 (ja) | 半導体集積回路 | |

| JP2015002507A (ja) | スイッチ回路 | |

| WO2014114399A1 (en) | Level-shifting device | |

| KR20000074289A (ko) | 레벨 쉬프터 회로 | |

| WO2012132281A1 (ja) | レベルシフト回路及び半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121211 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121211 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131025 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131119 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131205 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5431992 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |