JP5431329B2 - 半導体構成素子および半導体構成素子の製造方法 - Google Patents

半導体構成素子および半導体構成素子の製造方法 Download PDFInfo

- Publication number

- JP5431329B2 JP5431329B2 JP2010523271A JP2010523271A JP5431329B2 JP 5431329 B2 JP5431329 B2 JP 5431329B2 JP 2010523271 A JP2010523271 A JP 2010523271A JP 2010523271 A JP2010523271 A JP 2010523271A JP 5431329 B2 JP5431329 B2 JP 5431329B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- region

- semiconductor component

- electromagnetic beam

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 119

- 238000004519 manufacturing process Methods 0.000 title claims description 16

- 238000000034 method Methods 0.000 title claims description 12

- 230000003287 optical effect Effects 0.000 claims description 62

- 230000005540 biological transmission Effects 0.000 claims description 31

- 239000000463 material Substances 0.000 claims description 25

- 230000005855 radiation Effects 0.000 claims description 25

- 238000001816 cooling Methods 0.000 claims description 19

- 239000000758 substrate Substances 0.000 claims description 17

- 239000007769 metal material Substances 0.000 claims description 12

- 238000006243 chemical reaction Methods 0.000 claims description 9

- 239000000110 cooling liquid Substances 0.000 claims description 3

- 238000001914 filtration Methods 0.000 claims description 2

- 238000007599 discharging Methods 0.000 claims 1

- 239000002985 plastic film Substances 0.000 description 22

- 229920006255 plastic film Polymers 0.000 description 21

- 239000002184 metal Substances 0.000 description 18

- 239000004020 conductor Substances 0.000 description 9

- 239000002826 coolant Substances 0.000 description 6

- 239000012778 molding material Substances 0.000 description 5

- 238000010586 diagram Methods 0.000 description 4

- 238000000576 coating method Methods 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 230000018109 developmental process Effects 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 229910010293 ceramic material Inorganic materials 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000005670 electromagnetic radiation Effects 0.000 description 1

- 229920002457 flexible plastic Polymers 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000002905 metal composite material Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 239000000088 plastic resin Substances 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000003595 spectral effect Effects 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0756—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0753—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00 the devices being arranged next to each other

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Led Devices (AREA)

- Led Device Packages (AREA)

- Optical Integrated Circuits (AREA)

- Semiconductor Lasers (AREA)

Description

・少なくとも1つの放射方向に電磁ビームを放射するための少なくとも1つの第1光学的アクティブ領域を備える第1層を製造する。

・前記第1層を、ケーシングの中、または支持材料の上に配置する。

・電磁ビームを放射するための少なくとも1つの第2光学的アクティブ領域と、少なくとも1つの透明または半透明の透過領域とを備える第2層を製造する。

・前記第2層を、前記第1層の上に配置する。この際前記第2層の前記透過領域は、前記第1層の第1領域の上に配置される。

Claims (16)

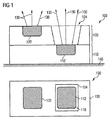

- 少なくとも第1層(110)と第2層(120)とからなるスタックを備える半導体構成素子であって、

・少なくとも1つの放射方向に電磁ビーム(130)を放射するための少なくとも1つの第1光学的アクティブ領域(112)を含む前記第1層(110)と、

・前記少なくとも1つの放射方向に電磁ビーム(130)を放射するための少なくとも1つの第2光学的アクティブ領域(122)を含む前記第2層(120)と

を有する形式の半導体構成素子において、

・前記第1領域(112)は第1層(110)に配置されており、前記第2領域(122)は第2層(120)に配置されており、

前記第2層(120)は、前記第1領域(112)の電磁ビーム(130)が放射される放射方向において前記第1層(110)の上に配置されており、前記第1領域(112)に割り当てられた第1透過領域(124)を有しており、

該第1透過領域は、前記第1領域(112)の前記電磁ビーム(130)に対して少なくとも部分的に透過性であり、

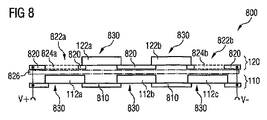

前記第1層と前記第2層(110,120)との間に、少なくとも1つの金属製材料からなる層が配置されており、

該層は、前記第1領域(112)に割り当てられた第2透過領域において少なくとも1つの切欠部を有する

ことを特徴とする半導体構成素子。 - 前記第2層(120)は、前記第1透過領域(124)において、前記第1層(110)の前記電磁ビーム(130)を透過するための少なくとも1つの切欠部を有する、

ことを特徴とする請求項1記載の半導体構成素子。 - 前記第2層(120)は、前記第1透過領域(124)において、少なくとも1つの切欠部を備える金属製材料を含む、

ことを特徴とする請求項2記載の半導体構成素子。 - 前記第2層(120)は、前記第1透過領域(124)において、前記第1層(110)の前記電磁ビーム(130)を透過するための少なくとも1つの透明または不透明な材料を有する、

ことを特徴とする請求項1記載の半導体構成素子。 - 前記金属製材料は、前記第1領域(112)および/または第2領域(122)から熱を排出するように構成されている、

ことを特徴とする請求項1記載の半導体構成素子。 - 前記第1透過領域(124)および前記第2領域(122)は、空間的に隣接しており、かつ空間的につながった1つの放射領域を形成している、

ことを特徴とする請求項1〜5のいずれか一項記載の半導体構成素子。 - 少なくとも前記第1層および第2層(110,120)は、共通の1つのケーシングボディ(570)の中に配置されており、

該ケーシングボディ(570)は光学素子を含み、

該光学素子は、第1領域および/または第2領域(112,122)から放射される電磁ビーム(130)を、所定の方式で、とりわけ周波数変換、回折、屈折、および/またはフィルタリングによって変換する、

ことを特徴とする請求項1〜6のいずれか一項記載の半導体構成素子。 - 前記第1領域および/または前記第2領域(112,122)は、基板レスの半導体構造として、とりわけダイオード構造(210)として構成されている、

ことを特徴とする請求項1〜7のいずれか一項記載の半導体構成素子。 - 前記第1層(110)および前記第2層(120)は、それぞれ半導体基板であり、

前記ダイオード構造(210)は、前記半導体基板の半導体材料にドープすることによって形成されている、

ことを特徴とする請求項1〜7のいずれか一項記載の半導体構成素子。 - 前記第1領域および/または前記第2領域(112,122)のうちの少なくともいずれか、電磁ビーム(130)を、第1の放射方向および該第1の放射方向とは反対の第2の放射方向に放射するように構成されている、

ことを特徴とする請求項8または9記載の半導体構成素子。 - 前記第1層と前記第2層(110,120)との間に、前記第1領域および/または前記第2領域(112,122)の熱を排出するための少なくとも1つの冷却層(520)が配置されており、

該冷却層は、少なくとも前記第1領域(112)に割り当てられた第2透過領域において、部分的に透明に構成されている、

ことを特徴とする請求項1〜10のいずれか一項記載の半導体構成素子。 - 前記冷却層は、少なくとも部分的に冷却液によって充填された空洞を含む、

ことを特徴とする請求項11記載の半導体構成素子。 - 前記第1領域および前記第2領域(112,122)は、放射方向において上下に重なり合って配置されている、

ことを特徴とする請求項1〜12のいずれか一項記載の半導体構成素子。 - 前記第1層および/または前記第2層(110,120)は、電磁ビーム(130)を放射するための複数の光学的アクティブ領域(112,122)を有し、

前記第1層(110)の各光学的アクティブ領域(112)に、それぞれ前記第2層(120)の第1透過領域(124)が割り当てられている、

ことを特徴とする請求項1〜13のいずれか一項記載の半導体構成素子。 - 前記半導体構成素子は、電磁ビーム(130)を放射するためのそれぞれ少なくとも1つの光学的アクティブ領域(112,122,332,342,352)を備える、上下に重なり合って配置された複数の層(110,120,330,340,350)を有しており、

この際、それぞれ上に位置する各層(120,330,340,350)は、その下に位置する層(110,120,330,340)の電磁ビーム(130)に対する少なくとも1つの透過領域(124)を有する、

ことを特徴とする請求項1〜14のいずれか一項記載の半導体構成素子。 - 少なくとも第1及び第2層からなるスタックを備える半導体構成素子の製造方法において、

・少なくとも1つの放射方向に電磁ビーム(130)を放射するための少なくとも1つの第1光学的アクティブ領域(112)を備える前記第1層(110)を製造し、

・該第1層(110)を、ケーシングボディ(570)の中、または支持材料(140)の上に配置し、

・電磁ビーム(130)を放射するための少なくとも1つの第2光学的アクティブ領域(122)と、少なくとも1つの透明または半透明の透過領域(124)とを備える前記第2層(120)を製造し、

・該第2層(120)を前記第1層(110)の上に配置し、

この際、当該第2層(120)を、前記第1領域(112)の電磁ビーム(130)が放射される方向において、第1層(110)の上に配置し、前記第2層(120)の前記透過領域(124)を、透過方向において、前記第1層(110)の前記第1領域(112)の上に配置し、

・前記第1層と前記第2層(110,120)との間に、少なくとも1つの切欠部を有する金属製材料からなる層を、該少なくとも1つの切欠部が前記第1領域(112)に割り当てられた第2透過領域に配置されるように配置する、

ことを特徴とする方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102007041896.7 | 2007-09-04 | ||

| DE102007041896A DE102007041896A1 (de) | 2007-09-04 | 2007-09-04 | Halbleiterbauelement und Verfahren zur Herstellung eines Halbleiterbauelements |

| PCT/DE2008/001449 WO2009030204A2 (de) | 2007-09-04 | 2008-08-29 | Halbleiterbauelement und verfahren zur herstellung eines halbleiterbauelements |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010538479A JP2010538479A (ja) | 2010-12-09 |

| JP2010538479A5 JP2010538479A5 (ja) | 2011-07-14 |

| JP5431329B2 true JP5431329B2 (ja) | 2014-03-05 |

Family

ID=40139376

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010523271A Active JP5431329B2 (ja) | 2007-09-04 | 2008-08-29 | 半導体構成素子および半導体構成素子の製造方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8384096B2 (ja) |

| EP (1) | EP2183779B1 (ja) |

| JP (1) | JP5431329B2 (ja) |

| KR (1) | KR20100080782A (ja) |

| CN (1) | CN101796638B (ja) |

| DE (1) | DE102007041896A1 (ja) |

| WO (1) | WO2009030204A2 (ja) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102009015307A1 (de) * | 2009-03-27 | 2010-09-30 | Osram Opto Semiconductors Gmbh | Anordnung optoelektronischer Bauelemente |

| DE102009015224A1 (de) * | 2009-03-31 | 2010-12-02 | Siemens Aktiengesellschaft | LED-Lichtquelle mit einer Vielzahl von LED-Chips und LED-Chip zur Verwendung in selbiger |

| US8337030B2 (en) | 2009-05-13 | 2012-12-25 | Cree, Inc. | Solid state lighting devices having remote luminescent material-containing element, and lighting methods |

| DE102010006396A1 (de) * | 2010-02-01 | 2011-08-04 | Giesecke & Devrient GmbH, 81677 | Beleuchtungseinrichtung und Sensor zur Prüfung von Wertdokumenten |

| EP2407706A1 (en) * | 2010-07-14 | 2012-01-18 | Civilight Shenzhen Semiconductor Lighting Co., Ltd | Warm white light LED lamp with high luminance and high color rendering index and led module |

| TWI446578B (zh) * | 2010-09-23 | 2014-07-21 | Epistar Corp | 發光元件及其製法 |

| CN102446907A (zh) * | 2010-10-13 | 2012-05-09 | 环旭电子股份有限公司 | 立体封装结构及其制作方法 |

| US9648673B2 (en) * | 2010-11-05 | 2017-05-09 | Cree, Inc. | Lighting device with spatially segregated primary and secondary emitters |

| DE102011087887A1 (de) * | 2011-12-07 | 2013-06-13 | Osram Gmbh | Leuchtdiodenanordnung |

| DE102013201327A1 (de) * | 2013-01-28 | 2014-07-31 | Osram Gmbh | Leiterplatte, optoelektronisches Bauteil und Anordnung optoelektronischer Bauteile |

| JP6083253B2 (ja) * | 2013-02-21 | 2017-02-22 | 日亜化学工業株式会社 | 発光装置の積層体 |

| KR101998765B1 (ko) * | 2013-03-25 | 2019-07-10 | 엘지이노텍 주식회사 | 발광소자 패키지 |

| JP6318510B2 (ja) * | 2013-09-12 | 2018-05-09 | 日亜化学工業株式会社 | フレキシブル基板及び発光装置 |

| EP3170202B1 (en) | 2014-07-18 | 2021-05-19 | Lumileds LLC | Led light source for automotive application |

| KR102244435B1 (ko) | 2014-09-03 | 2021-04-26 | 삼성디스플레이 주식회사 | 회로판 및 이를 포함하는 전자 장치 |

| DE102015215301A1 (de) * | 2015-08-11 | 2017-02-16 | Osram Gmbh | Leuchtdiodenanordnung und Verfahren zum Herstellen einer Leuchtdiodenanordnung |

| CN105527770B (zh) * | 2016-02-03 | 2019-03-05 | 京东方科技集团股份有限公司 | 一种显示装置 |

| KR102006188B1 (ko) * | 2017-12-29 | 2019-08-01 | 엘지전자 주식회사 | 반도체 발광 소자를 이용한 차량용 램프 및 그 제어방법 |

| TWI692865B (zh) * | 2018-11-21 | 2020-05-01 | 友達光電股份有限公司 | 顯示裝置 |

| US11637219B2 (en) | 2019-04-12 | 2023-04-25 | Google Llc | Monolithic integration of different light emitting structures on a same substrate |

| CN110931614B (zh) * | 2019-05-08 | 2021-08-13 | 深圳第三代半导体研究院 | 一种正装集成单元二极管芯片 |

| DE102019216924A1 (de) | 2019-11-04 | 2021-05-06 | Robert Bosch Gmbh | Laseremitteranordnung sowie LiDAR-System |

| CN111081730B (zh) * | 2019-12-13 | 2022-12-27 | 深圳第三代半导体研究院 | Micro-LED芯片及其制造方法 |

| DE102021120915A1 (de) | 2021-08-11 | 2023-02-16 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Anordnung für eine Heckleuchte für ein Kraftfahrzeug und Verfahren zum Betreiben einer Anordnung für eine Heckleuchte für ein Kraftfahrzeug |

Family Cites Families (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4331938A (en) * | 1980-08-25 | 1982-05-25 | Rca Corporation | Injection laser diode array having high conductivity regions in the substrate |

| US4960660A (en) * | 1989-03-31 | 1990-10-02 | E. I. Du Pont De Nemours And Company | High resolution superimposed images from photopolymer electrographic master |

| JPH0668977B2 (ja) * | 1989-08-03 | 1994-08-31 | 矢崎総業株式会社 | 圧接端子および圧接端子のハウジングへの誤挿入検出装置 |

| JPH05128588A (ja) * | 1991-05-16 | 1993-05-25 | Canon Inc | 光記録媒体、光記録方法及び再生方法、情報書込み装置及び情報レコードの再生装置 |

| JP2877611B2 (ja) * | 1991-06-07 | 1999-03-31 | 株式会社東芝 | 光半導体装置 |

| US5386139A (en) * | 1992-04-16 | 1995-01-31 | Kabushiki Kaisha Toshiba | Semiconductor light emitting element with improved structure of groove therein |

| JPH0668977A (ja) | 1992-08-13 | 1994-03-11 | Konica Corp | 多色電界発光表示装置 |

| FR2714956B1 (fr) | 1994-01-12 | 1996-04-05 | 3Sa | Dispositif lumineux de signalisation, notamment destiné à assurer un balisage de sécurité. |

| US6273589B1 (en) * | 1999-01-29 | 2001-08-14 | Agilent Technologies, Inc. | Solid state illumination source utilizing dichroic reflectors |

| US7202506B1 (en) * | 1999-11-19 | 2007-04-10 | Cree, Inc. | Multi element, multi color solid state LED/laser |

| US6250775B1 (en) | 1999-12-09 | 2001-06-26 | Marpole International, Inc. | Light-emitting diode display systems and methods with enhanced light intensity |

| JP3486900B2 (ja) * | 2000-02-15 | 2004-01-13 | ソニー株式会社 | 発光装置およびそれを用いた光装置 |

| JP3659407B2 (ja) * | 2001-08-03 | 2005-06-15 | ソニー株式会社 | 発光装置 |

| JP4054631B2 (ja) * | 2001-09-13 | 2008-02-27 | シャープ株式会社 | 半導体発光素子およびその製造方法、ledランプ並びにled表示装置 |

| US6936856B2 (en) * | 2002-01-15 | 2005-08-30 | Osram Opto Semiconductors Gmbh | Multi substrate organic light emitting devices |

| US6853014B2 (en) * | 2002-10-25 | 2005-02-08 | The University Of Connecticut | Optoelectronic circuit employing a heterojunction thyristor device that performs high speed sampling |

| TWI232066B (en) * | 2002-12-25 | 2005-05-01 | Au Optronics Corp | Manufacturing method of organic light emitting diode for reducing reflection of external light |

| TWI257718B (en) * | 2004-03-18 | 2006-07-01 | Phoseon Technology Inc | Direct cooling of LEDs |

| MXPA06011114A (es) * | 2004-03-29 | 2007-01-25 | Articulated Technologies Llc | Hoja luminosa fabricada de rodillo a rodillo y dispositivos encapsulados de circuito semiconductor. |

| KR101097486B1 (ko) * | 2004-06-28 | 2011-12-22 | 엘지디스플레이 주식회사 | 액정표시장치의 백라이트 유닛 |

| US20060034886A1 (en) | 2004-07-23 | 2006-02-16 | Ward Bennett C | Bonded fiber structures for use in controlling fluid flow |

| KR100649019B1 (ko) * | 2004-08-11 | 2006-11-24 | 동부일렉트로닉스 주식회사 | 씨모스 이미지 센서 및 그의 제조 방법 |

| DE102004039897A1 (de) | 2004-08-17 | 2006-03-02 | Schott Ag | Element mit einer Vielzahl von Leuchtdioden |

| WO2006054236A2 (en) * | 2004-11-19 | 2006-05-26 | Koninklijke Philips Electronics N.V. | Composite led modules |

| TWI269420B (en) * | 2005-05-03 | 2006-12-21 | Megica Corp | Stacked chip package and process thereof |

| DE102005055293A1 (de) | 2005-08-05 | 2007-02-15 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung von Halbleiterchips und Dünnfilm-Halbleiterchip |

| JP2007115928A (ja) | 2005-10-20 | 2007-05-10 | Citizen Electronics Co Ltd | 半導体発光装置 |

| DE102007004303A1 (de) | 2006-08-04 | 2008-02-07 | Osram Opto Semiconductors Gmbh | Dünnfilm-Halbleiterbauelement und Bauelement-Verbund |

| PL1947693T3 (pl) | 2007-01-18 | 2015-09-30 | Polytron Tech Inc | Płaska struktura urządzenia oświetleniowego z diodami emitującymi światło |

| DE102007004304A1 (de) | 2007-01-29 | 2008-07-31 | Osram Opto Semiconductors Gmbh | Dünnfilm-Leuchtdioden-Chip und Verfahren zur Herstellung eines Dünnfilm-Leuchtdioden-Chips |

| DE102007017113A1 (de) | 2007-01-31 | 2008-08-07 | Osram Opto Semiconductors Gmbh | Halbleiterbauelement mit einer optisch aktiven Schicht, Anordnung mit einer Vielzahl von optisch aktiven Schichten und Verfahren zur Herstellung eines Halbleiterbauelements |

-

2007

- 2007-09-04 DE DE102007041896A patent/DE102007041896A1/de not_active Withdrawn

-

2008

- 2008-08-29 US US12/675,050 patent/US8384096B2/en active Active

- 2008-08-29 CN CN2008801055803A patent/CN101796638B/zh active Active

- 2008-08-29 JP JP2010523271A patent/JP5431329B2/ja active Active

- 2008-08-29 KR KR1020107007280A patent/KR20100080782A/ko not_active Application Discontinuation

- 2008-08-29 EP EP08801256.2A patent/EP2183779B1/de active Active

- 2008-08-29 WO PCT/DE2008/001449 patent/WO2009030204A2/de active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| US20110101383A1 (en) | 2011-05-05 |

| WO2009030204A2 (de) | 2009-03-12 |

| JP2010538479A (ja) | 2010-12-09 |

| DE102007041896A1 (de) | 2009-03-05 |

| KR20100080782A (ko) | 2010-07-12 |

| EP2183779A2 (de) | 2010-05-12 |

| CN101796638A (zh) | 2010-08-04 |

| WO2009030204A3 (de) | 2009-06-18 |

| EP2183779B1 (de) | 2019-03-27 |

| US8384096B2 (en) | 2013-02-26 |

| CN101796638B (zh) | 2012-07-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5431329B2 (ja) | 半導体構成素子および半導体構成素子の製造方法 | |

| JP7282138B2 (ja) | 表示装置 | |

| US7906793B2 (en) | Solid metal block semiconductor light emitting device mounting substrates | |

| KR101170401B1 (ko) | 복합 발광 다이오드 모듈 | |

| CN105826448B (zh) | 用于制造光电子半导体器件的方法和光电子半导体器件 | |

| JP5379634B2 (ja) | Ledパッケージモジュール | |

| KR100819883B1 (ko) | 발광소자 패키지 및 그 제조방법 | |

| TWI389328B (zh) | 光電半導體構件及其製造方法 | |

| CN103688378B (zh) | 光学元件、光电子器件和它们的制造方法 | |

| US20150014708A1 (en) | Package for light emitting and receiving devices | |

| US20060124953A1 (en) | Semiconductor light emitting device mounting substrates and packages including cavities and cover plates, and methods of packaging same | |

| JP2011507198A (ja) | オプトエレクトロニクス部品およびその製造方法 | |

| TWI438888B (zh) | 具載體基板與複數發光半導體元件之光電模組及其製造方法 | |

| CN101164170A (zh) | Led封装设计 | |

| JP2012504318A (ja) | Ledモジュールおよびその製造方法 | |

| TWI590486B (zh) | 光電系統 | |

| CN107591394A (zh) | 发光系统 | |

| KR20120079084A (ko) | 방사선 방출면 및 절연 층을 갖는 적어도 하나의 제 1 반도체 몸체를 포함하는 광전자 모듈 그리고 상기 광전자 모듈을 제조하기 위한 방법 | |

| JP2020113799A (ja) | 発光装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20101228 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110527 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121022 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121026 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130121 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130128 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130226 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130603 |

|

| RD13 | Notification of appointment of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7433 Effective date: 20130905 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20130905 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131001 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20131008 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131105 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131204 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5431329 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |