JP5419659B2 - 撮像装置 - Google Patents

撮像装置 Download PDFInfo

- Publication number

- JP5419659B2 JP5419659B2 JP2009276703A JP2009276703A JP5419659B2 JP 5419659 B2 JP5419659 B2 JP 5419659B2 JP 2009276703 A JP2009276703 A JP 2009276703A JP 2009276703 A JP2009276703 A JP 2009276703A JP 5419659 B2 JP5419659 B2 JP 5419659B2

- Authority

- JP

- Japan

- Prior art keywords

- unit

- gain

- pixel

- signal processing

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000003384 imaging method Methods 0.000 title claims description 23

- 238000012545 processing Methods 0.000 claims description 45

- 230000003321 amplification Effects 0.000 claims description 20

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 20

- 238000006243 chemical reaction Methods 0.000 claims description 17

- 230000002194 synthesizing effect Effects 0.000 claims description 15

- 239000011159 matrix material Substances 0.000 claims description 3

- 230000015572 biosynthetic process Effects 0.000 description 11

- 238000000034 method Methods 0.000 description 11

- 238000003786 synthesis reaction Methods 0.000 description 11

- 238000010586 diagram Methods 0.000 description 6

- 238000004891 communication Methods 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 238000013461 design Methods 0.000 description 3

- 229920006395 saturated elastomer Polymers 0.000 description 3

- 238000003705 background correction Methods 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 238000001308 synthesis method Methods 0.000 description 2

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/70—Circuitry for compensating brightness variation in the scene

- H04N23/76—Circuitry for compensating brightness variation in the scene by influencing the image signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Studio Devices (AREA)

Description

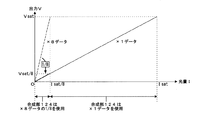

図1は、本発明の第1の実施形態による撮像装置100の構成例を示すブロック図である。光学部110を通って入射した被写体光は、画素部121上に結像される。画素部121は、例えば画素が2次元行列状に配置されており、入射した被写体光が結像されると、各画素により被写体光が電気信号(画素信号)に変換されて画像が撮像される。画素部121の各画素で変換された画像信号は、列増幅部122によって複数のゲインで増幅される。列増幅部122は、複数のゲインに対応する複数の画素信号を出力する。列増幅部122からのゲインの異なる複数の出力が、AD変換部123でアナログデジタル(AD)変換され、さらに合成部124で合成される。合成部124は、入力した画素信号の大きさに応じて、入力した複数の画素信号のうちの1つを選択し、選択した画素信号に基づく信号を出力する。合成の方法については後述する。信号処理部130は、合成部124により選択された画素信号に対応する列増幅部122のゲインに応じて、合成部124により出力された信号に対して、予め決められた方法によって信号処理を行う。そして、信号処理部130で信号処理された画像信号は、記録・通信部140によって記録媒体への記録や外部装置への出力が行われたり、あるいは、再生・表示部150に直接出力されて再生や表示がなされたりする。また、記録・通信部140によって記録媒体に記録された画像信号は、必要に応じて、再生・表示部150に出力されて再生や表示がなされる。

図5は、本発明の第2の実施形態による列合成部1241の動作を表す図である。以下、本実施形態が第1の実施形態と異なる点を説明する。本実施形態の基本的な合成動作は第1の実施形態の場合と同様である。判定閾値とフラグのみが異なる。本実施形態では、12ビットの最大値4095を判定閾値とし、合成後のデータの15ビット中の上位3ビットをフラグとして利用する。元データのゲインが×8倍の場合、上位3ビットは必ず新たに付加された“000”である。また判定閾値はゲインが×8倍の場合で4095であり、これはゲインが×1倍の場合の512に相当する(4095/8)。ゲインが×1倍のデータは左3ビットシフト、つまり8倍されるので、セレクタへの入力は4096以上になる。つまり元データのゲインが×1倍の場合は、上位3ビットは必ず“000”以外となる。以上より、上位ビット(3ビット)をフラグ(ゲインの情報)として用い、後段の信号処理部130は、上位3ビットが“000”以外であれば元データのゲインは×1倍、“000”であれば元データのゲインは×8倍と判断することができる。なお、フラグに用いる‘0’のビットは、データのうちの複数のゲインの倍率差に相当するビット数の上位ビットを用いることが有効である(本実施形態の場合、8倍=3ビット)。また、フラグは、必ずしもデータの上位ビット側に付加する必要はなく、下位ビット側等に付加してもよい。

図6は、本発明の第3の実施形態による列合成部1241の動作を表す図である。以下、本実施形態が第1の実施形態と異なる点を説明する。本実施形態の基本的な合成方法は、第1の実施形態の場合と同様である。本実施形態ではフラグを用いず、全画素データに先立ち、判定閾値を合成部124から信号処理部130に出力する。これにより、信号処理部130では、その後に出てくる各画素データと、判定閾値とを比べることで、画素データが判定閾値以上であれば元データのゲインは×1倍、画素データが判定閾値より小さければ元データのゲインは×8倍と判断できる。すなわち、列合成部1241は、ゲインが×8のデータと判定閾値とを比較し、その比較の結果に応じてセレクタで選択を行う。そして、合成部124は、先立って、判定閾値を信号処理部130に出力する。信号処理部130は、合成部124により出力されたデータ及び判定閾値を比較し、その比較の結果を列増幅部122のゲインの情報として、列増幅部122のゲインに応じて、合成部124により出力されたデータに対して信号処理する。なお、上記では全画素データの前のヘッダ情報として判定閾値を出力するとしたが、出力するタイミングはこの限りではない。また、他の例として、図1のシステムコントロール部170から、タイミング制御部160を介して、合成部124と信号処理部130の両方に判定閾値の情報を出力する方法もある。この方法でも、判定閾値を合成部124と信号処理部130で共有できるので、信号処理部130による元データのゲインの判別が可能となる。また、信号処理部130が合成部124に対して判定閾値を出力して指定する方法もある。

上記の第2の実施形態及び第3の実施形態では、ゲインが×1倍とゲインが×8倍の倍率差が、ぴったり8倍の場合を想定している。実際にはゲインは誤差を持ち、8倍からずれる可能性が大きい。本発明の第4の実施形態は、ゲイン誤差がある場合の解決策を示すものである。本発明の第4の実施形態の説明にも図6を用いる。例えば、列アンプ1221のゲインの×8倍の実際値が、設計値(設定値)に対して±2%ばらつくとする。このときゲインの設計値が×8倍だと、最大で実際値は×8.16倍となる。実際のゲインが×8.16倍のとき、×8倍の方のデータが3690であった場合を考える。判定閾値以上なので、×1倍のデータが採用される。このとき、×1倍のデータは、×8倍のデータの“1/実ゲイン”の出力が、3ビットシフトで8倍されるので、(3690)/(8.16)×8=3618である。これは判定閾値3685よりも小さい。よって後段の信号処理部130は、元データを×8倍データだと判断してしまう。

Claims (10)

- 光電変換により画素信号を生成する一の画素と、

前記一の画素により生成された画素信号に対して複数のゲインで増幅し、前記複数のゲインに対応する複数の画素信号を出力する増幅部と、

前記増幅部により出力された画素信号の大きさに応じて、前記増幅部により出力された複数の画素信号のうちの1つを選択し、前記選択した画素信号に基づく信号を出力する合成部と、

前記合成部により選択された画素信号に対応する前記増幅部のゲインに応じて、前記合成部により出力された信号に対して信号処理する信号処理部と

を有し、

前記合成部は、前記増幅部により出力された画素信号と閾値とを比較し、前記比較の結果に応じて前記選択を行い、

前記信号処理部は、前記合成部により出力された信号及び前記閾値を比較し、前記比較の結果を前記増幅部のゲインの情報として、前記増幅部のゲインに応じて、前記合成部により出力された信号に対して信号処理することを特徴とする撮像装置。 - 前記合成部は、前記選択した画素信号に基づく信号に前記増幅部のゲインの情報を付加して前記信号処理部に出力することを特徴とする請求項1記載の撮像装置。

- 前記信号処理部は、前記合成部により出力された信号に含まれる前記増幅部のゲインの情報に応じて、前記合成部により出力された信号に対して信号処理することを特徴とする請求項1記載の撮像装置。

- 前記増幅部のゲインの情報は、前記合成部により出力された信号のうちの前記複数のゲインの倍率差に相当するビット数であることを特徴とする請求項3記載の撮像装置。

- 前記合成部は、前記閾値を前記信号処理部に出力することを特徴とする請求項1記載の撮像装置。

- 前記信号処理部は、前記閾値を前記合成部に出力することを特徴とする請求項1記載の撮像装置。

- さらに、前記閾値を前記合成部及び前記信号処理部に出力するコントロール部を有することを特徴とする請求項1記載の撮像装置。

- 前記増幅部の2つのゲインの設定値ai及びbiに対し、前記2つのゲインの実際値がar及びbrである場合、ai>biであるとき、ar<br×ai/biの関係が成立することを特徴とする請求項3〜7のいずれか1項に記載の撮像装置。

- 前記画素が行列状に複数設けられ、

前記増幅部が前記画素の各列に対応して複数設けられ、

さらに、前記複数の増幅部に対応して設けられ、前記複数の増幅部により出力される画素信号をアナログデジタル変換する複数のアナログデジタル変換部を有することを特徴とする請求項1〜8のいずれか1項に記載の撮像装置。 - 前記合成部は、前記増幅部により出力された複数の画素信号が同じゲインの信号になるようにビットシフトにより正規化し、前記正規化された複数の画素信号のうちの1つを選択して出力することを特徴とする請求項1〜9のいずれか1項に記載の撮像装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009276703A JP5419659B2 (ja) | 2009-12-04 | 2009-12-04 | 撮像装置 |

| US12/941,603 US8614748B2 (en) | 2009-12-04 | 2010-11-08 | Imaging apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009276703A JP5419659B2 (ja) | 2009-12-04 | 2009-12-04 | 撮像装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011120087A JP2011120087A (ja) | 2011-06-16 |

| JP2011120087A5 JP2011120087A5 (ja) | 2013-01-10 |

| JP5419659B2 true JP5419659B2 (ja) | 2014-02-19 |

Family

ID=44081653

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009276703A Active JP5419659B2 (ja) | 2009-12-04 | 2009-12-04 | 撮像装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8614748B2 (ja) |

| JP (1) | JP5419659B2 (ja) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5610961B2 (ja) | 2010-09-30 | 2014-10-22 | キヤノン株式会社 | 固体撮像装置及び固体撮像装置の駆動方法 |

| JP5862126B2 (ja) * | 2011-09-06 | 2016-02-16 | ソニー株式会社 | 撮像素子および方法、並びに、撮像装置 |

| JP2015039086A (ja) * | 2011-12-16 | 2015-02-26 | パナソニック株式会社 | 固体撮像装置、撮像装置 |

| US9531961B2 (en) | 2015-05-01 | 2016-12-27 | Duelight Llc | Systems and methods for generating a digital image using separate color and intensity data |

| US9918017B2 (en) | 2012-09-04 | 2018-03-13 | Duelight Llc | Image sensor apparatus and method for obtaining multiple exposures with zero interframe time |

| US9167169B1 (en) * | 2014-11-05 | 2015-10-20 | Duelight Llc | Image sensor apparatus and method for simultaneously capturing multiple images |

| US8976264B2 (en) | 2012-09-04 | 2015-03-10 | Duelight Llc | Color balance in digital photography |

| US9167174B1 (en) | 2014-11-05 | 2015-10-20 | Duelight Llc | Systems and methods for high-dynamic range images |

| US9179062B1 (en) | 2014-11-06 | 2015-11-03 | Duelight Llc | Systems and methods for performing operations on pixel data |

| US9179085B1 (en) * | 2014-11-06 | 2015-11-03 | Duelight Llc | Image sensor apparatus and method for obtaining low-noise, high-speed captures of a photographic scene |

| US9154708B1 (en) * | 2014-11-06 | 2015-10-06 | Duelight Llc | Image sensor apparatus and method for simultaneously capturing flash and ambient illuminated images |

| US9160936B1 (en) | 2014-11-07 | 2015-10-13 | Duelight Llc | Systems and methods for generating a high-dynamic range (HDR) pixel stream |

| US9137455B1 (en) | 2014-11-05 | 2015-09-15 | Duelight Llc | Image sensor apparatus and method for obtaining multiple exposures with zero interframe time |

| JP6097574B2 (ja) * | 2013-01-25 | 2017-03-15 | キヤノン株式会社 | 撮像装置、その駆動方法、及び撮像システム |

| US9819849B1 (en) | 2016-07-01 | 2017-11-14 | Duelight Llc | Systems and methods for capturing digital images |

| US9807322B2 (en) | 2013-03-15 | 2017-10-31 | Duelight Llc | Systems and methods for a digital image sensor |

| US10558848B2 (en) | 2017-10-05 | 2020-02-11 | Duelight Llc | System, method, and computer program for capturing an image with correct skin tone exposure |

| US10924688B2 (en) | 2014-11-06 | 2021-02-16 | Duelight Llc | Image sensor apparatus and method for obtaining low-noise, high-speed captures of a photographic scene |

| US11463630B2 (en) | 2014-11-07 | 2022-10-04 | Duelight Llc | Systems and methods for generating a high-dynamic range (HDR) pixel stream |

| CN109792478B (zh) | 2016-09-01 | 2021-11-12 | 迪尤莱特公司 | 基于焦点目标信息调整焦点的装置和方法 |

| WO2018198691A1 (ja) | 2017-04-25 | 2018-11-01 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子、撮像装置、および、固体撮像素子の制御方法 |

| JP2018186478A (ja) | 2017-04-25 | 2018-11-22 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子、撮像装置、および、固体撮像素子の制御方法 |

| US11284017B2 (en) * | 2020-03-24 | 2022-03-22 | Canon Kabushiki Kaisha | Image pickup device and storage medium |

| JP2022117079A (ja) * | 2021-01-29 | 2022-08-10 | キヤノン株式会社 | 画像処理装置、画像処理方法及びプログラム |

| WO2024162221A1 (ja) * | 2023-01-31 | 2024-08-08 | ヌヴォトンテクノロジージャパン株式会社 | 固体撮像装置および撮像装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0795856B2 (ja) * | 1992-04-16 | 1995-10-11 | 三洋電機株式会社 | ディジタルビデオカメラ |

| US5663562A (en) * | 1995-09-06 | 1997-09-02 | Hughes Electronics | Thermal imaging device |

| US6137533A (en) * | 1997-05-14 | 2000-10-24 | Cirrus Logic, Inc. | System and method for enhancing dynamic range in images |

| US6707492B1 (en) * | 1999-03-31 | 2004-03-16 | Cirrus Logic, Inc. | Successive approximation calibration apparatus, system, and method for dynamic range extender |

| JP2001054013A (ja) * | 1999-08-13 | 2001-02-23 | Fuji Photo Film Co Ltd | 撮像信号処理装置およびその処理方法 |

| JP3872333B2 (ja) * | 2001-12-07 | 2007-01-24 | 浜松ホトニクス株式会社 | 物体表面形状計測装置 |

| JP4022862B2 (ja) | 2002-06-11 | 2007-12-19 | ソニー株式会社 | 固体撮像装置及びその制御方法 |

| JP4311181B2 (ja) | 2003-12-05 | 2009-08-12 | ソニー株式会社 | 半導体装置の制御方法および信号処理方法並びに半導体装置および電子機器 |

| JP4861015B2 (ja) * | 2006-01-13 | 2012-01-25 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| JP2008060708A (ja) * | 2006-08-29 | 2008-03-13 | Matsushita Electric Ind Co Ltd | 固体撮像装置及びこれを用いた撮像装置 |

| US8115841B2 (en) * | 2007-03-13 | 2012-02-14 | Micron Technology, Inc. | Method, apparatus and system providing an image sensor having pixels with multiple exposures, diodes and gain readouts |

| US7825975B2 (en) * | 2008-02-25 | 2010-11-02 | Fairchild Imaging, Inc. | Imaging array with improved dynamic range |

| US8339474B2 (en) * | 2008-08-20 | 2012-12-25 | Freescale Semiconductor, Inc. | Gain controlled threshold in denoising filter for image signal processing |

-

2009

- 2009-12-04 JP JP2009276703A patent/JP5419659B2/ja active Active

-

2010

- 2010-11-08 US US12/941,603 patent/US8614748B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8614748B2 (en) | 2013-12-24 |

| JP2011120087A (ja) | 2011-06-16 |

| US20110134267A1 (en) | 2011-06-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5419659B2 (ja) | 撮像装置 | |

| JP4587184B2 (ja) | 固体撮像装置及び固体撮像装置の駆動方法 | |

| JP4500862B2 (ja) | 固体撮像装置の駆動方法 | |

| JP5188292B2 (ja) | 撮像システムおよび撮像システムの駆動方法 | |

| JP5074297B2 (ja) | 固体撮像装置およびその駆動方法、並びに電子情報機器 | |

| JP5456971B2 (ja) | 列バッファ、cmos画像センサ及びデジタルビデオカメラ | |

| JP5085140B2 (ja) | 固体撮像装置 | |

| JP5123601B2 (ja) | 光電変換装置 | |

| JP6351288B2 (ja) | 固体撮像装置及び撮像システム | |

| JP4759293B2 (ja) | 撮像素子 | |

| JP2015128253A (ja) | 固体撮像装置およびその駆動方法 | |

| JP2006311240A (ja) | 撮像装置 | |

| JP2011120094A5 (ja) | ||

| JP6541324B2 (ja) | 固体撮像装置及びその駆動方法、並びに、撮像システム | |

| JP5446717B2 (ja) | 撮像装置 | |

| JP4693863B2 (ja) | 固体撮像装置及び固体撮像装置の駆動方法 | |

| JP4192900B2 (ja) | 量子化精度再生方法、量子化精度再生装置、撮像装置、情報処理装置及びプログラム | |

| JP4478723B2 (ja) | 固体撮像装置及び固体撮像装置の駆動方法 | |

| US20090262210A1 (en) | Solid-state imaging apparatus, imaging system, and method of driving solid-state imaging apparatus | |

| JP2008072188A (ja) | 固体撮像装置 | |

| JP2014103559A (ja) | 画像処理装置及び画像処理方法 | |

| JP5518217B2 (ja) | 撮像システムおよび撮像システムの駆動方法 | |

| JP2007202044A (ja) | 撮像装置 | |

| JP6160139B2 (ja) | 撮像装置及び方法 | |

| JP5033700B2 (ja) | 撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121120 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121120 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130416 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130423 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130620 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131022 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131119 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5419659 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |