JP5259382B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP5259382B2 JP5259382B2 JP2008333972A JP2008333972A JP5259382B2 JP 5259382 B2 JP5259382 B2 JP 5259382B2 JP 2008333972 A JP2008333972 A JP 2008333972A JP 2008333972 A JP2008333972 A JP 2008333972A JP 5259382 B2 JP5259382 B2 JP 5259382B2

- Authority

- JP

- Japan

- Prior art keywords

- replica

- circuit

- input

- gate

- timing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/02—Arrangements for writing information into, or reading information out from, a digital store with means for avoiding parasitic signals

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/227—Timing of memory operations based on dummy memory elements or replica circuits

Landscapes

- Dram (AREA)

- Static Random-Access Memory (AREA)

Description

特開平9−259589号公報

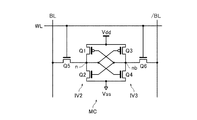

図1は、本発明の第1の実施形態に係る半導体記憶装置の概略図である。

図8は、本発明の第2の実施形態に係る半導体記憶装置のタイミング発生回路200である。

図9は、本発明の第3の実施形態に係る半導体記憶装置のタイミング発生回路300の回路図である。

以上、発明の実施の形態としてSRAMを取り上げ説明したが、本発明はSRAMに限定されるものではなく、DRAM、フラッシュメモリ等あらゆる半導体記憶装置に適用することができる。

Claims (4)

- 複数のワード線、前記ワード線に交差する複数のビット線、前記ワード線及び前記ビット線の各交差部に設けられた複数のメモリセルからなるメモリセルアレイと、

前記ビット線の信号レベルを検知・増幅する複数のセンスアンプ回路と、

レプリカワード線、前記レプリカワード線に交差するレプリカビット線、前記レプリカワード線及びレプリカビット線の各交差部に設けられたレプリカメモリセルからなり、前記メモリセルの読み出し動作を模擬するレプリカ回路と、

基準タイミングから前記レプリカビット線が変化するまでの時間であるレプリカ遅延時間を量子化し、その結果に基づいて、前記センスアンプ回路の活性化タイミングを生成するタイミング発生回路と

を有し、

前記タイミング発生回路は、

所定数のゲートからなる単位回路(ステージ)を複数接続してなる往路回路を備え、

前記基本タイミングが前記複数のステージを順次伝搬されるタイミングと、前記レプリカビット線が変化するタイミングとを比較し、前記ステージ毎に生じる遅延時間単位で前記レプリカ遅延時間を量子化する

ことを特徴とする半導体記憶装置。 - 複数のワード線、前記ワード線に交差する複数のビット線、前記ワード線及び前記ビット線の各交差部に設けられた複数のメモリセルからなるメモリセルアレイと、

前記ビット線の信号レベルを検知・増幅する複数のセンスアンプ回路と、

レプリカワード線、前記レプリカワード線に交差するレプリカビット線、前記レプリカワード線及びレプリカビット線の各交差部に設けられたレプリカメモリセルからなり、前記メモリセルの読み出し動作を模擬するレプリカ回路と、

基準タイミングから前記レプリカビット線が変化するまでの時間であるレプリカ遅延時間を量子化し、その結果に基づいて、前記センスアンプ回路の活性化タイミングを生成するタイミング発生回路と

を有し、

前記タイミング発生回路は、

前記基準タイミングを入力する縦続接続された第1及び第2のゲート、並びに、前記第2のゲートの出力が第1の入力端に入力され、前記レプリカビット線が変化するタイミングが第2の入力端に入力される第3のゲートを備えた第1の単位回路(ステージ)を複数縦続接続してなる往路回路と、

縦続接続された第4及び第5のゲートを備えた第2の単位回路(ステージ)を有し、前記第2の単位回路は、前記第1の単位回路と対応させて複数縦続接続され、前記第4のゲートの第1の入力端に前記第3のゲートの出力が入力され、前記第4のゲートの第2の入力端に前段の前記第2の単位回路の出力が入力され、最終段の前記第2の単位回路の出力の変化から、前記センスアンプ回路の活性化タイミングを生成する復路回路と

を有する

ことを特徴とする半導体記憶装置。 - 複数のワード線、前記ワード線に交差する複数のビット線、前記ワード線及び前記ビット線の各交差部に設けられた複数のメモリセルからなるメモリセルアレイと、

前記ビット線の信号レベルを検知・増幅する複数のセンスアンプ回路と、

レプリカワード線、前記レプリカワード線に交差するレプリカビット線、前記レプリカワード線及びレプリカビット線の各交差部に設けられたレプリカメモリセルからなり、前記メモリセルの読み出し動作を模擬するレプリカ回路と、

基準タイミングから前記レプリカビット線が変化するまでの時間であるレプリカ遅延時間を量子化し、その結果に基づいて、前記センスアンプ回路の活性化タイミングを生成するタイミング発生回路と

を有し、

前記タイミング発生回路は、

前記基準タイミングを入力する縦続接続された第1及び第2のゲート、並びに、前記第2のゲートの出力が第1の入力端に入力され、前記レプリカビット線が変化するタイミングが第2の入力端に入力される第3のゲートを備えた第1の単位回路(ステージ)を複数縦続接続してなる往路回路と、

縦続接続された第4乃至第7のゲートを備えた第2の単位回路(ステージ)を有し、前記第2の単位回路は、前記第1の単位回路と対応させて複数縦続接続され、前記第4のゲートの第1の入力端に前記第3のゲートの出力が入力され、前記第4のゲートの第2の入力端に前段の前記第2の単位回路の出力が入力され、最終段の前記第2の単位回路の出力の変化から、前記センスアンプ回路の活性化タイミングを生成する復路回路と

を有する

ことを特徴とする半導体記憶装置。 - 複数のワード線、前記ワード線に交差する複数のビット線、前記ワード線及び前記ビット線の各交差部に設けられた複数のメモリセルからなるメモリセルアレイと、

前記ビット線の信号レベルを検知・増幅する複数のセンスアンプ回路と、

レプリカワード線、前記レプリカワード線に交差するレプリカビット線、前記レプリカワード線及びレプリカビット線の各交差部に設けられたレプリカメモリセルからなり、前記メモリセルの読み出し動作を模擬するレプリカ回路と、

基準タイミングから前記レプリカビット線が変化するまでの時間であるレプリカ遅延時間を量子化し、その結果に基づいて、前記センスアンプ回路の活性化タイミングを生成するタイミング発生回路と

を有し、

前記タイミング発生回路は、

前記基準タイミングが入力される第1のゲート、この第1のゲートの出力が第1の入力端に入力され、前記レプリカビット線が変化するタイミングが第2の入力端に入力される第2のゲートを備えた第1の単位回路(ステージ)、並びに、前記第1の単位回路の出力が入力される第3のゲート、この第3のゲートの出力が第1の入力端に入力され、前記レプリカビット線が変化するタイミングを逆論理にした信号が第2の入力端に入力される第4のゲートを備えた第2の単位回路(ステージ)を交互に複数縦続接続してなる往路回路と、

前記第1のゲートに対応する第5のゲートを備えた第3の単位回路(ステージ)、並びに、前記第3のゲートに対応する第6のゲートを備えた第4の単位回路(ステージ)が前記第1及び第2の単位回路に対応させて交互に複数縦続接続され、前記第5のゲートの第1の入力端に前記第2のゲートの出力が入力され、前記第5の第2の入力端に前段の前記第4の単位回路の出力が入力され、前記第6のゲートの第1の入力端に前記第4のゲートの出力が入力され、前記第6のゲートの第2の入力端に前段の前記第3の単位回路の出力が入力され、最終段の第4の単位回路の出力の変化から、前記センスアンプ回路の活性化タイミングを生成する復路回路と

を有する

ことを特徴とする半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008333972A JP5259382B2 (ja) | 2008-12-26 | 2008-12-26 | 半導体記憶装置 |

| US12/643,925 US8111571B2 (en) | 2008-12-26 | 2009-12-21 | Semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008333972A JP5259382B2 (ja) | 2008-12-26 | 2008-12-26 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010157279A JP2010157279A (ja) | 2010-07-15 |

| JP5259382B2 true JP5259382B2 (ja) | 2013-08-07 |

Family

ID=42284805

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008333972A Expired - Fee Related JP5259382B2 (ja) | 2008-12-26 | 2008-12-26 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8111571B2 (ja) |

| JP (1) | JP5259382B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5404584B2 (ja) | 2010-11-19 | 2014-02-05 | 株式会社東芝 | 半導体記憶装置 |

| JP5917219B2 (ja) | 2012-03-21 | 2016-05-11 | 株式会社東芝 | 半導体記憶装置 |

| US9318190B1 (en) | 2014-09-30 | 2016-04-19 | Taiwan Semiconductor Manufacturing Co., Ltd. | Memory device |

| CN112542185B (zh) * | 2019-09-20 | 2024-05-14 | 长鑫存储技术有限公司 | 灵敏放大器及其控制方法、存储器读写电路以及存储器 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3542225B2 (ja) | 1996-03-19 | 2004-07-14 | 株式会社日立製作所 | 半導体装置 |

| JPH09282889A (ja) * | 1996-04-09 | 1997-10-31 | Toshiba Corp | 半導体装置 |

| JPH11203877A (ja) * | 1998-01-19 | 1999-07-30 | Hitachi Ltd | 半導体集積回路及びその設計方法 |

| JP2002216481A (ja) * | 2001-01-19 | 2002-08-02 | Hitachi Ltd | 半導体集積回路装置 |

| JP3699920B2 (ja) * | 2001-10-25 | 2005-09-28 | 株式会社東芝 | 遅延回路および同期型遅延装置 |

| JP2004022070A (ja) * | 2002-06-17 | 2004-01-22 | Renesas Technology Corp | 半導体記憶装置 |

| US7042776B2 (en) * | 2004-02-18 | 2006-05-09 | International Business Machines Corporation | Method and circuit for dynamic read margin control of a memory array |

| US7061793B2 (en) * | 2004-03-19 | 2006-06-13 | International Business Machines Corporation | Apparatus and method for small signal sensing in an SRAM cell utilizing PFET access devices |

-

2008

- 2008-12-26 JP JP2008333972A patent/JP5259382B2/ja not_active Expired - Fee Related

-

2009

- 2009-12-21 US US12/643,925 patent/US8111571B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8111571B2 (en) | 2012-02-07 |

| JP2010157279A (ja) | 2010-07-15 |

| US20100165771A1 (en) | 2010-07-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102408572B1 (ko) | 반도체 메모리 장치 | |

| CN102150213B (zh) | 用于优化存储器读出放大器时序的电路和方法 | |

| KR102424285B1 (ko) | 멀티 레벨 센싱 회로 및 이를 포함하는 반도체 장치 | |

| JP5478772B2 (ja) | 安定性が改善されビットセルサイズが縮小された低出力5tsram | |

| CN110660419B (zh) | 存储电路及操作该电路的方法 | |

| US8208336B2 (en) | Fuse circuit and semiconductor device having the same | |

| US8116119B1 (en) | Desensitizing static random access memory (SRAM) to process variations | |

| CN101667452A (zh) | 半导体器件 | |

| CN110890119B (zh) | 电压产生电路、存储器装置和产生位线预充电电压的方法 | |

| JP4960419B2 (ja) | 半導体記憶装置及び半導体装置 | |

| KR102532606B1 (ko) | 뉴럴 네트워크를 구현하기 위한 전자 장치 | |

| US9099168B2 (en) | Method for extending word-line pulses | |

| JP4090967B2 (ja) | 半導体記憶装置 | |

| JP5259382B2 (ja) | 半導体記憶装置 | |

| US9431094B1 (en) | Input buffer | |

| US20190172507A1 (en) | Apparatuses and methods for providing bias signals in a semiconductor device | |

| US9001613B2 (en) | Tracking mechanisms | |

| US6707741B1 (en) | Current steering reduced bitline voltage swing, sense amplifier | |

| JP5404584B2 (ja) | 半導体記憶装置 | |

| US8619478B2 (en) | System and method for generating a clock | |

| US10373655B2 (en) | Apparatuses and methods for providing bias signals according to operation modes as supply voltages vary in a semiconductor device | |

| KR100884761B1 (ko) | 센스 엠프 인에이블 신호 발생 회로, 이를 가지는 메모리장치 및 센스 엠프 인에이블 신호 발생 방법 | |

| KR102815077B1 (ko) | Sram의 전력 소모를 저감시키기 위한 펄스 신호 생성기 및 이를 구비하는 sram | |

| KR100771545B1 (ko) | 센스앰프 제어신호 생성회로 | |

| TWI869917B (zh) | 記憶體裝置、感測放大器系統以及記憶體陣列操作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110314 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121010 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121023 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121212 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20130221 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |