JP5167022B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5167022B2 JP5167022B2 JP2008204141A JP2008204141A JP5167022B2 JP 5167022 B2 JP5167022 B2 JP 5167022B2 JP 2008204141 A JP2008204141 A JP 2008204141A JP 2008204141 A JP2008204141 A JP 2008204141A JP 5167022 B2 JP5167022 B2 JP 5167022B2

- Authority

- JP

- Japan

- Prior art keywords

- sealing body

- metal substrate

- substrate

- metal

- molding die

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

- Lead Frames For Integrated Circuits (AREA)

Description

(a)金属板と、前記金属板の片面に形成されたリードとからなる金属基板を用意する工程と、

(b)前記リード上に半導体チップを搭載し、前記半導体チップと前記リードとを電気的に接続する工程と、

(c)前記(b)工程の後、前記金属基板を成形金型に装着し、前記成形金型のキャビティ内に溶融した樹脂を流し込み、前記樹脂に熱を加えることによって、前記リード、および前記半導体チップを覆う第1封止体と、前記成形金型のカル、ランナおよびゲートに位置し、前記第1封止体と一体の第2封止体とを形成する工程と、

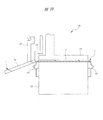

(d)前記第1および第2封止体が形成された前記金属基板を前記成形金型から取り出した後、前記金属基板の裏面がゲートブレーク装置の基板ステージの上面と接触するように、前記金属基板を前記基板ステージ上に位置決めし、前記金属基板を前記基板ステージに密着させる工程と、

(e)前記(d)工程の後、前記第2封止体に荷重を印加することによって、前記第2封止体を前記第1封止体から分離・除去する工程と、

(f)前記(e)工程の後、前記第1封止体から前記金属板を剥離する工程と、

(g)前記(f)工程の後、前記第1封止体をダイシングすることによって、半導体パッケージを得る工程と、

を含み、

前記(d)工程において、前記第1および第2封止体が形成された前記金属基板を前記成形金型から取り出した後、前記金属基板を前記基板ステージに密着させる工程に先だって、前記金属基板を前記基板ステージと非接触の状態に保ちながら、前記金属基板を室温雰囲気中で徐冷する工程をさらに含み、

前記基板ステージは、複数の支持部材を備えており、前記(d)工程において、前記成形金型から取り出した前記金属基板を前記複数の支持部材で支持することによって、前記金属基板を前記基板ステージと非接触の状態に保つものである。

1a デバイス領域

2 リード

2a 吊りリード

3 ダイパッド部

4 半導体チップ

5 ボンディングパッド

6 Auワイヤ

7 封止体

7a 樹脂

8 金属板

10 ゲートブレーク装置

11 基板ステージ

12 封止体押さえ板

13 基板押さえ板

14 樹脂突き落とし板

15 弾性支持部材

17 ダイシングテープ

18 ダイシングブレード

20 SON

Claims (6)

- (a)金属板と、前記金属板の片面に形成されたリードとからなる金属基板を用意する工程と、

(b)前記リード上に半導体チップを搭載し、前記半導体チップと前記リードとを電気的に接続する工程と、

(c)前記(b)工程の後、前記金属基板を成形金型に装着し、前記成形金型のキャビティ内に溶融した樹脂を流し込み、前記樹脂に熱を加えることによって、前記リード、および前記半導体チップを覆う第1封止体と、前記成形金型のカル、ランナおよびゲートに位置し、前記第1封止体と一体の第2封止体とを形成する工程と、

(d)前記第1および第2封止体が形成された前記金属基板を前記成形金型から取り出した後、前記金属基板の裏面がゲートブレーク装置の基板ステージの上面と接触するように、前記金属基板を前記基板ステージ上に位置決めし、前記金属基板を前記基板ステージに密着させる工程と、

(e)前記(d)工程の後、前記第2封止体に荷重を印加することによって、前記第2封止体を前記第1封止体から分離・除去する工程と、

(f)前記(e)工程の後、前記第1封止体から前記金属板を剥離する工程と、

(g)前記(f)工程の後、前記第1封止体をダイシングすることによって、半導体パッケージを得る工程と、

を含む半導体装置の製造方法であって、

前記(d)工程において、前記第1および第2封止体が形成された前記金属基板を前記成形金型から取り出した後、前記金属基板を前記基板ステージに密着させる工程に先だって、前記金属基板を前記基板ステージと非接触の状態に保ちながら、前記金属基板を室温雰囲気中で徐冷する工程をさらに含み、

前記基板ステージは、複数の支持部材を備えており、前記(d)工程において、前記成形金型から取り出した前記金属基板を前記複数の支持部材で支持することによって、前記金属基板を前記基板ステージと非接触の状態に保つことを特徴とする半導体装置の製造方法。 - 前記基板ステージは、金属からなることを特徴とする請求項1記載の半導体装置の製造方法。

- 前記支持部材は、板バネ、コイル状の押しバネ、トーションバネ、またはゴム状弾性体で構成されていることを特徴とする請求項1記載の半導体装置の製造方法。

- 前記(d)工程において、前記金属基板を前記成形金型から取り出してから、前記金属基板の徐冷が完了するまでの時間は、20秒以上であることを特徴とする請求項1記載の半導体装置の製造方法。

- 前記リードは、電鋳加工法によって前記金属板の片面に形成された電着層からなることを特徴とする請求項1記載の半導体装置の製造方法。

- 前記金属板は、ステンレスからなることを特徴とする請求項1記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008204141A JP5167022B2 (ja) | 2008-08-07 | 2008-08-07 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008204141A JP5167022B2 (ja) | 2008-08-07 | 2008-08-07 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010040911A JP2010040911A (ja) | 2010-02-18 |

| JP2010040911A5 JP2010040911A5 (ja) | 2011-09-15 |

| JP5167022B2 true JP5167022B2 (ja) | 2013-03-21 |

Family

ID=42013110

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008204141A Expired - Fee Related JP5167022B2 (ja) | 2008-08-07 | 2008-08-07 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5167022B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105280567B (zh) | 2014-06-19 | 2018-12-28 | 株式会社吉帝伟士 | 半导体封装件及其制造方法 |

| JP6457206B2 (ja) | 2014-06-19 | 2019-01-23 | 株式会社ジェイデバイス | 半導体パッケージ及びその製造方法 |

| JP6466252B2 (ja) | 2014-06-19 | 2019-02-06 | 株式会社ジェイデバイス | 半導体パッケージ及びその製造方法 |

| JP6304435B1 (ja) * | 2017-07-25 | 2018-04-04 | 第一精工株式会社 | 基材の変形止め機構及び基材の変形止め方法 |

| CN117939794B (zh) * | 2024-03-20 | 2024-05-28 | 大连保税区金宝至电子有限公司 | 一种分布式外引脚覆铜陶瓷基板的加工方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62124747A (ja) * | 1985-11-25 | 1987-06-06 | Sharp Corp | 自動モ−ルド装置に於けるカルブレイク方法 |

| JP2000299329A (ja) * | 1999-04-12 | 2000-10-24 | Mitsubishi Electric Corp | 樹脂パッケージ型半導体装置の製造装置及び製造方法 |

| JP4106844B2 (ja) * | 2000-02-22 | 2008-06-25 | 沖電気工業株式会社 | 樹脂封止半導体装置のリード部のゲートブレーク方法 |

| JP2002016181A (ja) * | 2000-04-25 | 2002-01-18 | Torex Semiconductor Ltd | 半導体装置、その製造方法、及び電着フレーム |

| JP2004214265A (ja) * | 2002-12-27 | 2004-07-29 | Kyushu Hitachi Maxell Ltd | 半導体装置および半導体装置の製造方法 |

| JP2006269486A (ja) * | 2005-03-22 | 2006-10-05 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2006351835A (ja) * | 2005-06-16 | 2006-12-28 | Aoi Electronics Co Ltd | 半導体装置および半導体装置の製造方法 |

-

2008

- 2008-08-07 JP JP2008204141A patent/JP5167022B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010040911A (ja) | 2010-02-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7164210B2 (en) | Semiconductor package with heat sink and method for fabricating same | |

| US7968982B2 (en) | Thermal enhanced upper and dual heat sink exposed molded leadless package | |

| US6838315B2 (en) | Semiconductor device manufacturing method wherein electrode members are exposed from a mounting surface of a resin encapsulator | |

| KR100551641B1 (ko) | 반도체 장치의 제조 방법 및 반도체 장치 | |

| US10008472B2 (en) | Method for making semiconductor device with sidewall recess and related devices | |

| JP5167022B2 (ja) | 半導体装置の製造方法 | |

| US6613607B2 (en) | Method for manufacturing encapsulated electronic components, particularly integrated circuits | |

| US20090039506A1 (en) | Semiconductor device including a semiconductor chip which is mounted spaning a plurality of wiring boards and manufacturing method thereof | |

| JP2004349316A (ja) | 半導体装置及びその製造方法 | |

| JP2002343817A (ja) | 半導体装置ユニット | |

| CN211125635U (zh) | 半导体设备和电子设备 | |

| JP2007311577A (ja) | 半導体装置 | |

| JP2011040640A (ja) | 半導体装置の製造方法 | |

| JP2002254481A (ja) | 樹脂モールド金型及び樹脂モールドパッケージの製造方法 | |

| JP2017183417A (ja) | 半導体装置 | |

| KR100648509B1 (ko) | 테이프형 리드 프레임 스트립과 이를 이용한 리드 노출형반도체 칩 패키지 및 제조 방법 | |

| KR102340866B1 (ko) | 반도체 패키지 및 그 제조 방법 | |

| JP2011014606A (ja) | 半導体装置の製造方法 | |

| JP2007081232A (ja) | 半導体装置の製造方法 | |

| TWI385773B (zh) | Lead frame carrier and method of manufacturing the same | |

| JPH08125051A (ja) | 半導体装置 | |

| JP4451874B2 (ja) | 半導体装置の製造方法 | |

| JP2013165304A (ja) | 半導体装置の製造方法 | |

| KR100251866B1 (ko) | 반도체 패키지의 마킹방법 | |

| JP2006351908A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110802 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110802 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120829 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120904 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121031 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121221 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |