JP5039368B2 - 半導体記憶装置、その製造方法及びその駆動方法 - Google Patents

半導体記憶装置、その製造方法及びその駆動方法 Download PDFInfo

- Publication number

- JP5039368B2 JP5039368B2 JP2006325510A JP2006325510A JP5039368B2 JP 5039368 B2 JP5039368 B2 JP 5039368B2 JP 2006325510 A JP2006325510 A JP 2006325510A JP 2006325510 A JP2006325510 A JP 2006325510A JP 5039368 B2 JP5039368 B2 JP 5039368B2

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- region

- diffusion layer

- type well

- type diffusion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 281

- 238000000034 method Methods 0.000 title claims description 98

- 238000004519 manufacturing process Methods 0.000 title claims description 90

- 238000009792 diffusion process Methods 0.000 claims description 316

- 239000000758 substrate Substances 0.000 claims description 76

- 230000001681 protective effect Effects 0.000 claims description 75

- 238000003860 storage Methods 0.000 claims description 45

- 229910021332 silicide Inorganic materials 0.000 claims description 39

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical group [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 39

- 230000008878 coupling Effects 0.000 claims description 28

- 238000010168 coupling process Methods 0.000 claims description 28

- 238000005859 coupling reaction Methods 0.000 claims description 28

- 238000002955 isolation Methods 0.000 claims description 21

- 229910052751 metal Inorganic materials 0.000 claims description 20

- 239000002184 metal Substances 0.000 claims description 20

- 239000003990 capacitor Substances 0.000 claims description 19

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 16

- 239000011159 matrix material Substances 0.000 claims description 16

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 16

- 238000005530 etching Methods 0.000 claims description 10

- 238000000059 patterning Methods 0.000 claims description 10

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 8

- 238000005498 polishing Methods 0.000 claims description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 8

- 239000000126 substance Substances 0.000 claims description 6

- 230000005283 ground state Effects 0.000 claims description 4

- 238000005304 joining Methods 0.000 claims description 3

- 150000004767 nitrides Chemical class 0.000 claims description 2

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 claims 1

- 230000008569 process Effects 0.000 description 37

- 238000001312 dry etching Methods 0.000 description 18

- 238000002347 injection Methods 0.000 description 18

- 239000007924 injection Substances 0.000 description 18

- 230000004048 modification Effects 0.000 description 17

- 238000012986 modification Methods 0.000 description 17

- 230000015572 biosynthetic process Effects 0.000 description 15

- 238000005229 chemical vapour deposition Methods 0.000 description 13

- 230000006870 function Effects 0.000 description 13

- 238000000151 deposition Methods 0.000 description 12

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 12

- 230000015556 catabolic process Effects 0.000 description 11

- 239000012535 impurity Substances 0.000 description 9

- 238000001459 lithography Methods 0.000 description 9

- 239000003870 refractory metal Substances 0.000 description 8

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 4

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- CIWBSHSKHKDKBQ-JLAZNSOCSA-N Ascorbic acid Chemical compound OC[C@H](O)[C@H]1OC(=O)C(O)=C1O CIWBSHSKHKDKBQ-JLAZNSOCSA-N 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 230000003111 delayed effect Effects 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 150000002736 metal compounds Chemical class 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000008685 targeting Effects 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

Images

Landscapes

- Non-Volatile Memory (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

Description

本発明の第1の実施形態について図面を参照しながら説明する。第1の実施形態においては、ゲート絶縁膜に電荷蓄積層を有する不揮発性半導体記憶装置を一例として取り上げる。

以下、本発明の第2の実施形態について図面を参照しながら説明する。

以下、本発明の第3の実施形態について図面を参照しながら説明する。

以下、本発明の第4の実施形態について図面を参照しながら説明する。

以下、本発明の第5の実施形態について図面を参照しながら説明する。

以下、本発明の第6の実施形態について図面を参照しながら説明する。

以下、本発明の第7の実施形態について図面を参照しながら説明する。

以下、本発明の第8の実施形態について図面を参照しながら説明する。

以下、本発明の第9の実施形態について図面を参照しながら説明する。

まず、書き込み動作について説明する。

次に、消去動作について説明する。

次に、読み出し動作について説明する。

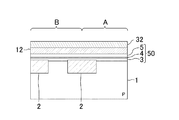

2 素子分離絶縁膜

3 第1ゲート絶縁膜

4 電荷蓄積層

5 第2ゲート絶縁膜

6 ソースドレイン拡散層

9 N型拡散層

12 第1導電層

13 第2導電層(ワード線)

14 N型半導体基板

15 N型ウェル

16 P型拡散層

17 深いN型ウェル

18 N型拡散層

19A 第1のシリサイド領域

19B 第2のシリサイド領域

20 レジスト

21 絶縁膜

31 第3ゲート絶縁膜

32 ゲート電極加工用絶縁膜

33 ソースドレイン拡散層上絶縁膜(絶縁膜)

34 第1のレジストパターン

35 第2のレジストパターン

36 トンネル酸化膜(トンネル絶縁膜)

37 結合容量絶縁膜

40 N型拡散層

41 P型拡散層

42 第1のレジストパターン

43 第2のレジストパターン

50 ゲート絶縁膜

Claims (29)

- 第1の半導体領域に形成され、複数のメモリセルが行列状に配置されたメモリセルアレイ領域と、

前記複数のメモリセルのうち、同一の行に並ぶメモリセル同士を共通に接続する複数のワード線と、

第2の半導体領域に前記メモリセルアレイ領域と分離して形成された保護ダイオード領域とを備え、

前記保護ダイオード領域には、前記第2の半導体領域の上部に形成された第1の拡散層と前記第2の半導体領域とが接合してなる保護ダイオード素子が構成され、

前記各ワード線は、前記保護ダイオード領域に延伸して前記第1の拡散層と直接に接続されることにより、前記保護ダイオード素子と電気的に接続されており、

前記第1の半導体領域は、第1導電型であり、

前記第2の半導体領域は、第1導電型ウエルを含み、

前記第1の拡散層は、第2導電型であって、且つ前記第1導電型ウエル内に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエルと、該第1導電型ウエルに隣接して形成された第1の第2導電型ウエルと、前記第1導電型ウエルと前記第1の第2導電型ウエルとの上部で且つ接合部を跨ぐように形成された第1の第1導電型拡散層とを有し、

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の第1導電型拡散層及び第1の第2導電型ウエルにより構成されていることを特徴とする半導体記憶装置。 - 前記第1導電型ウエル及び第1の第2導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエル及び第1の第2導電型ウエルを内包し且つ前記第1導電型ウエル及び第1の第2導電型ウエルよりも接合面が深い第2の第2導電型ウエルと、前記第1の第2導電型ウエルと前記半導体基板との上部で且つ接合部を跨ぐように形成された第2の第2導電型拡散層とを有し、

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の第1導電型拡散層、第1の第2導電型ウエル、第2の第2導電型ウエル及び第2の第2導電型拡散層により構成されていることを特徴とする請求項1に記載の半導体記憶装置。 - 前記第1導電型ウエル及び第1の第2導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエル及び第1の第2導電型ウエルを内包し且つ前記第1導電型ウエル及び第1の第2導電型ウエルよりも接合面が深い第2の第2導電型ウエルと、前記第1の第1導電型拡散層の上部に形成された金属による第1のシリサイド領域と、前記第1の第2導電型ウエルと前記半導体基板との上部で且つ接合部を跨ぐように形成された金属による第2のシリサイド領域とを有し、

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の第1導電型拡散層、第1のシリサイド領域、第1の第2導電型ウエル、第2の第2導電型ウエル及び第2のシリサイド領域により構成されていることを特徴とする請求項1に記載の半導体記憶装置。 - 前記第1導電型ウエル及び第1の第2導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエル及び第1の第2導電型ウエルを内包し且つ前記第1導電型ウエル及び第1の第2導電型ウエルよりも接合面が深い第2の第2導電型ウエルと、前記第1の第2導電型ウエルにおける前記第1の第1導電型拡散層と反対側の上部に形成された第2の第2導電型拡散層と、前記半導体基板の上部における前記第2の第2導電型拡散層と隣接して形成された第2の第1導電型拡散層とを有し、

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の第1導電型拡散層、第1の第2導電型ウエル、第2の第2導電型ウエル、第2の第2導電型拡散層及び第2の第1導電型拡散層により構成されていることを特徴とする請求項1に記載の半導体記憶装置。 - 前記第1の第1導電型拡散層の上部には金属による第1のシリサイド領域が形成され、

前記第2の第2導電型拡散層の上部には金属による第2のシリサイド領域が形成されていることを特徴とする請求項2に記載の半導体記憶装置。 - 前記第1の第1導電型拡散層の上部には金属による第1のシリサイド領域が形成され、

前記第2の第2導電型拡散層の上部及び前記第2の第1導電型拡散層の上部に跨るように、金属による第2のシリサイド領域が形成されていることを特徴とする請求項4に記載の半導体記憶装置。 - 前記メモリセルアレイ領域における互いに隣接する前記メモリセル同士の間には絶縁膜が形成され、

前記保護ダイオード領域における前記第1の拡散層の上には前記絶縁膜が形成されていないことを特徴とする請求項1に記載の半導体記憶装置。 - 第1の半導体領域に形成され、複数のメモリセルが行列状に配置されたメモリセルアレイ領域と、

前記複数のメモリセルのうち、同一の行に並ぶメモリセル同士を共通に接続する複数のワード線と、

第2の半導体領域に前記メモリセルアレイ領域と分離して形成された保護ダイオード領域とを備え、

前記保護ダイオード領域には、前記第2の半導体領域の上部に形成された第1の拡散層と前記第2の半導体領域とが接合してなる保護ダイオード素子が構成され、

前記各ワード線は、前記保護ダイオード領域に延伸して前記第1の拡散層と直接に接続されることにより、前記保護ダイオード素子と電気的に接続されており、

前記第1の半導体領域は、第1導電型であり、

前記第2の半導体領域は、第2導電型ウエルを含み、

前記第1の拡散層は、第1導電型であって、且つ前記第2導電型ウエル内に形成されており、

前記保護ダイオード領域は、前記第2導電型ウエルと、該第2導電型ウエルに隣接して形成された第1の第1導電型ウエルと、前記第2導電型ウエルと前記第1の第1導電型ウエルとの上部で且つ接合部を跨ぐように形成された第1の第2導電型拡散層とを有し、

前記保護ダイオード素子は、前記第1の第1導電型拡散層、第2導電型ウエル、第1の第2導電型拡散層及び第1の第1導電型ウエルにより構成されていることを特徴とする半導体記憶装置。 - 前記第2導電型ウエル及び第1の第1導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1の第1導電型ウエルにおける前記第1の第2導電型拡散層と反対側の上部に形成された第2の第1導電型拡散層を有し、

前記保護ダイオード素子は、前記第1の第1導電型拡散層、第2導電型ウエル、第1の第2導電型拡散層、第1の第1導電型ウエル及び第2の第1導電型拡散層により構成されていることを特徴とする請求項8に記載の半導体記憶装置。 - 前記第1の第2導電型拡散層の上部には金属による第1のシリサイド領域が形成され、

前記第2の第1導電型拡散層の上部には金属による第2のシリサイド領域が形成されていることを特徴とする請求項9に記載の半導体記憶装置。 - 前記メモリセルアレイ領域における互いに隣接する前記メモリセル同士の間には絶縁膜が形成され、

前記保護ダイオード領域における前記第1の拡散層の上には前記絶縁膜が形成されていないことを特徴とする請求項8に記載の半導体記憶装置。 - 前記各ワード線は、前記複数のメモリセルにそれぞれ形成された第1の導電層と、前記複数の第1の導電層のうち同一の行に並ぶ第1の導電層同士を共通に接続する第2の導電層とから構成されていることを特徴とする請求項1〜11のいずれか1項に記載の半導体記憶装置。

- 前記各メモリセルは、前記第1の半導体領域と前記各第1の導電層との間に形成され、酸化膜の間に窒化膜が挟まれてなる積層絶縁膜を有するMONOS型メモリセルであることを特徴とする請求項12に記載の半導体記憶装置。

- 前記各ワード線は、前記複数のメモリセルにそれぞれ形成された第1の導電層と、前記複数の第1の導電層のうち同一の行に並ぶ第1の導電層同士を絶縁膜を介在させて容量結合する第2の導電層とから構成されていることを特徴とする請求項1〜11のいずれか1項に記載の半導体記憶装置。

- 前記各メモリセルは、前記第1の半導体領域と前記各第1の導電層との間に形成されたトンネル絶縁膜を有する浮遊ゲート電極型メモリセルであることを特徴とする請求項14に記載の半導体記憶装置。

- 第1導電型の半導体領域の上に、複数のメモリセルを行列状に配置したメモリセルアレイ領域と保護ダイオード領域とを分離して形成する半導体記憶装置の製造方法であって、

前記半導体領域に素子分離絶縁膜を選択的に形成する工程(a)と、

前記素子分離絶縁膜を含む前記半導体領域の上に、第1のシリコン酸化膜、シリコン窒化膜及び第2のシリコン酸化膜からなるONO膜、並びに第1の導電層を順次形成する工程(b)と、

前記メモリセルアレイ領域において、前記第1の導電層及びONO膜を列方向に延びる短冊状にパターニングすると共に、前記保護ダイオード領域において、前記第1の導電層を除去するようにパターニングする工程(c)と、

前記工程(c)よりも後に、パターニングされた前記第1の導電層をマスクとして、前記半導体領域の前記メモリセルアレイ領域においては、第2導電型拡散層からなり前記メモリセルのソースドレイン領域を形成すると共に、前記半導体領域の前記保護ダイオード領域においては、保護ダイオード素子を構成する第2導電型拡散層を形成する工程(d)と、

前記工程(d)よりも後に、パターニングされた前記第1の導電層を含む前記半導体領域の上に絶縁膜を形成した後、前記メモリセルアレイ領域において、パターニングされた前記第1の導電層の上面を露出する工程(e)と、

前記工程(d)よりも後に、前記保護ダイオード領域において、前記第2導電型拡散層の少なくとも一部を露出する工程(f)と、

前記工程(f)よりも後に、前記半導体領域における前記メモリセルアレイ領域及び保護ダイオード領域の上に第2 の導電層を形成する工程(g)と、

前記工程(g)よりも後に、前記メモリセルアレイ領域において、前記第2の導電層及び第1の導電層を行方向にパターニングすることにより、それぞれ前記第1の導電層を含む行列状に配置された複数の前記メモリセルと、前記第2の導電層からなり同一の行に並ぶ複数の前記メモリセルを共通に接続する複数のワード線とを形成すると共に、前記保護ダイオード領域において、前記保護ダイオード素子の第2導電型拡散層と前記ワード線の端部とを直接に接続する工程(h)とを備えていることを特徴とする半導体記憶装置の製造方法。 - 前記工程(e)及び工程(f)は、形成された前記絶縁膜に対してエッチングを行なうことにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出し且つ互いに隣接する前記第1の導電層及びONO膜の間を埋め込むと共に、前記保護ダイオード領域において、前記第2 導電型拡散層の少なくとも一部を露出する工程であることを特徴とする請求項16に記載の半導体記憶装置の製造方法。

- 前記工程(e)は、形成された前記絶縁膜に対して、化学機械研磨法により研磨することにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出する工程であり、

前記工程(f)は、前記保護ダイオード領域において、前記絶縁膜に対してエッチングを行なうことにより、前記第2導電型拡散層の少なくとも一部を露出する工程であることを特徴とする請求項16に記載の半導体記憶装置の製造方法。 - 前記工程(c)において、前記保護ダイオード領域における前記ONO膜をさらに除去するようにパターニングすることを特徴とする請求項16〜18のいずれか1項に記載の半導体記憶装置の製造方法。

- 前記工程(b)は、前記保護ダイオード領域における前記ONO膜を選択的に除去する工程と、

前記ONO膜が除去された前記保護ダイオード領域に第3のシリコン酸化膜を選択的に形成する工程とを含むことを特徴とする請求項16〜18のいずれか1項に記載の半導体記憶装置の製造方法。 - 第1導電型の半導体領域の上に、複数のメモリセルを行列状に配置したメモリセルアレイ領域と保護ダイオード領域とを分離して形成する半導体記憶装置の製造方法であって、

前記半導体領域に素子分離絶縁膜を選択的に形成する工程(a)と、

前記素子分離絶縁膜を含む前記半導体領域の上に、トンネル絶縁膜及び第1の導電層を順次形成する工程(b)と、

前記メモリセルアレイ領域において、前記第1の導電層を列方向に延びる短冊状にパターニングすると共に、前記保護ダイオード領域において、前記第1の導電層を除去するようにパターニングする工程(c)と、

前記工程(c)よりも後に、パターニングされた前記第1の導電層をマスクとして、前記半導体領域の前記メモリセルアレイ領域においては、第2導電型拡散層からなり前記メモリセルのソースドレイン領域を形成すると共に、前記半導体領域の前記保護ダイオード領域においては、保護ダイオード素子を構成する第2導電型拡散層を形成する工程(d)と、

前記工程(d)よりも後に、パターニングされた前記第1の導電層を含む前記半導体領域の上に絶縁膜を形成した後、前記メモリセルアレイ領域において、パターニングされた前記第1の導電層の上面を露出する工程(e)と、

前記工程(d)よりも後に、前記保護ダイオード領域において、前記第2導電型拡散層の少なくとも一部を露出する工程(f)と、

前記メモリセルアレイ領域において、上面が露出した前記第1の導電層の上に、結合容量絶縁膜を選択的に形成する工程(g)と、

前記工程(g)よりも後に、前記半導体領域における前記メモリセルアレイ領域及び保護ダイオード領域の上に第2の導電層を形成する工程(h)と、

前記工程(h)よりも後に、前記メモリセルアレイ領域において、前記第2の導電層、結合容量絶縁膜及び第1の導電層を行方向にパターニングすることにより、それぞれ前記第1の導電層及び結合容量絶縁膜を含む行列状に配置された複数の前記メモリセルと、前記第2の導電層からなり同一の行に並ぶ複数の前記メモリセルを共通に接続する複数のワード線とを形成すると共に、前記保護ダイオード領域において、前記保護ダイオード素子の第2導電型拡散層と前記ワード線の端部とを直接に接続する工程(i)とを備えていることを特徴とする半導体記憶装置の製造方法。 - 前記工程(e)及び工程(f)は、形成された前記絶縁膜に対してエッチングを行なうことにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出し且つ互いに隣接する前記第1の導電層の間を埋め込むと共に、前記保護ダイオード領域において、前記第2導電型拡散層の少なくとも一部を露出する工程であることを特徴とする請求項21に記載の半導体記憶装置の製造方法。

- 前記工程(e)は、形成された前記絶縁膜に対して、化学機械研磨法により研磨することにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出する工程であり、

前記工程(f)及び(g)は、前記保護ダイオード領域において、前記結合容量絶縁膜及び絶縁膜に対してエッチングを行なうことにより、前記第2導電型拡散層の少なくとも一部を露出する工程であることを特徴とする請求項21に記載の半導体記憶装置の製造方法。 - 請求項4又は6に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1の第1導電型拡散層に第2の端子を接続し、前記第2の第2導電型拡散層及び第2の第1導電型拡散層に第3の端子を接続する工程と、

前記第1の端子に正のバイアス電圧を印加する際に、前記第2の端子及び第3 の端子は接地状態とする工程とを備えていることを特徴とする半導体記憶装置の駆動方法。 - 前記第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程をさらに備えていることを特徴とする請求項24に記載の半導体記憶装置の駆動方法。

- 請求項4又は6に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1の第1導電型拡散層に第2の端子を接続し、前記第2の第2導電型拡散層及び第2の第1導電型拡散層に第3の端子を接続する工程と、

前記第1の端子に負のバイアス電圧を印加する際に、前記第2の端子には前記第1の端子と同一の電圧を印加し、且つ前記第3の端子は接地状態とする工程とを備えていることを特徴とする半導体記憶装置の駆動方法。 - 前記第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程をさらに備えていることを特徴とする請求項26に記載の半導体記憶装置の駆動方法。

- 請求項2又は5に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1の第1導電型拡散層に第2の端子を接続し、前記第2の第2導電型拡散層に第3の端子を接続する工程と、

前記第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程と、

前記第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程とを備えていることを特徴とする半導体記憶装置の駆動方法。 - 請求項3に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1のシリサイド領域に第2の端子を接続し、前記第2のシリサイド領域に第3の端子を接続する工程と、

前記第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程と、

前記第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程とを備えていることを特徴とする半導体記憶装置の駆動方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006325510A JP5039368B2 (ja) | 2005-12-13 | 2006-12-01 | 半導体記憶装置、その製造方法及びその駆動方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005358969 | 2005-12-13 | ||

| JP2005358969 | 2005-12-13 | ||

| JP2006325510A JP5039368B2 (ja) | 2005-12-13 | 2006-12-01 | 半導体記憶装置、その製造方法及びその駆動方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007189204A JP2007189204A (ja) | 2007-07-26 |

| JP2007189204A5 JP2007189204A5 (ja) | 2009-04-09 |

| JP5039368B2 true JP5039368B2 (ja) | 2012-10-03 |

Family

ID=38344120

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006325510A Expired - Fee Related JP5039368B2 (ja) | 2005-12-13 | 2006-12-01 | 半導体記憶装置、その製造方法及びその駆動方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5039368B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9802374B2 (en) | 2006-11-03 | 2017-10-31 | Tufts University | Biopolymer sensor and method of manufacturing the same |

| US9969134B2 (en) | 2006-11-03 | 2018-05-15 | Trustees Of Tufts College | Nanopatterned biopolymer optical device and method of manufacturing the same |

| US10040834B2 (en) | 2006-11-03 | 2018-08-07 | Tufts University | Biopolymer optofluidic device and method of manufacturing the same |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5274878B2 (ja) * | 2008-04-15 | 2013-08-28 | パナソニック株式会社 | 半導体装置及びその製造方法 |

| JP5259246B2 (ja) * | 2008-05-09 | 2013-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP6292041B2 (ja) * | 2014-06-11 | 2018-03-14 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| JPWO2023281795A1 (ja) * | 2021-07-09 | 2023-01-12 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10173157A (ja) * | 1996-12-06 | 1998-06-26 | Toshiba Corp | 半導体装置 |

| JPH10200077A (ja) * | 1997-01-08 | 1998-07-31 | Sony Corp | 半導体装置及びその製造方法 |

| JP3528575B2 (ja) * | 1998-02-17 | 2004-05-17 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置及びその製造方法 |

| JP2002164447A (ja) * | 2000-11-28 | 2002-06-07 | Sharp Corp | 不揮発性半導体メモリの製造方法 |

| US6940152B2 (en) * | 2002-02-21 | 2005-09-06 | Matsushita Electric Industrial Co., Ltd. | Semiconductor storage device and its manufacturing method |

| JP4163610B2 (ja) * | 2003-12-22 | 2008-10-08 | 株式会社東芝 | 不揮発性半導体記憶装置 |

-

2006

- 2006-12-01 JP JP2006325510A patent/JP5039368B2/ja not_active Expired - Fee Related

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9802374B2 (en) | 2006-11-03 | 2017-10-31 | Tufts University | Biopolymer sensor and method of manufacturing the same |

| US9969134B2 (en) | 2006-11-03 | 2018-05-15 | Trustees Of Tufts College | Nanopatterned biopolymer optical device and method of manufacturing the same |

| US10040834B2 (en) | 2006-11-03 | 2018-08-07 | Tufts University | Biopolymer optofluidic device and method of manufacturing the same |

| US10280204B2 (en) | 2006-11-03 | 2019-05-07 | Tufts University | Electroactive biopolymer optical and electro-optical devices and method of manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007189204A (ja) | 2007-07-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6591291B2 (ja) | 半導体装置およびその製造方法 | |

| JP5191633B2 (ja) | 半導体装置およびその製造方法 | |

| JP4758625B2 (ja) | 半導体装置 | |

| JP4818061B2 (ja) | 不揮発性半導体メモリ | |

| TWI408800B (zh) | 非揮發性記憶體單元及其製造方法 | |

| JP5086558B2 (ja) | 半導体装置およびその製造方法 | |

| JP5039368B2 (ja) | 半導体記憶装置、その製造方法及びその駆動方法 | |

| JP2008530771A (ja) | 多重データを保存するための電気的に書換え可能な非揮発性メモリセル及びその製造方法 | |

| JP2006005357A (ja) | スプリットゲート型フラッシュメモリ素子及びその製造方法 | |

| US8409949B2 (en) | Non-volatile semiconductor memory device and method of manufacturing the same | |

| CN106024889B (zh) | 半导体器件及其制造方法 | |

| US7474548B2 (en) | Semiconductor memory device and method for manufacturing the same | |

| KR100953050B1 (ko) | 비휘발성 메모리 소자 및 그의 제조 방법 | |

| US6432773B1 (en) | Memory cell having an ONO film with an ONO sidewall and method of fabricating same | |

| CN100568508C (zh) | 对称及自对准的非易失性存储器结构 | |

| JP6786440B2 (ja) | 半導体装置およびその製造方法 | |

| JP2019117913A (ja) | 半導体装置およびその製造方法 | |

| US7611946B2 (en) | Method of fabricating a non-volatile memory device | |

| JP4758951B2 (ja) | 半導体装置 | |

| KR20000076852A (ko) | 반도체 기억장치 및 그 제조방법 | |

| US11205655B2 (en) | Method for manufacturing semiconductor device including fin-structured transistor | |

| JP2009194221A (ja) | 半導体装置およびその製造方法 | |

| JP2006310564A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| US20120037974A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP2011159712A (ja) | 不揮発性半導体記憶装置、および不揮発性半導体記憶装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090224 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090224 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110519 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20120120 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120417 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120522 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120612 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120709 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150713 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5039368 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |