JP4968982B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4968982B2 JP4968982B2 JP2000382599A JP2000382599A JP4968982B2 JP 4968982 B2 JP4968982 B2 JP 4968982B2 JP 2000382599 A JP2000382599 A JP 2000382599A JP 2000382599 A JP2000382599 A JP 2000382599A JP 4968982 B2 JP4968982 B2 JP 4968982B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor film

- region

- substrate

- tft

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

【発明の属する分野】

本発明は薄膜トランジスタ(以下、TFTと言う)で構成された回路を有する半導体装置の作製方法に関する。例えば、液晶表示装置に代表される電気光学装置、及び電気光学装置を部品として搭載した電気機器の構成に関する。また、前記装置の作製方法に関する。なお、本明細書中において半導体装置とは、半導体特性を利用することで機能し得る装置全般を指し、上記電気光学装置及び電気機器もその範疇にあるとする。

【0002】

【従来の技術】

ガラス等の絶縁基板上に形成された非晶質半導体膜に対し、加熱、またはレーザアニール、または加熱とレーザアニールの両方を行ない、結晶化させたり、結晶性を向上させる技術が広く研究されている。上記半導体膜には珪素膜がよく用いられる。

【0003】

上記技術により得られた結晶質半導体膜は多くの結晶粒からできているため、多結晶半導体膜とも呼ばれる。結晶質半導体膜は、非晶質半導体膜と比較し、非常に高い移動度を有する。このため、結晶質半導体膜を利用すると、例えば、従来の非晶質半導体膜を使って作製した半導体装置では実現できなかったモノリシック型の液晶電気光学装置(一枚の基板上に、画素駆動用と駆動回路用の薄膜トランジスタ(TFT)を作製した半導体装置)が作製できる。

【0004】

このように、結晶質半導体膜は、非晶質半導体膜と比較し、非常に特性の高い半導体膜である。これが、上記研究の行われる理由である。例えば、加熱による非晶質半導体膜の結晶化を行なうには、600℃以上の加熱温度と10時間以上の加熱時間が必要であった。この結晶化条件に耐える基板には、例えば、合成石英基板がある。しかしながら、合成石英基板は高価で加工性に乏しく、特に大面積に加工するのは非常に困難であった。基板の大面積化は特に量産効率を上げるためには必要不可欠な要素である。近年、量産効率の向上のために基板を大面積化する動きが著しく、新しく建設される量産工場のラインは、基板サイズ600×720mmが標準となりつつある。将来的には800×950mmまたは960×1100mmが標準になると考えられる。

【0005】

合成石英基板をこのような大面積基板に加工することは現在の技術では難しく、たとえできたとしても産業として成り立つ価格までは下がらないと考えられる。大面積基板を容易に作製できる材料に、例えばガラス基板がある。ガラス基板には、例えばコーニング7059と呼ばれているものがある。コーニング7059は非常に安価で加工性に富み、大面積化も容易である。しかしながら、コーニング7059は歪点温度が593℃であり、600℃以上の加熱には問題があった。

【0006】

ガラス基板の1つに、歪点温度が比較的高いコーニング1737というものがある。これの歪点温度は667℃とコーニング7059の歪点温度に比べて高い。前記コーニング1737基板に非晶質半導体膜を成膜し、600℃、20時間の雰囲気に置いても、作製工程に影響するほどの基板の変形は見られなかった。しかしながら、20時間の加熱時間は量産工程としては長過ぎた。

【0007】

このような問題を解決するため、新しい結晶化の方法が考案された。前記方法の詳細は特開平7−183540号公報に記載されている。ここで、前記方法を簡単に説明する。まず、非晶質半導体膜にニッケルまたは、パラジウム、または鉛等の金属元素を微量に添加する。添加の方法は、プラズマ処理法や蒸着法、イオン注入法、スパッタ法、溶液塗布法等を利用すればよい。前記添加の後、例えば550℃の窒素雰囲気に4時間、非晶質半導体膜を置くと、特性の良好な結晶質半導体膜が得られる。結晶化に最適な加熱温度や加熱時間等は、前記金属元素の添加量や、非晶質半導体膜の状態による。例えば、膜厚54nmの非晶質珪素膜に、酢酸ニッケル水溶液(重量換算濃度5ppm、体積10ml)を前記非晶質珪素膜表面にスピンコートにて塗布し、温度500℃の窒素雰囲気で1時間、更に温度550℃の窒素雰囲気で4時間加熱も行なったときに形成される結晶質珪素膜を図4に示す。図4は光学顕微鏡により明視野透過モードで500倍にて結晶質珪素膜を観察した結果であり、図5はその模式図である。図4および図5から、結晶化領域とまだ結晶化していない非晶質領域が混在していることがわかる。なお、本明細書中では、外周を結晶質の領域で囲まれている非晶質部分を非晶質領域と呼称する。

【0008】

また、結晶粒内と比較して、結晶粒の界面(結晶粒界)は非晶質構造や結晶欠陥などに起因する再結合中心や捕獲中心が無数に存在している。この捕獲中心にキャリアがトラップされると、結晶粒界のポテンシャルが上昇し、キャリアに対して障壁となるため、キャリアの電流輸送特性が低下することが知られている。

【0009】

【本発明が解決しようとする課題】

しかしながら、現在のLSIは高集積化、高速化するためにデバイスの微細化が図られており、前記デバイスの大きさは1μmを切っている。これまでの結晶化の方法で形成される結晶質半導体膜を用いてこのようなデバイスを作製する場合、素子分離のために前記結晶質半導体膜をパターニングして分離すると、個々のデバイスの活性領域において、結晶粒界が多く存在するものと、ほとんど単結晶で形成されるものなどのばらつきが生じた。このばらつきは、電気的特性においてもばらつきの原因となっていた。

【0010】

そこで、金属元素を多量に添加すれば、前記金属元素が表面エネルギーを低下させ、臨界核半径を小さくする。その結果、多数の結晶核が発生して、結晶粒の粒径を小さくする事ができる。しかしながら、この方法では前記金属元素が高抵抗領域(チャネル形成領域やオフセット領域)中に金属化合物として過剰に残留すると言う問題がある。前記金属化合物は電流が流れやすいため、高抵抗領域であるべき領域の抵抗を下げることになり、TFTの特性の安定性および信頼性を損なう原因となる。

【0011】

一方で、位置制御された大粒径の結晶粒を形成する方法も求められている。これは、全てのデバイスの高抵抗領域(好ましくは活性領域)をほとんど単結晶で形成することができれば、電気的特性のばらつきを低減させるだけでなく、さらに向上させることが可能になるためである。

【0012】

本発明はこれらの問題を解決するための技術であり、結晶核の生成密度を制御することで、それぞれのデバイスのサイズに応じた粒径の結晶粒を形成するための技術であり、前記金属元素の使用量を増加することなく、TFTを用いて作製するアクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、半導体装置の動作特性および信頼性の向上を実現することを目的としている。

【0013】

【課題を解決するための手段】

本発明者は、上記の課題を解決するために、以下に示す第1および第2の実験を行なった。

【0014】

まず、第1の実験として、プラズマCVD法によって形成された膜厚54nmの非晶質珪素膜に、B(ボロン)をイオン注入法により加速電圧を10kV、ドーズ量2.0×1014/cm2、5.0×1014/cm2、1.0×1015/cm2と条件を振って添加した。そして、特開平7−183540号公報に記載されたような方法を利用して、酢酸ニッケル水溶液(重量換算濃度10ppm、体積10ml)を前記非晶質珪素膜表面にスピンコートにて塗布し、温度500℃の窒素雰囲気で1時間、更に温度550℃の窒素雰囲気で4時間加熱した。その結果を図6に、図6の模式図を図7に示す。また、ラマン測定によって得られた強度から、非晶質領域および結晶化領域によって得られる強度が異なることから、その比を取って結晶化率とした。その結果を図21に示す。図21より、ドーズ量を増やすにしたがって、結晶化率も増加していることがわかる。図6、図7および図21より、ドーズ量が増えるにしたがって結晶化領域が増えたことがわかる。つまり、Bを添加したことにより、表面エネルギーを低下させ、臨界核半径を小さくする。その結果、結晶核の生成密度が増加して、半導体膜の結晶化を促進すると考えられる。

【0015】

次に、第2の実験として、プラズマCVD法によって形成された膜厚54nmの非晶質珪素膜に、P(リン)をイオン注入法により加速電圧を10kV、ドーズ量5.0×1014/cm2として添加した。そして、特開平7−183540号公報に記載されたような方法を利用して、酢酸ニッケル水溶液(重量換算濃度10ppm、体積10ml)を前記非晶質珪素膜表面にスピンコートにて塗布し、温度500℃の窒素雰囲気で1時間、更に温度550℃の窒素雰囲気で4時間加熱した。その結果を図8に、図8の模式図を図9示す。図8および図9より、Pを添加することにより、結晶化領域が減ることがわかる。つまり、Pを添加したことにより、表面エネルギーを増加させ、臨界核半径を大きくする。その結果、結晶核の生成密度が低下して、半導体膜の結晶化を阻害すると考えられる。また、結晶成長に特徴が見られ、個々の結晶化領域が非常に大きい。

【0016】

以上の実験から、あらかじめ半導体膜にB(ボロン)を添加することにより、表面エネルギーを低下させ、臨界核半径を小さくするため、結晶核の生成密度が増加して、半導体膜の結晶化が促進されることがわかる。また、あらかじめ半導体膜にP(リン)を添加することにより、表面エネルギーを増加させ、臨界核半径を大きくするため、結晶核の生成密度が低下して、半導体膜の結晶化が阻害することがわかる。つまり、BやPを半導体膜に添加することで、結晶核の生成密度を制御することができる。また、Bを半導体膜に添加することにより結晶化が促進されることから、加熱時間の短縮や低温での結晶化を可能にしている。また金属元素の添加量を減少することも可能にしている。Pを半導体膜に添加することにより形成される個々の結晶化領域が大きいことから、任意の位置に大粒径の結晶粒を形成することを可能とする。さらに、BやPの添加量が微量であれば、TFTのしきい値を制御するために有効であることから、BやPを除去するための工程を増やす必要もない。しかしながら、BやPがTFTの電気的特性に悪影響を及ぼすほど添加する場合もある。その場合には、例えばBを除去する方法として、温度700〜950度程度の酸素雰囲気中に30分〜3時間程度曝せば、半導体膜上に酸化膜が形成され、前記酸化膜中にBが取り込まれる。そこで、前記酸化膜を除去すれば、半導体膜中からBを除去することが出来る。

【0017】

なお、前記第1および第2の実験において、半導体膜として珪素膜を、結晶化を助長する元素としてニッケルを、不純物元素としてBやPを用いた。しかし、本発明はこれらに限定するものではなく、半導体膜としてシリコンゲルマニウム(SiGe)合金などの非晶質構造を有する化合物半導体膜を適用しても良いし、Bの代わりに13族に属する元素から選ばれた一種または複数の元素、Pの代わりに15属に属する元素から選ばれた一種または複数の元素を用いることができる。

【0018】

このように、本発明は、不純物元素をあらかじめ添加した半導体膜を用いることで、結晶核の生成密度を制御することが出来る。結晶核の生成密度を制御することで、目的とするデバイスのサイズに応じた粒径の結晶粒を形成することができる。また、前記不純物元素に13族に属する元素を用いれば、結晶化のための加熱時間の短縮や加熱温度の低下も可能とする。また金属元素の添加量を減少することも可能にしている。また、前記不純物元素に15族に属する元素を用いれば、大きな結晶化領域が形成されることから、任意の位置に大粒径の結晶粒を形成することを可能とする。また、13族に属する元素および15属に属する元素の両方を用いれば、任意の位置に大粒径の結晶粒を15属に属する元素のみを用いたときより早く形成することを可能にする。また、13族に属する元素および15族に属する元素はそれぞれp型またはn型を付与する不純物元素としてよく用いられている。両元素を同程度添加すれば、中和されて半導体膜は実質的に真性となり、不純物元素を除去する工程を増やす必要がなくなる。さらに、不純物元素の添加量が微量であれば、TFTのしきい値を制御するために有効であり、前記不純物元素を除去するための工程を増やす必要もない。また、不純物元素の添加による結晶性の欠陥は、結晶化のための加熱処理によって回復するため、問題にならない。

【0019】

また、半導体膜上に13族に属する元素を添加する領域と15族に属する元素を添加する領域とを設け、結晶化を助長する金属元素を添加して加熱処理を行なえば、得られる結晶質半導体膜において所定の領域に所望の粒径の結晶粒を形成することを可能とする。

【0020】

もちろん、本発明において、結晶化を助長する金属元素を半導体膜に添加したのち、不純物元素を添加して加熱処理を行なってもよい。

【0021】

本明細書で開示する本発明の作製方法は、

半導体膜に不純物元素を添加する第1の工程と、

前記不純物元素が添加された前記半導体膜に金属元素を添加する第2の工程と、前記不純物元素および前記金属元素が添加された前記半導体膜を加熱処理により結晶化させる第3の工程と、

を有することを特徴とする半導体装置の作製方法である。

【0022】

上記作製方法において、前記不純物元素は、13族に属する元素から選ばれた一種または複数の元素、または、15族に属する元素から選ばれた一種または複数の元素、13族に属する元素および15族に属する元素から選ばれた一種または複数の元素であることを特徴としている。

【0023】

また、上記作製方法において、前記金属元素は、Ni、Pd、Pt、Cu、Ag、Au、In、Sn、Pd、P、As、Sbから選ばれた一種または複数の元素であることを特徴としている。

【0024】

また、上記第2の工程において、前記不純物元素の添加量を調節することにより、上記第3の工程によって形成される結晶核の生成密度を制御することを可能にすることを特徴としている。

【0025】

【発明の実施の形態】

[実施形態1]

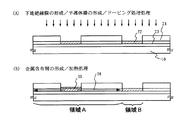

本発明の実施形態の1つについて図1の断面図を用いて説明する。

【0026】

図1(A)において基板10には、合成石英ガラス基板、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラスなどの無アルカリガラスと言ったガラス基板を用いても良い。例えば、コーニング社製の7059ガラスや1737ガラスなどを好適に用いることが出来る。また、本実施形態の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。

【0027】

前記基板10の上に下地絶縁膜11を公知の手段(LPCVD法、プラズマCVD法等)により窒化珪素膜、酸化窒化珪素膜または酸化珪素膜などで形成する。

【0028】

次に、半導体膜12をプラズマCVD法やスパッタ法などの公知の手段で10〜200nm(好ましくは30〜100nm)の厚さに形成する。前記半導体膜12aとしては、非晶質半導体膜や微結晶半導体膜などがあり、非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。

【0029】

続いて、前記半導体膜に不純物元素の添加を行なう。本実施形態においては、13族に属する元素、または、13族に属する元素および15族に属する元素をドーピング処理によって添加する。ドーピング処理はイオンドープ法、若しくはイオン注入法で行なえば良い。イオンドープ法の条件はそれぞれの濃度が1×1016〜5×1021/cm3としなるように添加する。

【0030】

その後、結晶化を助長するための金属元素を含む層(金属含有層13)を形成する。前記金属元素としては、ニッケル、またはパラジウム、または鉛等の金属元素があり、添加の方法は、プラズマ処理法や蒸着法、イオン注入法、スパッタ法、溶液塗布法等を利用すればよい。そして、加熱処理を行なって、半導体膜12bの結晶化を行なう。この加熱処理はファーネスアニール炉を用いる熱アニール法で行なう。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行なえばよい。また、熱アニール法の他に加熱処理としてレーザアニール法、またはラピッドサーマルアニール法(RTA法)等があり、熱アニール法とこれらを組み合わせて加熱処理を行なうこともできる。

【0031】

この後、半導体膜において過剰に不純物元素が残留する場合は、除去する必要がある。例えば、Bを除去するのであれば、温度700〜950度程度の酸素雰囲気中に30分〜3時間程度曝せば、形成される酸化膜中にBが取り込まれるので、前記酸化膜を除去することにより、Bを除去することが出来る。

【0032】

このようにして得られた結晶質半導体膜は、粒径の小さな結晶粒を有し、特にサブミクロンデバイスを作製するのに適しており、電気的特性のばらつきを低減することを可能にする。また、結晶化に要する加熱時間の短縮も可能にしている。

【0033】

[実施形態2]

本発明の実施形態の1つについて図2の断面図を用いて説明する。

【0034】

図2(A)において基板10には、合成石英ガラス基板、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラスなどの無アルカリガラスと言ったガラス基板を用いても良い。例えば、コーニング社製の7059ガラスや1737ガラスなどを好適に用いることが出来る。また、本実施形態の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。

【0035】

前記基板10の上に下地絶縁膜11を公知の手段(LPCVD法、プラズマCVD法等)により窒化珪素膜、酸化窒化珪素膜または酸化珪素膜などで形成する。

【0036】

次に、半導体膜12をプラズマCVD法やスパッタ法などの公知の手段で10〜200nm(好ましくは30〜100nm)の厚さに形成する。前記半導体膜12としては、非晶質半導体膜や微結晶半導体膜などがあり、非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。

【0037】

続いて、マスク24を形成して前記半導体膜に選択的に不純物元素の添加を行なう。不純物元素が導入された領域22を活性領域としてデバイスを作製するのが望ましい。本実施形態においては、15族に属する元素、または15族に属する元素および13族に属する元素をドーピング処理によって添加する。ドーピング処理はイオンドープ法、若しくはイオン注入法で行なえば良い。イオンドープ法の条件は濃度が1×1016〜5×1021/cm3としなるように添加する。

【0038】

その後、結晶化を助長するための金属元素を含む層(金属含有層25)を形成する。前記金属元素としては、ニッケル、またはパラジウム、または鉛等の金属元素があり、添加の方法は、プラズマ処理法や蒸着法、イオン注入法、スパッタ法、溶液塗布法等を利用すればよい。そして、加熱処理を行なって、半導体膜22の結晶化を行なう。この加熱処理はファーネスアニール炉を用いる熱アニール法で行なう。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行なえばよい。また、熱アニール法の他に加熱処理として、レーザアニール法、またはラピッドサーマルアニール法(RTA法)等があり、熱アニール法とこれらを組み合わせて加熱処理を行なうこともできる。

【0039】

加熱処理により、結晶核は領域22から26で示した方向へ成長し、それに伴い、結晶化を助長するために用いた金属元素および不純物元素は領域23へが移動する。そこで、領域23を除去し、領域22を活性領域としてTFTを作製すれば、その電気的特性は良好なものとなる。

【0040】

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行なうこととする。

【0041】

【実施例】

[実施例1]

本発明の実施例について図1の断面図を用いて説明する。

【0042】

図1(A)において基板10には、合成石英ガラス基板、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラスなどの無アルカリガラスと言ったガラス基板を用いても良い。例えば、コーニング社製の7059ガラスや1737ガラスなどを好適に用いることが出来る。また、本実施例の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。本実施例において、基板10として合成石英ガラス基板を用いた。

【0043】

前記基板10の上に下地絶縁膜11を公知の手段(LPCVD法、プラズマCVD法等)により窒化珪素膜、酸化窒化珪素膜または酸化珪素膜などで形成する。本実施例において、下地絶縁膜として膜厚150nmの酸化窒化珪素膜(組成比Si=32%、O=27%、N=24%、H=17%)を形成した。

【0044】

次に、半導体膜12をプラズマCVD法やスパッタ法などの公知の手段で10〜200nm(好ましくは30〜100nm)の厚さに形成する。前記半導体膜12aとしては、非晶質半導体膜や微結晶半導体膜などがあり、非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。本実施例では、プラズマCVD法を用い、55nmの非晶質珪素膜を成膜した。

【0045】

続いて、前記半導体膜に不純物元素の添加を行なう。本実施形態においては、13族に属する元素、または、13族に属する元素および15族に属する元素をドーピング処理によって添加する。ドーピング処理はイオンドープ法、若しくはイオン注入法で行なえば良い。イオンドープ法の条件はそれぞれの濃度が1×1016〜5×1021/cm3となるように添加する。本実施例ではボロンを用い、ドーズ量を5×1013/cm2とし、加速電圧を10kVとして、ドーピング処理を行なった。このドーピング処理により、半導体膜中におけるB濃度は5.0×1018/cm3となった。

【0046】

その後、結晶化を助長するための金属元素を含む層(金属含有層13)を形成する。前記金属元素としては、ニッケル、またはパラジウム、または鉛等の金属元素があり、添加の方法は、プラズマ処理法や蒸着法、イオン注入法、スパッタ法、溶液塗布法等を利用すればよい。そして、加熱処理を行なって、半導体膜12bの結晶化を行なう。この加熱処理はファーネスアニール炉を用いる熱アニール法で行なう。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行なえばよい。また、熱アニール法の他に加熱処理としてレーザアニール法、またはラピッドサーマルアニール法(RTA法)等があり、熱アニール法とこれらを組み合わせて加熱処理を行なうこともできる。本実施例では、酢酸ニッケル水溶液(重量換算濃度5ppm、体積10ml)を非晶質珪素膜表面にスピンコートにて塗布し、加熱処理(550℃、2時間)を行ない、結晶質珪素膜を形成した。

【0047】

本実施例において、半導体膜中に過剰に不純物元素が残留しているため、除去する必要がある。そこで、温度950度の酸素雰囲気中に30分曝すと、形成される酸化膜中にBが取り込まれるので、前記酸化膜を除去することにより、Bを除去することが出来た。

【0048】

このようにして得られた結晶質半導体膜は、粒径の小さな結晶粒を有し、特にサブミクロンデバイスを作製するのに適しており、電気的特性のばらつきを低減することを可能にする。また、結晶化に要する加熱時間の短縮も可能にしている。

【0049】

[実施例2]

本発明の実施例について図2の断面図を用いて説明する。

【0050】

図2(A)において基板10には、合成石英ガラス基板、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラスなどの無アルカリガラスと言ったガラス基板を用いても良い。例えば、コーニング社製の7059ガラスや1737ガラスなどを好適に用いることが出来る。また、本実施例の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。本実施例において、基板10としてコーニング社製1737ガラス基板を用いた。

【0051】

前記基板10の上に下地絶縁膜11を公知の手段(LPCVD法、プラズマCVD法等)により窒化珪素膜、酸化窒化珪素膜または酸化珪素膜などで形成する。本実施例において、下地絶縁膜として膜厚150nmの酸化窒化珪素膜(組成比Si=32%、O=27%、N=24%、H=17%)を形成した。

【0052】

次に、半導体膜12をプラズマCVD法やスパッタ法などの公知の手段で10〜200nm(好ましくは30〜100nm)の厚さに形成する。前記半導体膜12aとしては、非晶質半導体膜や微結晶半導体膜などがあり、非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。本実施例では、プラズマCVD法を用い、55nmの非晶質珪素膜を成膜した。

【0053】

続いて、マスク24を形成して、前記半導体膜に不純物元素の添加を行なう。本実施形態においては、13族に属する元素をドーピング処理によって添加する。不純物元素が導入された領域22を活性領域としてデバイスを作製するのが望ましい。ドーピング処理はイオンドープ法、若しくはイオン注入法で行なえば良い。イオンドープ法の条件は濃度が1×1016〜5×1021/cm3としなるように添加する。本実施例では、プラズマCVD法またはスパッタ法を用いて、厚さを40〜150nmとして酸化珪素膜を成膜し、パターニングを行なってマスク24を形成した。もちろん、マスク24は酸化珪素膜に限定されない。そして、リンを用い、ドーズ量を2×1014/cm2とし、加速電圧を10kVとして、ドーピング処理を行なった。このドーピング処理により、半導体膜中におけるP濃度は1.0×1020/cm3となった。

【0054】

その後、結晶化を助長するための金属元素を含む層(金属含有層25)を形成する。前記金属元素としては、ニッケル、またはパラジウム、または鉛等の金属元素があり、添加の方法は、プラズマ処理法や蒸着法、イオン注入法、スパッタ法、溶液塗布法等を利用すればよい。そして、加熱処理を行なって、半導体膜22の結晶化を行なう。この加熱処理はファーネスアニール炉を用いる熱アニール法で行なう。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行なえばよい。また、熱アニール法の他に加熱処理としてレーザアニール法、またはラピッドサーマルアニール法(RTA法)等があり、熱アニール法とこれらを組み合わせて加熱処理を行なうこともできる。本実施例では、酢酸ニッケル水溶液(重量換算濃度5ppm、体積10ml)を非晶質珪素膜表面にスピンコートにて塗布し、加熱処理(550℃、2時間)を行ない、結晶質珪素膜を形成した。

【0055】

加熱処理により、結晶核は領域22から26で示した方向へ成長し、それに伴い、結晶化を助長するために用いた金属元素および不純物元素は領域23へが移動する。そこで、領域23を除去し、領域22を活性領域としてTFTを作製すれば、その電気的特性は良好なものとなる。

【0056】

[実施例3]

本発明の実施例について図3の断面図を用いて説明する。

【0057】

実施例2にしたがって、図2(B)まで形成する。なお、図2(B)と図3(A)は同じ状態を示す。

【0058】

そして、結晶化を助長するための金属元素を含む層(金属含有層35)を選択的に形成する。前記金属元素としては、ニッケル、またはパラジウム、または鉛等の金属元素があり、添加の方法は、プラズマ処理法や蒸着法、イオン注入法、スパッタ法、溶液塗布法等を利用すればよい。本実施例において、Pが添加された領域にのうち、1つおきの領域に選択的にニッケルを添加した。(図3(B))そして、加熱処理を行なって、半導体膜22の結晶化を行なう。この加熱処理はファーネスアニール炉を用いる熱アニール法で行なう。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行なえばよい。また、熱アニール法の他に加熱処理としてレーザアニール法、またはラピッドサーマルアニール法(RTA法)等があり、熱アニール法とこれらを組み合わせて加熱処理を行なうこともできる。本実施例では、非晶質珪素膜に加熱処理(550℃、2時間)を行ない、結晶質珪素膜を形成した。

【0059】

加熱処理により、結晶核は前記金属元素が添加された領域から36で示した方向へ成長し、それに伴い、結晶化を助長するために用いた金属元素および不純物元素は、前記金属元素が添加されなかった領域(領域B)へが移動する。そこで、領域Bを除去し、それ以外の領域(領域A)を活性領域としてTFTを作製すれば、その電気的特性は良好なものとなる。

【0060】

[実施例4]

本実施例では、実施例1乃至3とは異なる加熱方法によって半導体膜の結晶化を行なう方法について図1を用いて説明する。

【0061】

実施例1にしたがって、図1(B)まで形成する。そして、結晶化を助長するための金属元素を含む層(金属含有層35)を選択的に形成する。前記金属元素としては、ニッケル、またはパラジウム、または鉛等の金属元素があり、添加の方法は、プラズマ処理法や蒸着法、イオン注入法、スパッタ法、溶液塗布法等を利用すればよい。本実施例において、Pが添加された領域にのうち、1つおきの領域に選択的にニッケルを添加した。(図1(C))

【0062】

そして、加熱処理を行なって、半導体膜22の結晶化を行なう。この加熱処理はファーネスアニール炉を用いる熱アニール法で行なう。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下での窒素雰囲気中で、圧力が13.3Pa程度の減圧雰囲気中で400〜700℃、代表的には500〜550℃で行なえばよい。また、減圧雰囲気中での熱アニール法の他にPPTA(Plural Pulse Thermal Anneal)装置での加熱処理も有効である。PPTA装置では、光源をパルス状に発光させて照射することにより、瞬間的に半導体膜だけを加熱してその熱がガラス基板に伝わる前に加熱を止めることができる急速加熱、急冷が可能な加熱方法であるため、ガラス基板が熱によって変形したりダメージを受けることはない。さらに、パルス状に制御した光源の点灯による熱の伝達を温度センサーにより制御しており、この制御にあわせてガラス基板にガラス転移温度以上の熱が伝わらないような冷却手段を用いている。また、この加熱処理を繰り返すことにより、半導体膜の結晶化を促進する触媒元素が半導体中を拡散する温度を保持している間も、ガラス基板を歪ませることなく、比較的短時間で効率よく半導体膜の結晶化するための半導体膜の加熱処理を行なうことができる。

【0063】

本実施例では、酢酸ニッケル水溶液(重量換算濃度5ppm、体積10ml)を非晶質珪素膜表面にスピンコートにて塗布し、13.3Paの減圧雰囲気中で加熱処理(550℃、2時間)を行ない、結晶質珪素膜を形成した。

【0064】

このようにして得られた結晶質半導体膜は、粒径の小さな結晶粒を有し、特にサブミクロンデバイスを作製するのに適しており、電気的特性のばらつきを低減することを可能にする。また、結晶化に要する加熱時間の短縮も可能にしている。

【0065】

[実施例5]

本実施例ではアクティブマトリクス基板の作製方法について図10〜図21を用いて説明する。

【0066】

まず、本実施例ではコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラスからなる基板300を用いる。なお、基板300としては、石英基板やシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施例の処理温度に耐えうる耐熱性が有するプラスチック基板を用いてもよい。

【0067】

次いで、基板300上に酸化珪素膜、窒化珪素膜または酸化窒化珪素膜などの絶縁膜から成る下地膜301を形成する。本実施例では下地膜301として2層構造を用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。下地膜301の一層目としては、プラズマCVD法を用い、SiH4、NH3、及びN2Oを反応ガスとして成膜される酸化窒化珪素膜301aを10〜200nm(好ましくは50〜100nm)形成する。本実施例では、膜厚50nmの酸化窒化珪素膜301a(組成比Si=32%、O=27%、N=24%、H=17%)を形成した。次いで、下地膜301のニ層目としては、プラズマCVD法を用い、SiH4、及びN2Oを反応ガスとして成膜される酸化窒化珪素膜301bを50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。本実施例では、膜厚100nmの酸化窒化珪素膜401b(組成比Si=32%、O=59%、N=7%、H=2%)を形成した。

【0068】

次いで、下地膜上に半導体膜302を形成する。半導体膜302は、非晶質構造を有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により、25〜80nm(好ましくは30〜60nm)の厚さで形成する。半導体膜の材料に限定はないが、好ましくは珪素または珪素ゲルマニウム(SiGe)合金などで形成すると良い。本実施例では、プラズマCVD法を用い、55nmの非晶質珪素膜を成膜した。

【0069】

そして、第1のドーピング処理を行なう。ドーピング処理はイオンドープ法、若しくはイオン注入法で行なえば良い。不純物元素は13族に属する元素、または15族に属する元素から選ばれた一種または複数の元素を用いる。イオンドープ法の条件は濃度が1×1016〜5×1021/cm3となるように添加する。本実施例では、Bを用いて、1×1017/cm3となるように添加した。1×1016〜1×1018/cm3の微量な濃度であれば、しきい値を制御するのに有効であり、不純物元素を除去する工程を増やさなくて済む。

【0070】

続いて、半導体膜の結晶化を行なう。半導体膜の結晶化にはニッケルなどの金属元素を用いる熱アニール法を適用する。半導体膜の結晶化には、他にもレーザ結晶化法、RTA法等があり、これらの結晶化法のいずれかとニッケルなどの金属元素を用いる熱アニール法と組み合わせて行なっても良い。本実施例では、酢酸ニッケル水溶液(重量換算濃度5ppm、体積10ml)を非晶質珪素膜表面にスピンコートにて塗布して金属含有層303を形成した。そして、加熱処理(550℃、2時間)を行ない、結晶質珪素膜を形成した。

【0071】

また、半導体膜の結晶化にレーザ結晶化法も合わせて適用する場合には、パルス発振型または連続発光型のエキシマレーザやYAGレーザ、YVO4レーザ等を用いることができる。これらのレーザを用いる場合には、レーザ発振器から放射されたレーザビームを光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宣選択するものであるが、エキシマレーザを用いる場合はパルス発振周波数300Hzとし、レーザエネルギー密度を100〜800mJ/cm2(代表的には200〜700mJ/cm2)とする。また、YAGレーザを用いる場合にはその第2高調波を用いパルス発振周波数1〜300Hzとし、レーザエネルギー密度を300〜1000mJ/cm2(代表的には350〜800mJ/cm2)とすると良い。そして幅100〜1000μm、例えば400μmで線状に集光したレーザビームを基板全面に渡って照射し、この時の線状ビームの重ね合わせ率(オーバーラップ率)を50〜98%として行えばよい。

【0072】

このようにして得られた結晶質半導体膜を所望の形状にパターニングして、半導体層402〜406を形成する。本実施例では、結晶質珪素膜をフォトリソグラフィ法を用いたパターニング処理によって、半導体層402〜406を形成した。

【0073】

次いで、半導体層402〜406を覆うゲート絶縁膜407を形成する。ゲート絶縁膜407はプラズマCVD法またはスパッタ法を用い、厚さを40〜150nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により110nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成した。もちろん、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

【0074】

また、酸化珪素膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製される酸化珪素膜は、その後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0075】

次いで、図10(C)に示すように、ゲート絶縁膜407上に膜厚20〜100nmの第1の導電膜408と、膜厚100〜400nmの第2の導電膜409とを積層形成する。本実施例では、膜厚30nmのTaN膜からなる第1の導電膜408と、膜厚370nmのW膜からなる第2の導電膜409を積層形成した。TaN膜はスパッタ法で形成し、Taのターゲットを用い、窒素を含む雰囲気内でスパッタした。また、W膜は、Wのターゲットを用いたスパッタ法で形成した。その他に6フッ化タングステン(WF6)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度のW(純度99.9999%)のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9〜20μΩcmを実現することができた。

【0076】

なお、本実施例では、第1の導電膜408をTaN、第2の導電膜409をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした結晶質珪素膜に代表される半導体膜を用いてもよい。また、AgPdCu合金を用いてもよい。また、第1の導電膜をタンタル(Ta)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化チタン(TiN)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をAl膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をCu膜とする組み合わせとしてもよい。

【0077】

次に、フォトリソグラフィ法を用いてレジストからなるマスク410〜415を形成し、電極及び配線を形成するための第1のエッチング処理を行なう。第1のエッチング処理では第1及び第2のエッチング条件で行なう。本実施例では第1のエッチング条件として、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を25/25/10(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行った。ここでは、松下電器産業(株)製のICPを用いたドライエッチング装置(Model E645−□ICP)を用いた。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。

【0078】

この後、レジストからなるマスク410〜415を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4とCl2とを用い、それぞれのガス流量比を30/30(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した第2のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。なお、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。

【0079】

上記第1のエッチング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15〜45°となる。こうして、第1のエッチング処理により第1の導電層と第2の導電層から成る第1の形状の導電層417〜422(第1の導電層417a〜422aと第2の導電層417b〜422b)を形成する。416はゲート絶縁膜であり、第1の形状の導電層417〜422で覆われない領域は20〜50nm程度エッチングされ薄くなった領域が形成される。

【0080】

そして、レジストからなるマスクを除去せずに第2のドーピング処理を行ない、半導体層にn型を付与する不純物元素を添加する。(図11(A))ドーピング処理はイオンドープ法、若しくはイオン注入法で行なえば良い。イオンドープ法の条件はドーズ量を1×1013〜5×1015/cm2とし、加速電圧を60〜100keVとして行なう。本実施例ではドーズ量を1.5×1015/cm2とし、加速電圧を80keVとして行った。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いた。この場合、導電層417〜421がn型を付与する不純物元素に対するマスクとなり、自己整合的に第1の高濃度不純物領域306〜310が形成される。第1の高濃度不純物領域306〜310には1×1020〜1×1021/cm3の濃度範囲でn型を付与する不純物元素を添加する。

【0081】

次いで、レジストからなるマスクを除去せずに第2のエッチング処理を行なう。ここでは、エッチングガスにCF4とCl2とO2とを用い、W膜を選択的にエッチングする。この時、第2のエッチング処理により第2の導電層428b〜433bを形成する。一方、第1の導電層417a〜422aは、ほとんどエッチングされず、第2の形状の導電層428〜433を形成する。

【0082】

次いで、レジストからなるマスクを除去せずに、図11(B)に示すように、第3のドーピング処理を行なう。この場合、第2のドーピング処理よりもドーズ量を下げて、70〜120keVの高い加速電圧で、n型を付与する不純物元素を導入する。本実施例ではドーズ量を1.5×1014/cm2とし、加速電圧を90keVとして行なった。第2のドーピング処理は第2の形状の導電層428〜433をマスクとして用い、第2の導電層428b〜433bの下方における半導体層にも不純物元素が導入され、新たに第2の高濃度不純物領域423a〜427aおよび低濃度不純物領域423b〜427bが形成される。

【0083】

次いで、レジストからなるマスクを除去した後、新たにレジストからなるマスク434aおよび434bを形成して、図11(C)に示すように、第3のエッチング処理を行なう。エッチング用ガスにSF6およびCl2とを用い、ガス流量比を50/10(sccm)とし、1.3Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成し、約30秒のエッチング処理を行なう。基板側(資料ステージ)には10WのRF(13.56MHz)電力を投入し、実質的には不の自己バイアス電圧を印加する。こうして、前記大3のエッチング処理により、pチャネル型TFTおよび画素部のTFT(画素TFT)のTaN膜をエッチングして、第3の形状の導電層435〜438を形成する。

【0084】

次いで、レジストからなるマスクを除去した後、第2の形状の導電層428、430および第2の形状の導電層435〜438をマスクとして用い、ゲート絶縁膜416を選択的に除去して絶縁層439〜444を形成する。(図12(A))

【0085】

次いで、新たにレジストからなるマスク445a〜445cを形成して第4のドーピング処理を行なう。この第4のドーピング処理により、pチャネル型TFTの活性層となる半導体層に前記一導電型とは逆の導電型を付与する不純物元素が添加された不純物領域446、447を形成する。第2の導電層435a、438aを不純物元素に対するマスクとして用い、p型を付与する不純物元素を添加して自己整合的に不純物領域を形成する。本実施例では、不純物領域446、447はジボラン(B2H6)を用いたイオンドープ法で形成する。(図12(B))この第4のドーピング処理の際には、nチャネル型TFTを形成する半導体層はレジストからなるマスク445a〜445cで覆われている。第1のドーピング処理及び第2のドーピング処理によって、不純物領域446、447にはそれぞれ異なる濃度でリンが添加されているが、そのいずれの領域においてもp型を付与する不純物元素の濃度を2×1020〜2×1021/cm3となるようにドーピング処理することにより、pチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問題は生じない。本実施例では、pチャネル型TFTの活性層となる半導体層の一部が露呈しているため、不純物元素(ボロン)を添加しやすい利点を有している。

【0086】

以上までの工程で、それぞれの半導体層に不純物領域が形成される。

【0087】

次いで、レジストからなるマスク445a〜445cを除去して第1の層間絶縁膜461を形成する。この第1の層間絶縁膜461としては、プラズマCVD法またはスパッタ法を用い、厚さを100〜200nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚150nmの酸化窒化珪素膜を形成した。もちろん、第1の層間絶縁膜461は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

【0088】

次いで、図12(C)に示すように、加熱処理を行なって、半導体層の結晶性の回復、それぞれの半導体層に添加された不純物元素の活性化を行なう。この加熱処理はファーネスアニール炉を用いる熱アニール法で行なう。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜550℃で行えばよく、本実施例では550℃、4時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

【0089】

なお、結晶化の際にニッケルなどを触媒として熱結晶化法も適用した場合は、上記活性化処理と同時に、金属元素が高濃度のリンを含む不純物領域423a、425a、426a、446a、447aを結晶化する。そのため、前記不純物領域に前記金属元素がゲッタリングされ、主にチャネル形成領域となる半導体層中の金属元素濃度が低減される。このようにして作製したチャネル形成領域を有するTFTはオフ電流値が下がり、結晶性が良いことから高い電界効果移動度が得られ、良好な特性を達成することができる。

【0090】

また、第1の層間絶縁膜を形成する前に加熱処理を行なっても良い。ただし、用いた配線材料が熱に弱い場合には、本実施例のように配線等を保護するため層間絶縁膜(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で活性化処理を行なうことが好ましい。

【0091】

さらに、3〜100%の水素を含む雰囲気中で、300〜550℃で1〜12時間の熱処理を行ない、半導体層を水素化する工程を行なう。本実施例では水素を約3%の含む窒素雰囲気中で410℃、1時間の熱処理を行なった。この工程は層間絶縁膜に含まれる水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行なっても良い。

【0092】

また、活性化処理としてレーザアニール法を用いる場合には、上記水素化を行った後、YAGレーザ等のレーザビームを照射することが望ましい。

【0093】

次いで、第1の層間絶縁膜461上に無機絶縁膜材料または有機絶縁物材料から成る第2の層間絶縁膜462を形成する。本実施例では、膜厚1.6μmのアクリル樹脂膜を形成したが、粘度が10〜1000cp、好ましくは40〜200cpのものを用い、表面に凸凹が形成されるものを用いた。

【0094】

本実施例では、鏡面反射を防ぐため、表面に凸凹が形成される第2の層間絶縁膜を形成することによって画素電極の表面に凸凹を形成した。また、画素電極の表面に凹凸を持たせて光散乱性を図るため、画素電極の下方の領域に凸部を形成してもよい。その場合、凸部の形成は、TFTの形成と同じフォトマスクで行なうことができるため、工程数の増加なく形成することができる。なお、この凸部は配線及びTFT部以外の画素部領域の基板上に適宜設ければよい。こうして、凸部を覆う絶縁膜の表面に形成された凸凹に沿って画素電極の表面に凸凹が形成される。

【0095】

また、第2の層間絶縁膜462として表面が平坦化する膜を用いてもよい。その場合は、画素電極を形成した後、公知のサンドブラスト法やエッチング法等の工程を追加して表面を凹凸化させて、鏡面反射を防ぎ、反射光を散乱させることによって白色度を増加させることが好ましい。

【0096】

そして、駆動回路506において、各不純物領域とそれぞれ電気的に接続する配線463〜467を形成する。なお、これらの配線は、膜厚50nmのTi膜と、膜厚500nmの合金膜(AlとTiとの合金膜)との積層膜をパターニングして形成する。

【0097】

また、画素部507においては、画素電極470、ゲート配線469、接続電極468を形成する。(図13)この接続電極468によりソース配線(443bと449の積層)は、画素TFTと電気的な接続が形成される。また、ゲート配線469は、画素TFTのゲート電極と電気的な接続が形成される。また、画素電極470は、画素TFTのドレイン領域442と電気的な接続が形成され、さらに保持容量を形成する一方の電極として機能する半導体層458と電気的な接続が形成される。また、画素電極470としては、AlまたはAgを主成分とする膜、またはそれらの積層膜等の反射性の優れた材料を用いることが望ましい。

【0098】

以上の様にして、nチャネル型TFT501とpチャネル型TFT502からなるCMOS回路、及びnチャネル型TFT503を有する駆動回路506と、画素TFT504、保持容量505とを有する画素部507を同一基板上に形成することができる。こうして、アクティブマトリクス基板が完成する。

【0099】

駆動回路506のnチャネル型TFT501はチャネル形成領域423c、ゲート電極の一部を構成する第1の導電層428aと重なる低濃度不純物領域423b(GOLD領域)、とソース領域またはドレイン領域として機能する高濃度不純物領域423aを有している。このnチャネル型TFT501と電極466で接続してCMOS回路を形成するpチャネル型TFT502にはチャネル形成領域446d、ゲート電極の外側に形成される不純物領域446b、446c、ソース領域またはドレイン領域として機能する高濃度不純物領域446aを有している。また、nチャネル型TFT503にはチャネル形成領域425c、ゲート電極の一部を構成する第1の導電層430aと重なる低濃度不純物領域425b(GOLD領域)、とソース領域またはドレイン領域として機能する高濃度不純物領域425aを有している。

【0100】

画素部の画素TFT504にはチャネル形成領域426c、ゲート電極の外側に形成される低濃度不純物領域426b(LDD領域)とソース領域またはドレイン領域として機能する高濃度不純物領域426aを有している。また、保持容量505の一方の電極として機能する半導体層447a、447bには、それぞれp型を付与する不純物元素が添加されている。保持容量505は、絶縁膜444を誘電体として、電極(438aと438bの積層)と、半導体層447a〜447cとで形成している。

【0101】

また、本実施例の画素構造は、ブラックマトリクスを用いることなく、画素電極間の隙間が遮光されるように、画素電極の端部をソース配線と重なるように配置形成する。

【0102】

また、本実施例で作製するアクティブマトリクス基板の画素部の上面図を図14に示す。なお、図10〜図13に対応する部分には同じ符号を用いている。図13中の鎖線A−A’は図14中の鎖線A―A’で切断した断面図に対応している。また、図13中の鎖線B−B’は図14中の鎖線B―B’で切断した断面図に対応している。

【0103】

なお、本実施例は実施例1乃至4と自由に組み合わせることが可能である。

【0104】

[実施例6]

本実施例では、実施例5で作製したアクティブマトリクス基板から、反射型液晶表示装置を作製する工程を以下に説明する。説明には図15を用いる。

【0105】

まず、実施例5に従い、図14の状態のアクティブマトリクス基板を得た後、図14のアクティブマトリクス基板上、少なくとも画素電極470上に配向膜567を形成しラビング処理を行なう。なお、本実施例では配向膜567を形成する前に、アクリル樹脂膜等の有機樹脂膜をパターニングすることによって基板間隔を保持するための柱状のスペーサ572を所望の位置に形成した。また、柱状のスペーサに代えて、球状のスペーサを基板全面に散布してもよい。

【0106】

次いで、対向基板569を用意する。次いで、対向基板569上に着色層570、571、平坦化膜573を形成する。赤色の着色層570と青色の着色層572とを重ねて、遮光部を形成する。また、赤色の着色層と緑色の着色層とを一部重ねて、遮光部を形成してもよい。

【0107】

本実施例では、実施例5に示す基板を用いている。従って、実施例5の画素部の上面図を示す図14では、少なくともゲート配線469と画素電極470の間隙と、ゲート配線469と接続電極468の間隙と、接続電極468と画素電極470の間隙を遮光する必要がある。本実施例では、それらの遮光すべき位置に着色層の積層からなる遮光部が重なるように各着色層を配置して、対向基板を貼り合わせた。

【0108】

このように、ブラックマスク等の遮光層を形成することなく、各画素間の隙間を着色層の積層からなる遮光部で遮光することによって工程数の低減を可能とした。

【0109】

次いで、平坦化膜573上に透明導電膜からなる対向電極576を少なくとも画素部に形成し、対向基板の全面に配向膜574を形成し、ラビング処理を施した。

【0110】

そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール材568で貼り合わせる。シール材568にはフィラーが混入されていて、このフィラーと柱状スペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料575を注入し、封止剤(図示せず)によって完全に封止する。液晶材料575には公知の液晶材料を用いれば良い。このようにして図15に示す反射型液晶表示装置が完成する。そして、必要があれば、アクティブマトリクス基板または対向基板を所望の形状に分断する。さらに、対向基板のみに偏光板(図示しない)を貼りつけた。そして、公知の技術を用いてFPCを貼りつけた。

【0111】

以上のようにして作製される液晶表示パネルは各種電子機器の表示部として用いることができる。

【0112】

なお、本実施例は実施例1乃至5と自由に組み合わせることが可能である。

【0113】

[実施例7]

本実施例では、本発明を用いて発光装置を作製した例について説明する。発光装置とは、電場を加えることで発生するルミネッセンスが得られる有機化合物を含む層(発光素子)を光源とする装置である。有機化合物における発光素子には、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)がある。なお、図16は本実施例の発光装置の断面図である。

【0114】

図16において、基板700上に設けられたスイッチングTFT603は図16のnチャネル型TFT503を用いて形成される。したがって、構造の説明はnチャネル型TFT503の説明を参照すれば良い。

【0115】

なお、本実施例ではチャネル形成領域が二つ形成されるダブルゲート構造としているが、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。

【0116】

基板700上に設けられた駆動回路は図16のCMOS回路を用いて形成される。従って、構造の説明はnチャネル型TFT501とpチャネル型TFT502の説明を参照すれば良い。なお、本実施例ではシングルゲート構造としているが、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

【0117】

また、配線701、703はCMOS回路のソース配線、702はドレイン配線として機能する。また、配線704はソース配線708とスイッチングTFTのソース領域とを電気的に接続する配線として機能し、配線705はドレイン配線709とスイッチングTFTのドレイン領域とを電気的に接続する配線として機能する。

【0118】

なお、電流制御TFT604は図16のpチャネル型TFT502を用いて形成される。従って、構造の説明はpチャネル型TFT502の説明を参照すれば良い。なお、本実施例ではシングルゲート構造としているが、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

【0119】

また、配線706は電流制御TFTのソース配線(電流供給線に相当する)であり、707は電流制御TFTの画素電極710上に重ねることで画素電極710と電気的に接続する電極である。

【0120】

なお、710は、透明導電膜からなる画素電極(発光素子の陽極)である。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したものを用いても良い。画素電極710は、上記配線を形成する前に平坦な層間絶縁膜711上に形成する。本実施例においては、樹脂からなる平坦化膜711を用いてTFTによる段差を平坦化することは非常に重要である。後に形成される発光層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、発光層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

【0121】

配線701〜707を形成後、図16に示すようにバンク712を形成する。バンク712は100〜400nmの珪素を含む絶縁膜もしくは有機樹脂膜をパターニングして形成すれば良い。

【0122】

なお、バンク712は絶縁膜であるため、成膜時における素子の静電破壊には注意が必要である。本実施例ではバンク712の材料となる絶縁膜中にカーボン粒子や金属粒子を添加して抵抗率を下げ、静電気の発生を抑制する。この際、抵抗率は1×106〜1×1012Ωm(好ましくは1×108〜1×1010Ωm)となるようにカーボン粒子や金属粒子の添加量を調節すれば良い。

【0123】

画素電極710の上には発光層713が形成される。なお、図16では一画素しか図示していないが、本実施例ではR(赤)、G(緑)、B(青)の各色に対応した発光層を作り分けている。また、本実施例では蒸着法により低分子系有機発光材料を形成している。具体的には、正孔注入層として20nm厚の銅フタロシアニン(CuPc)膜を設け、その上に発光層として70nm厚のトリス−8−キノリノラトアルミニウム錯体(Alq3)膜を設けた積層構造としている。Alq3にキナクリドン、ペリレンもしくはDCM1といった蛍光色素を添加することで発光色を制御することができる。

【0124】

但し、以上の例は発光層として用いることのできる有機発光材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせて発光層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。例えば、本実施例では低分子系有機発光材料を発光層として用いる例を示したが、高分子系有機発光材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機発光材料や無機材料は公知の材料を用いることができる。

【0125】

次に、発光層713の上には導電膜からなる陰極714が設けられる。本実施例の場合、導電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を用いれば良い。

【0126】

この陰極714まで形成された時点で発光素子715が完成する。なお、ここでいう発光素子715は、画素電極(陽極)710、発光層713及び陰極714で形成されたダイオードを指す。

【0127】

発光素子715を完全に覆うようにしてパッシベーション膜716を設けることは有効である。パッシベーション膜716としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いる。

【0128】

この際、カバレッジの良い膜をパッシベーション膜として用いることが好ましく、炭素膜、特にDLC(ダイヤモンドライクカーボン)膜を用いることは有効である。DLC膜は室温から100℃以下の温度範囲で成膜可能であるため、耐熱性の低い発光層713の上方にも容易に成膜することができる。また、DLC膜は酸素に対するブロッキング効果が高く、発光層713の酸化を抑制することが可能である。そのため、この後に続く封止工程を行う間に発光層713が酸化するといった問題を防止できる。

【0129】

さらに、パッシベーション膜716上に封止材717を設け、カバー材718を貼り合わせる。封止材717としては紫外線硬化樹脂を用いれば良く、内部に吸湿効果を有する物質もしくは酸化防止効果を有する物質を設けることは有効である。また、本実施例においてカバー材718はガラス基板や石英基板やプラスチック基板(プラスチックフィルムも含む)の両面に炭素膜(好ましくはダイヤモンドライクカーボン膜)を形成したものを用いる。

【0130】

こうして図16に示すような構造の発光装置が完成する。なお、バンク712を形成した後、パッシベーション膜716を形成するまでの工程をマルチチャンバー方式(またはインライン方式)の成膜装置を用いて、大気解放せずに連続的に処理することは有効である。また、さらに発展させてカバー材718を貼り合わせる工程までを大気解放せずに連続的に処理することも可能である。

【0131】

こうして、プラスチック基板を母体とする絶縁体501上にnチャネル型TFT601、602、スイッチングTFT(nチャネル型TFT)603および電流制御TFT(nチャネル型TFT)604が形成される。ここまでの製造工程で必要としたマスク数は、一般的なアクティブマトリクス型発光装置よりも少ない。

【0132】

即ち、TFTの製造工程が大幅に簡略化されており、歩留まりの向上および製造コストの低減が実現できる。

【0133】

さらに、図16を用いて説明したように、ゲート電極に絶縁膜を介して重なる不純物領域を設けることによりホットキャリア効果に起因する劣化に強いnチャネル型TFTを形成することができる。そのため、信頼性の高い発光装置を実現できる。

【0134】

また、本実施例では画素部と駆動回路の構成のみ示しているが、本実施例の製造工程に従えば、その他にも信号分割回路、D/Aコンバータ、オペアンプ、γ補正回路などの論理回路を同一の絶縁体上に形成可能であり、さらにはメモリやマイクロプロセッサをも形成しうる。

【0135】

さらに、発光素子を保護するための封止(または封入)工程まで行った後の本実施例の発光装置について図17を用いて説明する。なお、必要に応じて図16で用いた符号を引用する。

【0136】

図17(A)は、発光素子の封止までを行った状態を示す上面図、図17(B)は図17(A)をC−C’で切断した断面図である。点線で示された801はソース側駆動回路、806は画素部、807はゲート側駆動回路である。また、901はカバー材、902は第1シール材、903は第2シール材であり、第1シール材902で囲まれた内側には封止材907が設けられる。

【0137】

なお、904はソース側駆動回路801及びゲート側駆動回路807に入力される信号を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキット)905からビデオ信号やクロック信号を受け取る。なお、ここではFPCしか図示されていないが、このFPCにはプリント配線基盤(PWB)が取り付けられていても良い。本明細書における発光装置には、発光装置本体だけでなく、それにFPCもしくはPWBが取り付けられた状態をも含むものとする。

【0138】

次に、断面構造について図17(B)を用いて説明する。基板700の上方には画素部806、ゲート側駆動回路807が形成されており、画素部806は電流制御TFT604とそのドレインに電気的に接続された画素電極710を含む複数の画素により形成される。また、ゲート側駆動回路807はnチャネル型TFT601とpチャネル型TFT602とを組み合わせたCMOS回路(図14参照)を用いて形成される。

【0139】

画素電極710は発光素子の陽極として機能する。また、画素電極710の両端にはバンク712が形成され、画素電極710上には発光層713および発光素子の陰極714が形成される。

【0140】

陰極714は全画素に共通の配線としても機能し、接続配線904を経由してFPC905に電気的に接続されている。さらに、画素部806及びゲート側駆動回路807に含まれる素子は全て陰極714およびパッシベーション膜567で覆われている。

【0141】

また、第1シール材902によりカバー材901が貼り合わされている。なお、カバー材901と発光素子との間隔を確保するために樹脂膜からなるスペーサを設けても良い。そして、第1シール材902の内側には封止材907が充填されている。なお、第1シール材902、封止材907としてはエポキシ系樹脂を用いるのが好ましい。また、第1シール材902はできるだけ水分や酸素を透過しない材料であることが望ましい。さらに、封止材907の内部に吸湿効果をもつ物質や酸化防止効果をもつ物質を含有させても良い。

【0142】

発光素子を覆うようにして設けられた封止材907はカバー材901を接着するための接着剤としても機能する。また、本実施例ではカバー材901を構成するプラスチック基板901aの材料としてFRP(Fiberglass-Reinforced Plastics)、PVF(ポリビニルフロライド)、マイラー、ポリエステルまたはアクリルを用いることができる。

【0143】

また、封止材907を用いてカバー材901を接着した後、封止材907の側面(露呈面)を覆うように第2シール材903を設ける。第2シール材903は第1シール材902と同じ材料を用いることができる。

【0144】

以上のような構造で発光素子を封止材907に封入することにより、発光素子を外部から完全に遮断することができ、外部から水分や酸素等の発光層の酸化による劣化を促す物質が侵入することを防ぐことができる。従って、信頼性の高い発光装置が得られる。

【0145】

なお、本実施例は実施例1乃至5と自由に組み合わせることが可能である。

【0146】

[実施例8]

本発明を適用して、様々な電気光学装置(アクティブマトリクス型液晶表示装置、アクティブマトリクス型発光装置、アクティブマトリクス型EC表示装置)を作製することができる。即ち、それら電気光学装置を表示部に組み込んだ電子機器全てに本発明を実施できる。

【0147】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図18、図19及び図20に示す。

【0148】

図18(A)はパーソナルコンピュータであり、本体2001、画像入力部2002、表示部2003、キーボード2004等を含む。本発明を表示部2003に適用することができる。

【0149】

図18(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。本発明を表示部2102に適用することができる。

【0150】

図18(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205等を含む。本発明は表示部2205に適用できる。

【0151】

図18(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303等を含む。本発明は表示部2302に適用することができる。

【0152】

図18(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレイヤーであり、本体2401、表示部2402、スピーカ部2403、記録媒体2404、操作スイッチ2405等を含む。なお、このプレイヤーは記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行なうことができる。本発明は表示部2402に適用することができる。

【0153】

図18(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)等を含む。本発明を表示部2502に適用することができる。

【0154】

図19(A)はフロント型プロジェクターであり、投射装置2601、スクリーン2602等を含む。本発明は投射装置2601の一部を構成する液晶表示装置2808やその他の駆動回路に適用することができる。

【0155】

図19(B)はリア型プロジェクターであり、本体2701、投射装置2702、ミラー2703、スクリーン2704等を含む。本発明は投射装置2702の一部を構成する液晶表示装置2808やその他の駆動回路に適用することができる。

【0156】

なお、図19(C)は、図19(A)及び図19(B)中における投射装置2601、2702の構造の一例を示した図である。投射装置2601、2702は、光源光学系2801、ミラー2802、2804〜2806、ダイクロイックミラー2803、プリズム2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図19(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

【0157】

また、図19(D)は、図19(C)中における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801は、リフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構成される。なお、図19(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

【0158】

ただし、図19に示したプロジェクターにおいては、透過型の電気光学装置を用いた場合を示しており、反射型の電気光学装置及び発光装置での適用例は図示していない。

【0159】

図20(A)は携帯電話であり、本体2901、音声出力部2902、音声入力部2903、表示部2904、操作スイッチ2905、アンテナ2906等を含む。本発明を表示部2904に適用することができる。

【0160】

図20(B)は携帯書籍(電子書籍)であり、本体3001、表示部3002、3003、記憶媒体3004、操作スイッチ3005、アンテナ3006等を含む。本発明は表示部3002、3003に適用することができる。

【0161】

図20(C)はディスプレイであり、本体3101、支持台3102、表示部3103等を含む。本発明は表示部3103に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)のディスプレイには有利である。

【0162】

以上の様に、本発明の適用範囲は極めて広く、さまざまな分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1〜7のどのような組み合わせからなる構成を用いても実現することができる。

【0163】

【発明の効果】

本発明の構成を採用することにより、以下に示すような基本的有意性を得ることが出来る。

(a)従来のTFTの作製プロセスに適合した、簡単な方法である。

(b)結晶核の生成密度を制御することができる。

(c)結晶化の時間を短縮することができるため、工程時間の短縮を図ることができる。

(d)不純物元素の添加量を減らすことができる。

(e)以上の利点を満たした上で、良好な結晶性を有する結晶質半導体膜を形成することができ、その結晶質半導体膜を用いれば、電気的特性の優れたTFTを作製できる方法である。

【図面の簡単な説明】

【図1】 本発明が開示する結晶核の生成密度を制御する構成の一例を示す図。

【図2】 本発明が開示する結晶核の生成密度を制御する構成の一例を示す図。

【図3】 本発明が開示する結晶核の生成密度を制御する構成の一例を示す図。

【図4】 金属元素を用いた熱アニール法によって形成された結晶質珪素膜を示す図。

【図5】 図4の模式図。

【図6】 B(ボロン)のドーズ量を振って添加し、さらに金属元素を添加して熱アニール法によって形成された結晶質珪素膜を示す図。

【図7】 図6の模式図。

【図8】 P(リン)を添加し、さらに金属元素を添加して熱アニール法によって形成された結晶質珪素膜を示す図。

【図9】 図7の模式図。

【図10】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図11】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図12】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図13】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図14】 画素TFTの構成を示す上面図。

【図15】 アクティブマトリクス型液晶表示装置の作製工程を示す断面図。

【図16】 発光装置の駆動回路及び画素部の断面構造図。

【図17】 (A)発光装置の上面図。

(B)発光装置の駆動回路及び画素部の断面構造図。

【図18】 半導体装置の一例を示す図。

【図19】 半導体装置の一例を示す図。

【図20】 半導体装置の一例を示す図。

【図21】 B(ボロン)のドーズ量を振って添加し、さらに金属元素を添加して熱アニール法によって形成された結晶質珪素膜の結晶化率を示す図。

Claims (7)

- 非晶質半導体膜を形成する工程と、

前記非晶質半導体膜の少なくともチャネル形成領域、ソース領域、ドレイン領域及びLDD領域となる部分に硼素およびリンを添加する工程と、

前記硼素およびリンが添加された前記非晶質半導体膜に、前記非晶質半導体膜の結晶化を助長する元素を添加する工程と、

前記硼素およびリン、および前記結晶化を助長する元素が添加された前記非晶質半導体膜を加熱して結晶化して結晶質半導体膜を形成する工程と、

を有することを特徴とする半導体装置の作製方法。 - 請求項1において、

前記硼素及び前記リンは前記非晶質半導体膜の全面に添加されることを特徴とする半導体装置の作製方法。 - 請求項1又は2において、

前記非晶質半導体膜は珪素を含む膜であることを特徴とする半導体装置の作製方法。 - 請求項1乃至2のいずれか一項において、

前記硼素の濃度は1×1016〜5×1021/cm3であり、

前記リンの濃度は1×1016〜5×1021/cm3であることを特徴とする半導体装置の作製方法。 - 請求項1乃至2のいずれか一項において、

前記硼素の濃度は1×1016〜1×1018/cm3であり、

前記リンの濃度は1×1016〜1×1018/cm3であることを特徴とする半導体装置の作製方法。 - 請求項1乃至5のいずれか一項において、

前記結晶質半導体膜上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上にゲート電極を形成する工程と、

を有することを特徴とする半導体装置の作製方法。 - 請求項1乃至6のいずれか一項において、

前記結晶質半導体膜を形成する工程の後に、前記結晶質半導体膜を酸素雰囲気中で加熱して、前記結晶質半導体膜上に酸化膜を形成し、前記酸化膜中に前記硼素又はリンを取り込む工程と、

前記酸化膜を除去する工程と、

を有することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000382599A JP4968982B2 (ja) | 2000-12-15 | 2000-12-15 | 半導体装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000382599A JP4968982B2 (ja) | 2000-12-15 | 2000-12-15 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002184694A JP2002184694A (ja) | 2002-06-28 |

| JP2002184694A5 JP2002184694A5 (ja) | 2008-01-10 |

| JP4968982B2 true JP4968982B2 (ja) | 2012-07-04 |

Family

ID=18850396

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000382599A Expired - Lifetime JP4968982B2 (ja) | 2000-12-15 | 2000-12-15 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4968982B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5177784B2 (ja) * | 2005-08-25 | 2013-04-10 | 孝晏 望月 | 半導体結晶膜の製造方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3137797B2 (ja) * | 1993-03-12 | 2001-02-26 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタおよびその作製方法 |

| JP3405955B2 (ja) * | 1993-03-22 | 2003-05-12 | 株式会社半導体エネルギー研究所 | 半導体回路 |

| JP3486240B2 (ja) * | 1994-10-20 | 2004-01-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP3364081B2 (ja) * | 1995-02-16 | 2003-01-08 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3522441B2 (ja) * | 1996-03-12 | 2004-04-26 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP4044176B2 (ja) * | 1996-07-11 | 2008-02-06 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP3592535B2 (ja) * | 1998-07-16 | 2004-11-24 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3460962B2 (ja) * | 1999-01-21 | 2003-10-27 | シャープ株式会社 | 半導体装置の製造方法 |

-

2000

- 2000-12-15 JP JP2000382599A patent/JP4968982B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002184694A (ja) | 2002-06-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5227900B2 (ja) | 半導体装置の作製方法 | |

| JP4831885B2 (ja) | 半導体装置の作製方法 | |

| KR100803231B1 (ko) | 반도체장치 및 그의 제작방법 | |

| JP5078205B2 (ja) | レーザ照射装置 | |

| US7459354B2 (en) | Method for manufacturing a semiconductor device including top gate thin film transistor and method for manufacturing an active matrix device including top gate thin film transistor | |

| JP4869509B2 (ja) | 半導体装置の作製方法 | |

| KR100856840B1 (ko) | 반도체장치 제작방법 | |

| KR20020053760A (ko) | 레이저 어닐 방법 및 반도체장치 제작방법 | |

| JP2003152086A (ja) | 半導体装置 | |

| KR100871449B1 (ko) | 반도체장치 제작방법 | |

| JP4845309B2 (ja) | レーザアニール方法及び半導体装置の作製方法 | |

| JP5046439B2 (ja) | 半導体装置の作製方法 | |

| JP4827305B2 (ja) | 半導体装置の作製方法 | |

| JP5292453B2 (ja) | 半導体装置の作製方法 | |

| JP4748873B2 (ja) | 半導体装置の作製方法 | |

| JP5520911B2 (ja) | 半導体装置の作製方法 | |

| JP4968996B2 (ja) | 半導体装置の作製方法 | |

| JP4968982B2 (ja) | 半導体装置の作製方法 | |

| JP5222450B2 (ja) | レーザー照射装置及び半導体装置の作製方法 | |

| JP4255639B2 (ja) | 半導体装置の作製方法 | |

| JP4641598B2 (ja) | 半導体装置の作製方法 | |

| JP2002057344A (ja) | 半導体装置の作製方法 | |

| JP4677546B2 (ja) | 半導体装置の作製方法 | |

| JP4573953B2 (ja) | 半導体装置の作製方法 | |

| JP2002329668A (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071116 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071116 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110125 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110316 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110607 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120306 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120403 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150413 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4968982 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150413 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |