JP4907003B2 - アクティブマトリクス型表示装置およびそれを用いた電気器具 - Google Patents

アクティブマトリクス型表示装置およびそれを用いた電気器具 Download PDFInfo

- Publication number

- JP4907003B2 JP4907003B2 JP2000391869A JP2000391869A JP4907003B2 JP 4907003 B2 JP4907003 B2 JP 4907003B2 JP 2000391869 A JP2000391869 A JP 2000391869A JP 2000391869 A JP2000391869 A JP 2000391869A JP 4907003 B2 JP4907003 B2 JP 4907003B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- film

- display device

- active matrix

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Shift Register Type Memory (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本発明は、薄膜トランジスタ(以下、TFTという)をスイッチング素子に用いたアクティブマトリクス型表示装置に係り、特に前記表示装置の各画素における保持容量の構造に関する。

【0002】

【従来の技術】

アクティブマトリクス型表示装置の一つとして、TFT駆動方式の液晶表示装置が知られている。このTFT駆動方式の液晶表示装置は、ガラス等の透明基板上に形成されたTFTにより1画素ごとに液晶への印加を制御するため、画像が鮮明であり、OA機器やTV等に広く用いられている。また、文字や図形をより鮮明に表示するため、1画素のサイズを小さくして、いわゆる精細度を高くすることが要求されている。

【0003】

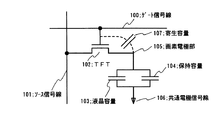

図1に、TFT駆動方式の液晶表示装置の1画素の等価回路図を示す。ゲート信号線100とソース信号線101との交差部にTFT102が配置され、このTFT102の負荷として液晶容量103と並列に保持容量104が接続されている。このため、ゲート信号線100の信号に応じてTFT102がON状態になると、ソース信号線101の電位は画素電極部105に書き込まれ、液晶容量103と保持容量104とに電荷が蓄積される。また、TFT102がOFF状態になると、液晶容量103に蓄積された電荷は保持されるが、保持容量104を並列に配置することにより、保持特性を向上することができる。

【0004】

また、保持容量104は、TFT102の動作時に生じる表示電極電圧のシフトを抑制する作用がある。即ち、ゲート信号線100とソース信号線101との重なり合う部分において、TFT102のON/OFFに従って寄生容量107の変化が生じる。そのため、保持容量104を並列に配置し全容量を増大させることにより、寄生容量107による直流成分の画素電極部105の電位への影響を緩和している。

【0005】

このような利点があることから、保持容量104はTFT駆動方式の液晶表示装置の画素に必須の回路要素となっている。

【0006】

図2は、従来の保持容量の一例を示す図である。ガラス基板200上に形成された活性層201およびゲート配線と同一膜で形成された容量配線203を電極として、その間に挟まれるように形成されたゲート絶縁膜と同一膜である誘電体202によって、保持容量を形成している。これは、ゲート絶縁膜を誘電体202として用いることにより、膜厚が薄くても非常に信頼性の高い良質の保持容量を形成することができるという利点がある。

【0007】

しかしながら、保持容量は、スイッチング素子となるTFTのチャネル幅とチャネル長との比率及び寄生容量等により1画素当たりに必要な値が決まり、誘電体の単位面積当たりの容量値から容量素子の面積が決定される。従って、実質的には必要な容量値に応じて、誘電体202の面積を制御することで必要な容量値を満たしている。

【0008】

従来技術では通常、保持容量は画素TFT領域の外部、即ち表示領域に形成されていた。このため、容量値の十分な確保のために容量素子が占める面積が画素部で増大し、画素の開口率の減少、光透過率の低下及びコントラストの低下を引き起こし、鮮明な画面表示ができなくなるという問題があった。特に、高精細度の表示装置を実現しようとすると、この欠点が顕著になる。

【0009】

【発明が解決しようとする課題】

本発明の第1の課題は、アクティブマトリクス型表示装置において、高解像度化に伴い1画素あたりの面積が縮小しても、十分な保持容量を確保できる容量素子構造を得ることにある。

【0010】

また、本発明の第2の課題は、アクティブマトリクス型表示装置において、開口率を低下させることなく、各画素の表示保持特性を向上することにある。

【0011】

また、本発明の第3の課題は、アクティブマトリクス型表示装置において、信頼性の高い容量素子の構造を得ることにある。

【0012】

そして、上記第1の課題、第2の課題及び第3の課題を全て解決することにより、高開口率でなおかつ保持容量の十分な表示装置を作製することを課題とする。

【0013】

さらに、TFTを同一基板上に集積化した表示装置(代表的には液晶表示装置または発光装置)のスループットおよび信頼性の向上を課題とする。また、同時に、本発明を用いて表示装置を作製することによって、その表示装置を用いた電気器具の信頼性をも向上することを課題とする。

【0014】

【課題を解決するための手段】

上記第1の課題を解決するためには、まず開口率に影響する表示領域には容量素子を形成しないことが必要である。そこで本発明者は、容量素子を画素TFT領域に形成することを考えた。さらに、画素TFT領域の面積を増大させることなく十分な保持容量を得るには、図3に示すように容量素子を画素TFT領域の下方に配置することによって課題を解決できる。

【0015】

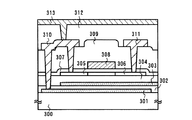

また第2の課題を解決するためには、上記第1の要件を満たすと共に、保持容量を1つ以上設ければよい。図4は、画素TFT領域の下方に第一配線301、第二配線303および第三配線314を用いた2つの保持容量を設けた例である。これにより、高解像度化に伴い各画素の面積が縮小しても、十分な面積を確保できるため、良好な保持特性を得ることができる。

【0016】

また、第3の課題を解決するためには、上記第1の要件及び第2の要件を満たすと共に、容量素子が画素TFT領域の下方に配置されることが必要である。下方に配置されることにより、誘電体には膜質向上のための十分な熱処理を行えるため信頼性の高い膜が得られる。

【0017】

また、この容量配線は遮光性を有する材質を用いることにより、光の入射による活性層(半導体膜)の劣化を低減することができる。

【0018】

【発明の実施の形態】

本発明による、保持容量を画素TFT領域の下方に配置する構造を実施した表示装置(液晶表示装置あるいは発光装置等)の作製プロセスについて図を用いて説明していく。

【0019】

【実施例】

[実施例1]

本発明の実施例について図5〜図7を用いて説明する。ここでは、アクティブマトリクス基板の作製方法、特に画素部を作製する方法について説明する。画素部は、画素に設けられたTFTである画素TFT領域と、TFT領域を含まない表示領域とからなる。

【0020】

図5(A)において、基板500には、ガラス基板や石英基板を使用することができる。その他にもシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを基板としても良い。耐熱性が許せばプラスチック基板を用いることも可能である。そして、後に画素TFT領域が形成される領域に、第一容量配線501として200nm厚のタンタル膜を島状に形成する。

【0021】

次に、第一容量配線501上に誘電体502を形成する。本実施例では、誘電体502として100〜200nmの厚さの窒化酸化珪素膜を用いる。また誘電体としては、珪素を含む酸化膜または窒化膜を用いることもできる。さらに、誘電体502上に第二容量配線503として、200nm厚のタンタル膜を島状に形成する(図5(B))。

【0022】

なお、第一容量配線および第二容量配線としては、タンタル膜以外にも、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素、または前記元素を組み合わせた合金膜(代表的にはMo−W合金、Mo−Ta合金)を用いることができる。

【0023】

また、本発明の容量素子は、画素TFT領域527の下方にあるため、外的ダメージによる欠陥を最小限に抑制できる。ここで外的ダメージによる欠陥とは、例えば、スペーサの局部的圧力によるクラック等をいう。

【0024】

次に、前記形成した容量配線501、503および誘電体502からなる容量素子と上方に形成されるTFTとを絶縁するための絶縁膜504として、酸化珪素膜を500〜900nmの厚さに形成する(図5(C))。連続して、絶縁膜504の上に20〜100nmの厚さの、非晶質半導体膜(本実施例では非晶質珪素膜(アモルファスシリコン膜))505を公知の成膜法で形成する。なお、非晶質半導体膜としては、非晶質珪素膜以外にも、非晶質珪素ゲルマニウム膜などの非晶質の化合物半導体膜を用いることもできる。

【0025】

そして、特開平7−130652号公報(USP5,643,826号に対応)に記載された技術に従って結晶構造を含む半導体膜(本実施例では結晶質珪素膜)506を形成する。同公報記載の技術は、非晶質珪素膜の結晶化に際して、結晶化を助長する触媒元素(ニッケル、コバルト、ゲルマニウム、錫、鉛、パラジウム、鉄、銅から選ばれた一種または複数の元素、代表的にはニッケル)を用いる結晶化手段である。

【0026】

具体的には、非晶質珪素膜表面に触媒元素を保持させた状態で加熱処理を行い、非晶質珪素膜を結晶質珪素膜に変化させるものである。本実施例では同公報の実施例1に記載された技術を用いるが、実施例2に記載された技術を用いてもよい。なお、結晶質珪素膜にはいわゆる単結晶珪素膜も多結晶珪素膜も含まれるが、本実施例で形成される結晶質珪素膜は結晶粒界を有する珪素膜である。

【0027】

非晶質珪素膜は含有水素量にもよるが、好ましくは400〜550℃で数時間加熱して脱水素処理を行い、含有水素量を5atom%以下として結晶化の工程を行うことが望ましい。また、非晶質珪素膜をスパッタ法や蒸着法などの他の作製法で形成しても良いが、膜中に含まれる酸素、窒素、などの不純物元素を十分に低減させておくことが望ましい。

【0028】

次に、非晶質珪素膜505に対して公知の技術を使って結晶質珪素膜(ポリシリコン膜又は多結晶珪素膜)506を形成する(図5(E))。本実施例では、非晶質珪素膜505に対してレーザーから発する光(レーザー光)を照射して結晶質珪素膜506を形成した。レーザーとしては、パルス発振型または連続発振型のエキシマレーザーを用いれば良いが、連続発振型のアルゴンレーザーでも良い。またはNd:YAGレーザーもしくはNd:YVO4レーザーの第2高調波、第3高調波または第4高調波を用いても良い。さらに、レーザー光のビーム形状は線状(長方形状も含む)であっても矩形状であっても構わない。

【0029】

また、レーザー光の代わりにランプから発する光(ランプ光)を照射(以下、ランプアニールという)しても良い。ランプ光としては、ハロゲンランプ、赤外ランプ等から発するランプ光を用いることができる。

【0030】

なお、このようにレーザー光またはランプ光により熱処理(アニール)を施す工程を光アニール工程という。光アニール工程は短時間で高温熱処理が行えるため、ガラス基板等の耐熱性の低い基板を用いる場合にも効果的な熱処理工程を高いスループットで行うことができる。勿論、目的はアニールであるので電熱炉を用いたファーネスアニール(熱アニールともいう)で代用することもできる。

【0031】

本実施例では、パルス発振型エキシマレーザー光を線状に加工してレーザーアニール工程を行う。レーザーアニール条件は、励起ガスとしてXeClガスを用い、処理温度を室温、パルス発振周波数を30Hzとし、レーザーエネルギー密度を250〜500mJ/cm2(代表的には350〜400mJ/cm2)とする。

【0032】

上記条件で行われるレーザーアニール工程は、熱結晶化後に残存した非晶質領域を完全に結晶化すると共に、既に結晶化された結晶質領域の欠陥等を低減する効果を有する。そのため、本工程は光アニールにより半導体膜の結晶性を改善する工程、または半導体膜の結晶化を助長する工程と呼ぶこともできる。このような効果はランプアニールの条件を最適化することによっても得ることが可能である。

【0033】

次に、結晶質珪素膜506上に後の不純物添加時のために保護膜507を形成する。保護膜507は100〜200nm(好ましくは130〜170nm)の厚さの窒化酸化珪素膜または酸化珪素膜を用いる。この保護膜507は不純物添加時に結晶質珪素膜506が直接プラズマに曝されないようにするためと、微妙な濃度制御を可能にするための意味がある。

【0034】

続いて、保護膜507を介してp型を付与する不純物元素(以下、p型不純物元素という)を添加する。p型不純物元素としては、代表的には周期表の13族に属する元素、典型的にはボロンまたはガリウムを用いることができる。この工程(チャネルドープ工程という)はTFTのしきい値電圧を制御するための工程である。なお、ここではジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加した。勿論、質量分離を行うイオンインプランテーション法を用いても良い。

【0035】

この工程により1×1015〜1×1018atoms/cm3(代表的には5×1016〜5×1017atoms/cm3)の濃度でp型不純物元素(本実施例ではボロン)を含む不純物領域508を形成する。なお、本明細書中では少なくとも上記濃度範囲でp型不純物元素を含む不純物領域をp型不純物領域(b)と定義する。(図5(F))

【0036】

次に、保護膜507を除去した後、結晶質珪素膜の不要な部分を除去して、島状の半導体膜(以下、活性層という)509を形成する。(図5(G))

【0037】

次に、活性層509を覆ってゲート絶縁膜510を形成した。ゲート絶縁膜510は、10〜200nm、好ましくは50〜150nmの厚さに形成すれば良い。本実施例では、プラズマCVD法でN2OとSiH4を原料とした窒化酸化珪素膜を115nmの厚さに形成する。(図6(A))

【0038】

次に、ゲート配線511として、図示しないが厚さ50nmの窒化タングステン(WN)と厚さ350nmのタンタル(Ta)との2層の積層膜を形成する(図6(B))。ゲート配線は単層の導電膜で形成してもよいが、必要に応じて2層、3層といった積層膜とすることが好ましい。

【0039】

また、本実施例では図6(B)に示すように、ダブルゲートとしている。ゲートのリーク対策としてマルチゲート方式を採用することは有効であり、さらに画素TFT領域の面積が十分に確保できるため、とくに本発明における容量素子の配置には適合した構造であるといえる。

【0040】

なお、ゲート配線としては、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素、または前記元素を組み合わせた合金膜(代表的にはMo−W合金、Mo−Ta合金)を用いることができる。

【0041】

次に、ゲート配線511をマスクとして自己整合的にn型不純物元素(本実施例ではリン)を添加する。こうして形成された不純物領域512には前述のチャネルドープ工程で添加されたボロン濃度よりも5〜10倍高い濃度(代表的には1×1016〜5×1018atoms/cm3、典型的には3×1017〜3×1018atoms/cm3)でリンが添加されるように調節する。なお、本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域をn型不純物領域(c)と定義する。(図6(C))

【0042】

なお、前述のp型不純物領域(b)508には既にチャネルドープ工程で1×1015〜1×1018atoms/cm3の濃度のボロンが添加されているが、この工程ではp型不純物領域(b)508に含まれるボロンの5〜10倍の濃度でリンが添加されるので、この場合もボロンはp型不純物領域(b)の機能には影響を与えないと考えて良い。

【0043】

次に、ゲート配線511をマスクとして自己整合的にゲート絶縁膜513をエッチングする。エッチングはドライエッチング法を用い、エッチングガスとしてはCHF3ガスを用いる。但し、エッチングガスはこれに限定する必要はない。こうしてゲート配線下にゲート絶縁膜513が形成される。(図6(D))

【0044】

このように活性層を露呈させることによって、次に不純物元素の添加工程を行う際に加速電圧を低くすることができる。また、必要なドーズ量が少なくて済むのでスループットが向上する。勿論、ゲート絶縁膜をエッチングしないで残し、スルードーピングによって不純物領域を形成しても良い。

【0045】

次に、ゲート配線を覆う形でレジストマスク514を形成し、n型不純物元素(本実施例ではリン)を添加して高濃度にリンを含む不純物領域515を形成する。ここでも、フォスフィン(PH3)を用いたイオンドープ法(勿論、イオンインプランテーション法でも良い)で行い、この領域のリンの濃度は1×1020〜1×1021atoms/cm3(代表的には2×1020〜5×1021atoms/cm3)とする。(図6(E))

【0046】

なお、本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域をn型不純物領域(a)と定義する。また、不純物領域515が形成された領域には既に前工程で添加されたリンまたはボロンが含まれるが、十分に高い濃度でリンが添加されることになるので、前工程で添加されたリンまたはボロンの影響は考えなくて良い。従って、本明細書中では不純物領域515はn型不純物領域(a)と言い換えても構わない。

【0047】

次に、レジストマスク514を除去した後、第1層間絶縁膜517を形成する。第1層間絶縁膜517としては、珪素を含む絶縁膜、具体的には窒化珪素膜、酸化珪素膜、窒化酸化珪素膜またはそれらを組み合わせた積層膜で形成すれば良い。また、膜厚は600nm〜1.5μmとすれば良い。本実施例では、プラズマCVD法でSiH4、N2O、NH3を原料ガスとし、1μm厚の窒化酸化珪素膜(但し窒素濃度が25〜50atomic%)を用いる。

【0048】

その後、それぞれの濃度で添加されたn型またはp型不純物元素を活性化するために熱処理工程を行う。この工程はファーネスアニール法、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)で行うことができる。ここではファーネスアニール法で活性化工程を行う。加熱処理は、窒素雰囲気中において300〜650℃、好ましくは400〜550℃、ここでは550℃、4時間の熱処理を行う(図6(F))。

【0049】

この時、本実施例において非晶質珪素膜の結晶化に用いた触媒元素(本実施例ではニッケル)が、矢印で示す方向に移動して、前述の図6(E)の工程で形成された高濃度にリンを含む領域515に捕獲(ゲッタリング)される。これはリンによる金属元素のゲッタリング効果に起因する現象であり、この結果、後のチャネル形成領域516は前記触媒元素の濃度が1×1017atoms/cm3以下(好ましくは1×1016atoms/cm3以下)となる。

【0050】

また逆に触媒元素のゲッタリングサイトとなった領域(図6(E)の工程で形成された不純物領域515)は高濃度に触媒元素が偏析して5×1018atoms/cm3以上(代表的には1×1019〜5×1020atoms/cm3)の濃度で存在するようになる。

【0051】

さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、活性層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

【0052】

その後、第一容量配線501、TFTのソース領域及びドレイン領域に達するスルーホール518〜520を形成し(図7(A))、ソース配線521とドレイン配線522を形成する(図7(B))。本実施例では、ドレイン配線522が容量配線501、ドレイン領域および画素電極と導通をとるための配線として形成される構造であるがこの限りではなく、実施例3で異なる構造の一つを示す。また、図示していないが、本実施例ではこの配線を、Ti膜を100nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とする。

【0053】

次に、パッシベーション膜523として、窒化珪素膜、酸化珪素膜、または窒化酸化珪素膜で50〜500nm(代表的には200〜300nm)の厚さで形成する。この時、本実施例では膜の形成に先立ってH2、NH3等水素を含むガスを用いてプラズマ処理を行い、成膜後に熱処理を行う。この前処理により励起された水素が第1層間絶縁膜中に供給される。この状態で熱処理を行うことで、パッシベーション膜523の膜質を改善するとともに、第1層間絶縁膜中に添加された水素が下方側に拡散するため、効果的に活性層を水素化することができる。(図7(C))

【0054】

また、パッシベーション膜523を形成した後に、さらに水素化工程を行っても良い。例えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られる。なお、ここで後に画素電極とドレイン配線を接続するためのスルーホールを形成する位置において、パッシベーション膜523に開口部を形成しておいても良い。

【0055】

その後、有機樹脂からなる第2層間絶縁膜524を約1μmの厚さに形成する。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成する。

【0056】

次に、第2層間絶縁膜524及びパッシベーション膜523にドレイン配線522に達するスルーホールを形成し、画素電極526を形成する。画素電極526は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウムと酸化スズとの化合物からなる酸化物導電膜(ITO膜)を110nmの厚さにスパッタ法で形成する。

【0057】

こうして画素部には、表示部528の面積即ち開口率を低下させることなく、nチャネル型TFTでなる画素TFT領域527が形成され、十分な保持容量を得ることができる。また、この容量配線には、遮光性を有する材質を用いることによって、光の入射による活性層の劣化を低減できる。(図7(D))なお、図15のA−A’が図7(D)のA−A’に対応する。

【0058】

[実施例2]

本実例では、実施例1で作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。図8に示すように、図7(D)の状態の基板に対し、配向膜801を形成する。本実施例では配向膜としてポリイミド膜を用いた。また、対向基板802には、透明導電膜803と、配向膜804とを形成する。なお、対向基板には必要に応じてカラーフィルターや遮蔽膜を形成しても良い。

【0059】

次に、配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにする。そして、画素部と、駆動回路が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。その後、両基板の間に液晶805を注入し、封止剤(図示せず)によって完全に封止する。液晶には公知の液晶材料を用いれば良い。このようにして図8に示すアクティブマトリクス型液晶表示装置が完成する。

【0060】

次に、このアクティブマトリクス型液晶表示装置の構成を、図9の斜視図を用いて説明する。尚、図9は、図5〜図8の断面構造図と対応付けるため、共通の符号を用いている。アクティブマトリクス基板は、ガラス基板500上に形成された、画素部806と、ゲート信号駆動回路807と、画像(ソース)信号駆動回路808で構成される。画素TFT領域813はnチャネル型TFTであり、周辺に設けられる駆動回路はCMOS回路を基本として構成されている。ゲート信号駆動回路807と、画像信号駆動回路808はそれぞれゲート配線511とソース配線521で画素部806に接続されている。また、FPC809が接続された外部入出力端子810から駆動回路の入出力端子までの接続配線811、812が設けられている。

【0061】

[実施参考例3]

本実施参考例では、実施例1とは異なる構造で画素TFTを作製する場合について、図10を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることにする。

【0062】

ます実施例1の工程に従って、絶縁膜504までを形成する。そして、絶縁膜504をエッチング開孔し、第一容量配線501に接続されるスルーホール(開孔部)1001を形成する(図10(A))。

【0063】

次に、絶縁膜504の上に20〜100nmの厚さの、非晶質半導体膜(本実施参考例では非晶質珪素膜(アモルファスシリコン膜))505を公知の成膜法で形成する(図10(B))。なお、非晶質半導体膜としては、非晶質珪素膜以外にも、非晶質珪素ゲルマニウム膜などの非晶質の化合物半導体膜を用いることもできる。

【0064】

本実施参考例では、第一容量配線501に接続される配線を結晶質珪素で形成することを特徴としている。実施例1では、ソース領域およびドレイン領域に到達するスルーホール形成時に、第一容量配線501に到達するスルーホールを同時に形成しなければならないが、本実施参考例ではこれを分けて行うことによりエッチングプロセスをより容易なものとすることができる。

【0065】

この後は、実施例1の工程に従って図5(D)以降の工程に従えばよい。また、本実施参考例の構成を実施例2のアクティブマトリクス型液晶表示装置を作製する際に実施できる。

【0066】

[実施参考例4]

本実施参考例では、本参考発明を用いて発光装置としてEL(エレクトロルミネセンス)表示装置を作製した例について説明する。発光装置とは、電場を加えることで発生するルミネッセンスが得られる有機化合物を含む層(発光素子)を光源とする装置である。有機化合物における発光素子には、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)がある。なお、図11は本参考発明のEL表示装置の上面図であり、図12はその断面図である。

【0067】

図11、12において、4001は基板、4002は画素部、4003はソース側駆動回路、4004はゲート側駆動回路であり、それぞれの駆動回路は配線4005を経てFPC(フレキシブルプリントサーキット)4006に至り、外部機器へと接続される。

【0068】

このとき、画素部4002、ソース側駆動回路4003及びゲート側駆動回路4004を囲むようにして第1シール材4101、カバー材4102、充填材4103及び第2シール材4104が設けられている。

【0069】

また、図12は、図11をB−B’で切断した断面図に相当し、基板4001の上にソース側駆動回路4003に含まれる駆動TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを図示している。)4201及び画素部4002に含まれる画素TFT(但し、ここではEL素子への電流を制御するTFTを図示している。)4202が形成されている。

【0070】

本実施参考例では、本参考発明の容量素子構造を用いて画素TFT4202が作製される。すなわち、画素TFT4202には図7(D)の画素部と同じ構造のTFTが用いられる。

【0071】

駆動TFT4201及び画素TFT4202の上には樹脂材料でなる層間絶縁膜(平坦化膜)4301が形成され、その上に画素TFT4202のドレインと電気的に接続する画素電極(陽極)4302が形成される。画素電極4302としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物または酸化インジウムと酸化亜鉛との化合物を用いることができる。

【0072】

そして、画素電極4302の上には絶縁膜4303が形成され、絶縁膜4303は画素電極4302の上に開口部が形成されている。この開口部において、画素電極4302の上にはEL層4304が形成される。EL層4304は公知の有機EL材料または無機EL材料を用いることができる。また、有機EL材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

【0073】

EL層4304の形成方法は公知の技術を用いれば良い。また、EL層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

【0074】

EL層4304の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4305が形成される。また、陰極4305とEL層4304の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中で両者を連続成膜するか、EL層4304を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4305を形成するといった工夫が必要である。本実施参考例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

【0075】

そして陰極4305は4306で示される領域において配線4005に電気的に接続される。配線4005は陰極4305に所定の電圧を与えるための配線であり、導電性材料4307を介してFPC4006に電気的に接続される。

【0076】

以上のようにして、画素電極(陽極)4302、EL層4304及び陰極4305からなるEL素子が形成される。このEL素子は、第1シール材4101及び第1シール材4101によって基板4001に貼り合わされたカバー材4102で囲まれ、充填材4103により封入されている。

【0077】

カバー材4102としては、ガラス板、金属板(代表的にはステンレス板)、セラミックス板、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

【0078】

但し、EL素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

【0079】

また、充填材4103としては紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材4103の内部に吸湿性物質(好ましくは酸化バリウム)を設けておくとEL素子の劣化を抑制できる。

【0080】

また、充填材4103の中にスペーサを含有させてもよい。このとき、スペーサを酸化バリウムで形成すればスペーサ自体に吸湿性をもたせることが可能である。また、スペーサを設けた場合、スペーサからの圧力を緩和するバッファ層として陽極4305上に樹脂膜を設けることも有効である。

【0081】

また、配線4005は導電性材料4305を介してFPC4006に電気的に接続される。配線4005は画素部4002、ソース側駆動回路4003及びゲート側駆動回路4004に送られる信号をFPC4006に伝え、FPC4006により外部機器と電気的に接続される。

【0082】

また、本実施参考例では第1シール材4101の露呈部及びFPC4006の一部を覆うように第2シール材4104を設け、EL素子を徹底的に外気から遮断する構造となっている。こうして図12の断面構造を有するEL表示装置となる。なお、本実施参考例のEL表示装置は実施例1の構成と組み合わせて作製しても構わない。

【0083】

[実施例5]

本実施例では、実施例1とは異なる構造で画素TFTを作製する場合について、図13を用いて説明する。なお、実施例1とは途中の工程が異なるだけでその他は同様であるので、同じ工程については同一の符号を用いることにする。

【0084】

ます実施例1の工程に従って、第二容量配線503までを形成する(図13(A))。そして、第二容量配線503上に第二誘電体1301を形成し、第一容量配線501に到達するスルーホール(開孔部)1302を形成する(図13(B))。なお、本実施例では、第二誘電体1301として100〜200nmの厚さの窒化酸化珪素膜を用いる。

【0085】

次に、第二誘電体1301上に第三容量配線1303を形成する。これにより、第三容量配線1303は第一容量配線501と電気的に接続される。また、本実施例では第三容量配線1303として、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素、または前記元素を組み合わせた合金膜(代表的にはMo−W合金、Mo−Ta合金)を用いることができる(図13(C))。

【0086】

この後は、実施例1の工程に従って図5(D)以降の工程に従えばよい。ただし、本実施例では、ドレイン配線522は第二容量配線503と接続される。

【0087】

本実施例では、画素TFT領域527と基板500との間に電気的に並列な2つの保持容量を形成している(図13(E))。一つ目は、第一誘電体502と、前記第一誘電体502をはさむ第一容量配線501および第二容量配線503とからなる第一保持容量であり、二つ目は、第二誘電体1301と、前記第二誘電体1301をはさむ第二容量配線503および第三容量配線1303とからなる第二保持容量である。すなわち、画素TFTと接続される第二容量配線503は、第一保持容量と第二保持容量における共通の配線となっている。

【0088】

このように、2つ以上の保持容量を電気的に並列に配置することにより、より大きい保持容量を得られる。このため、高精細化が進み1画素あたりの面積が縮小しても、開口率を損ねることなく十分な保持容量を得ることができる。なお、本実施例の構成を実施例2のアクティブマトリクス型液晶表示装置を作製する際にも実施できる。

【0089】

[実施参考例6]

本参考発明の電子装置は電気器具の表示部として用いることができる。そのような電気器具としては、ビデオカメラ、デジタルカメラ、プロジェクター、プロジェクションTV、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置などが挙げられる。それら電気器具の具体例を図14に示す。

【0090】

図14(A)は携帯電話であり、本体2001、音声出力部2002、音声入力部2003、表示部2004、操作スイッチ2005、アンテナ2006で構成される。本参考発明の電子装置は表示部2004に用いることができる。

【0091】

図14(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本参考発明の電子装置は表示部2102に用いることができる。

【0092】

図14(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205で構成される。本参考発明の電子装置は表示部2205に用いることができる。

【0093】

図14(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303で構成される。本参考発明の電子装置は表示部2302に用いることができる。

【0094】

図14(E)はリアプロジェクター(プロジェクションTV)であり、本体2401、光源2402、液晶表示装置2403、偏光ビームスプリッタ2404、リフレクター2405、2406、スクリーン2407で構成される。本参考発明は液晶表示装置2403に用いることができる。

【0095】

図14(F)はフロントプロジェクターであり、本体2501、光源2502、液晶表示装置2503、光学系2504、スクリーン2505で構成される。本参考発明は液晶表示装置2503に用いることができる。

【0096】

以上の様に、本参考発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用することが可能である。また、本実施参考例の電気器具は実施例1、2、5及び実施参考例3、4、6のどのような組み合わせからなる構成を用いても実現することができる。

【0097】

【発明の効果】

本発明を用いた保持容量を有するアクティブマトリクス型表示装置を作製すれば、1画素の面積が縮小しても十分な保持容量の確保が可能であるため、表示品位を向上できるだけでなく前記表示装置を高精細化することができる。

【0098】

さらに本発明を用いた液晶表示装置をはじめとする表示装置の保持特性を向上すると共に信頼性を向上できる。また同時に、本発明を用いた電子装置を作製することによって、前記電子装置を表示部として用いた電気器具の品質および信頼性をも向上させることができる。

【図面の簡単な説明】

【図1】 液晶表示装置の1画素の等価回路を示す図。

【図2】 従来の保持容量構造を示す断面図。

【図3】 本発明における保持容量の構造を示す図。

【図4】 本発明における保持容量の構造を示す図。

【図5】 実施例1の画素部の作製工程を示す図。

【図6】 実施例1の画素部の作製工程を示す図。

【図7】 実施例1の画素部の作製工程を示す図。

【図8】 アクティブマトリクス型液晶表示装置の断面図。

【図9】 アクティブマトリクス型液晶表示装置の斜視図。

【図10】 実施例3の画素部の作製工程を示す図。

【図11】 アクティブマトリクス型EL表示装置の構成を示す図。

【図12】 アクティブマトリクス型EL表示装置の構成を示す図。

【図13】 実施例5の画素部の作製工程を示す図。

【図14】 電気器具の一例を示す図。

【図15】 画素部の上面図。

Claims (8)

- 基板の上方に、半導体膜と、前記半導体膜に近接するゲートと、前記半導体膜と前記ゲートとの間にゲート絶縁膜とを有する画素トランジスタと、前記基板と前記画素トランジスタとの間に複数の保持容量と、を有し、

前記複数の保持容量は、前記基板に対して垂線方向に並んでおり、

前記複数の保持容量は、前記基板の上方に第1の保持容量と、前記第1の保持容量の上方に第2の保持容量とを有し、

前記第1の保持容量は、前記基板の上方に第1の配線と、前記第1の配線の上方に第1の誘電体と、前記第1の誘電体の上方に第2の配線とを有し、

前記第2の保持容量は、前記第2の配線と、前記第2の配線の上方に第2の誘電体と、前記第2の誘電体の上方に第3の配線とを有することを特徴とするアクティブマトリクス型表示装置。 - 基板の上方に第1の配線と、

前記第1の配線の上方に第1の絶縁膜と、

前記第1の絶縁膜の上方に第2の配線と、

前記第2の配線の上方に第2の絶縁膜と、

前記第2の絶縁膜の上方に第3の配線と、

前記第3の配線の上方に第3の絶縁膜と、

前記第3の絶縁膜の上方に、半導体膜と、

前記半導体膜に近接するゲートと、

前記半導体膜と前記ゲートとの間にゲート絶縁膜とを有する画素トランジスタと、

前記基板と前記画素トランジスタとの間に複数の保持容量と、を有し、

前記複数の保持容量は、前記基板に対して垂線方向に並んでいることを特徴とするアクティブマトリクス型表示装置。 - 請求項1または請求項2において、

前記半導体膜は、前記第2の配線と電気的に接続されていることを特徴とするアクティブマトリクス型表示装置 - 請求項1乃至3のいずれか一において、

前記第3の配線は、前記第1の配線と電気的に接続されていることを特徴とするアクティブマトリクス型表示装置。 - 請求項1乃至4のいずれか一において、

前記第1の配線、前記第2の配線または前記第3の配線には、遮光性を有する材料が用いられることを特徴とするアクティブマトリクス型表示装置。 - 請求項1乃至4のいずれか一において、

前記第1の配線、前記第2の配線および前記第3の配線には、タンタル、チタン、モリブデン、タングステン、クロム、シリコンから選ばれた元素、または前記元素を組み合わせた合金膜が用いられることを特徴とするアクティブマトリクス型表示装置。 - 請求項1乃至6のいずれか一において、

前記アクティブマトリクス型表示装置は、アクティブマトリクス型EL表示装置であることを特徴とするアクティブマトリクス型表示装置。 - 請求項1乃至7のいずれか一において、

前記アクティブマトリクス型表示装置を表示部に用いたことを特徴とする電気器具。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000391869A JP4907003B2 (ja) | 1999-12-27 | 2000-12-25 | アクティブマトリクス型表示装置およびそれを用いた電気器具 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP1999369935 | 1999-12-27 | ||

| JP36993599 | 1999-12-27 | ||

| JP11-369935 | 1999-12-27 | ||

| JP2000391869A JP4907003B2 (ja) | 1999-12-27 | 2000-12-25 | アクティブマトリクス型表示装置およびそれを用いた電気器具 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001249362A JP2001249362A (ja) | 2001-09-14 |

| JP2001249362A5 JP2001249362A5 (ja) | 2009-01-08 |

| JP4907003B2 true JP4907003B2 (ja) | 2012-03-28 |

Family

ID=26582171

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000391869A Expired - Fee Related JP4907003B2 (ja) | 1999-12-27 | 2000-12-25 | アクティブマトリクス型表示装置およびそれを用いた電気器具 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4907003B2 (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003152086A (ja) * | 2001-11-15 | 2003-05-23 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US7045861B2 (en) * | 2002-03-26 | 2006-05-16 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device, liquid-crystal display device and method for manufacturing same |

| KR100462861B1 (ko) * | 2002-04-15 | 2004-12-17 | 삼성에스디아이 주식회사 | 블랙매트릭스를 구비한 평판표시장치 및 그의 제조방법 |

| JP4732294B2 (ja) * | 2003-02-12 | 2011-07-27 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US7528643B2 (en) | 2003-02-12 | 2009-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic device having the same, and driving method of the same |

| CN1307479C (zh) * | 2003-07-10 | 2007-03-28 | 友达光电股份有限公司 | 电容器装置 |

| JP4324441B2 (ja) * | 2003-10-09 | 2009-09-02 | シャープ株式会社 | 素子基板、表示装置 |

| US8115206B2 (en) * | 2005-07-22 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| CN102859605A (zh) * | 2010-04-28 | 2013-01-02 | 夏普株式会社 | 移位寄存器和显示装置 |

| WO2011145468A1 (en) | 2010-05-21 | 2011-11-24 | Semiconductor Energy Laboratory Co., Ltd. | Memory device and semiconductor device |

| FR2965942B1 (fr) * | 2010-10-08 | 2013-02-22 | Commissariat Energie Atomique | Afficheur a cristal liquide de type transmissif en technologie cmos avec capacite de stockage auxiliaire |

| JP2012119532A (ja) * | 2010-12-01 | 2012-06-21 | Seiko Epson Corp | 薄膜トランジスタ形成用基板、半導体装置、電気装置 |

| JP5909919B2 (ja) * | 2011-08-17 | 2016-04-27 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP2015094880A (ja) * | 2013-11-13 | 2015-05-18 | セイコーエプソン株式会社 | 電気光学装置、および電子機器 |

| JP6169005B2 (ja) * | 2014-01-17 | 2017-07-26 | 株式会社ジャパンディスプレイ | 発光素子表示装置 |

| KR102296945B1 (ko) * | 2014-07-04 | 2021-09-01 | 엘지디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR102465381B1 (ko) * | 2015-12-14 | 2022-11-10 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| KR102928365B1 (ko) * | 2016-05-31 | 2026-02-13 | 엘지디스플레이 주식회사 | 유기발광 표시장치 및 그의 제조방법 |

| KR20200098723A (ko) | 2018-01-11 | 2020-08-20 | 어플라이드 머티어리얼스, 인코포레이티드 | 금속 산화물 스위치를 갖는 작은 저장 커패시터를 갖는 박막 트랜지스터 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2616160B2 (ja) * | 1990-06-25 | 1997-06-04 | 日本電気株式会社 | 薄膜電界効果型トランジスタ素子アレイ |

| JPH0824193B2 (ja) * | 1990-10-16 | 1996-03-06 | 工業技術院長 | 平板型光弁駆動用半導体装置の製造方法 |

| JPH08184852A (ja) * | 1994-12-27 | 1996-07-16 | Sharp Corp | アクティブマトリクス型表示装置 |

| JP2720862B2 (ja) * | 1995-12-08 | 1998-03-04 | 日本電気株式会社 | 薄膜トランジスタおよび薄膜トランジスタアレイ |

| JP3433779B2 (ja) * | 1996-06-19 | 2003-08-04 | シャープ株式会社 | アクティブマトリクス基板およびその製造方法 |

| JP4403329B2 (ja) * | 1999-08-30 | 2010-01-27 | ソニー株式会社 | 液晶表示装置の製造方法 |

-

2000

- 2000-12-25 JP JP2000391869A patent/JP4907003B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001249362A (ja) | 2001-09-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6590227B2 (en) | Active matrix display device | |

| US9035314B2 (en) | Method for manufacturing an electrooptical device | |

| JP5648019B2 (ja) | 表示装置の作製方法 | |

| JP4907003B2 (ja) | アクティブマトリクス型表示装置およびそれを用いた電気器具 | |

| US6542205B2 (en) | Display device | |

| US20010053559A1 (en) | Method of fabricating display device | |

| JP4896314B2 (ja) | 表示装置 | |

| JP5121103B2 (ja) | 半導体装置、半導体装置の作製方法及び電気器具 | |

| JP2002319679A (ja) | 半導体装置 | |

| JPH11112002A (ja) | 半導体装置およびその製造方法 | |

| JP2000349298A (ja) | 電気光学装置およびその作製方法 | |

| JP2001284342A (ja) | 電気光学装置の作製方法 | |

| JP4850763B2 (ja) | 半導体装置の作製方法 | |

| JP5422626B2 (ja) | 半導体装置 | |

| CN100550398C (zh) | 半导体器件及其制造方法 | |

| JP4641586B2 (ja) | 半導体装置の作製方法 | |

| JP4963158B2 (ja) | 表示装置の作製方法、電気光学装置の作製方法 | |

| JP4700159B2 (ja) | 半導体装置の作製方法 | |

| JP2013157611A (ja) | 半導体装置 | |

| JP5159005B2 (ja) | 半導体装置の作製方法 | |

| JP2017004013A (ja) | 半導体装置 | |

| JP2005148728A (ja) | 集積回路 | |

| JP2018159938A (ja) | 液晶表示装置 | |

| JP2014081645A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071221 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110607 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110720 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111011 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111122 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120110 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |