JP4904670B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4904670B2 JP4904670B2 JP2004164857A JP2004164857A JP4904670B2 JP 4904670 B2 JP4904670 B2 JP 4904670B2 JP 2004164857 A JP2004164857 A JP 2004164857A JP 2004164857 A JP2004164857 A JP 2004164857A JP 4904670 B2 JP4904670 B2 JP 4904670B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- semiconductor element

- conductor layer

- opening

- supply line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/528—Layout of the interconnection structure

- H01L23/5286—Arrangements of power or ground buses

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/03—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/023—Redistribution layers [RDL] for bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01014—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01028—Nickel [Ni]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19042—Component type being an inductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19043—Component type being a resistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Geometry (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Wire Bonding (AREA)

Description

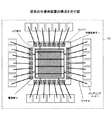

2 電極パッド

4 電源線

5 コア部

7 ボンディングリード

8 ワイヤ

10 従来の半導体装置

11、11a、11b 半導体素子

12 電極パッド

12a、12b バンプ

13 開口部

14 電源線

15 配線層

15a 絶縁膜

16 導体層

17 ボンディングリード

18 ワイヤ

19 基板

20 半導体装置

21 配線基板

21a ダイ付材

22 基板

23 接続端子

24 接続端子

27 リード

28 TABテープ

29 電源用リード

30 半導体装置

40 半導体装置

Claims (5)

- 中央に設けた回路部が外部からの電源を供給するための電源用電極と電源線により接続された半導体素子と、

前記半導体素子を搭載すると共に、前記半導体素子を取り囲む領域に配設した第1の接続端子が前記電源用電極と電気的に接合された基板と、

前記回路部の中央に配置された電源線上に形成された第1の開口部と、

前記回路部の外周部に配置された電源線上に形成された第2の開口部と、

前記基板上の前記半導体素子を取り囲む前記領域に配設した第2の接続端子と電気的に接合されると共に、前記第1の開口部における電源線と前記第2の開口部における電源線とを互いに接続する導体層と

を備え、前記導体層が前記回路部の中央及び外周部を含む全面を覆うように前記半導体素子上に形成され、前記基板の前記第1の接続端子がワイヤにより前記半導体素子の前記電源用電極と接合され、かつ、前記基板の前記第2の接続端子がワイヤにより前記半導体素子の前記導体層と接合されることにより、動作時に前記第1の開口部と前記導体層とを介して前記半導体素子の前記回路部の中央に供給される電源電流を増加させることを特徴とする半導体装置。 - 中央に設けた回路部が外部からの電源を供給するための電源用バンプと電源線により接続された半導体素子と、

前記半導体素子を搭載すると共に、前記半導体素子上の前記電源用バンプと対向する領域に配設した第1の接続端子が前記電源用バンプと電気的に接合された基板と、

前記回路部の中央に配置された電源線上に形成された第1の開口部と、

前記回路部の外周部に配置された電源線上に形成された第2の開口部と、

前記基板上の前記回路部と対向する領域に配設した第2の接続端子と電気的に接合されると共に、前記第1の開口部における電源線と前記第2の開口部における電源線とを互いに接続する導体層と

を備え、前記導体層が前記回路部の中央及び外周部を含む全面を覆うように前記半導体素子上に形成され、前記基板の前記第1の接続端子中の、電源と接続された電源用接続端子がそれぞれ対向する前記半導体素子の前記電源用バンプと電気的に接合され、かつ、前記基板の前記第2の接続端子が前記半導体素子の前記導体層と電気的に接合されることにより、動作時に前記第1の開口部と前記導体層とを介して前記半導体素子の前記回路部の中央に供給される電源電流を増加させることを特徴とする半導体装置。 - 中央に設けた回路部が外部からの電源を供給するための電源用バンプと電源線により接続された半導体素子と、

前記半導体素子を搭載すると共に、前記半導体素子を取り囲む領域に配設した第1のリードが前記電源用バンプと電気的に接合されたTABテープと、

前記回路部の中央に配置された電源線上に形成された第1の開口部と、

前記回路部の外周部に配置された電源線上に形成された第2の開口部と、

前記TABテープ上の前記半導体素子と対向する領域に配設した第2のリードと電気的に接合されると共に、前記第1の開口部における電源線と前記第2の開口部における電源線とを互いに接続する導体層と

を備え、前記導体層が前記回路部の中央及び外周部を含む全面を覆うように前記半導体素子上に形成され、前記TABテープの前記第1のリード中の、電源と接続された電源用リードが前記半導体素子の前記電源用バンプと電気的に接合され、かつ、前記TABテープの前記第2のリードが前記半導体素子の前記導体層と電気的に接合されることにより、動作時に前記第1の開口部と前記導体層とを介して前記半導体素子の前記回路部の中央に供給される電源電流を増加させることを特徴とする半導体装置。 - 前記導体層は、銀、金、銅のうちいずれかの導電性物質を用いて形成されることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

- 前記第1の開口部における前記電源線と前記第2の開口部における前記電源線は、金属めっき層を介して前記導体層と接続することを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004164857A JP4904670B2 (ja) | 2004-06-02 | 2004-06-02 | 半導体装置 |

| KR1020050043947A KR100662070B1 (ko) | 2004-06-02 | 2005-05-25 | 반도체 장치 |

| TW094117246A TWI271829B (en) | 2004-06-02 | 2005-05-26 | Semiconductor device |

| US11/137,697 US7361980B2 (en) | 2004-06-02 | 2005-05-26 | Semiconductor device |

| CNB2005100743166A CN100392843C (zh) | 2004-06-02 | 2005-06-01 | 半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004164857A JP4904670B2 (ja) | 2004-06-02 | 2004-06-02 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005347488A JP2005347488A (ja) | 2005-12-15 |

| JP4904670B2 true JP4904670B2 (ja) | 2012-03-28 |

Family

ID=35479722

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004164857A Expired - Fee Related JP4904670B2 (ja) | 2004-06-02 | 2004-06-02 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7361980B2 (ja) |

| JP (1) | JP4904670B2 (ja) |

| KR (1) | KR100662070B1 (ja) |

| CN (1) | CN100392843C (ja) |

| TW (1) | TWI271829B (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7750375B2 (en) * | 2006-09-30 | 2010-07-06 | Taiwan Semiconductor Manufacturing Co., Ltd. | Power line layout techniques for integrated circuits having modular cells |

| US7906424B2 (en) | 2007-08-01 | 2011-03-15 | Advanced Micro Devices, Inc. | Conductor bump method and apparatus |

| US20090032941A1 (en) * | 2007-08-01 | 2009-02-05 | Mclellan Neil | Under Bump Routing Layer Method and Apparatus |

| US8258615B2 (en) * | 2008-03-07 | 2012-09-04 | Mediatek Inc. | Semiconductor device and fabricating method thereof |

| US7554133B1 (en) * | 2008-05-13 | 2009-06-30 | Lsi Corporation | Pad current splitting |

| US8314474B2 (en) * | 2008-07-25 | 2012-11-20 | Ati Technologies Ulc | Under bump metallization for on-die capacitor |

| JP5404454B2 (ja) * | 2010-01-29 | 2014-01-29 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP2013229455A (ja) * | 2012-04-26 | 2013-11-07 | Renesas Electronics Corp | 半導体装置および半導体装置の製造方法 |

| KR102172786B1 (ko) * | 2013-11-01 | 2020-11-02 | 에스케이하이닉스 주식회사 | 반도체 패키지 및 그의 제조방법 |

| CN108336056B (zh) * | 2018-04-12 | 2024-06-04 | 苏州震坤科技有限公司 | 用于半导体封装结构的万用转接电路层 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6489447A (en) | 1987-09-30 | 1989-04-03 | Toshiba Corp | Semiconductor integrated circuit |

| JPH02130946A (ja) * | 1988-11-11 | 1990-05-18 | Fujitsu Ltd | 半導体装置 |

| JPH02295144A (ja) * | 1989-05-09 | 1990-12-06 | Nec Corp | 集積回路 |

| JPH038360A (ja) | 1989-06-06 | 1991-01-16 | Toshiba Corp | 半導体装置 |

| JPH053222A (ja) * | 1991-06-25 | 1993-01-08 | Sony Corp | 半導体装置 |

| US5229639A (en) * | 1991-10-31 | 1993-07-20 | International Business Machines Corporation | Low powder distribution inductance lead frame for semiconductor chips |

| US5220195A (en) * | 1991-12-19 | 1993-06-15 | Motorola, Inc. | Semiconductor device having a multilayer leadframe with full power and ground planes |

| JPH06318597A (ja) * | 1993-05-07 | 1994-11-15 | Nec Kyushu Ltd | 半導体装置 |

| JPH0786281A (ja) * | 1993-09-17 | 1995-03-31 | Fujitsu Ltd | 半導体装置および半導体装置の製造方法 |

| US6025616A (en) * | 1997-06-25 | 2000-02-15 | Honeywell Inc. | Power distribution system for semiconductor die |

| US5952611A (en) * | 1997-12-19 | 1999-09-14 | Texas Instruments Incorporated | Flexible pin location integrated circuit package |

| JP2003243538A (ja) * | 2002-02-12 | 2003-08-29 | Hitachi Ltd | 半導体集積回路装置 |

| US6861762B1 (en) * | 2002-05-01 | 2005-03-01 | Marvell Semiconductor Israel Ltd. | Flip chip with novel power and ground arrangement |

| JP4141322B2 (ja) * | 2003-06-13 | 2008-08-27 | Necエレクトロニクス株式会社 | 半導体集積回路の自動配線方法及び半導体集積回路の設計のプログラム |

| JP2005057125A (ja) * | 2003-08-06 | 2005-03-03 | Rohm Co Ltd | 半導体装置 |

| JP4084737B2 (ja) * | 2003-11-20 | 2008-04-30 | 松下電器産業株式会社 | 半導体装置 |

-

2004

- 2004-06-02 JP JP2004164857A patent/JP4904670B2/ja not_active Expired - Fee Related

-

2005

- 2005-05-25 KR KR1020050043947A patent/KR100662070B1/ko not_active Expired - Fee Related

- 2005-05-26 US US11/137,697 patent/US7361980B2/en not_active Expired - Fee Related

- 2005-05-26 TW TW094117246A patent/TWI271829B/zh not_active IP Right Cessation

- 2005-06-01 CN CNB2005100743166A patent/CN100392843C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR100662070B1 (ko) | 2006-12-27 |

| CN1705099A (zh) | 2005-12-07 |

| TW200603352A (en) | 2006-01-16 |

| KR20060046166A (ko) | 2006-05-17 |

| US7361980B2 (en) | 2008-04-22 |

| TWI271829B (en) | 2007-01-21 |

| US20050280034A1 (en) | 2005-12-22 |

| JP2005347488A (ja) | 2005-12-15 |

| CN100392843C (zh) | 2008-06-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4474431B2 (ja) | 半導体パッケージおよび該製造方法 | |

| US6921980B2 (en) | Integrated semiconductor circuit including electronic component connected between different component connection portions | |

| JP2013080957A (ja) | 高密度コンタクトを有するリードレス集積回路パッケージ | |

| JPH08111497A (ja) | 樹脂封止型半導体装置 | |

| JP4904670B2 (ja) | 半導体装置 | |

| JP3437477B2 (ja) | 配線基板および半導体装置 | |

| US20060006504A1 (en) | Multilayer leadframe module with embedded passive component and method of fabricating the same | |

| JP2007281509A (ja) | 半導体装置 | |

| JP2001250876A (ja) | 半導体装置及びその製造方法 | |

| JP2803656B2 (ja) | 半導体装置 | |

| US6020631A (en) | Method and apparatus for connecting a bondwire to a bondring near a via | |

| CN100401487C (zh) | 半导体器件及半导体器件的制造方法 | |

| JP2008198916A (ja) | 半導体装置及びその製造方法 | |

| JP3721299B2 (ja) | 半導体パッケージの製造方法 | |

| JP4007917B2 (ja) | 半導体装置及びその製造方法 | |

| JP3889311B2 (ja) | プリント配線板 | |

| US7265443B2 (en) | Wire bonded semiconductor device having low inductance and noise | |

| JP4296916B2 (ja) | 半導体装置 | |

| JP2990120B2 (ja) | 半導体装置 | |

| JP2556204B2 (ja) | フィルムキャリア半導体装置の実装方法 | |

| US20070105270A1 (en) | Packaging methods | |

| JPH05166971A (ja) | 半導体装置 | |

| JPH04352463A (ja) | リードフレームおよびこれを用いた半導体装置 | |

| US20070145607A1 (en) | System to wirebond power signals to flip-chip core | |

| JPH04275443A (ja) | 半導体集積回路装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070424 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20080728 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100419 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100427 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100628 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110628 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110826 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111213 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111226 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4904670 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |