JP4893814B2 - 半導体チップの接合方法および接合装置 - Google Patents

半導体チップの接合方法および接合装置 Download PDFInfo

- Publication number

- JP4893814B2 JP4893814B2 JP2009278298A JP2009278298A JP4893814B2 JP 4893814 B2 JP4893814 B2 JP 4893814B2 JP 2009278298 A JP2009278298 A JP 2009278298A JP 2009278298 A JP2009278298 A JP 2009278298A JP 4893814 B2 JP4893814 B2 JP 4893814B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor chip

- bonding

- ultrasonic vibration

- contact

- electrode terminals

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/75—Apparatus for connecting with bump connectors or layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Wire Bonding (AREA)

Description

特許文献1記載のフリップチップの接続方法においては、マウントヘッドに吸着保持させたフリップチップ(半導体チップ)のバンプを、基板の被接続端子に接触させて荷重を加え、マウントヘッドに内蔵された超音波振動子を超音波振動させることで、マウントヘッドを介してフリップチップを超音波振動させる(特許文献1 段落0016−0018、第1−2図)。

これにより、被接続部の酸化層などを容易に除去でき、信頼性の高い電気的接続行うことができるものとしている(特許文献1 段落0022)。

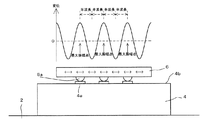

図6において、ステージ2上に配線基板4が保持されている。また、半導体チップ6がボンディングツール8(マウントヘッド)に保持されてボンディングツール8とともに移動されて、半導体チップ6に設けられたバンプ6a、6a・・が、配線基板4に設けられた対応するパッド4a、4a・・にそれぞれ当接するよう位置決めされている。ボンディングツール8の両側端面には、超音波振動子9が接続され、超音波振動子9が図示しない発振制御装置で水平方向に超音波振動されることにより、ボンディングツール8と半導体チップ6とがともに超音波振動される。

即ち、従来の半導体チップの接合方法においては一般的に50kHz程度の超音波振動が用いられているが、これよりも大幅に高い周波数の超音波振動を用いることができれば、電極端子同士の接合性を向上できるものと考えた。

また、超音波振動(粗密波)の周波数をさらに上げれば、不動点が半導体チップ6上に重なってしまい、全く振幅の作用しない電極端子ができてしまう。

このように、単に周波数を上げるのみでは、全ての電極端子の接合性を高めることはできない。

図1および図2は、実施例1、2に係る半導体チップの接合方法の原理を模式的に示した説明図である。

図1および図2において、半導体チップ6が搭載される搭載面4b側に、半導体チップ6のバンプ6a、6a・・(電極端子)と対応して設けられたパッド4a、4a・・(電極端子)を有する配線基板4(基板)が、ステージ2上に保持されている。

半導体チップ6は、電極端子としてのバンプ6a、6a・・が、配線基板4のパッド4a、4a・・にそれぞれ当接するよう、位置決めされている。

図1および図2において、この超音波振動(粗密波)の振幅(粗密波進行方向の変位量)を、半導体チップ6の上方にグラフとして表している。

図3に示すように、超音波振動子10の先端に、接触体としてのホーン12を取り付け、ホーン12の先端部を、半導体チップ6の側端面に当接させる。そして、図示しない発振制御装置により超音波振動子10を超音波振動させることで、ホーン12を介して半導体チップ6に前記超音波振動を印加する。

また、別途、半導体チップ6を上方から配線基板4に向けて押圧する押圧手段を設けて、半導体チップ6を配線基板に押圧しながら超音波振動を印加すれば、電極端子の接合をより強くすることができる。

図4において、ステージ2上に配線基板4が保持されている。また、半導体チップ6が接触体としてのボンディングツール14(マウントヘッド)に保持されてボンディングツール14とともに移動されて、半導体チップ6に設けられたバンプ6a、6a・・が、配線基板4に設けられた対応するパッド4a、4a・・にそれぞれ当接するよう位置決めされている。

これによれば、突起部14aを介して超音波振動を各電極端子に有効に印加することができる。

実施例3の構成を示す説明図を、図5に示す。

なお、本実施例3の半導体チップの接合装置は、上記実施例2と基本的な構成は共通するため、実施例2と共通する構成の説明は省略し、相違する構成のみを説明する。

また、50kHzの超音波振動を印加する印加継続時間を長くして、振動数を、前記高周波の超音波印加によりなされる振動数と等しくする対照実験を行ったが、この場合においても高周波の超音波振動による接合の方が、接合強度が高かった。

これは、前述の通り、高周波の超音波振動の方が振動周期が短いため、接合中、振動周期の間に電極端子が酸化してしまうのを防ぐことができ、また単位時間中に電極端子に与えるエネルギーを大きくできることなどに起因するものと考えられる。

例えば、近年、半導体チップ同士を電極端子を介して接合する技術が研究されているが、その場合にも、電極端子の位置に超音波振動の最大振幅点がくるように超音波振動を設定し、または、半導体チップ全体を高周波に超音波振動させる本発明を適用することができる。

さらに、半導体装置の外部接続端子(電極端子)を超音波振動を用いてプリント基板に接合するような場合においても、外部接続端子の位置に超音波振動の最大振幅点がくるように超音波振動を設定し、または、半導体チップ全体を高周波に超音波振動させる本発明を適用することができる。

4 配線基板(基板)

4a パッド(電極端子)

4b 半導体チップの搭載面

6 半導体チップ

6a バンプ(電極端子)

10 超音波振動子

12 ホーン(接触体)

14、16 ボンディングツール(接触体)

14a、16a 突起部

Claims (2)

- 半導体チップの電極端子と基板の電極端子とを当接させ、半導体チップの前記電極端子の形成面の反対面に当接させた接触体を超音波振動させて、半導体チップに超音波振動を印加することで、半導体チップと基板との電極端子同士を接合する半導体チップの接合方法において、

前記接触体には、複数の突起部が形成され、

前記接触体を、前記突起部の先端面で前記半導体チップの前記反対面に当接させ、

前記超音波振動は、前記接触体を伝わる粗密波であって、波長が、該粗密波の進行方向に隣接する各前記突起部の間隔の、自然数分の1の長さであるとともに、最大振幅点が、各突起部の位置となるように設定されていることを特徴とする半導体チップの接合方法。 - 半導体チップの電極端子と基板の電極端子とを当接させ、半導体チップに超音波振動を印加することで、半導体チップと基板との電極端子同士を接合する半導体チップの接合装置において、

先端面で前記半導体チップの前記反対面に当接する複数の突起部が形成された接触体と、

前記接触体を伝わる粗密波であって、波長が、該粗密波の進行方向に隣接する各前記突起部の間隔の、自然数分の1の長さであるとともに、最大振幅点が、各突起部の位置となる前記超音波振動を、接触体を介して半導体チップに印加する超音波振動子とを備えることを特徴とする半導体チップの接合装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009278298A JP4893814B2 (ja) | 2004-08-27 | 2009-12-08 | 半導体チップの接合方法および接合装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004247663 | 2004-08-27 | ||

| JP2004247663 | 2004-08-27 | ||

| JP2009278298A JP4893814B2 (ja) | 2004-08-27 | 2009-12-08 | 半導体チップの接合方法および接合装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004303729A Division JP2006093636A (ja) | 2004-08-27 | 2004-10-19 | 半導体チップの接合方法および接合装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010056580A JP2010056580A (ja) | 2010-03-11 |

| JP4893814B2 true JP4893814B2 (ja) | 2012-03-07 |

Family

ID=42072094

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009278298A Expired - Fee Related JP4893814B2 (ja) | 2004-08-27 | 2009-12-08 | 半導体チップの接合方法および接合装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4893814B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20230268312A1 (en) * | 2022-02-18 | 2023-08-24 | Bae Systems Information And Electronic Systems Integration Inc. | Soft touch eutectic solder pressure pad |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000306957A (ja) * | 1999-04-21 | 2000-11-02 | Tdk Corp | 超音波ボンディング実装方法及び超音波ボンディング装置 |

| JP2001308141A (ja) * | 2000-02-18 | 2001-11-02 | Sony Corp | 電子回路装置の製造方法 |

| JP3866150B2 (ja) * | 2001-05-16 | 2007-01-10 | 株式会社カイジョー | ボンディングヘッド及びこれを備えたボンディング装置 |

| JP2003100803A (ja) * | 2001-09-27 | 2003-04-04 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

-

2009

- 2009-12-08 JP JP2009278298A patent/JP4893814B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010056580A (ja) | 2010-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7523775B2 (en) | Bonding apparatus and method of bonding for a semiconductor chip | |

| US6811630B2 (en) | Ultrasonic vibration method and ultrasonic vibration apparatus | |

| JP2006135249A (ja) | 超音波実装方法およびこれに用いる超音波実装装置 | |

| KR20080047273A (ko) | 강도를 향상시킨 플랜지형 진동자 | |

| JP2006093636A (ja) | 半導体チップの接合方法および接合装置 | |

| US20120138662A1 (en) | Wire bonding method | |

| US7208059B2 (en) | Method of ultrasonic-mounting electronic component and ultrasonic mounting machine | |

| JP4893814B2 (ja) | 半導体チップの接合方法および接合装置 | |

| JPH08153759A (ja) | シングルポイントボンダーおよび半導体装置の製造方法 | |

| JP4491321B2 (ja) | 超音波実装方法およびこれに用いる超音波実装装置 | |

| JP3932286B2 (ja) | ボンディングヘッドおよびこれを備えたボンディング装置 | |

| JP3522906B2 (ja) | 超音波接合方法および装置 | |

| JP4395043B2 (ja) | 半導体チップの接合方法、半導体チップおよび基板 | |

| JP2007173362A (ja) | フライングリードの接合方法 | |

| JP2005079527A (ja) | 電子部品実装装置、電子部品実装方法および電子回路装置 | |

| JP2004167435A (ja) | ボンディング用超音波ホーン及びこれを備えたボンディング装置 | |

| JP5119948B2 (ja) | 半導体装置の製造方法 | |

| KR100996958B1 (ko) | 와이어본딩용 트랜스듀서 어셈블리 | |

| JP2003059972A (ja) | ボンディングヘッド及びこれを備えたボンディング装置 | |

| JP3796943B2 (ja) | ワイヤボンディング装置及びワイヤボンディング方法 | |

| JP4109074B2 (ja) | 超音波ホーンとそのツール保持方法及びそれを用いたバンプボンディング装置 | |

| JP2002343831A (ja) | ボンディングヘッド及びこれを備えたボンディング装置 | |

| JP3682452B2 (ja) | 超音波フリップチップ実装装置 | |

| JP2004047857A (ja) | 超音波フリップチップ実装方法および装置 | |

| JP2006066689A (ja) | 半導体素子及びバンプ電極の平坦化方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111114 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111122 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111205 |

|

| R150 | Certificate of patent (=grant) or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150106 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |