JP4802139B2 - 半導体集積回路モジュール - Google Patents

半導体集積回路モジュール Download PDFInfo

- Publication number

- JP4802139B2 JP4802139B2 JP2007129720A JP2007129720A JP4802139B2 JP 4802139 B2 JP4802139 B2 JP 4802139B2 JP 2007129720 A JP2007129720 A JP 2007129720A JP 2007129720 A JP2007129720 A JP 2007129720A JP 4802139 B2 JP4802139 B2 JP 4802139B2

- Authority

- JP

- Japan

- Prior art keywords

- scan

- semiconductor integrated

- integrated circuit

- circuit

- compression

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/18—Address generation devices; Devices for accessing memories, e.g. details of addressing circuits

- G11C29/30—Accessing single arrays

- G11C29/32—Serial access; Scan testing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/18—Address generation devices; Devices for accessing memories, e.g. details of addressing circuits

- G11C29/30—Accessing single arrays

- G11C2029/3202—Scan chain

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

- G11C5/04—Supports for storage elements, e.g. memory modules; Mounting or fixing of storage elements on such supports

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P74/00—Testing or measuring during manufacture or treatment of wafers, substrates or devices

- H10P74/27—Structural arrangements therefor

- H10P74/277—Circuits for electrically characterising or monitoring manufacturing processes, e.g. circuits in tested chips or circuits in testing wafers

Landscapes

- Tests Of Electronic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

Januz Rajki et al, "Embedded Deterministic Test for Low-Cost Manufacturing Test", Proceeding International Test Conference 2002 (ITC'02), 2002, p.301-310 (U.S.A.)

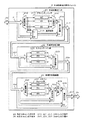

半導体集積回路41に対する圧縮スキャンデータとともに、半導体集積回路42に対する圧縮スキャンデータを外部スキャン入力端子43からスキャン入力端子411を介して展開回路412へ入力する。この入力を受けて、展開回路412は、半導体集積回路41のスキャンチェーン群413の各スキャンチェーン(SC)に分配するスキャンテストデータとともに、半導体集積回路42のスキャンチェーン群422の各スキャンチェーン(SC)に分配するスキャンテストデータも生成する。

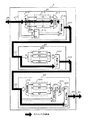

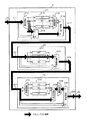

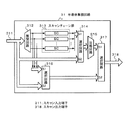

11、12、13、21、22、31、41、42、43、51、52 半導体集積回路

53 圧縮スキャンテスト制御用集積回路

14、24、43、54 外部スキャン入力端子

15、25、44、55 外部スキャン出力端子

111、121、131、211、221、231、311、411、531 スキャン入力端子

116、126、136、217、224、237、318、415、534 スキャン出力端子

112、122、132、212、232、312、412、532 展開回路

113、123、133、213、222、233、313、413、422、511、521 スキャンチェーン群

114、124、134、214、235、315、414、533 圧縮回路

115、125、135、215、216、223、234、236、314、316、317 選択回路

Claims (3)

- 複数の圧縮スキャンテスト対応半導体集積回路を搭載し、

前記複数の圧縮スキャンテスト対応半導体集積回路のそれぞれが、

スキャン入力端子と、

前記スキャン入力端子に接続された圧縮スキャンテスト用展開回路と、

前記展開回路の出力が入力されるスキャンチェーンと、

前記スキャンチェーンの出力が入力される圧縮スキャンテスト用圧縮回路と、

前記圧縮回路の出力に切り替えて前記スキャン入力端子に入力された信号を出力する選択回路と、

前記選択回路の出力が入力されるスキャン出力端子と、

を有し、

それぞれの前記圧縮スキャンテスト対応半導体集積回路の前記スキャン出力端子が後段の前記スキャン入力端子へ順次接続され、

初段の前記圧縮スキャンテスト対応半導体集積回路の前記スキャン入力端子が外部スキャン入力端子へ接続され、最終段の前記圧縮スキャンテスト対応半導体集積回路の前記スキャン出力端子が外部スキャン出力端子へ接続され、

前記選択回路の切り替えの制御により、

前記外部スキャン入力端子と前記外部スキャン出力端子との間に、前記複数の圧縮スキャンテスト対応半導体集積回路を個々に圧縮スキャンテストする、スキャンテスト経路が形成される

ことを特徴とする半導体集積回路モジュール。 - スキャン入力端子、スキャン出力端子およびスキャンチェーンを有する圧縮スキャンテスト非対応半導体集積回路と、

前記圧縮スキャンテスト非対応半導体集積回路の前記スキャン入力端子にスキャン出力端子が接続される第1の圧縮スキャンテスト対応半導体集積回路と、

前記圧縮スキャンテスト非対応半導体集積回路の前記スキャン出力端子にスキャン入力端子が接続される第2の圧縮スキャンテスト対応半導体集積回路と、

を備え、

前記第1の圧縮スキャンテスト対応半導体集積回路は、

自身の展開回路の出力の一部または入力のいずれかを選択して出力する第1の選択回路と、

自身の圧縮回路の出力に切り替えて前記第1の選択回路の出力を前記スキャン出力端子へ出力する第2の選択回路と、

を有し、

前記圧縮スキャンテスト非対応半導体集積回路は、

自身の前記スキャンチェーンの出力に切り替えて前記第1の圧縮スキャンテスト対応半導体集積回路の前記スキャン出力端子の出力を自身の前記スキャン出力端子へ出力する第3の選択回路

を有し、

前記第2の圧縮スキャンテスト対応半導体集積回路は、

自身のスキャンチェーンの出力に切り替えて前記圧縮スキャンテスト非対応半導体集積回路の前記スキャン出力端子の出力を自身の圧縮回路へ入力する第4の選択回路と、

前記自身の圧縮回路の出力に切り替えて前記圧縮スキャンテスト非対応半導体集積回路の前記スキャン出力端子の出力を自身のスキャン出力端子へ出力する第5の選択回路と、

を有する

ことを特徴とする半導体集積回路モジュール。 - 前記圧縮スキャンテスト対応半導体集積回路のそれぞれを、

自身のスキャンチェーンの出力に切り替えて前記展開回路への入力を前記圧縮回路へ入力する第1の選択回路と、

前記展開回路の出力の一部または入力のいずれかを選択して出力する第2の選択回路と、

前記圧縮回路出力に切り替えて前記第2の選択回路の出力をスキャン出力端子へ出力する第3の選択回路と、

を有する圧縮スキャンテスト対応半導体集積回路とした

ことを特徴とする請求項1または2に記載の半導体集積回路モジュール。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007129720A JP4802139B2 (ja) | 2007-05-15 | 2007-05-15 | 半導体集積回路モジュール |

| US12/120,538 US7890823B2 (en) | 2007-05-15 | 2008-05-14 | Nonvolatile semiconductor memory system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007129720A JP4802139B2 (ja) | 2007-05-15 | 2007-05-15 | 半導体集積回路モジュール |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008286553A JP2008286553A (ja) | 2008-11-27 |

| JP4802139B2 true JP4802139B2 (ja) | 2011-10-26 |

Family

ID=40028759

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007129720A Expired - Fee Related JP4802139B2 (ja) | 2007-05-15 | 2007-05-15 | 半導体集積回路モジュール |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7890823B2 (ja) |

| JP (1) | JP4802139B2 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8856601B2 (en) * | 2009-08-25 | 2014-10-07 | Texas Instruments Incorporated | Scan compression architecture with bypassable scan chains for low test mode power |

| US8832512B2 (en) * | 2010-03-16 | 2014-09-09 | Mentor Graphics Corporation | Low power compression of incompatible test cubes |

| KR101709071B1 (ko) * | 2010-05-19 | 2017-02-22 | 삼성전자주식회사 | 컴프레션 모드 스캔 테스트를 위한 집적 회로 |

| CN101915892B (zh) * | 2010-08-27 | 2012-06-27 | 钰创科技股份有限公司 | 芯片测试电路 |

| US8812921B2 (en) * | 2011-10-25 | 2014-08-19 | Lsi Corporation | Dynamic clock domain bypass for scan chains |

| JP6491507B2 (ja) * | 2015-03-20 | 2019-03-27 | ルネサスエレクトロニクス株式会社 | 半導体装置、電子装置および半導体装置の自己診断方法 |

| JP6731733B2 (ja) | 2016-01-20 | 2020-07-29 | 株式会社メガチップス | スキャンテスト回路、スキャンテスト方法およびスキャンテスト回路の設計方法 |

| CN112305404B (zh) * | 2020-09-29 | 2022-11-08 | 上海兆芯集成电路有限公司 | 核分区电路与测试装置 |

| US11495315B1 (en) * | 2021-08-11 | 2022-11-08 | Siemens Industry Software Inc. | Configurable built-in self-repair chain for fast repair data loading |

| KR20240024674A (ko) | 2022-08-17 | 2024-02-26 | 삼성전자주식회사 | 반도체 칩을 스캔 테스트 하기 위한 집적 회로 패키지, 집적 회로 패키지의 동작 방법 및 집적 회로 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2676169B2 (ja) * | 1989-12-27 | 1997-11-12 | 三菱電機株式会社 | スキャンパス回路 |

| US5991909A (en) * | 1996-10-15 | 1999-11-23 | Mentor Graphics Corporation | Parallel decompressor and related methods and apparatuses |

| JP2001074811A (ja) * | 1999-09-03 | 2001-03-23 | Hitachi Ltd | 半導体集積回路 |

| JP3845016B2 (ja) * | 1999-11-23 | 2006-11-15 | メンター・グラフィクス・コーポレーション | テスト中回路技術分野へのテストパターンの連続的な適用およびデコンプレッション |

| JP2002005998A (ja) * | 2000-06-21 | 2002-01-09 | Matsushita Electric Ind Co Ltd | 集積回路のテスト方法およびテスト回路 |

| US7512851B2 (en) * | 2003-08-01 | 2009-03-31 | Syntest Technologies, Inc. | Method and apparatus for shifting at-speed scan patterns in a scan-based integrated circuit |

| EP1690102A1 (en) * | 2003-12-01 | 2006-08-16 | Nokia Corporation | Integrated circuit with leakage control and method for leakage control |

| KR20050078704A (ko) * | 2004-01-31 | 2005-08-08 | 삼성전자주식회사 | 스캔 베이스 atpg 테스트회로, 테스트방법 및 스캔체인 재배열방법 |

| JP2005309867A (ja) * | 2004-04-22 | 2005-11-04 | Fujitsu Ltd | マルチコア・プロセサ試験方法 |

| EP2677328B1 (en) | 2006-02-17 | 2015-07-29 | Mentor Graphics Corporation | Multi-stage test response compactors |

| US7949920B2 (en) * | 2006-04-19 | 2011-05-24 | Texas Instruments Incorporated | DFT techniques to reduce test time and power for SoCs |

-

2007

- 2007-05-15 JP JP2007129720A patent/JP4802139B2/ja not_active Expired - Fee Related

-

2008

- 2008-05-14 US US12/120,538 patent/US7890823B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7890823B2 (en) | 2011-02-15 |

| US20080288838A1 (en) | 2008-11-20 |

| JP2008286553A (ja) | 2008-11-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4802139B2 (ja) | 半導体集積回路モジュール | |

| US8843795B2 (en) | Test system of reconfigurable device and its method and reconfigurable device for use therein | |

| US7249300B2 (en) | Integrated circuit device including a scan test circuit and methods of testing the same | |

| JPS63243890A (ja) | 半導体集積回路装置 | |

| US20110175638A1 (en) | Semiconductor integrated circuit and core test circuit | |

| KR20070029654A (ko) | 테스트 액세스 아키텍처 및 모듈 테스트 방법 | |

| US7293211B2 (en) | Semiconductor integrated circuit | |

| US20240310427A1 (en) | Semiconductor device and method of manufacturing the same | |

| CN112684327A (zh) | 扫描链及其设计方法和基于扫描链的串行扫描复位方法 | |

| JP2007205933A (ja) | 半導体集積回路 | |

| CN101111776A (zh) | 半导体集成电路和系统lsi | |

| JP2005257366A (ja) | 半導体回路装置及び半導体回路に関するスキャンテスト方法 | |

| JP4610919B2 (ja) | 半導体集積回路装置 | |

| JP2005024410A (ja) | 半導体集積回路装置 | |

| JP4234357B2 (ja) | 半導体集積回路の故障解析方法 | |

| JP2007003423A (ja) | 半導体集積回路およびその制御方法 | |

| KR101174679B1 (ko) | 반도체 집적회로 | |

| JP2007272982A (ja) | 半導体記憶装置およびその検査方法 | |

| JP2005505781A (ja) | 複雑な集積回路の自動的なスキャン・ベースのテスト | |

| JP2002009238A (ja) | スキャンパス設計方法 | |

| JP2006329876A (ja) | 半導体集積回路及びそのテスト方法 | |

| JP2024138860A (ja) | 半導体集積回路及び半導体集積回路のテスト方法 | |

| JP2011090762A (ja) | データ転送回路 | |

| JP2008224535A (ja) | 半導体集積回路およびその検査方法 | |

| JP2006023225A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090731 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110415 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110422 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110614 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110614 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20110614 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110714 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110808 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140812 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140812 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |