JP4698776B2 - 低電圧二重平衡型ミキサー回路装置 - Google Patents

低電圧二重平衡型ミキサー回路装置 Download PDFInfo

- Publication number

- JP4698776B2 JP4698776B2 JP01507698A JP1507698A JP4698776B2 JP 4698776 B2 JP4698776 B2 JP 4698776B2 JP 01507698 A JP01507698 A JP 01507698A JP 1507698 A JP1507698 A JP 1507698A JP 4698776 B2 JP4698776 B2 JP 4698776B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- mixer

- transistors

- circuit

- mixer circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000010355 oscillation Effects 0.000 claims description 27

- 239000003990 capacitor Substances 0.000 claims description 7

- 230000003321 amplification Effects 0.000 claims 6

- 238000003199 nucleic acid amplification method Methods 0.000 claims 6

- 238000010586 diagram Methods 0.000 description 7

- 238000005513 bias potential Methods 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

- H03D7/1433—Balanced arrangements with transistors using bipolar transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

- H03D7/1441—Balanced arrangements with transistors using field-effect transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

- H03D7/1458—Double balanced arrangements, i.e. where both input signals are differential

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

- H03D7/1491—Arrangements to linearise a transconductance stage of a mixer arrangement

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B01—PHYSICAL OR CHEMICAL PROCESSES OR APPARATUS IN GENERAL

- B01F—MIXING, e.g. DISSOLVING, EMULSIFYING OR DISPERSING

- B01F33/00—Other mixers; Mixing plants; Combinations of mixers

- B01F33/30—Micromixers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D2200/00—Indexing scheme relating to details of demodulation or transference of modulation from one carrier to another covered by H03D

- H03D2200/0041—Functional aspects of demodulators

- H03D2200/0043—Bias and operating point

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D2200/00—Indexing scheme relating to details of demodulation or transference of modulation from one carrier to another covered by H03D

- H03D2200/0041—Functional aspects of demodulators

- H03D2200/0084—Lowering the supply voltage and saving power

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/12—Transference of modulation from one carrier to another, e.g. frequency-changing by means of semiconductor devices having more than two electrodes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/12—Transference of modulation from one carrier to another, e.g. frequency-changing by means of semiconductor devices having more than two electrodes

- H03D7/125—Transference of modulation from one carrier to another, e.g. frequency-changing by means of semiconductor devices having more than two electrodes with field effect transistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Superheterodyne Receivers (AREA)

- Amplifiers (AREA)

- Inductance-Capacitance Distribution Constants And Capacitance-Resistance Oscillators (AREA)

Description

【発明の属する技術分野】

本発明は、ミキサー回路装置に関し、特にシングルエンド入力と差動出力とを有するミキサー回路装置に関する。

【0002】

【従来の技術】

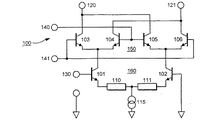

RFミキサー回路は、最新の無線システムにおいて重要な構成部であり、このミキサー回路のパラメータが、ミキサー回路が使用されるシステムの主な特性を決定する。従来、最も一般的なミキサー回路構成は、ギルバートセル構成もしくはマイクロミキサー構成であり、図3及び図4に示されている。

【0003】

図3及び図4において、各ミキサー回路は、入力端子において、シングルエンドrf入力信号を受信し、出力端子において、差動信号を出力する。この差動信号は、入力信号を増幅し、続いてそれを局部発振器からの信号と混合したものである。両ミキサー回路とも、容易にIC構成で実施することができ、自動車電話等においてよく使用される。しかし、従来のこのような回路構成を有するミキサー回路は、雑音特性が悪い。また、このようなミキサー回路においては、2.7Vあるいはそれ以上の供給電圧が必要であり、これは電源と接地との間に3つのトランジスタが直列に配置されているからである。従って、これらミキサー回路は、低電圧適用に適さない場合がある。

【0004】

図3は、従来のミキサー回路である、ギルバートセル回路を示す図である。図3によると、ギルバートセル回路100は、入力端子130でシングルエンド入力電圧信号を受信し、入力端子140、141で局部発振器電圧の差動信号を受信する。トランジスタ101、102、抵抗110、111、及び電源115は、差動型相互コンダクタンス増幅回路160を形成し、トランジスタ103〜106はミキサーコア150を形成する。入力端子130における入力電圧の増加は、トランジスタ101のコレクタ電極からの信号電流を増加させる。電源115及び抵抗110、111は、トランジスタ102のコレクタ電極から相補形減少電流が送られることを確実にする。これら電流信号は、電源115が定電流源として適用されている場合、平衡調整される。

【0005】

ミキサーコア150は、入力端子140、141において局部発振器の差動信号を受信する。入力端子140の電圧が正の場合、入力端子141の電圧は負になり、トランジスタ104、105は、ONに切り換えられ、トランジスタ103、106は、OFFに切り換えられる。従って、トランジスタ101のコレクタ電流は出力端子121へと送られ、トランジスタ102のコレクタ電流は、出力端子120へと送られる。トランジスタ101、102のコレクタ電流は、入力端子141の電圧が入力端子140よりも高い場合、逆の出力端子121、120に切り換えられる。

【0006】

図4は、従来のミキサー回路である、マイクロミキサー回路を示す図である。図4によると、マイクロミキサー回路200は、入力端子230においてシングルエンド入力信号を受信し、出力端子240、241において、局部発振器の差動信号を受信する。トランジスタ201〜203及び抵抗210〜212は、相互コンダクタンス増幅回路260を形成し、トランジスタ204〜207は、ミキサーコア250を形成する。

【0007】

入力端子230における電圧の増加は、トランジスタ202のコレクタ電極から送られる電流を増加させ、トランジスタ203のコレクタ電極から送られる電流を減少させる。従って、このミキサー回路は、シングルエンド入力と差動出力とを有する、相互コンダクタンス増幅回路として機能する。増幅回路260からの出力は、差動電流信号としてトランジスタ202、203のコレクタ電極に与えられ、ミキサーコア250に出力される。

【0008】

ミキサーコア250は、図3に示されるミキサー回路におけるミキサーコア150と同様に機能する。

【0009】

【発明が解決しようとする課題】

図3に示されるギルバートセル回路において、雑音特性が悪いのは、主に抵抗110、111による熱雑音によるところが大きく、抵抗110、111は、電流路に直接雑音を生じさせる。電源115もまた出力信号に雑音を発生させる。これは、電源115の入力端子と出力端子にかけて大きな電圧の振れが生じるからである。また、トランジスタ101、102は、ベース抵抗が直列に配置されているため、出力端子120、121においてかなり大きな雑音が発生することになる。

【0010】

図4に示されるマイクロミキサー回路は、非常に線形的な特性と無線周波数における大きなダイナミックレンジとを有している。しかし主電流路において使用される抵抗の数が多いため、雑音特性は、ギルバートセル回路よりもむしろ悪い。

【0011】

本発明は、上記事情に鑑みなされたもので、より優れた雑音特性と低電圧供給条件とを有するミキサー回路装置を提供することを目的とする。

【0012】

【課題を解決するための手段】

本発明は、ミキサーコアと、シングルエンド増幅段とを有するミキサー回路装置において、前記ミキサーコアは、第1の信号入力で前記増幅段からのシングルエンド出力信号を受信し、該シングルエンド出力信号に対応して差動出力信号を出力することを特徴とする。

【0013】

本発明は、入力される信号に応じて差動出力信号を出力し、ミキサーコアと、シングルエンド増幅段と、バイアス手段とを有するミキサー回路装置において、前記ミキサーコアは、第1の電流信号入力と、第2の電流信号入力と、第1の局部発振器信号入力と、第2の局部発振器信号入力とを有し、前記シングルエンド増幅段は、前記入力信号に応じて前記ミキサーコアの前記第1の電流信号入力に電流信号を与え、前記バイアス手段は、低acインピーダンスを有し、前記ミキサーコアの前記第2の信号入力にバイアス電流を与えることを特徴とする。

【0014】

【発明の実施の形態】

次に、本発明に係るミキサー回路の実施の形態について、図面を参照して詳細に説明する。

【0015】

図1は、本発明の実施の形態である二重平衡型ミキサー回路を示す図である。

【0016】

図1において、ミキサー回路300は、増幅回路390と、バイアス装置392とミキサーコア391と、局部発振器ドライバ回路393によって構成される。その動作において、局部発振器の差動信号が入力端子340、341に入力され、バイアス電位が端子360、361に印加され、シングルエンド入力信号が入力端子330に入力され、差動出力信号が出力端子320、321で得られる。

【0017】

増幅回路390は、トランジスタ301の周辺に配置されている。トランジスタ301のベース電極は、抵抗311を介して端子360に接続し、またキャパシタ350を介して入力端子330に接続している。インダクタ310は、トランジスタ301のエミッタ電極と接地電位との間に接続されている。トランジスタ301のコレクタ電極は、ミキサーコア391への出力電流路を形成している。

【0018】

電流バイアス装置392は、トランジスタ302を有している。トランジスタ302は、エミッタ電極が接地電位に直接接続し、ベース電極が抵抗312を介して端子361に接続している。またトランジスタ302は、コレクタ電極からミキサーコア391に対して電流信号を与える。キャパシタ351は、トランジスタ302のコレクタ電極と接地電位との間に接続されている。

【0019】

ミキサーコア391は4つのトランジスタ303〜306を有している。トランジスタ303、304は、お互いのエミッタ電極が結合し、増幅回路390からの出力電流信号を受信する。また、トランジスタ305、306は、お互いのエミッタ電極が結合し、バイアス装置392から電流を与えられる。トランジスタ303、305のコレクタ電極は、お互いに接続し、また出力端子320に接続している。トランジスタ304、306のコレクタ電極は、お互いに接続し、また出力端子321に接続している。ミキサーコア391は、トランジスタ303〜306のベース電極と局部発振ドライバ回路393の差動出力との接合点において、局部発振ドライバ回路393によって制御されている。トランジスタ303、306は、ベース電極がお互いに接続し、また局部発振ドライバ回路393の第1の出力に接続している。また、トランジスタ304、305は、ベース電極がお互いに接続し、また局部発振ドライバ回路393のもう一方の出力に接続している。

【0020】

増幅回路390は、入力端子330で、RF電圧信号を受信し、これを電流信号に変換する。変換された電流信号は、トランジスタ301のベース電極に与えられる。従って、増幅回路390は、高インピーダンス電源を構成する。キャパシタ350は、入力信号のあらゆるdc要素を阻止すべく動作する。トランジスタ301のDCバイアスは、抵抗311及び端子360に印加されるバイアス電位によって実行される。トランジスタ301のエミッタ接地電流利得βの複雑な特性により、インンダクタ310は、トランジスタ301のベースエミッタ回路において直列負帰還を実行する。

【0021】

インダクタ310は非雑音素子であり、特定の周波数領域において周波数に無関係の負帰還を実行する。この周波数領域は、インダクタ310の値及び所望の周波数におけるトランジスタ301のベースエミッタ抵抗に左右される。またインダクタ310の値は増幅回路390の利得及び線形性に影響を及ぼす。抵抗をインダクタ310の代わりに使用することもできるが、インダクタ310を使用する方が増幅回路390においてより多くの線形特性及び優良な雑音特性を得ることができる。

【0022】

インダクタ310は、全体もしくは一部分において、IC実装の寄生インダクタンス、及び/もしくはボンディングワイヤー、及び/もしくは、接続ピンによって構成することができる。

【0023】

トランジスタ301は、ベースエミッタ抵抗による雑音の発生を軽減するために、広域エミッタ領域を有するトランジスタであることが望ましい。しかし、エミッタ領域の大きいトランジスタは寄生容量も高く、従って、リーク及び低電流密度による電流利得βの低減が生じる。従って、特定のミキサー回路に組み込まれるトランジスタ領域及び駆動電流を選択する際に、雑音特性を優先するか利得を優先するかを選択する必要がある。

【0024】

ミキサー回路300の入力インピーダンスは、インダクタ310の値及び、トランジスタ301のfT (トランジション周波数) によって決定される。

【0025】

バイアス装置392は、トランジスタ302のコレクタ電極からミキサーコア391のトランジスタ305、306にバイアス電流を与えるために動作する。抵抗312は、トランジスタ302のベース電極をバイアス電位が印加されている端子361に接続する。キャパシタ351は、トランジスタ302のコレクタ電極における信号のac要素の低インピーダンス接地を実行する。この信号のdc要素は、適度に一定に保たれる。

【0026】

局部発振ドライバ回路393の条件は、局部発振ドライバ回路の入力端に入力される電圧信号を変換して出力端に与えることと、この入力信号に応じた出力端で接地電位基準の同相出力インピーダンスを高くすることが必要である。これに対する理由は、下記に述べるミキサーコア391の動作の説明の中で明らかにする。

【0027】

局部発振ドライバ回路393は、変成器として適用することができる。局部発振ドライバ回路393が、全ミキサー回路300と同一のチップ上に搭載されなければならない場合においては、図2に示されるような局部発振ドライバ回路493を適用することができる。

【0028】

ドライバ回路493は、ロングテイルトランジスタ組であるトランジスタ401、402を有し、トランジスタ401、402は、ベース電極がそれぞれ局部発振器信号入力端子340、341に接続しいる。抵抗410、411はそれぞれトランジスタ401、402のコレクタ電極を供給電圧端子440に接続している。抵抗412はトランジスタ401及び402のエミッタ電極の間に接続されている。局部発振ドライバ回路出力端子430、431は、トランジスタ402、401のコレクタ電極にそれぞれ接続され、これら出力端子430、431は、図1に示されるミキサーコア391のトランジスタ303〜306のベース電極への接続を形成する。

【0029】

局部発振ドライバ回路493は、局部発振器信号入力端子340、341に入力される局部発振器信号によって制御される。トランジスタ401、402は、交互に動作し、また正の電圧を交互に出力端子430、431に与えるよう、局部発振器信号によって「ハード切り換え」がされる。この電圧は、トランジスタ304、305、及びトランジスタ303、306を交互にONに切り換える。

【0030】

トランジスタ304、305がONになるとき、トランジスタ301のコレクタ電流は、トランジスタ304のエミッタ電極を通過しトランジスタ304のベース電極及びコレクタ電極へと送られる。出力端子321へと送られるトランジスタ304のコレクタ電流は、ベース電流に比例し、トランジスタの電流利得係数βに応じて増大する。トランジスタ305の入力インピーダンスが、局部発振ドライバ回路493の同相出力インピーダンスに比べて低いという条件の下、トランジスタ304のベース電極からの信号電流は、主としてトランジスタ305のベース電極へと送られ、またトランジスタ305のコレクタ電流は、トランジスタ304のコレクタ電流を補足する。接地への入力信号を基準とする同相出力インピーダンスが、トランジスタ305の入力インピーダンスよりも十分に高い場合、差動出力端子320、321において平衡出力が得られる。

【0031】

ミキサーコアの出力の平衡は、さらにトランジスタ303、306及びトランジスタ304、305によるインピーダンスバイアスによって制御することができ、この制御は、端子360、361に印加される電位を変化させることで得ることができる。

【0032】

トランジスタ303、306がONに切り換えられるとき、トランジスタ301のコレクタ電流は、逆の差動出力端子320へと送られ、相補形出力は、もう一方の出力端子321へと送られる。

【0033】

従って、シングルエンド入力信号から差動出力信号への変換は、ミキサーコア391自体で実行され、これによりミキサー回路の実施において使用されるトランジスタ数は削減され、使用される供給電圧は低減される。

【0034】

トランジスタ305、306の相補形電流は、トランジスタ303、304のエミッタ領域をトランジスタ305、306のそれよりも大きく設定することで増加させることができる。例えば、関連する周波数に応じて3:2または、2:1の比率で設定することができる。このことにより、トランジスタ303、304のベース電流は高くなり、ミキサーコアにおけるトランジスタの寄生容量による損失が補われる。

【0035】

局部発振ドライバ回路493の同相出力インピーダンスは、抵抗410、411によって決定される。これら抵抗の値は、ドライバ回路493の適切な動作に対応してできるだけ高い方が望ましい。通常、抵抗410、411は、抵抗412よりもかなり大きく、抵抗412の抵抗は、局部発振ドライバ回路493の差動出力インピーダンスを決定するものである。抵抗410、411を双方とも同様に適当なインダクタと交換してもほとんど同様の効果を得ることができる。

【0036】

本実施の形態は、npn二極性トランジスタについてのみ説明がなされているが、本発明はこれに限定されるものではなく、同様に、pnp二極性トランジスタまたは、電界効果トランジスタでも実現が可能である。上述のコレクタ電極及びエミッタ電極は、電界効果トランジスタの第1及び第2の主電極としてのドレイン電極及びソース電極に対応する。

【0037】

【発明の効果】

上記の説明のように、本発明に係るミキサー回路装置において、シングルエンド入力信号から差動出力信号への変換は、ミキサーコア391自体で実行され、これによりミキサー回路の実施において使用されるトランジスタ数は削減され、使用される供給電圧は低減される。また、非雑音素子である負帰還インダクタ310の適用により雑音値は軽減される。従って、雑音の少ない低電圧二重平衡型ミキサー回路を得ることができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態であるミキサー回路装置を示す図である。

【図2】 本発明の実施の形態である図1のミキサー回路に適当な局部発振ドライバ回路を示す図である。

【図3】 従来のギルバートセルミキサー回路を示す図である。

【図4】 従来のマイクロミキサー回路を示す図である。

【符号の説明】

100、200、300 ミキサー回路

101〜106、201〜207、

301〜306、401、402 トランジスタ

110、111、210〜212、

311、312、410〜413 抵抗

115 電源

120、121、220、221、

320、321、430、431 出力端子

130、140、141、230、240、241、

330、340、341 入力端子

150、250、391 ミキサーコア

160、260、390 増幅回路

310 インダクタ

350、351 キャパシタ

360、361 バイアス電位の端子

392 バイアス装置

393、493 局部発振ドライバ回路

440 供給電圧端子

Claims (10)

- a)シングルエンド入力端とシングルエンド出力端とを有する増幅段と、

b)第1及び第2電流信号入力端と、同相入力インピーダンスを有する局部発振ドライバー側第1及び第2入力端と、第1及び第2差動出力端とを配置したミキサーコアの構成であり、且つこの第1電流信号入力端を前記増幅段の前記シングルエンド出力端に接続するミキサーコアと、

c)接地部と、前記ミキサーコアの前記第2電流信号入力端との間に配したDC電流源を有するバイアス回路と、

d)前記バイアス回路の出力部と前記接地部のそれぞれに接続するキャパシタと

を備えており、更に、

e)発振入力端を配置して且つ第1及び第2発振出力端を配置した局部発振ドライバー回路の前記第1及び第2発振出力端を、前記ミキサーコアの局部発振ドライバー側第1及び第2入力端へそれぞれ接続すると共に、この局部発振ドライバー側第1及び第2入力端の同相入力インピーダンスが、前記局部発振ドライバー回路の前記第1及び第2発振出力端における同相出力インピーダンスに比べて低い関係を成す前記局部発振ドライバー回路とを備えたことを特徴とするミキサー回路。 - 前記ミキサーコアが二重平衡型である請求項1に記載のミキサー回路。

- 前記増幅段が相互コンダクタンス増幅器として動作する増幅用トランジスタを含む請求項1に記載のミキサー回路。

- 前記増幅段のトランジスタは、その制御電極を前記シングルエンド入力端からの信号入力端にして、このトランジスタの第1主電極を前記シングルエンド出力端に接続して、更に、第2主電極を接地部に接続する請求項3に記載のミキサー回路。

- 前記増幅段のトランジスタの前記制御電極にDCバイアスを与えて、更に、入力キャパシタを介して前記シングルエンド入力端に接続する請求項4に記載のミキサー回路。

- 前記増幅段のトランジスタの前記第2主電極と前記接地部との間にインダクタを接続する請求項4に記載のミキサー回路。

- 前記バイアス回路が、DCバイアスする制御電極と、この出力部とする第1主電極と、前記接地部に接続する第2主電極と有するバイアス用トランジスタを含む請求項1に記載のミキサー回路。

- 前記局部発振ドライバー回路が、2つの前記発振入力端と、第1及び第2トランジスタとを有するものであって、前記第1及び第2トランジスタのそれぞれが制御電極と第1及び第2主電極とを備え、

そして、

前記第1トランジスタの制御電極を一方の前記発振入力端に接続して、

前記第2トランジスタの制御電極を他方の前記発振入力端に接続して、

前記第1及び第2トランジスタの各第2主電極を互いに接続して且つ電流源に接続して、前記第1及び第2トランジスタの各第1主電極を、前記局部発振ドライバー回路の前記第1及び第2発振出力端のそれぞれに接続する請求項1に記載のミキサー回路。 - 前記第1トランジスタの前記第1主電極と電圧供給源との間に第1の抵抗を接続して、前記第2トランジスタの前記第1主電極と前記電圧供給源との間に第2の抵抗を接続する請求項8に記載のミキサー回路。

- 前記局部発振ドライバー回路が、更に、第3の抵抗を前記第1及び第2トランジスタの各前記第1主電極間に接続する請求項9に記載のミキサー回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB9700486A GB2321149B (en) | 1997-01-11 | 1997-01-11 | Low voltage double balanced mixer |

| GB9700486.5 | 1997-01-11 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPH10209760A JPH10209760A (ja) | 1998-08-07 |

| JPH10209760A5 JPH10209760A5 (ja) | 2004-10-07 |

| JP4698776B2 true JP4698776B2 (ja) | 2011-06-08 |

Family

ID=10805819

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP01507698A Expired - Fee Related JP4698776B2 (ja) | 1997-01-11 | 1998-01-09 | 低電圧二重平衡型ミキサー回路装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6211718B1 (ja) |

| EP (1) | EP0853376B1 (ja) |

| JP (1) | JP4698776B2 (ja) |

| DE (1) | DE69706954T2 (ja) |

| GB (1) | GB2321149B (ja) |

Families Citing this family (47)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6061551A (en) | 1998-10-21 | 2000-05-09 | Parkervision, Inc. | Method and system for down-converting electromagnetic signals |

| US7515896B1 (en) | 1998-10-21 | 2009-04-07 | Parkervision, Inc. | Method and system for down-converting an electromagnetic signal, and transforms for same, and aperture relationships |

| US7295826B1 (en) | 1998-10-21 | 2007-11-13 | Parkervision, Inc. | Integrated frequency translation and selectivity with gain control functionality, and applications thereof |

| US7236754B2 (en) | 1999-08-23 | 2007-06-26 | Parkervision, Inc. | Method and system for frequency up-conversion |

| US6813485B2 (en) | 1998-10-21 | 2004-11-02 | Parkervision, Inc. | Method and system for down-converting and up-converting an electromagnetic signal, and transforms for same |

| US6542722B1 (en) | 1998-10-21 | 2003-04-01 | Parkervision, Inc. | Method and system for frequency up-conversion with variety of transmitter configurations |

| US7039372B1 (en) | 1998-10-21 | 2006-05-02 | Parkervision, Inc. | Method and system for frequency up-conversion with modulation embodiments |

| US6370371B1 (en) | 1998-10-21 | 2002-04-09 | Parkervision, Inc. | Applications of universal frequency translation |

| US6560301B1 (en) | 1998-10-21 | 2003-05-06 | Parkervision, Inc. | Integrated frequency translation and selectivity with a variety of filter embodiments |

| US7006805B1 (en) | 1999-01-22 | 2006-02-28 | Parker Vision, Inc. | Aliasing communication system with multi-mode and multi-band functionality and embodiments thereof, such as the family radio service |

| US6853690B1 (en) | 1999-04-16 | 2005-02-08 | Parkervision, Inc. | Method, system and apparatus for balanced frequency up-conversion of a baseband signal and 4-phase receiver and transceiver embodiments |

| US6879817B1 (en) | 1999-04-16 | 2005-04-12 | Parkervision, Inc. | DC offset, re-radiation, and I/Q solutions using universal frequency translation technology |

| US6873836B1 (en) | 1999-03-03 | 2005-03-29 | Parkervision, Inc. | Universal platform module and methods and apparatuses relating thereto enabled by universal frequency translation technology |

| US7110435B1 (en) | 1999-03-15 | 2006-09-19 | Parkervision, Inc. | Spread spectrum applications of universal frequency translation |

| US7693230B2 (en) | 1999-04-16 | 2010-04-06 | Parkervision, Inc. | Apparatus and method of differential IQ frequency up-conversion |

| US7110444B1 (en) | 1999-08-04 | 2006-09-19 | Parkervision, Inc. | Wireless local area network (WLAN) using universal frequency translation technology including multi-phase embodiments and circuit implementations |

| US7065162B1 (en) | 1999-04-16 | 2006-06-20 | Parkervision, Inc. | Method and system for down-converting an electromagnetic signal, and transforms for same |

| US7072390B1 (en) | 1999-08-04 | 2006-07-04 | Parkervision, Inc. | Wireless local area network (WLAN) using universal frequency translation technology including multi-phase embodiments |

| US7054296B1 (en) | 1999-08-04 | 2006-05-30 | Parkervision, Inc. | Wireless local area network (WLAN) technology and applications including techniques of universal frequency translation |

| US8295406B1 (en) | 1999-08-04 | 2012-10-23 | Parkervision, Inc. | Universal platform module for a plurality of communication protocols |

| US6591093B1 (en) * | 1999-10-25 | 2003-07-08 | Motorola, Inc. | Circuit and method for frequency translation |

| US7082171B1 (en) | 1999-11-24 | 2006-07-25 | Parkervision, Inc. | Phase shifting applications of universal frequency translation |

| US7292835B2 (en) | 2000-01-28 | 2007-11-06 | Parkervision, Inc. | Wireless and wired cable modem applications of universal frequency translation technology |

| US7010286B2 (en) * | 2000-04-14 | 2006-03-07 | Parkervision, Inc. | Apparatus, system, and method for down-converting and up-converting electromagnetic signals |

| FR2809552B1 (fr) * | 2000-05-25 | 2002-07-19 | Cit Alcatel | Melangeur doublement equilibre en technologie mmic |

| US7554508B2 (en) | 2000-06-09 | 2009-06-30 | Parker Vision, Inc. | Phased array antenna applications on universal frequency translation |

| US6704559B1 (en) * | 2000-09-18 | 2004-03-09 | Maxim Integrated Products, Inc. | Broadband RF mixer with improved intermodulation suppression |

| US7010559B2 (en) | 2000-11-14 | 2006-03-07 | Parkervision, Inc. | Method and apparatus for a parallel correlator and applications thereof |

| US7454453B2 (en) | 2000-11-14 | 2008-11-18 | Parkervision, Inc. | Methods, systems, and computer program products for parallel correlation and applications thereof |

| US6653885B2 (en) * | 2001-05-03 | 2003-11-25 | Peregrine Semiconductor Corporation | On-chip integrated mixer with balun circuit and method of making the same |

| US7072427B2 (en) | 2001-11-09 | 2006-07-04 | Parkervision, Inc. | Method and apparatus for reducing DC offsets in a communication system |

| US7085335B2 (en) * | 2001-11-09 | 2006-08-01 | Parkervision, Inc. | Method and apparatus for reducing DC offsets in a communication system |

| US6975848B2 (en) | 2002-06-04 | 2005-12-13 | Parkervision, Inc. | Method and apparatus for DC offset removal in a radio frequency communication channel |

| US7321640B2 (en) * | 2002-06-07 | 2008-01-22 | Parkervision, Inc. | Active polyphase inverter filter for quadrature signal generation |

| US7460584B2 (en) | 2002-07-18 | 2008-12-02 | Parkervision, Inc. | Networking methods and systems |

| US7379883B2 (en) | 2002-07-18 | 2008-05-27 | Parkervision, Inc. | Networking methods and systems |

| SE0203880D0 (sv) | 2002-12-20 | 2002-12-20 | Infineon Technologies Wireless | An RF front-end receiver |

| JP2004207874A (ja) * | 2002-12-24 | 2004-07-22 | Toshiba Corp | 周波数変換器及び無線通信端末装置 |

| US6765441B1 (en) * | 2003-01-24 | 2004-07-20 | Atheros Communications, Inc. | Differential amplifier |

| US7146149B1 (en) * | 2003-07-10 | 2006-12-05 | Maxim Integrated Products, Inc. | High isolation switch buffer for frequency hopping radios |

| DE102005005332A1 (de) * | 2005-01-28 | 2006-08-10 | Atmel Germany Gmbh | Mischstufe und Verfahren zur Mischung von Signalen verschiedener Frequenzen |

| WO2007046732A1 (en) * | 2005-10-20 | 2007-04-26 | Telefonaktiebolaget L M Ericsson (Publ) | A transconductance stage arrangement |

| US20080113644A1 (en) * | 2006-11-14 | 2008-05-15 | Saverio Trotta | Low Noise Mixer |

| US8515362B2 (en) * | 2008-10-30 | 2013-08-20 | Qualcomm, Incorporated | Mixer architectures |

| US9948239B2 (en) | 2016-09-21 | 2018-04-17 | Qualcomm Incorporated | Configurable mixer |

| EP3840220A1 (en) * | 2019-12-20 | 2021-06-23 | Socionext Inc. | Mixer circuitry |

| US11381203B2 (en) | 2020-08-07 | 2022-07-05 | Analog Devices International Unlimited Company | Flicker noise elimination in a double balanced mixer DC bias circuit |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NL8301099A (nl) * | 1983-03-29 | 1984-10-16 | Philips Nv | Afstembare ontvangeringangsschakeling. |

| JP2884869B2 (ja) * | 1991-12-12 | 1999-04-19 | 日本電気株式会社 | 周波数ミキサ回路 |

| FR2695272B1 (fr) * | 1992-08-26 | 1994-12-09 | Philips Composants | Circuit mélangeur pour des signaux de radio ou de télévision. |

| US5521545A (en) * | 1994-10-21 | 1996-05-28 | Motorola, Inc. | Collector-injection mixer with radio frequency signal applied to collectors of lower transistor pair |

| US5826182A (en) * | 1995-01-25 | 1998-10-20 | Analog Devices, Inc. | Double balanced RF mixer with predetermined input impedance |

| JPH08223065A (ja) * | 1995-02-13 | 1996-08-30 | Toshiba Corp | 周波数変換器 |

| GB2299230A (en) * | 1995-03-24 | 1996-09-25 | Northern Telecom Ltd | Low voltage mixer, multiplier or modulator circuit |

-

1997

- 1997-01-11 GB GB9700486A patent/GB2321149B/en not_active Expired - Fee Related

- 1997-12-16 DE DE69706954T patent/DE69706954T2/de not_active Expired - Fee Related

- 1997-12-16 EP EP97310154A patent/EP0853376B1/en not_active Expired - Lifetime

-

1998

- 1998-01-07 US US09/003,908 patent/US6211718B1/en not_active Expired - Lifetime

- 1998-01-09 JP JP01507698A patent/JP4698776B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| EP0853376B1 (en) | 2001-09-26 |

| GB2321149B (en) | 2001-04-04 |

| DE69706954T2 (de) | 2002-04-11 |

| GB9700486D0 (en) | 1997-02-26 |

| EP0853376A1 (en) | 1998-07-15 |

| GB2321149A (en) | 1998-07-15 |

| JPH10209760A (ja) | 1998-08-07 |

| US6211718B1 (en) | 2001-04-03 |

| DE69706954D1 (de) | 2001-10-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4698776B2 (ja) | 低電圧二重平衡型ミキサー回路装置 | |

| JPH10209760A5 (ja) | ||

| US6417735B1 (en) | Amplifier with bias compensation using a current mirror circuit | |

| JP3263089B2 (ja) | 低電圧アナログフロントエンド | |

| JP2002111412A (ja) | 増幅回路 | |

| US6043710A (en) | Low-voltage amplifiers | |

| JP2559392B2 (ja) | ブリツジ増幅器 | |

| KR100830812B1 (ko) | 고주파 증폭기 회로 | |

| JP3944541B2 (ja) | 増幅回路装置 | |

| JP2622321B2 (ja) | 高周波数クロス接合折返しカスコード回路 | |

| US20010048336A1 (en) | Analog multiplying circuit and variable gain amplifying circuit | |

| US4163908A (en) | Bias circuit for complementary transistors | |

| JP2002368559A (ja) | 差動増幅回路、ミキサ回路および可変利得増幅回路 | |

| JP3097563B2 (ja) | 利得可変増幅器 | |

| JPH0677739A (ja) | 利得制御回路 | |

| JPH10209761A (ja) | ミキサ回路装置 | |

| JP3080488B2 (ja) | 差動増幅器 | |

| JP3233107B2 (ja) | バイアス発生回路およびミキサ | |

| JP3802425B2 (ja) | エミッタ接地差動増幅器用バイアス回路内蔵の半導体集積回路 | |

| US20050104659A1 (en) | Darlington differential amplifier | |

| JP3834422B2 (ja) | 可変利得増幅器 | |

| KR20010017641A (ko) | 저 전압용 발룬 회로 | |

| JPH1041750A (ja) | 利得制御周波数変換回路 | |

| JP2007028503A (ja) | 電圧―電流変換回路及びそれを備える差動電圧増幅回路、電圧制御利得可変増幅回路ならびにミキサ回路 | |

| JP4221131B2 (ja) | 可変利得増幅回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061016 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061107 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20070207 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20070216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070322 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20070323 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20070911 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071207 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20080111 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20080613 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100122 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110302 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |