JP4641741B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4641741B2 JP4641741B2 JP2004159597A JP2004159597A JP4641741B2 JP 4641741 B2 JP4641741 B2 JP 4641741B2 JP 2004159597 A JP2004159597 A JP 2004159597A JP 2004159597 A JP2004159597 A JP 2004159597A JP 4641741 B2 JP4641741 B2 JP 4641741B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- impurity region

- impurity

- channel

- thin film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 60

- 239000012535 impurity Substances 0.000 claims description 160

- 239000000758 substrate Substances 0.000 claims description 71

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 20

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 18

- 239000011521 glass Substances 0.000 claims description 12

- 239000010453 quartz Substances 0.000 claims description 2

- 239000010409 thin film Substances 0.000 description 165

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 145

- 239000010408 film Substances 0.000 description 87

- 239000004973 liquid crystal related substance Substances 0.000 description 45

- 229910052814 silicon oxide Inorganic materials 0.000 description 19

- 230000015556 catabolic process Effects 0.000 description 18

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 14

- 229910052698 phosphorus Inorganic materials 0.000 description 14

- 239000011574 phosphorus Substances 0.000 description 14

- 239000010410 layer Substances 0.000 description 13

- 239000011229 interlayer Substances 0.000 description 11

- 238000000034 method Methods 0.000 description 11

- 239000003990 capacitor Substances 0.000 description 10

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- 230000008569 process Effects 0.000 description 7

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 6

- 230000001133 acceleration Effects 0.000 description 6

- 229910021417 amorphous silicon Inorganic materials 0.000 description 6

- 229910052804 chromium Inorganic materials 0.000 description 6

- 239000011651 chromium Substances 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 6

- 238000004380 ashing Methods 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 238000005530 etching Methods 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 238000003860 storage Methods 0.000 description 4

- 230000005684 electric field Effects 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910017083 AlN Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910003465 moissanite Inorganic materials 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

- H01L29/78627—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile with a significant overlap between the lightly doped drain and the gate electrode, e.g. GOLDD

Description

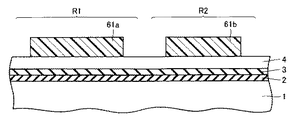

本発明の実施の形態1に係る半導体装置として液晶表示装置について説明する。図1は、液晶表示装置のTFTアレイ基板の構成を示すブロック図である。まず、画像を表示するための画素部21は、画素薄膜トランジスタ22、液晶(画素容量)23、蓄積容量24、コモン電極(コモン線)25、データ線26、アドレス線27、Cs(Common Source)線28および画素電極29から構成されている。

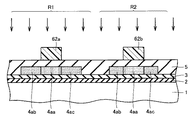

そのレジストパターン62a,62bをマスクとして、たとえばドーズ量7×1012atom/cm2、加速エネルギ80KeVにて不純物領域4aaにリンを注入することにより、領域R1,R2にはそれぞれ不純物領域4ab,4acが形成される。この注入量がGOLD領域における注入量(1×1018atom/cm3)になる。その後、アッシングと薬液処理を施すことで、レジストパターン62a,62bが除去される。

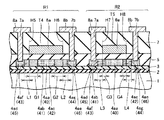

ここでは、GOLD領域に加えてLDD領域を含む薄膜トランジスタを有する液晶表示装置のTFTアレイ基板を例に挙げる。

そのレジストパターン62a,62bをマスクとして、たとえばドーズ量7×1012atom/cm2、加速エネルギ80KeVにて不純物領域4aaにリンを注入することにより、領域R1,R2にはそれぞれ不純物領域4ab,4acが形成される。この注入量がGOLD領域における注入量(1×1018atom/cm3)になる。その後、アッシングと薬液処理を施すことで、レジストパターン62a,62bが除去される。

ここでは、液晶表示装置のTFTアレイ基板のバリエーションの一例として、実施の形態1において説明した薄膜トランジスタT1,T2と、実施の形態2において説明した薄膜トランジスタT4,T5とを有するTFTアレイ基板について説明する。

Claims (10)

- それぞれ半導体層、絶縁膜および電極を有して所定の基板上に形成された複数の半導体素子を含む半導体装置であって、

前記電極は単層の導電層から形成され、

複数の前記半導体素子のそれぞれは、

前記半導体層に形成され、所定の不純物濃度を有する第1不純物領域と、

前記第1不純物領域と距離を隔てて前記半導体層に形成され、所定の不純物濃度を有する第2不純物領域と、

前記第1不純物領域と前記第2不純物領域との間に位置する前記半導体層の部分に前記第1不純物領域および前記第2不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有するチャネルとなるチャネル領域と、

前記第1不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域と接するように形成され、前記第1不純物領域よりも低い不純物濃度を有するとともに、チャネル長方向に一定の不純物濃度を有する第3不純物領域と、

前記第2不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域に接するように形成され、前記第2不純物領域よりも低い不純物濃度を有するとともに、チャネル長方向に一定の不純物濃度を有する第4不純物領域と、

前記第1不純物領域と前記第3不純物領域との間に位置する前記半導体層の部分に形成され、前記第1不純物領域に接する第5不純物領域と、

前記第2不純物領域と前記第4不純物領域との間に位置する前記半導体層の部分に形成され、前記第2不純物領域に接する第6不純物領域と

を有し、

複数の前記半導体素子のそれぞれでは、

前記絶縁膜は前記半導体層と前記電極とにそれぞれ接するように前記半導体層と前記電極との間に形成され、

前記電極は、対向する一方側部および他方側部を有し、

前記第3不純物領域と前記第5不純物領域との接合部および前記一方側部は略同一平面上に位置するとともに、前記第4不純物領域と前記第6不純物領域との接合部および前記他方側部は略同一平面上に位置し、

前記電極は、前記チャネル領域、前記第3不純物領域および前記第4不純物領域のそれぞれの全体と対向してオーバラップし、前記第1不純物領域、前記第2不純物領域、前記第5不純物領域および前記第6不純物領域とはオーバラップしないように形成され、

前記電極と前記第3不純物領域とが対向してオーバラップしている部分および前記電極と前記第4不純物領域とが対向してオーバラップしている部分が、チャネル長方向に略等しい所定のオーバラップ長を有し、

複数の前記半導体素子は、

前記所定のオーバラップ長として第1のオーバラップ長を有する第1素子と、

前記所定のオーバラップ長として前記第1のオーバラップ長よりも短い第2のオーバラップ長を有する第2素子と

を備え、

前記第1素子および前記第2素子をそれぞれ形成する前記第1不純物領域〜前記第6不純物領域は、同じ導電型とされ、

前記第1素子および前記第2素子では、前記第5不純物領域のチャネル長方向の長さと前記第6不純物領域のチャネル長方向の長さはすべて同じ長さにされた、半導体装置。 - 複数の前記半導体素子は、

前記所定のオーバラップ長として第3のオーバラップ長を有する第3素子と、

前記所定のオーバラップ長として前記第3のオーバラップ長よりも短い第4のオーバラップ長を有する第4素子と

を備え、

前記第3素子および前記第4素子のそれぞれは、

前記半導体層に形成され、所定の不純物濃度を有する第7不純物領域と、

前記第7不純物領域と距離を隔てて前記半導体層に形成され、所定の不純物濃度を有する第8不純物領域と、

前記第7不純物領域と前記第8不純物領域との間に位置する前記半導体層の部分に前記第7不純物領域および前記第8不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有するチャネルとなるチャネル領域と、

前記第7不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域と接するように形成され、前記第7不純物領域よりも低い不純物濃度を有するとともに、チャネル長方向に一定の不純物濃度を有する第9不純物領域と、

前記第8不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域に接するように形成され、前記第8不純物領域よりも低い不純物濃度を有するとともに、チャネル長方向に一定の不純物濃度を有する第10不純物領域と

を有し、

前記第3素子および前記第4素子をそれぞれ形成する前記第7不純物領域〜前記第10不純物領域は、同じ導電型とされた、請求項1記載の半導体装置。 - 前記第1素子〜前記第4素子は、所定の前記基板として同一の基板上に形成された、請求項2記載の半導体装置。

- 複数の画素から構成され、画像を表示するための画素部と、

前記画素部を駆動するための駆動回路部と

を備え、

前記画素部および前記駆動回路部は、前記第1素子および前記第3素子の少なくともいずれかによって構成される、請求項2または3に記載の半導体装置。 - 前記第1素子〜前記第4素子は、nチャネル型のトランジスタである、請求項2〜4のいずれかに記載の半導体装置。

- 前記第3不純物領域および前記第4不純物領域の不純物濃度は、1×1017atom/

cm3以上で1×1019atom/cm3以下である、請求項1〜5のいずれかに記載の半

導体装置。 - 前記第3不純物領域および前記第4不純物領域の不純物濃度は、前記第5不純物領域および前記第6不純物領域の不純物濃度よりも低く設定された、請求項2〜6のいずれかに記載の半導体装置。

- 前記第1のオーバラップ長〜前記第4のオーバラップ長は、0.1μm以上2μm以下の範囲で設定された、請求項2〜7のいずれかに記載の半導体装置。

- 所定の前記基板はガラス基板および石英基板のいずれかである、請求項1〜8のいずれかに記載の半導体装置。

- 前記半導体層は多結晶シリコンである、請求項1〜9のいずれかに記載の半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004159597A JP4641741B2 (ja) | 2004-05-28 | 2004-05-28 | 半導体装置 |

| US11/137,660 US7262433B2 (en) | 2004-05-28 | 2005-05-26 | Semiconductor device |

| CN2005100713739A CN1716634B (zh) | 2004-05-28 | 2005-05-27 | 半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004159597A JP4641741B2 (ja) | 2004-05-28 | 2004-05-28 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005340638A JP2005340638A (ja) | 2005-12-08 |

| JP2005340638A5 JP2005340638A5 (ja) | 2006-11-24 |

| JP4641741B2 true JP4641741B2 (ja) | 2011-03-02 |

Family

ID=35424199

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004159597A Expired - Fee Related JP4641741B2 (ja) | 2004-05-28 | 2004-05-28 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7262433B2 (ja) |

| JP (1) | JP4641741B2 (ja) |

| CN (1) | CN1716634B (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW578122B (en) * | 2002-06-05 | 2004-03-01 | Au Optronics Corp | Driving circuit for thin film transistor liquid crystal display |

| JP4641741B2 (ja) | 2004-05-28 | 2011-03-02 | 三菱電機株式会社 | 半導体装置 |

| JP2006269808A (ja) * | 2005-03-24 | 2006-10-05 | Mitsubishi Electric Corp | 半導体装置および画像表示装置 |

| TWI409934B (zh) * | 2005-10-12 | 2013-09-21 | Semiconductor Energy Lab | 半導體裝置 |

| JP4548408B2 (ja) | 2006-11-29 | 2010-09-22 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| CN102576732B (zh) | 2009-07-18 | 2015-02-25 | 株式会社半导体能源研究所 | 半导体装置与用于制造半导体装置的方法 |

| US8653531B2 (en) | 2009-11-12 | 2014-02-18 | Sharp Kabushiki Kaisha | Thin film transistor and display device |

| KR20150044327A (ko) * | 2013-10-16 | 2015-04-24 | 삼성디스플레이 주식회사 | 전계 완화 박막트랜지스터, 이의 제조 방법 및 이를 포함하는 표시장치 |

| KR102586938B1 (ko) * | 2016-09-05 | 2023-10-10 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04269836A (ja) * | 1991-02-25 | 1992-09-25 | Sony Corp | nチャンネルMIS半導体装置 |

| JP2000223716A (ja) * | 1998-11-25 | 2000-08-11 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000243975A (ja) * | 1998-12-25 | 2000-09-08 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000332257A (ja) * | 1999-03-12 | 2000-11-30 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6365917B1 (en) * | 1998-11-25 | 2002-04-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2000252473A (ja) | 1998-12-18 | 2000-09-14 | Semiconductor Energy Lab Co Ltd | 配線およびその作製方法、半導体装置およびその作製方法 |

| JP4850328B2 (ja) | 2000-08-29 | 2012-01-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4801262B2 (ja) | 2001-01-30 | 2011-10-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5038560B2 (ja) * | 2001-08-01 | 2012-10-03 | ゲットナー・ファンデーション・エルエルシー | 電界効果型トランジスタ及びその製造方法並びに該トランジスタを使った液晶表示装置及びその製造方法 |

| JP4673513B2 (ja) * | 2001-08-01 | 2011-04-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4641741B2 (ja) | 2004-05-28 | 2011-03-02 | 三菱電機株式会社 | 半導体装置 |

-

2004

- 2004-05-28 JP JP2004159597A patent/JP4641741B2/ja not_active Expired - Fee Related

-

2005

- 2005-05-26 US US11/137,660 patent/US7262433B2/en not_active Expired - Fee Related

- 2005-05-27 CN CN2005100713739A patent/CN1716634B/zh not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04269836A (ja) * | 1991-02-25 | 1992-09-25 | Sony Corp | nチャンネルMIS半導体装置 |

| JP2000223716A (ja) * | 1998-11-25 | 2000-08-11 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000243975A (ja) * | 1998-12-25 | 2000-09-08 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000332257A (ja) * | 1999-03-12 | 2000-11-30 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050263770A1 (en) | 2005-12-01 |

| CN1716634A (zh) | 2006-01-04 |

| JP2005340638A (ja) | 2005-12-08 |

| US7262433B2 (en) | 2007-08-28 |

| CN1716634B (zh) | 2010-05-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107731858B (zh) | 一种阵列基板、其制作方法及显示面板 | |

| US5396084A (en) | Thin film transistor device having driving circuit and matrix circuit | |

| KR100815064B1 (ko) | 박막 반도체 장치 및 그의 구동 방법 | |

| JP5101116B2 (ja) | 表示装置及びその製造方法 | |

| US6995048B2 (en) | Thin film transistor and active matrix type display unit production methods therefor | |

| KR100727714B1 (ko) | 반도체 장치 및 화상 표시 장치 | |

| US7262433B2 (en) | Semiconductor device | |

| JP2011518434A (ja) | 薄膜トランジスタおよびアクティブマトリクスディスプレイ | |

| JP2006332400A (ja) | 薄膜半導体装置およびその製造方法 | |

| KR100458710B1 (ko) | Oeld용 결정질 실리콘 박막트랜지스터 패널 및 제작방법 | |

| US7432138B2 (en) | Thin film transistor substrate and manufacturing method for the same | |

| KR100458714B1 (ko) | Oeld용 결정질 실리콘 박막트랜지스터 패널 및 제작방법 | |

| US7256457B2 (en) | Thin-film transistor device, utilizing different types of thin film transistors | |

| WO2006126423A1 (ja) | 薄膜トランジスタ基板及びそれを備えた液晶表示装置、並びに薄膜トランジスタ基板の製造方法 | |

| JP2005311037A (ja) | 半導体装置およびその製造方法 | |

| US8357977B2 (en) | Semiconductor device and method for manufacturing same | |

| JP2006330719A (ja) | 有機発光ディスプレイ及びその製造方法 | |

| US8759166B2 (en) | Method for manufacturing thin film transistor device | |

| WO2011135890A1 (ja) | 半導体装置、表示装置、および半導体装置の製造方法 | |

| JP5414712B2 (ja) | 半導体装置 | |

| GB2459666A (en) | Thin film transistor with low leakage current | |

| JP2002083973A (ja) | 薄膜トランジスタとその製造方法、及びそれを用いた液晶表示装置 | |

| JP2005064049A (ja) | 薄膜トランジスタ及びその形成方法及びこの薄膜トランジスタを用いて構成される回路及び表示装置 | |

| JP2008227210A (ja) | 半導体装置、半導体装置の製造方法、および電気光学装置 | |

| KR20030081894A (ko) | 박막 트랜지스터 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061005 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061005 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090903 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090908 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091102 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100330 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100518 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101124 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101130 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4641741 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131210 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |