JP4587678B2 - アレイ基板の検査方法及び検査装置 - Google Patents

アレイ基板の検査方法及び検査装置 Download PDFInfo

- Publication number

- JP4587678B2 JP4587678B2 JP2004054863A JP2004054863A JP4587678B2 JP 4587678 B2 JP4587678 B2 JP 4587678B2 JP 2004054863 A JP2004054863 A JP 2004054863A JP 2004054863 A JP2004054863 A JP 2004054863A JP 4587678 B2 JP4587678 B2 JP 4587678B2

- Authority

- JP

- Japan

- Prior art keywords

- signal lines

- inspection

- pixel

- array substrate

- defective

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000007689 inspection Methods 0.000 title claims description 157

- 238000000034 method Methods 0.000 title claims description 99

- 239000000758 substrate Substances 0.000 title claims description 52

- 230000002950 deficient Effects 0.000 claims description 102

- 238000012360 testing method Methods 0.000 claims description 21

- 238000000691 measurement method Methods 0.000 description 79

- 230000007547 defect Effects 0.000 description 19

- 238000010586 diagram Methods 0.000 description 14

- 238000012883 sequential measurement Methods 0.000 description 14

- 238000005259 measurement Methods 0.000 description 11

- 239000004973 liquid crystal related substance Substances 0.000 description 8

- 239000011159 matrix material Substances 0.000 description 7

- 239000003990 capacitor Substances 0.000 description 6

- 238000001514 detection method Methods 0.000 description 6

- 241000375392 Tana Species 0.000 description 3

- 238000007796 conventional method Methods 0.000 description 3

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 238000012951 Remeasurement Methods 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 238000013102 re-test Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/006—Electronic inspection or testing of displays and display drivers, e.g. of LED or LCD displays

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136254—Checking; Testing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/10—Dealing with defective pixels

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Liquid Crystal (AREA)

- Testing Of Optical Devices Or Fibers (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Testing Electric Properties And Detecting Electric Faults (AREA)

Description

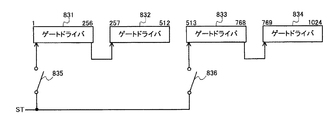

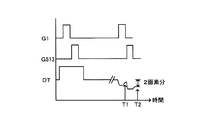

本実施の形態による検査方法は、まず最初の検査として「2画素同時測定方法」を実施し、次に再検査として「不良アドレス特定方法」を実施する。

(1)図2(a)に示すように、検査するアレイ基板10を準備する。ここでは、アレイ基板は900本の走査信号線を有し、700本目の走査信号線上に1つの不良画素3Dを有するものと仮定する。

不良画素のアドレスを特定する方法として、「不良候補画素個別測定方法」、「3画素同時測定方法」、「片側2画素同時測定方法」、及び「不良候補画素個別測定方法及び複数画素同時測定方法の切替方法」がある。以下、これらを順に説明する。

上記2画素同時測定方法で不良候補に挙げた全ての画素を1個ずつ順番に再検査する。図2(c)に示すように、本例では、まず250本目の走査信号線2Aを駆動してその上にある不良候補の画素3Cに蓄積された電荷量を測定し、次に700本目の走査信号線2Aを駆動してその上にある不良候補の画素3Cに蓄積された電荷量を測定する。250本目の走査信号線2A上の画素3Cは正常であるから通常の電荷量が検出されるが、700本目の走査信号線2A上の画素3Cは不良であるから通常と異なる電荷量が検出される。したがって、この画素3Cを不良と判別し、そのアドレスを特定できる。

図6(a)及び(b)に示すように、上述した通り最初の検査として2画素同時測定方法を実施し、不良画素の存在が判明した場合、図6(c)に示すように、検査ブロックの数を変更し、再びアレイ基板10全体を検査する。詳細は次の通り。

図9(a)及び(b)に示すように、最初の検査で2画素同時測定方法を実施し、不良画素の存在が判明した場合、図9(c)に示すように、再検査でアレイ基板10の前半又は後半のみについて再び2画素同時測定方法を実施してもよい。前半又は後半の一方に不良画素が存在すれば、その画素のアドレスを特定すればよく、不良画素が存在しなければ、当該他方の画素のアドレスを特定すれば足りるからである。詳細は次の通り。

実際のアレイ基板10では不良画素の数は0〜5個の場合が多い。不良画素の数が少ない場合、不良アドレス特定方法として不良候補画素個別測定方法を採用する方が複数画素同時測定方法を採用するよりも検査時間が短くなる。そのため、不良画素の数が少ない場合は不良アドレス特定方法を不良候補画素個別測定方法に切り替え、不良画素の数が多い場合は不良アドレス特定方法を複数画素同時測定方法に切り替えるようにしてもよい。この方法は、たとえば図10に示すようなソフトウエアで実現することができる。

以上、検査方法を説明したが、次にこの検査方法を実現するための検査装置の例を説明する。

2 走査信号線

3 画素

4 検出回路

7 データ信号線駆動回路

8 走査信号線駆動回路

10 アレイ基板

10A〜10G 検査ブロック

Claims (6)

- 複数の信号線を有するアレイ基板の検査方法であって、

各々が複数の信号線を含むN 1 (2以上の整数)個の第1検査ブロックに前記アレイ基板を分割するステップと、

前記第1検査ブロックの各々から1本ずつ合計N 1 本の信号線を選択するステップと、

選択したN 1 本の信号線を同時に検査するステップと、

各々が複数の信号線を含むN2(N1と異なる2以上の整数)個の第2検査ブロックに前記アレイ基板を分割するステップと、

前記第2検査ブロックの各々から1本ずつ合計N2本の信号線を選択するステップと、

選択したN2本の信号線を同時に再検査するステップとを含むことを特徴とするアレイ基板の検査方法。 - 複数の信号線を有するアレイ基板の検査方法であって、

各々が複数の信号線を含むN 1 (2以上の整数)個の第1検査ブロックに前記アレイ基板を分割するステップと、

前記第1検査ブロックの各々から1本ずつ合計N 1 本の信号線を選択するステップと、

選択したN 1 本の信号線を同時に検査するステップと、

N1は2であり、

前記検査方法はさらに、

前記第1検査ブロックの一方の信号線を再検査するステップを含むことを特徴とするアレイ基板の検査方法。 - 請求項2に記載の検査方法であって、

前記再検査のステップは、

各々が複数の信号線を含むN2(2以上の整数)個の第2検査ブロックに前記アレイ基板を分割するステップと、

前記第2検査ブロックの各々から1本ずつ合計N2本の信号線を選択するステップと、

選択したN2本の信号線を同時に検査するステップとを含むことを特徴とする検査方法。 - 複数の信号線を有するアレイ基板の検査方法であって、

各々が複数の信号線を含むN 1 (2以上の整数)個の第1検査ブロックに前記アレイ基板を分割するステップと、

前記第1検査ブロックの各々から1本ずつ合計N 1 本の信号線を選択するステップと、

選択したN 1 本の信号線を同時に検査するステップと、

検査の結果に従って不良の信号線の数をカウントするステップと、

カウントした数が予め定められた数よりも少ないとき、不良の信号線を再検査するステップと、

カウントした数が予め定められた数よりも多いとき、各々が複数の信号線を含むN2(N1と異なる2以上の整数)個の第2検査ブロックに前記アレイ基板を分割するステップと、

前記第2検査ブロックの各々から1本ずつ合計N2本の信号線を選択するステップと、

選択したN2本の信号線を同時に再検査するステップとを含むことを特徴とするアレイ基板の検査方法。 - 請求項1〜4のいずれか1項に記載の検査方法であって、

前記検査のステップは、

選択した信号線を順番に駆動するステップと、

N1本の信号線の駆動により順番に読み出されたデータ信号をそれぞれ検出するステップとを含むことを特徴とするアレイ基板の検査方法。 - 請求項5に記載の検査方法であって、

前記駆動のステップは、駆動した信号線をその次の信号線を駆動するまで駆動し続けることを特徴とするアレイ基板の検査方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004054863A JP4587678B2 (ja) | 2004-02-27 | 2004-02-27 | アレイ基板の検査方法及び検査装置 |

| TW094102899A TW200600803A (en) | 2004-02-27 | 2005-01-31 | Method and device for testing array substrate |

| US11/063,748 US7508229B2 (en) | 2004-02-27 | 2005-02-24 | Method and device for testing array substrate |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004054863A JP4587678B2 (ja) | 2004-02-27 | 2004-02-27 | アレイ基板の検査方法及び検査装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010178524A Division JP5328733B2 (ja) | 2010-08-09 | 2010-08-09 | アレイ基板の検査方法及び検査装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005242211A JP2005242211A (ja) | 2005-09-08 |

| JP2005242211A5 JP2005242211A5 (ja) | 2007-03-22 |

| JP4587678B2 true JP4587678B2 (ja) | 2010-11-24 |

Family

ID=34917904

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004054863A Expired - Fee Related JP4587678B2 (ja) | 2004-02-27 | 2004-02-27 | アレイ基板の検査方法及び検査装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7508229B2 (ja) |

| JP (1) | JP4587678B2 (ja) |

| TW (1) | TW200600803A (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4428255B2 (ja) * | 2005-02-28 | 2010-03-10 | エプソンイメージングデバイス株式会社 | 電気光学装置、駆動方法および電子機器 |

| JP5357399B2 (ja) * | 2007-03-09 | 2013-12-04 | 株式会社ジャパンディスプレイ | 表示装置 |

| TWI408382B (zh) * | 2009-11-13 | 2013-09-11 | 成像裝置的檢測方法及系統 | |

| JP5013554B2 (ja) * | 2010-03-31 | 2012-08-29 | 株式会社ジャパンディスプレイセントラル | 液晶表示装置 |

| US9601070B2 (en) | 2014-11-24 | 2017-03-21 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Method for performing detection on display panel |

| CN104375294B (zh) * | 2014-11-24 | 2017-03-15 | 深圳市华星光电技术有限公司 | 一种显示面板的检测电路及其检测方法 |

| CA2889870A1 (en) * | 2015-05-04 | 2016-11-04 | Ignis Innovation Inc. | Optical feedback system |

| CN109637405B (zh) * | 2018-12-05 | 2021-04-06 | 惠科股份有限公司 | 阵列基板的测试方法、装置及存储介质 |

| CN116129780B (zh) * | 2023-04-04 | 2023-06-23 | 惠科股份有限公司 | 故障检测电路、显示面板和故障检测方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10177357A (ja) * | 1996-12-18 | 1998-06-30 | Toshiba Corp | 平面表示装置の製造方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4968931A (en) * | 1989-11-03 | 1990-11-06 | Motorola, Inc. | Apparatus and method for burning in integrated circuit wafers |

| US5546013A (en) * | 1993-03-05 | 1996-08-13 | International Business Machines Corporation | Array tester for determining contact quality and line integrity in a TFT/LCD |

| KR0182184B1 (en) * | 1996-04-24 | 1999-04-15 | Samsung Electronics Co Ltd | Disconnection/short test apparatus and its method of signal line using metrix |

| JP3131585B2 (ja) | 1997-09-30 | 2001-02-05 | 株式会社東芝 | 半導体検査回路および半導体回路の検査方法 |

| JP2001265248A (ja) * | 2000-03-14 | 2001-09-28 | Internatl Business Mach Corp <Ibm> | アクティブ・マトリックス表示装置、及び、その検査方法 |

| TW589455B (en) * | 2000-11-24 | 2004-06-01 | Hannstar Display Corp | Testing method for LCD panel |

| JP4112300B2 (ja) * | 2002-07-26 | 2008-07-02 | 株式会社半導体エネルギー研究所 | 電気的検査方法及び半導体表示装置の作製方法 |

-

2004

- 2004-02-27 JP JP2004054863A patent/JP4587678B2/ja not_active Expired - Fee Related

-

2005

- 2005-01-31 TW TW094102899A patent/TW200600803A/zh not_active IP Right Cessation

- 2005-02-24 US US11/063,748 patent/US7508229B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10177357A (ja) * | 1996-12-18 | 1998-06-30 | Toshiba Corp | 平面表示装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050204219A1 (en) | 2005-09-15 |

| US7508229B2 (en) | 2009-03-24 |

| JP2005242211A (ja) | 2005-09-08 |

| TWI347442B (ja) | 2011-08-21 |

| TW200600803A (en) | 2006-01-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2810844B2 (ja) | Tft/lcdアレイをテストする方法 | |

| US7508229B2 (en) | Method and device for testing array substrate | |

| US20070236244A1 (en) | Test method, semiconductor device, and display | |

| JP6257192B2 (ja) | アレイ基板およびその検査方法ならびに液晶表示装置 | |

| JP2007333823A (ja) | 液晶表示装置および液晶表示装置の検査方法 | |

| US7554359B2 (en) | Circuit for inspecting semiconductor device and inspecting method | |

| JP3879668B2 (ja) | 液晶表示装置とその検査方法 | |

| US7269051B2 (en) | Inspection method of array board and inspection equipment thereof | |

| CN106782250A (zh) | 一种显示面板、其检测方法及显示装置 | |

| JP4473427B2 (ja) | アレイ基板の検査方法及び該検査装置 | |

| TW580684B (en) | Device and method for inspecting pixel of active matrix type display | |

| JP5328733B2 (ja) | アレイ基板の検査方法及び検査装置 | |

| JPH07199872A (ja) | 液晶表示装置 | |

| JP4239299B2 (ja) | アクティブマトリックス型液晶表示装置 | |

| JPH03142499A (ja) | 画像表示装置およびその検査方法 | |

| US6650138B2 (en) | Display device test procedure and apparatus | |

| JP3747409B2 (ja) | 画像表示素子の検査方法および検査装置 | |

| JP2007232404A (ja) | アクティブマトリックスtftアレイの測定方法 | |

| JPH04288588A (ja) | アクティブマトリクス型液晶表示装置 | |

| JP2000180809A (ja) | 液晶表示パネルの検査装置 | |

| JP2003028754A (ja) | 表示装置検査用装置及び表示装置検査方法 | |

| JP2003215192A (ja) | 表示パネルの検査方法および検査装置 | |

| JPH11242239A (ja) | 液晶表示装置の検査方法および液晶表示装置 | |

| JPH01227193A (ja) | ドットマトリックス表示装置 | |

| JP2008015202A (ja) | 表示パネルおよび表示パネル検査方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070206 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070206 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100809 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100824 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100907 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4587678 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130917 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |