JP4562371B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4562371B2 JP4562371B2 JP2003356195A JP2003356195A JP4562371B2 JP 4562371 B2 JP4562371 B2 JP 4562371B2 JP 2003356195 A JP2003356195 A JP 2003356195A JP 2003356195 A JP2003356195 A JP 2003356195A JP 4562371 B2 JP4562371 B2 JP 4562371B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- forming

- semiconductor device

- manufacturing

- support substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Description

Claims (15)

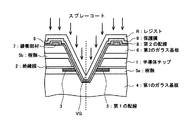

- 第1の配線が形成された半導体ウエハの表面側に第1の支持基板を貼り合わせる工程と、

前記半導体ウエハの裏面側に第2の支持基板を貼り合わせる工程と、

前記第2の支持基板の裏面からダイシングラインに沿って、前記第1の支持基板に至るまで切削を行うことによって溝を形成し、前記第1の配線を部分的に露出させる工程と、

前記溝内で、前記第1の配線の露出部分に接続され、前記第2の支持基板の裏面に延在する第2の配線を形成する工程と、

スプレーコートにより、前記溝内を完全に埋め込むことなく、前記溝内から前記第2の支持基板上に延在する前記第2の配線上に有機系樹脂から成る保護膜を形成する工程と、

前記保護膜の所定位置に前記第2の配線を露出する開口部を形成する工程と、を具備することを特徴とする半導体装置の製造方法。 - 前記第2の支持基板上に、スプレーコートにより、緩衝部材を形成する工程を具備することを特徴とする請求項1に記載の半導体装置の製造方法。

- 前記保護膜の表面に、スプレーコートにより、レジスト層を形成する工程を具備することを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

- 前記開口部に露出された第2の配線上に導電端子を形成する工程を具備することを特徴とする請求項1,2,3のいずれかに記載の半導体装置の製造方法。

- 第1の配線が形成された半導体ウエハの表面上に支持基板を貼り合わせる工程と、

前記半導体ウエハの裏面に溝を形成し、前記第1の配線を部分的に露出させる工程と、

前記溝内で、前記第1の配線の露出部分に接続され、前記半導体ウエハの裏面に延在する第2の配線を形成する工程と、

スプレーコートにより、前記溝内を完全に埋め込むことなく、前記溝内から前記半導体ウエハ上に延在する前記第2の配線上に有機系樹脂から成る保護膜を形成する工程と、

前記保護膜の所定位置に前記第2の配線を露出する開口部を形成する工程と、を具備することを特徴とする半導体装置の製造方法。 - 前記半導体ウエハの裏面に、スプレーコートにより、緩衝部材を形成する工程を具備することを特徴とする請求項5に記載の半導体装置の製造方法。

- 前記保護膜の表面に、スプレーコートにより、レジスト層を形成する工程を具備することを特徴とする請求項5または請求項6に記載の半導体装置の製造方法。

- 前記開口部に露出された第2の配線上に導電端子を形成する工程を具備することを特徴とする請求項5,6,7のいずれかに記載の半導体装置の製造方法。

- 前記有機系樹脂は、熱硬化性を有することを特徴とする請求項1,2,3,4,5,6,7,8のいずれかに記載の半導体装置の製造方法。

- 前記有機系樹脂は、エポキシ樹脂であることを特徴とする請求項1,2,3,4,5,6,7,8,9のいずれかに記載の半導体装置の製造方法。

- 第1の配線が形成された半導体ウエハの表面上に、第1の支持基板を貼り合わせる工程と、

前記半導体ウエハを、当該半導体ウエハの裏面からダイシングラインに沿ってエッチングして、複数の半導体チップに分離する工程と、

前記複数の半導体チップの裏面側に、樹脂を介して第2の支持基板を貼り合わせる工程と、

前記ダイシングラインに沿って、前記第2の支持基板の裏面から、前記第2の支持基板及び前記樹脂を切削し、さらに前記第1の支持基板の一部を切削することによって溝を形成し、前記第1の配線を部分的に露出させる工程と、

前記溝内で、前記第1の配線の露出部分に接続され、前記第2の支持基板の裏面に延在する第2の配線を形成する工程と、

スプレーコートにより、前記溝内を完全に埋め込むことなく、前記溝内から前記第2の支持基板上に延在する前記第2の配線上に有機系樹脂から成る保護膜を形成する工程と、

前記保護膜の所定位置に前記第2の配線を露出する開口部を形成する工程と、を具備することを特徴とする半導体装置の製造方法。 - 前記第2の支持基板上に、スプレーコートにより、緩衝部材を形成する工程を具備することを特徴とする請求項11に記載の半導体装置の製造方法。

- 前記保護膜の表面に、スプレーコートにより、レジスト層を形成する工程を具備することを特徴とする請求項11または請求項12に記載の半導体装置の製造方法。

- 前記開口部に露出された第2の配線上に導電端子を形成する工程を具備することを特徴とする請求項11,12,13のいずれかに記載の半導体装置の製造方法。

- パターニング時のマスク材としてレジスト層を使用する工程において、スプレーコートを用いることを特徴とする請求項1,5,11のいずれかに記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003356195A JP4562371B2 (ja) | 2002-10-30 | 2003-10-16 | 半導体装置の製造方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002315418 | 2002-10-30 | ||

| JP2003356195A JP4562371B2 (ja) | 2002-10-30 | 2003-10-16 | 半導体装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010021808A Division JP5258807B2 (ja) | 2002-10-30 | 2010-02-03 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004172587A JP2004172587A (ja) | 2004-06-17 |

| JP2004172587A5 JP2004172587A5 (ja) | 2006-11-30 |

| JP4562371B2 true JP4562371B2 (ja) | 2010-10-13 |

Family

ID=32715788

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003356195A Expired - Fee Related JP4562371B2 (ja) | 2002-10-30 | 2003-10-16 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4562371B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4936695B2 (ja) * | 2004-09-29 | 2012-05-23 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置及びその製造方法 |

| JP2008166381A (ja) * | 2006-12-27 | 2008-07-17 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP5101157B2 (ja) * | 2007-05-07 | 2012-12-19 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置の製造方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IL123207A0 (en) * | 1998-02-06 | 1998-09-24 | Shellcase Ltd | Integrated circuit device |

| JP2001053033A (ja) * | 1999-08-12 | 2001-02-23 | Texas Instr Japan Ltd | 半導体装置のダイシング方法 |

| JP3455948B2 (ja) * | 2000-05-19 | 2003-10-14 | カシオ計算機株式会社 | 半導体装置およびその製造方法 |

| JP3664432B2 (ja) * | 2000-05-18 | 2005-06-29 | カシオ計算機株式会社 | 半導体装置およびその製造方法 |

| JP3879816B2 (ja) * | 2000-06-02 | 2007-02-14 | セイコーエプソン株式会社 | 半導体装置及びその製造方法、積層型半導体装置、回路基板並びに電子機器 |

-

2003

- 2003-10-16 JP JP2003356195A patent/JP4562371B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004172587A (ja) | 2004-06-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5258807B2 (ja) | 半導体装置の製造方法 | |

| KR100510556B1 (ko) | 초박형 반도체 패키지 및 그 제조방법 | |

| JP3842548B2 (ja) | 半導体装置の製造方法及び半導体装置 | |

| JP2008244437A (ja) | ダイ収容開口部を備えたイメージセンサパッケージおよびその方法 | |

| US6849955B2 (en) | High density integrated circuit packages and method for the same | |

| KR20060101385A (ko) | 반도체 장치 및 그 제조 방법 | |

| US6489667B1 (en) | Semiconductor device and method of manufacturing such device | |

| JP2009094434A (ja) | 半導体装置およびその製造方法 | |

| JPH053183A (ja) | 半導体装置及びその製造方法 | |

| JPH11354560A (ja) | 半導体装置の製造方法 | |

| JP4963989B2 (ja) | 半導体素子搭載用基板およびその製造方法 | |

| JP2004134480A (ja) | 半導体装置及びその製造方法 | |

| US6919264B2 (en) | Method for the solder-stop structuring of elevations on wafers | |

| JP2002313985A (ja) | チップサイズパッケージの製造方法 | |

| JP4562371B2 (ja) | 半導体装置の製造方法 | |

| JP5238985B2 (ja) | 半導体装置の製造方法 | |

| JP3877700B2 (ja) | 半導体装置及びその製造方法 | |

| JP3522403B2 (ja) | 半導体装置 | |

| JP2010016395A5 (ja) | ||

| JP2006351950A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP4522213B2 (ja) | 半導体装置の製造方法 | |

| JP4401330B2 (ja) | 半導体装置及びその製造方法 | |

| JP2003017655A (ja) | 半導体実装体およびそれを用いた半導体装置 | |

| JP4805362B2 (ja) | 半導体装置の製造方法 | |

| JP3381833B2 (ja) | Bga型半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061016 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061016 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070205 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090805 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091002 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091217 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100203 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100426 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100521 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100701 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100727 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130806 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130806 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |