JP4529141B2 - 露光装置及びそれを用いた半導体装置の製造方法 - Google Patents

露光装置及びそれを用いた半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4529141B2 JP4529141B2 JP2005517741A JP2005517741A JP4529141B2 JP 4529141 B2 JP4529141 B2 JP 4529141B2 JP 2005517741 A JP2005517741 A JP 2005517741A JP 2005517741 A JP2005517741 A JP 2005517741A JP 4529141 B2 JP4529141 B2 JP 4529141B2

- Authority

- JP

- Japan

- Prior art keywords

- mask

- wafer

- circuit pattern

- photoresist

- exposure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 227

- 238000004519 manufacturing process Methods 0.000 title claims description 50

- 238000000034 method Methods 0.000 claims description 195

- 229920002120 photoresistant polymer Polymers 0.000 claims description 149

- 230000009467 reduction Effects 0.000 claims description 144

- 230000002829 reductive effect Effects 0.000 claims description 43

- 230000010363 phase shift Effects 0.000 claims description 38

- 239000011521 glass Substances 0.000 claims description 7

- 239000002952 polymeric resin Substances 0.000 claims 4

- 229920003002 synthetic resin Polymers 0.000 claims 4

- 235000012431 wafers Nutrition 0.000 description 356

- 230000008569 process Effects 0.000 description 87

- 238000012546 transfer Methods 0.000 description 53

- 230000003287 optical effect Effects 0.000 description 45

- 238000013461 design Methods 0.000 description 30

- 230000000694 effects Effects 0.000 description 27

- 230000004075 alteration Effects 0.000 description 24

- 239000010410 layer Substances 0.000 description 21

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 19

- 230000015572 biosynthetic process Effects 0.000 description 19

- 238000007654 immersion Methods 0.000 description 19

- 238000012937 correction Methods 0.000 description 18

- 239000000758 substrate Substances 0.000 description 18

- 238000003384 imaging method Methods 0.000 description 17

- 239000000463 material Substances 0.000 description 15

- 238000010586 diagram Methods 0.000 description 14

- 238000012545 processing Methods 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 13

- 238000011161 development Methods 0.000 description 13

- 230000018109 developmental process Effects 0.000 description 13

- 230000006870 function Effects 0.000 description 12

- 239000007788 liquid Substances 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 238000005530 etching Methods 0.000 description 11

- 238000005286 illumination Methods 0.000 description 10

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 10

- 229920005591 polysilicon Polymers 0.000 description 10

- 239000000126 substance Substances 0.000 description 10

- 238000005516 engineering process Methods 0.000 description 9

- 230000007261 regionalization Effects 0.000 description 9

- 229910052814 silicon oxide Inorganic materials 0.000 description 9

- 239000012535 impurity Substances 0.000 description 8

- 239000011229 interlayer Substances 0.000 description 8

- 238000005498 polishing Methods 0.000 description 8

- 238000010894 electron beam technology Methods 0.000 description 7

- 230000007246 mechanism Effects 0.000 description 7

- 238000002834 transmittance Methods 0.000 description 7

- 230000008859 change Effects 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 230000010354 integration Effects 0.000 description 6

- 238000000059 patterning Methods 0.000 description 6

- 238000000206 photolithography Methods 0.000 description 6

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 238000007689 inspection Methods 0.000 description 4

- 230000000873 masking effect Effects 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 238000004904 shortening Methods 0.000 description 4

- 238000004544 sputter deposition Methods 0.000 description 4

- 230000002195 synergetic effect Effects 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 229910000838 Al alloy Inorganic materials 0.000 description 3

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 238000007796 conventional method Methods 0.000 description 3

- 239000006059 cover glass Substances 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 238000012938 design process Methods 0.000 description 3

- 239000007789 gas Substances 0.000 description 3

- 238000000227 grinding Methods 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 238000004088 simulation Methods 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 238000007664 blowing Methods 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000011960 computer-aided design Methods 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 238000007687 exposure technique Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 238000003672 processing method Methods 0.000 description 2

- 210000001747 pupil Anatomy 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- 101100269850 Caenorhabditis elegans mask-1 gene Proteins 0.000 description 1

- 206010034972 Photosensitivity reaction Diseases 0.000 description 1

- 238000012356 Product development Methods 0.000 description 1

- VZPPHXVFMVZRTE-UHFFFAOYSA-N [Kr]F Chemical compound [Kr]F VZPPHXVFMVZRTE-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- ISQINHMJILFLAQ-UHFFFAOYSA-N argon hydrofluoride Chemical compound F.[Ar] ISQINHMJILFLAQ-UHFFFAOYSA-N 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000009835 boiling Methods 0.000 description 1

- WUKWITHWXAAZEY-UHFFFAOYSA-L calcium difluoride Chemical compound [F-].[F-].[Ca+2] WUKWITHWXAAZEY-UHFFFAOYSA-L 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 239000010436 fluorite Substances 0.000 description 1

- 125000001153 fluoro group Chemical class F* 0.000 description 1

- 230000004907 flux Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 230000036211 photosensitivity Effects 0.000 description 1

- 229920003023 plastic Polymers 0.000 description 1

- 238000011165 process development Methods 0.000 description 1

- 238000011946 reduction process Methods 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000002194 synthesizing effect Effects 0.000 description 1

- 230000001131 transforming effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

- H01L21/0273—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers characterised by the treatment of photoresist layers

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/38—Masks having auxiliary features, e.g. special coatings or marks for alignment or testing; Preparation thereof

- G03F1/48—Protective coatings

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F1/00—Originals for photomechanical production of textured or patterned surfaces, e.g., masks, photo-masks, reticles; Mask blanks or pellicles therefor; Containers specially adapted therefor; Preparation thereof

- G03F1/62—Pellicles, e.g. pellicle assemblies, e.g. having membrane on support frame; Preparation thereof

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70216—Mask projection systems

- G03F7/70308—Optical correction elements, filters or phase plates for manipulating imaging light, e.g. intensity, wavelength, polarisation, phase or image shift

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70483—Information management; Active and passive control; Testing; Wafer monitoring, e.g. pattern monitoring

- G03F7/70591—Testing optical components

- G03F7/706—Aberration measurement

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/708—Construction of apparatus, e.g. environment aspects, hygiene aspects or materials

- G03F7/70983—Optical system protection, e.g. pellicles or removable covers for protection of mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/304—Mechanical treatment, e.g. grinding, polishing, cutting

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S438/00—Semiconductor device manufacturing: process

- Y10S438/975—Substrate or mask aligning feature

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S438/00—Semiconductor device manufacturing: process

- Y10S438/976—Temporary protective layer

Landscapes

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Health & Medical Sciences (AREA)

- Public Health (AREA)

- Epidemiology (AREA)

- Environmental & Geological Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Preparing Plates And Mask In Photomechanical Process (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

Description

【0001】

本発明は、光露光技術に係り、例えば半導体集積回路等の製造プロセスにおける回路パタ−ンの転写技術等に適用して有効な技術に関するものである。

【背景技術】

【0002】

集積回路パターンの微細化および高集積化が進み、遠紫外光又は真空紫外光を使用してマスク上の集積回路パターンを半導体ウエハに転写するフォトリソグラフィ工程においては、露光波長の半分より微細な寸法の回路パターンを高精度に半導体ウエハ上へ露光し、パターン形成できる手段が求められている。

集積回路パターンの半導体ウエハへの転写精度の低下を防ぐことに関しては、例えば1996年8月20日、株式会社工業調査会発行、「フォトマスク技術のはなし」、p236〜p240に、半導体ウエハへ転写される集積回路パターンの変形を見込んで、マスク上に形成される回路パターンの寸法または形状を補正してマスクの設計を行い、集積回路パターンの半導体ウエハへの転写精度を向上させる光近接効果補正(Optical Proximity Correction;OPC)技術についての記載がある。

【0003】

また、本発明者による発明である特許第2710967号公報には、マスクを透過する光に位相差を設け、その透過光の干渉を用いて半導体ウエハへ転写される集積回路パターンの解像度を向上させる位相シフト技術が開示されている。

【0004】

また、例えば特許第2634037号公報にはマスク面の照明光に絞りを設けて露光光の分割斜め照明し、半導体ウエハへ転写される集積回路パターンの解像度を向上させる露光技術が開示されている。

また、例えば特開平10−303114号公報には、縮小投影レンズのウエハ面側とウエハ面とのスペースを液浸状態とすることで、微細パターンに対しても結像性能の劣化を招くことのない液浸式投影露光装置が開示されている。

【0005】

また、本発明者による発明である特許第3120474号公報には、遮光パターンを形成したマスクとその透過光の位相を反転させるシフタパターンを形成した基板とを重ね合わせた投影露光方式が開示されている。

【0006】

【特許文献1】

特許第2710967号公報

【特許文献2】

特許第2634037号公報

【特許文献3】

特開平10−303114号公報

【特許文献4】

特許第3120474号公報

【非特許文献1】

1996年8月20日、株式会社工業調査会発行、「フォトマスク技術のはなし」、p236〜p240

【発明の開示】

【発明が解決しようとする課題】

【0007】

半導体集積回路装置の高集積化は留まることなく進展している。半導体集積回路パターンの最小寸法は、量産レベルでも100ナノメータ以下まで微細化されつつある。このような微細な回路パターン形成には主に縮小投影露光方式が用いられてきた。この縮小投影露光方式は、これまでのように光源の短波長化、レンズの大口径化がますます困難になり、高集積化の進展に伴って要求される回路パターンの微細化に対応できなくなっている。

上記公知例の位相シフト技術を用いると露光光の波長の半分程度までは、半導体集積回路パターンの微細化に対応できるとされているが、それ以下は極めて困難である。

【0008】

特許第3120474号公報に開示された遮光パターンを形成したマスクとその透過光の位相を反転させるシフタパターンを形成した基板とを重ね合わせた投影露光方式においては、マスクの回路パターン面に位相シフトパターンの基板を設けると投影露光のパターン歪が増加し、微細な回路パターンの形成に適さないとする問題があった。

また、上記の特開平10−303114号に記載されている液浸式投影露光装置は、微小な泡の発生、露光光の繰り返し照射による液温変化などの課題がある。また、フォトレジスト、現像液の材料に制約があり、実用化に課題がある。

縮小投影露光装置は、投影レンズとウエハ面とで平面上の相対位置を変えて、ウエハ上へマスクパターンの転写を繰り返すものである。このため、例えば、上記液浸式において液体を固体にそのまま置き換えると、縮小投影レンズとウエハ面とで平面上の相対位置を変えることができなくなる。

本発明の目的は、縮小投影露光法を用いて、露光波長の半分より微細な回路パターンの半導体集積回路装置を精度良く、かつ、効率よく製造する手段を提供することである。

本発明の具体的な一つの目的は、縮小投影露光装置によりマスクに形成されたパターンを半導体ウエハ上のフォトレジストに露光する際に、投影露光パターン歪となる投影レンズの瞳面での理想的な波面との光路長差を低減し、投影レンズの実質的開口数を増加させて、通常実現できる以上に微細なパターンを半導体ウエハ上のフォトレジスト面へ精度よく露光する手段を提供することである。

【0009】

本発明の具体的な一つの目的は、マスクに形成された回路パターンを半導体ウエハ上に形成するための縮小投影露光装置、半導体製造プロセス開発用マスクの開発コスト削減する手法を提供することである。また半導体縮装置を開発製造するユーザの投資、半導体集積回路の製造コストを削減し、効率良い半導体製造技術を提供することにある。

本発明の具体的な一つの目的は、半導体ウエハ上の絶縁膜、導電膜に回路パターンを形成する工程において、絶縁膜、導電膜の段差と微細な回路パターン形成の課題を解消し、露光光の波長より微細な回路パターンを精度よく形成する手法を提供することである。

本発明の具体的な一つの目的は、液侵露光における微小な泡の発生、液温変化などの問題やレジスト材料、現像液などの制約を解消し、回路パターン形成プロセスの開発コストを削減する手法を提供することである。

本発明の具体的な一つの目的は、新規の集積回路の開発において、集積度の増加に伴う回路パターンの微細化、投影露光による転写パターンの歪補正による設計開発工数増加を削減する手法を提供することである。

本発明の具体的な一つの目的は、微細な集積回路パターン形成に対して位相シフトマスクの代わりに遮光マスクを適用可能とすることで、マスク製作コスト削減する手法を提供することである。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

すなわち、本発明は、集積回路パターンを形成したマスク、マスクの集積回路パターン面に接触させたマスクカバー、半導体ウエハ上のフォトレジスト面に接触させたウエハカバーを用い、縮小投影露光法により、半導体ウエハ上のフォトレジスト面に回路パターンを露光するものである。露光光は、マスクを照明し、マスクカバー、縮小投影露光装置の投影レンズ、ウエハカバーを透過して、半導体ウエハ上のフォトレジストを露光させる。ウエハカバーを除去して、フォトレジストを現像し、半導体ウエハ上に回路パターンを形成する。

【0011】

また、本発明は、厚さ限定し、マスクの集積回路パターン面に接触させた透明マスクカバーを設け、縮小投影露光法により、収差を低減させて半導体ウエハ上のフォトレジストに集積回路パターンを露光し、精度良い転写パターンを形成するものである。

また、本願において開示される発明のうち、他のものの概要を簡単に説明すれば、次のとおりである。

本発明は、フォトレジスト面に接触した透明液体から成るウエハカバー、ガラスの投影レンズカバーを設けた縮小投影露光装置であり、マスクの集積回路パターンを半導体ウエハ上のフォトレジストに露光する装置である。露光光は、マスクを照明して、縮小投影露光装置の投影レンズ、投影レンズカバー、ウエハカバーを透過し、前記半導体ウエハ上のフォトレジスト面に結像し、露光する機能を備えた装置である。

また、本発明は、縮小投影露光法を用い、従来マスクを流用して半導体ウエハ上で追加縮小した回路パターンを形成するものである。追加縮小する手法は、マスクまたはウエハの少なくとも一方を光軸方向に移動する手段、または縮小投影露光装置の投影レンズの一部である補正レンズを光軸方向に移動する手段を用いる。追加縮小して良好なパターン形成するため、フォトレジスト面に接触させたウエハカバーを用いる。露光光は、マスク、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、半導体ウエハ上のフォトレジスト面にマスクの集積回路パターンを結像させ、露光するものである。

また、本発明は、マスクに形成した集積回路パターンを半導体ウエハ上のフォトレジストに露光するため、次の第一の機能と第二の機能と両方備えた縮小投影露光装置である。

【0012】

第一の機能は、フォトレジスト面に接触させたウエハカバーを用い、半導体ウエハ上のフォトレジストを露光する機能である。露光光は、マスク、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、フォトレジスト面に結像する。

【0013】

第二の機能は、上記ウエハカバーを用いないで半導体ウエハ上のフォトレジストを露光する機能である。露光光は、マスク、縮小投影露光装置の投影レンズを透過し、フォトレジスト面に結像する。

また、本発明は、縮小投影露光装置の露光光の光束がマスクの回路パターンの方向性と周期性に対応してマスク面を斜め照明する手段とフォトレジスト面に接触させたウエハカバーとを併用するものである。露光光は、マスクを照明して、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、半導体ウエハ上のフォトレジスト面にマスクの集積回路パターンを結像し、露光する。ウエハカバーの媒質中で実質的に露光波長が短波長化し、斜め照明による超解像効果と相乗させ、露光光の波長の半分より微細なパターンの形成を可能とする。

また、本発明は、フォトレジスト面に接触させたウエハカバーを用いる回路パターンの形成工程とウエハカバーを用いない工程の両方を含む半導体装置の製造方法である。ウエハカバーを用いた回路パターンの形成工程では、露光光がマスクを照明して、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、半導体ウエハ上のフォトレジスト面にマスクの回路パターンを結像させて露光し、ウエハカバーを除去後、フォトレジストを現像することにより、半導体ウエハ上に回路パターンを形成する。ウエハカバーを用いない回路パターンの形成工程では、露光光がマスクを照明して、縮小投影露光装置の投影レンズを透過し、半導体ウエハ上のフォトレジスト面にマスクの回路パターンを結像させて露光し、フォトレジストを現像して、半導体ウエハ上に回路パターンを形成する。

また、本発明は、回路パターンの位相シフトマスクとフォトレジスト面に接触させたウエハカバーを用い、縮小投影露光法により、半導体ウエハ上に回路パターンを転写するものである。位相シフトマスクによる位相差光の効果と、ウエハカバー媒質中で実質的に露光波長が短くなった効果を相乗させて、露光波長の半分以下の微細な回路パターンの形成を実現させる。

位相シフトマスクは、マスクを透過する露光光の部分的位相を反転させ、その干渉を利用し、転写パターンの解像度を向上させたマスクである。露光光は、マスク、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、半導体ウエハ上のフォトレジスト面にマスク透過光の位相差による干渉を利用して集積回路パターンを結像させて露光する。ウエハカバーを除去後、フォトレジストを現像することにより、半導体ウエハ上に回路パターンを形成する。

また、本発明は、集積回路パターンを形成したマスクの回路パターン面へ斜め照明の露光とフォトレジスト面に接触させたウエハカバーとを併用し、縮小投影露光装置により、半導体ウエハ上に回路パターンを転写するものである。マスクの回路パターン面へ斜め照射露光する手段は、マスクの回路パターンの方向性と周期性に対応して最適化した角度だけ傾けてマスクの回路パターン面を照明する。

ウエハカバー媒質中で実質的に露光波長が短波長化し、露光光の斜め照射手法とウエハカバーとの相乗により、マスク自体に位相差を設けなくても、光露光による限界に近い微細な回路パターンの形成を実現する。露光光は、マスク、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、フォトレジストを露光させる。ウエハカバーを除去後、フォトレジストを現像することにより、半導体ウエハ上に回路パターンを形成する。

また、本発明は、半導体ウエハの主面に形成した絶縁膜を化学機械研磨法または化学機械研削法を用いて表面平坦化し、フォトレジスト面に接触させたウエハカバーを用い、集積回路パターンを形成したマスクと縮小投影露光装置により、フォトレジスト露光して、半導体ウエハ上の絶縁膜を堀込み加工するものである。露光光が、マスクを照明し、縮小投影露光装置の投影レンズ、ウエハカバーを透過して、半導体ウエハのフォトレジストを露光する。ウエハカバーを除去後、フォトレジストを現像して、エッチングマスクとし、絶縁膜の堀込みパターンを形成する。絶縁膜段差の影響が少なく、精度良い堀込みパターンが形成できる。

また、本発明は半導体ウエハの主面に形成した導電膜またはその下層膜を化学機械研磨法または化学機械研削法を用いて表面平坦化した後、フォトレジスト面に接触させたウエハカバーを用い、集積回路パターンを形成したマスクと縮小投影露光装置により、フォトレジスト露光して、半導体ウエハ上の導電膜の回路パターン加工するものである。露光光が、マスクを照明し、縮小投影露光装置の投影レンズ、ウエハカバーを透過して、半導体ウエハのフォトレジストを露光する。ウエハカバーを除去後、フォトレジストを現像して、エッチングマスクとし、導電膜の回路パターンを形成する。導電膜段差の影響が少なく、精度良い回路パターンを形成する。

また、本発明は、縮小投影露光装置の投影レンズ開口数が1以上と仮定し、露光光波長が193nm、157nmなどの個々の波長に対応させて最小寸法の回路パターンを設計したマスクとフォトレジスト面に接触させたウエハカバーを用い、マスクに形成された集積回路パターンを縮小投影露光装置により、半導体ウエハ上に回路パターンを転写するものである。

マスク設計に利用した縮小投影露光装置と露光光の波長が同じを装置用い、露光光がマスク、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、半導体ウエハ上のフォトレジストを露光する。ウエハカバーを除去後、フォトレジストを現像することにより、半導体ウエハ上に回路パターンを形成する。

また、本発明は、従来の集積回路の回路パターンデータからコンピュータ処理の方法が事前設定可能なデータ変換処理により得られる回路パターンのマスクとフォトレジスト面に接触させたウエハカバーを用い、集積回路パターンを形成したマスクと縮小投影露光装置により、半導体ウエハ上に回路パターンを形成するものである。

【0014】

従来の集積回路の回路パターンデータは、投影レンズ開口数1以下の縮小投影露光装置により、半導体ウエハ上のフォトレジストに露光してパターン形成できる寸法の回路パターンから構成される集積回路チップの回路パターンデータである。ウエハカバーを用いた回路パターンの形成に適した集積回路パターンのマスクは、従来の回路パターンデータをコンピュータ上に設定したデータ変換処理により、作成する。露光光は、マスク、縮小投影露光装置の投影レンズ、前記ウエハカバーを透過し、前記半導体ウエハ上のフォトレジストを露光させ、前記ウエハカバーを除去後、前記フォトレジストを現像することにより、半導体ウエハ上に回路パターンを形成する。

また、本発明は従来、位相シフトマスクと縮小投影露光装置とにより、微細回路パターンを形成していたものを、遮光マスクとフォトレジスト面に接触させたウエハカバーを用いて露光する方式に切り替えて微細回路パターンを形成するものである。

従来の位相シフトマスクを形成する元になった集積回路チップの回路パターンデータから透過光に位相差を設けないマスクとする処理により得られる回路パターンのマスクを作成する。露光光は遮光マスク、縮小投影露光装置の投影レンズ、ウエハカバーを透過し、半導体ウエハ上のフォトレジストを露光する。ウエハカバーを除去後、フォトレジストを現像し、半導体ウエハ上に回路パターンを形成する。

【発明の効果】

【0015】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

マスクの回路パターン面にマスクカバー、半導体ウエハのフォトレジスト面にウエハカバーを設け、マスクと縮小投影露光装置により、半導体ウエハ上のフォトレジストに露光することにより、縮小投影露光の収差問題を抑制し、半導体ウエハへ転写される回路パターンの精度を向上させる。

また、位相シフトマスク露光や斜め照射露光などの超解像露光手法とフォトレジスト面に接触させたウエハカバーを併用して露光する手法である。前者がマスク面での超解像露光手法による改善と、後者がウエハカバー中の露光光波長が実質的に短くなることによるウエハ面で改善との相乗効果により、露光波長の半分より微細なパターン形成を得る効果がある。

ウエハ上のフォトレジスト面に接触させたウエハカバーと縮小投影レンズとの間に微小ギャップを設けることで、縮小投影レンズとウエハ面との平面上の移動が可能となる。ウエハカバーは、投影レンズの開口数を増加させる。ウエハカバーを用いた縮小投影露光法は、開発に最もコストがかかる投影レンズへの影響が少なく、縮小投影露光装置の開発コストを大幅に抑制させる効果がある。

ウエハカバーを用いる露光とウエハカバーを用いない露光は、投影レンズの共用となり、露光装置のユーザ側の投資を削減させる。半導体集積回路装置の製造コストを削減させる効果がある。

また、半導体ウエハ上の絶縁膜の平坦化プロセスとウエハカバーを用い、マスクの回路パターンを縮小投影露光することにより、同じ露光波長、投影レンズ、フォトレジストを利用しても、光露光波長より微細な絶縁膜の開口パターンを精度よく形成させる効果がある。

また、半導体ウエハ上の導電膜の平坦化プロセスとウエハカバーを用い、マスクの回路パターンを縮小投影露光することにより、同じ露光波長、投影レンズ、フォトレジストを利用しても、光露光波長より微細な導電膜の回路パターンを精度よく形成させる効果がある。

また、従来の縮小投影露光装置の投影レンズでは限界に近い微細な回路パターンを有する集積回路マスクを流用して、さらに縮小された集積回路パターンを半導体ウエハ上に転写するものである。その結果、半導体集積回路装置の開発、製造コストを削減させる効果がある。

また、半導体集積回路装置の新規プロセス開発に用いる集積回路パターンデータに関し、それまでに開発済みの集積回路パターンデータを利用することにより、半導体設計開発工数を削減できる効果がある。回路パターンの微細化に伴って、投影露光歪が増加するが、ウエハカバーを用いた露光法では、これを抑制させることができる。このため、マスクデータ作成処理の簡略化だけでなく、マスクパターンの近接効果補正を少なくさせることが可能であり、マスク描画時間短縮、マスク検査の容易化により、パターン転写精度が向上した集積回路マスクが簡単に作成できる効果がある。その結果、集積回路装置の製造コストを削減する効果がある。

【0016】

従来の液侵露光においては、半導体ウエハのフォトレジストを液侵状態にするため、レジスト材料、現像液などに制約がある。ウエハカバー露光方式では、フォトレジストを液侵状態にしなくても良く、従来のフォトレジストがそのまま利用できるので、半導体集積回路の製造プロセスの開発コストを削減させる効果がある。

また、ウエハカバーが複数の半導体ウエハのフォトレジスト面へ異物による欠陥の転写を防止させる構造としたことにより、半導体集積回路装置の製造歩留りを向上させる効果がある。

また、従来位相シフトマスクを適用した半導体集積回路の製造工程において、これを遮光マスクに置き換え、ウエハカバーを用いた露光方法とすることで、半導体製造コストを削減させる効果がある。

【図面の簡単な説明】

【0017】

【図1】本発明の一実施例である半導体集積回路装置の製造に用いるマスク、縮小投影露光装置、半導体ウエハの全体構成図の一例を示している。

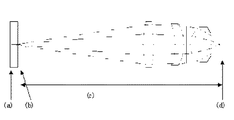

【図2】光学設計した縮小投影レンズとマスクの回路パターン面にマスクカバーを設けた時の配置図とレイトレーシング法による光束のプロット図である。

【図3】光学設計した縮小投影レンズにマスクカバーを設けない時の波面収差である。

【図4】マスクカバーの厚さに対する縮小投影レンズの波面収差を導出した評価データである。

【図5】マスクカバー厚さと、マスク面と結像面位置を光軸方向に位置を最適化した波面収差である。

【図6】図1に装着されるマスク、半導体ウエハおよびウエハカバーのローダ部の説明図である。

【図7】マスク面への斜め照明とウエハカバーを併用した露光方法の説明図である。

【図8】縮小倍率の追加変更とウエハカバーを用いた露光方法の説明図である。

【図9】マスクカバーを用いたマスクの一例の全体平面図と断面図である。

【図10】マスクカバーを用いたマスクの工程フロー説明図である。

【図11】回路の設計工程を説明するための工程フロー図である。

【図12】従来集積回路データのルール変換とウエハカバーを用いた露光方法の説明図である。

【図13】従来集積回路データのルール変換とウエハカバーを用いた露光方法の説明図である。

【図14】半導体装置の製造工程におけるフォトリソグラフィ工程のフローチャートである。

【図15】本実施例の半導体装置のゲートパターン形成フローチャートである。

【図16】本実施例の半導体装置の絶縁膜パターン形成フローチャートである。

【図17】本実施例の半導体装置の導電膜パターン形成フローチャートである。

【図18】本実施例の半導体装置の導電膜パターン形成フローチャートである。

【図19】ウエハカバーを用いた露光とウエハカバーを用いない露光による半導体装置の説明図である。

【符号の説明】

【0018】

図1:

EXP 縮小投影露光装置

E1 光源

E2 ミラー

E3 コンデンサレンズ

E4 マスキングブレード

E5 アライメント機構部

E6 マスク用XYZ駆動ステージ

E7 縮小投影レンズ

E8 ウエハ用XYZ駆動ステージ

E9 倍率校正、フォーカス校正用センサ

M1 マスク

M2 マスクカバー

W1 半導体ウエハ

W2 ウエハカバー

図2:

(a) マスクパターン面

(b) マスクカバー

(c) 投影レンズ

(d) 結像面

図6:

M1 マスク

E7 縮小投影レンズ

W1 半導体ウエハ

W2 ウエハカバー

E11 ウエハローダ

E12 ウエハカバーローダ

E13 マスクローダ

図7:

M1 マスク

E7 縮小投影レンズ

W1 半導体ウエハ

W2 ウエハカバー

W3 フォトレジスト

B1 斜め照明光

B2 0次回折光

B3 1次回折光

図8:

M1 マスク

E7 縮小投影レンズ

E8 ウエハ用XYZ駆動ステージ

W1 半導体ウエハ

W2 ウエハカバー

W4 追加縮小露光による半導体チップ

W5 通常縮小露光による半導体チップ

図9:

M1 マスク

M2 マスクカバー

M3 遮光金属膜

M4 転写倍率計測パターン

M5 レチクルアライメントマーク

M6 チップアライメントマーク

M7 フォーカス合せパターン

M8 転写用回路パターン

M9 製品名、工程名、バーコード他マスクID

図10:

M1 マスク

M2 マスクカバー

M11 レジスト

M12 クロム膜

M13 石英ガラス基板

MP1 レジスト塗布工程

MP2 電子ビーム露光、現像工程

MP3 クロムエッチング、レジスト除去工程

MP4 カバーガラス

MP5 反射防止膜塗布工程

MP6 カバーガラス貼り合せ工程

図19:

M1 マスク

E7 縮小投影レンズ

W1 半導体ウエハ

W2 ウエハカバー

E8 ウエハ用XYZ駆動ステージ

【発明を実施するための最良の形態】

【0019】

本実施の形態を詳細に説明する前に、本実施の形態における用語の意味を説明すると次の通りである。

半導体ウエハとは、半導体装置の製造に用いるシリコンその他の半導体単結晶基板、サファイア基板、ガラス基板その他の絶縁、反絶縁または半導体基板等、並びにそれらの複合的基板であり、絶縁層、エピタキシャル半導体層、その他の半導体層および配線層などを形成して集積回路を形成するものとする。また、基板表面の一部または全部を他の半導体、例えばシリコン−ゲルマニウム(SiGe)等にしても良い。

また、マスクとは、フォトマスクおよびレチクル等のような露光原版を含むものとし、マスク上に光を遮蔽するパターンや光の位相を変化させるパターンを形成したものとする。また、ハーフトーン型位相シフトマスクは、位相シフトマスクの一種で透過率が1%以上、40%未満で、それが無い部分に対し、透過光の位相を反転させるハーフトーンシフタ膜を有するものである。

また、縮小投影露光装置とは、マスクに形成された回路パターンを半導体ウエハなどの試料表面に形成したフォトレジストを露光するための装置である。ここでは、投影レンズとウエハ面とで平面上の相対位置を連続して変える(スキャナー)、または短時間のステップアンドリピートして変える(ステッパ)である。露光装置の光源は、例えばi線(波長365nm)、KrF(波長248nm)、ArF(波長193nm)またはF2ガスレーザ光(波長157nm)等のような露光光を放射することが可能な単色光源である。露光光は、波長により、紫外光、遠紫外光、真空紫外光などと呼ばれているものである。

以下の実施例においては便宜上その必要があり、複数に分割して説明する。特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。以下の実施例において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。

【実施例1】

【0020】

実施例1は、集積回路パターンを形成したマスクと縮小投影レンズを利用して半導体ウエハ上のフォトレジスト面へ回路パターンを露光するためのマスク、縮小投影露光装置、および集積回路パターンの形成手法に関するものである。

第一の発明は、集積回路パターンを形成したマスク、マスクの集積回路パターン面に接触させたマスクカバー、半導体ウエハ上のフォトレジスト面に接触させたウエハカバーを用い、縮小投影露光法により、半導体ウエハ上に回路パターンを露光する手法である。露光光は、マスクを照明し、マスクカバー、縮小投影露光装置の投影レンズ、ウエハカバーを透過して、半導体ウエハ上のフォトレジストを露光させる。露光後、ウエハカバーを除去、フォトレジストを現像し、半導体ウエハ上に微細な回路パターンを形成させる。

図1は、半導体集積回路装置の製造に用いるマスク、縮小投影露光装置、半導体ウエハの全体構成図の一例を示している。マスクには、回路パターン面に接触させたマスクカバーと半導体ウエハには、フォトレジスト面に接触させたウエハカバーを設けている。縮小投影レンズ端とウエハカバーとの間に微小ギャップを設けてある。この縮小投影露光法により、露光光の波長より微細な回路パターンが形成できるようにした。

最初に図1に示したマスクカバーに関して、特許第3120474号との違いを説明し、続けて本発明の特徴を説明する。

特許第3120474号に記載された方式においては、マスクの回路パターン面と縮小投影レンズとの間に厚い高屈折率の透明媒体を設けると転写パターンの歪が増し、転写できる回路パターンの解像度が劣化する問題があった。特に露光光の波長よりも微細な回路パターンの場合、精度不足となり、波面収差の問題があることが判明した。即ち、公知例となる特許第3120474号は、マスクの回路パターン面と縮小投影レンズとの間に厚い高屈折率媒質を設けた場合の波面収差を考慮していなかった。

転写パターン歪の問題解決のため、本発明者は、位相シフト手段となるガラス基板と遮光パターンを形成したマスク基板とを重ねて設けた場合の波面収差の解析を行った。本発明者は、マスクの回路パターン面と縮小投影レンズとの間に屈折率が1より大きい媒質のマスクカバーを設けた場合の波面収差は、マスクの回路パターン面、縮小投影レンズ、結像面の光軸方向位置を微調整すると大幅に減少することを発見した。

また、本発明者は、マスクカバーの材質として合成石英ガラスを用いた時、マスクカバーを今回の縮小投影レンズでは0.3mm程度とすれば、従来予測と違ってマスクカバーを設けない場合よりも波面収差が減少することを見出した。

さらに、本発明者は、露光波長、開口数、収差が同じ縮小投影レンズを用いた場合であっても、ウエハのフォトレジスト面にウエハカバーを用いる露光法により、転写された回路パターンの解像度が向上することを見出した。

以下、本発明の根拠に関して、図2から図5を用いて説明する。

図2は、光学設計した縮小投影レンズとマスクの回路パターン面に屈折率が1より大きい媒質のマスクカバーを設けた時の配置図とレイトレーシング法による光束のプロット図である。光学設計した縮小投影レンズは、波長λが248nmのKrF(クリプトンフロライド)エキシマレーザを用い、開口数0.75である。マスクカバーは、材質として、合成石英ガラスを用い、マスクの回路パターン面に接触配置して、その厚さを変えられるようにした。

図3は、光学設計した縮小投影レンズにマスクカバーの厚さが0mm、即ち、マスクカバーを設けなかった時の波面収差である。この波面収差は、縮小投影レンズの射出瞳面に形成した理想的な参照波面との光路長差であり、結像面からレンズをみた画角全体に対する光路長差を示している。取り扱いを簡単にするため、波面収差として、rms値を用いる。設計した投影レンズは、図3に示したように、rms値が0.0017λまで小さく追い込むことに成功した投影レンズである。これにより、投影レンズの意味ある評価できるようにした。

上記の縮小投影レンズを用い、マスクのパターン面に2.3mm(0.09インチ)厚の合成石英基板からなるマスクカバーを設けた時、マスクカバーを含む縮小投影レンズの波面収差は、rms値が0.3314λとなった。この値は、マスクカバーを設けなかった場合を基準とすると約200倍に激増した。

本発明者は、縮小投影レンズとマスクカバーがこのような大きい波面収差の状態となると、投影像パターンがボケ状態となり、パターン形成できないことを確認した。

同じ材質、厚さのマスクカバーと縮小投影レンズを用い、マスク面と結像面位置を光軸方向に位置を補正し最適化すると、マスクカバーを含む縮小投影レンズの波面収差は、rms値が0.0089λまで減少した。本発明者は、同一縮小投影レンズを用いても、マスク面と結像面位置を光軸方向に位置を補正し、最適化すれば激減することを見出した。

図4は、マスクカバーの厚さに対して、設計した縮小投影レンズの波面収差の変化を調べたものである。マスクカバーの材質は、屈折率1.47の合成石英ガラスである。波面収差は、マスクカバーを設ければその厚さに依存して激増する。図4に示したように、マスク面と結像面位置を光軸方向に補正し、最適化した場合、その波面収差は、マスクカバーの厚さに依存して変化した。

縮小投影レンズとマスク位置、ウエハ位置を光軸方向に調整し、最適化した場合の波面収差は、縮小投影レンズをブラックボックスとして扱う従来方式では予測できない結果である。上記した点について記載した論文、特許は本発明者の知る限りない。

本発明者は、マスクカバーの厚さが、0.1mmから0.6mmとし、マスク面と結像面位置を光軸方向に位置を補正して最適化すれば、マスクカバーを設けなかった時より小さくなることを見出した。マスクカバーの厚さが0.3mmの時、縮小投影レンズの波面収差は、図5に示すように、rms値が0.0008λである。

【0021】

縮小投影光学システムでは、マスク上の一点から出た光がウエハ上のフォトレジスト面の一点に結像する。結像投影光学系においては、マスク面である物面とウエハ面である結像面とは、投影レンズを挟んで一対一に対応する。仮に、ウエハ面から光を照射するならば、光束は最短距離となる光路パスを逆に進み、マスク面の対応箇所に結像する。

上記の検討から、本発明者は、マスクの回路パターン面でなく、ウエハ上のフォトレジスト面へウエハカバーを付加することで、縮小投影レンズを利用してフォトレジスト面へ露光するとパターン転写の解像度が向上することを見出した。

【0022】

本発明の最も効果のある形態は、上記の発見を元に、集積回路を形成したマスクから、フォトレジストまでの露光光の経路に、縮小投影露光レンズの他にマスクカバー、ウエハカバーを設け、マスク、縮小投影露光レンズと半導体ウエハの光軸方向位置を最適化調整して、微細な回路パターンの精度よい転写を実現するものである。

上記手法は、縮小投影レンズ端とウエハ面との間全体を液体で満たした液侵露光装置と異なる。縮小投影レンズ端とウエハ面との間全体を屈折率が1より大の媒質で満たす必要がないことに特徴がある。縮小投影露光装置としては、投影レンズとウエハ面と平面上でその相対位置を変えられることが不可欠であり、縮小投影レンズ端とウエハカバーとの間に狭小ギャップを設けた。

【0023】

発明の実施形態としては、フォトレジスト面上に所定の厚さのウエハカバーを設けることで、転写パターンの解像度を向上させることができる。以下に、図1に示した実施例1の縮小投影露光装置とウエハカバーについて詳細に説明する。

縮小投影露光装置は、縮小比5:1のステッパを改造したものである。マスクM1は、実際の集積回路パターンの約5倍に拡大された回路パターン原画が形成されたレチクルである。本明細書では、このレチクルをマスクと記す。

縮小投影露光装置の光源E1は、例えばi線(波長365nm)、KrF(波長248nm)、ArF(波長193nm)またはF2ガスレーザ光(波長157nm)等のような露光光を放射することが可能な単色光源である。光源E1から放射された露光光は、ミラーE2およびコンデンサレンズE3を介してマスクM1に照射され、さらにマスクカバーM2を透過して縮小レンズE7とウエハカバーW2を通じて半導体ウエハW1の主面(デバイス形成面)のフォトレジストに照射されるようになっている。マスクM1は、その第1主面を半導体ウエハW1側に向けた状態で置かれ、前記第1主面に接触し、露光光に対して透明なマスクカバーM2が設けられている。

半導体ウエハW1は、XYZステージE8上に載置されている。この半導体ウエハW1の主面には、露光光に対して感光性を有するフォトレジストが形成されている。このフォトレジスト面に接触させたウエハカバーW2が設けられている。ウエハカバーは、屈折率が高い材質が望ましい。ウエハカバーW2は、露光光に対して実質的に透明なマスクの基板材料である合成石英ガラス(1mm厚、屈折率が1.47)を用いた。投影レンズの結像面側のレンズ端面とウエハカバーとのギャップは、100ミクロンとした。ウエハカバーは、投影レンズの結像面側のレンズ端面からフォトレジスト面まで、90%以上となる光路長の厚さとなった。投影レンズの結像面側のレンズ端面からフォトレジスト面までの光路長に対し、ウエハカバーの厚さを増す程、転写パターンの解像度向上の大きい効果を得ることができる。投影レンズの結像面側のレンズ端面とウエハカバーとのギャップは、窒素ガスなどを充填し、ガス圧を検出するようにした。これにより、ギャップの幅の変動を抑制するようにした。

【0024】

図6は、図1に装着されるマスク、半導体ウエハおよびウエハカバーのローダ部を示したものである。マスクカバーは後述するようにマスクと一体化してあり、マスクローダは1箇所である。半導体ウエハは、1枚だけでなく多数枚露光処理する必要がある。

一部の半導体ウエハ上のフォトレジストに付着した異物が他の半導体ウエハの露光に影響しないように、半導体ウエハとウエハカバーはそれぞれ独立したローダ部を設けた。1枚のウエハカバーに複数枚数のウエハ接触させるようにすると、フォトレジスト、微小異物がウエハカバーに付着し、他のウエハへ転写欠陥の要因となる。

そこで、ウエハカバーは、1枚の半導体ウエハのフォトレジストに接触させ、露光処理すれば、直に洗浄クリーニングできるように、ウエハの露光処理と独立して露光装置へロードとアンロードできるようにした。

半導体ウエハとウエハカバーは、別々のローダから搬送アームにて、露光ステージに一体化して移載される。ウエハカバーは、半導体ウエハより外形寸法を大きくした。ウエハカバーは、露光前にウエハのフォトレジスト面に接触させ、共に露光ステージ上で、投影レンズと反対側から真空チャックにより保持するようにした。

【0025】

ウエハカバーは、真空チャックを用いないで、半導体ウエハのフォトレジスト面に少量の純水を滴下し、ウエハカバーを密着し、ウエハと一体として扱うようにしてもよい。

半導体ウエハ上のフォトレジストに付着した異物が他の半導体ウエハの露光に影響しないようにすることは、液侵露光方式を採用する場合にも不可欠なアイデアである。本発明の露光装置は、ウエハカバーとして、純水を用いる液侵露光装置としても露光できるようにした。液侵露光装置としては、透明液体を投影レンズに直接接触状態として使用すると、投影レンズ表面に異物が付着することが分った。さらに、投影レンズ表面に付着した異物をクリーニング除去する手段を導入すると、液侵露光の際に透明液体中の泡の発生要因となることが分った。

この対応手段として、透明液体をウエハカバーとする場合、投影レンズの結像面側にレンズカバーを設けた。このレンズカバーは、投影レンズと同じ材質の合成石英を用い、簡単に取り換え交換できるようにした。

【0026】

マスクの回路パターンの方向性と周期性に対応して、露光光を分割し、斜め照明すると共に半導体ウエハのフォトレジスト面へウエハカバーを設け、縮小投影露光できるようにした。図7に示すように、分割した一方の露光光は、マスクの回路パターン面を斜め照明し、縮小投影レンズ、ウエハカバーを透過して、前記ウエハ上のフォトレジスト面に結像し、露光する。

露光光を斜めに照明する方式は、マスクのパターンの方向性と周期性に対応して、斜め照明の角度を変える。斜め照明の角度は、光学系光軸から偏芯した位置に2個または4個の開口部を持つ特殊な絞りを照明光学系中に挿入し、光軸中心からの開口部の位置を変えて実現した。斜め照明光することで、マスクの回路パターンで生じた0次回折光、+1次回折光、1次回折光の方向も変化する。

図7に示すように、分割した一方の露光光は、露光光は、マスク面を斜め照射し、0次回折光と+1次回折光により結像を得るようにしている。この斜め照射方式は、マスクの回路パターンがx方向またはy方向に均一に並んでいるときに、有効である。

マスクの回路パターン面への露光光の照明角度の変更手段とウエハカバー手段とを併用することにより、ウエハカバー媒質中で露光光の波長が短くなり、露光光の波長より微細な回路パターンの精度良い形成を可能とした。

【0027】

マスク面を照明する露光光の光軸の中央部を円形状に遮蔽し、リング状の露光光を利用できるようにした。これにより、上記の斜め照明において、45度方向の回路パターンの解像度が劣化する問題を改善させた。

縮小投影露光装置の露光光がマスクの回路パターンに対応してマスク面を斜め照明し、ウエハカバーを透過して、前記ウエハ上のフォトレジスト面に結像することで、転写パターンの解像度向上を可能とした。

【0028】

実施例1の縮小投影露光装置では、ウエハカバー厚に関して、ウエハカバー毎の変動、ウエハカバー上の位置による変動を計測する手段を設けた。ウエハカバー厚の計測用レーザを用い、フォトレジスト面とウエハカバー表面にレーザ光を斜め照射して、その反射光の位置を検出するようにした。

フォトレジスト面の代わりにフォトレジスト面に対応した前記縮小投影露光装置の所定の部位、また、ウエハカバー表面の代わりにウエハカバー表面に対応した縮小投影露光装置の所定の部位にレーザ光を斜め照射して、その反射光の位置を検出することで代用できる。

図8に示すように、マスクに形成された集積回路パターンを半導体ウエハ上のフォトレジスト面に転写する際、予め設定された縮小倍率での露光に追加して縮小倍率を0.5倍程度まで乗じた露光ができるようにした。縮小倍率の変更は、マスク、半導体ウエハを光軸方向移動させて実現した。縮小投影露光装置の投影レンズの一部を構成する補正レンズを光軸方向移動させても良い。前記の縮小倍率追加とウエハカバー露光により、従来露光装置用に準備したマスクをそのまま流用して、集積回路チップ全体が縮小した回路パターンを転写するための露光ができるようにした。

本発明の縮小投影露光装置は、半導体ウエハのフォトレジスト面にウエハカバーを設けた場合と設けない従来のウエハに対しても縮小投影露光できるようにした。即ち、マスクの回路パターン面と縮小投影レンズとウエハ面との光軸方向の位置を調整し、最適化して、ウエハ面にウエハカバーを設けた露光と設けない露光とができるようにした。ウエハ面にウエハカバーを設けた露光と設けない露光を実現する機能は、縮小投影レンズを構成するレンズの一部を光軸方向に位置を調整移動させてもよい。また、縮小投影レンズ系に別レンズ追加するようにしてもよい。

【0029】

同一の半導体装置または同一系列の半導体装置の露光工程において、ラフパターンを転写するための露光工程と、ファインパターンを転写するための露光工程とで露光方法を使い分ける。ファインパターンは、高い寸法精度が要求されるパターンであり、露光光の波長よりも小さなパターンを半導体ウエハ上に転写する場合のパターンである。例えばMOSデバイスのゲート電極パターンや半導体装置の配線パターンがこれに該当し、ウエハカバーを用いた縮小投影露光方法が適用できる。

また、ラフパターンは、ファインパターンに比べて高い寸法精度が要求されないパターンであり、露光光の波長よりも大きなパターンを半導体ウエハに転写する場合のパターンである。例えばMOSデバイスのソースおよびドレイン用の半導体領域のパターンや活性領域(分離領域)のパターン等がこれに該当する。これらは、ウエハカバーを用いない従来の露光方法を適用することができる。

次に、実施例1のマスクについて詳細に説明する。図9は、実施例1のマスクの平面図と断面図である。図9に示すように、回路パターン面にマスクカバーのガラスM2が重ねて一体化してある。図9において、マスクM1を構成するマスクの基板は、例えば露光光に対して透明な平面四角形状の合成石英ガラス板からなり、第1主面とその反対面(裏面)側の第2主面とを有している。マスクの基板1の第1主面には、外周に縁取られた遮光帯M3を持つ転写領域M8がある。露光光を遮光する膜は、例えばクロム(Cr)等のような金属膜からなる。

露光においては、マスクM1と縮小投影レンズE7とウエハW1との間にマスクカバーとウエハカバーW2が光路上に存在し、それらの厚さの変動がマスクパターンの転写に影響する。このため、図9に示すマスク上の転写領域の周囲領域に、転写倍率計測パターンM4a、M4bとフォーカス合わせ用パターンM7を設けた。フォーカス合わせ用パターンM7はラインアンドスペースパターンを用い、光検出器(E9)により、検出器上に結像されるパターンのコントラストが最良となるようにした。前記光検出器(E9)は、前記ウエハ面またはウエハ面上と同一光軸面位置に設けている。

ウエハ上への露光前に、露光装置のステージE8に設置されている光検出器(E9)により、マスクに形成した転写倍率計測パターンM4a、M4b、フォーカス合わせ用パターンM7の透過光がウエハのウエハカバーを透過した状態で検出する。マスクM1面の倍率決めの基準となるマークパターンM4a、M4bの位置座標は、光検出器(E9)により、マスク上での位置座標が既知の転写倍率計測パターンM4a、M4bに対応した光信号を検出し、レーザ干渉により高精度計測しているウエハステージ位置座標系を基準として計測した。前記のマークパターンM4a、M4bの位置座標を計測した時、マークパターン位置がステージ上の所定の位置になるようにマスク倍率を合わせ、マスク面、結像面を光軸方向に微移動して校正する。前記マスクとウエハを光軸方向に微移動させる機構を設けて転写倍率校正できるようにした。この校正は、マスク面、結像面を光軸方向に微移動する代わりに縮小投影レンズの一部を移動させても良い。

マスク、ウエハを光軸方向に微移動する機構、または前記縮小投影露光装置の投影レンズの一部を構成する補正レンズを光軸方向に微移動させる機構を設け、ウエハカバーを露光光が透過する際のウエハカバー厚さ変動による転写倍率補正と結像面位置補正を行うようにした。

露光光は、マスクカバー、ウエハカバーを透過して、前記ウエハ上のフォトレジスト面に結像するように露光できるようにした。露光後、ウエハカバーW2を取り除き、フォトレジストを現像して、マスクM1のパターンを半導体ウエハW1上に転写した。

【0030】

縮小投影露光装置のコンデンサレンズE3とマスクM1との間の露光光の光路には、マスキングブレードE4が介在されている。マスキングブレードE4は、マスクM1の露光領域を選択するための機構部である。

【0031】

縮小投影露光装置の光源E1、マスクM1、半導体ウエハW1との間の露光路には、アライメント機構部E5が介在されている。アライメント機構部E5では、マスクM1と縮小投影露光装置および半導体ウエハW1とのアライメント情報を光学的に読み取ることで検出する。

これらのパターンは、上記したマスキングブレードE4により、露光光を遮断し、ウエハ上に転写されない。

次に、マスクM1のチップアライメントマークM6とウエハ上に形成された位置合わせマークを検出し、重ね合せることによって、マスク上の回路パターンのウエハ上への重ね合せ精度を確保した。

図9のM5は、マスクM1と縮小投影露光装置または半導体ウエハとの位置合わせに用いるアライメントマークパターンである。マスクM1の第1主面の遮光帯領域M3に遮光帯の金属膜の一部を除去することで形成されている。

図9のM8は、転写領域M8と半導体ウエハW1に形成されている下地のパターンとの位置合わせに用いるアライメントマークパターンである。また、転写領域M8内には、半導体ウエハ上に形成して、次の工程で形成する回路パターンと重ね合わせするためのアライメントマークパターンを必要に応じて形成する。この理由は、半導体集積回路は、下層のマスクパターンに順に上層のマスクパターンをウエハ上で重ね合わせるのでなく、ある特定のパターン層に形成したマークに複数層のマスクパターンを重ね合わせているためである。

また、マスクM1の第1主面上において、上記遮光帯の外側の周辺領域には、転写領域対応したパターン情報領域M9が配置されている。このパターン情報領域M9には、例えば半導体装置の製品名、転写領域の露光工程名(適用工程名)、枝番号のようなパターン情報が記載されている。このパターン情報は、例えばクロム(Cr)等のような遮光性を持つ金属膜パターンで形成されており、その記載形式は、例えば英字、数字または記号等のように人が認識できる形式でも良いし、二値表記やバーコード等のように機械的に自動認識できる形式にしても良い。

【0032】

次に、本実施例1のマスクM1の製造方法について説明する。図10は、本実施例1のマスクM1の製造工程中におけるマスク1の要部断面を示した説明図である。

図10のMP1は、マスクM1の第1主面全面上に、例えばCr等のような遮光膜をスパッタリング法等によって堆積した後に、その上に電子ビーム描画用のフォトレジストを塗布する工程である。

MP2は、マスクM1のフォトレジスト面に電子ビームを選択的に照射して集積回路転写用のパターンを描画し、現像処理を施してフォトレジストパターンを形成する工程である。

続いて、MP3は、フォトレジストパターンをエッチングマスクとしてマスクM1に対してエッチング処理を施し遮光膜をパターニングすることにより、マスクM1の第1主面上に遮光帯および回路パターン、アライメントマーク等を形成する工程である。このようにしてマスクM1を製造した後、マスク上の回路パターンの外観を検査する。マスク上に同一パターンがあれば、それらを比較し、無ければ、パターン形成の基の設計パターンデータと比較することで回路パターンの外観を検査する。

MP4は、マスクカバーを準備する工程である。特に図示しないが、マスクカバーに位相シフタパターンを設けておいても良い。

MP5は、マスクカバーの洗浄クリーニング、反射防止膜を設ける工程である。

MP6は、外観検査により、欠陥がなければ、反射防止膜を付けたマスクカバーを重ね、マスクカバー周辺部とマスクM1とを接着剤により固定する工程である。

マスクカバーは、従来ペリクルと呼ばれていた異物遮蔽膜の代用となる。マスクの回路パターンを覆うマスクカバーに付着した異物はクリーンエアーをブローして取り除くことができる。マスクカバー面とマスクパターン面までの距離の差により、小さな異物まで転写の影響があるが、ペリクルに比べ物理的強度あり、ブローして取り除くことが容易である。

【0033】

前記のマスクの遮光膜としてクロム膜を用いたものであるが、これを、前記の位相を反転させるハーフトーン膜に置き換え、ハーフトーン膜部と膜開口部とで透過光の位相が反転させた位相シフトマスクに適用できる。ハーフトーン型の位相シフトマスクでは、ハーフトーン膜上に転写領域M8の周辺遮光部になど遮光膜を形成する必要がある。マスクカバーを用いた場合、遮光金属膜だけでなく、露光光に対して遮光性がある有機膜を用いることができる。

【0034】

また、前記ハーフトーン型の位相シフトマスクだけでなく、隣接パターン間で透過光の位相を反転させた位相シフトマスク(オルタネイト型と呼ぶ)を用いても良い。その他、透過光の位相を反転による干渉の影を利用する広い意味での位相シフトマスクを用いも良い。位相シフトマスクにより、マスクの透過光に位相差を設け、ウエハカバーの効果により、露光光の波長より微細な回路パターンを精度良く半導体ウエハ上に形成することができる。

【0035】

また、前記マスクの転写領域M8には、投影露光時の転写歪みを補正するためのOPC(光近接効果補正:Optical Proximity Correction)パターンを配置してもよい。ウエハカバーを用いた投影露光方式は、マスクパターンの転写歪みが従来方式に比べて小さい。比較的簡単なOPC処理で済ますことができ、補正に要するマスクの描画データ処理時間短縮、電子ビームなどを用いたマスクパターンの描画時間短縮、マスクパターンの検査容易化などにより、OPCパターンを有する先端製品のマスクの製作コストが低減できる効果がある。

【実施例2】

【0036】

本実施例2は、半導体集積回路装置を製造するために、実施例1に示した露光に好都合なマスクとマスクの設計データの作成手法に適用したものである。

【0037】

マスクを最も効率よく新規の半導体プロセス技術開発に利用する方式は、従来の縮小投影露光法を採用すればパターン形成が限界に近い、微細な回路パターンが形成されたマスクを流用することである。図8に示したように、従来の縮小投影露光装置とそのマスクとの組み合せにより設定されるパターン転写の縮小率をウエハカバー露光に対応した露光装置側でさらに高くすることが効率的である。

従来の縮小投影露光装置に使われている投影レンズを用い、単に縮小率を高くしても解像度は向上しない。本提案方式は、投影レンズの開口数を大きくでき、効果は大きい。この方式の最大のメリットは、新規集積回路装置の開発に際して、半導体製造プロセス技術開発のためのマスク費用が節約できることである。

ここで、従来の縮小投影露光装置として想定されるものは、露光光波長が193nmまたは248nm、投影レンズ開口数が1以下である。

本発明のウエハカバー対応の縮小投影露光装置では、当初設定の縮小率の他に、追加して縮小率を可変とした機能を設けてある。露光装置で縮小率を可変とするため、図8に示すように、マスク、または半導体ウエハを光軸方向に可動手段を設けた。露光装置の投影レンズの一部を構成する補正レンズを光軸方向に可動するようにしても良い。これにより、マスクに形成された集積回路パターンを半導体ウエハ上のフォトレジスト面に転写する際、予め設定されている縮小倍率の他に、さらに0.5倍程度まで縮小倍率が変更できるようにした。

縮小投影レンズ自体の収差は、できるだけ小さくなるように、投影レンズ設計しておくことが必要である。液侵露光装置においても、上記の従来マスクを流用させるには、予め設定されている縮小倍率の他に、0.5倍程度まで縮小倍率が可変できるように改造することで、対応可能である。

露光装置側で追加縮小する機能は、半導体製品開発に必要なマスクの精度を緩くすることができ、新規にマスク製作する場合にも有効である。半導体装置の開発初期では、マスク製作技術が間に合わないので、既存のマスク技術でマスク製作し、マスク技術開発した後で、目標の精度で生産用マスク製作することができる。

以下、本実施例2における集積回路の設計工程からマスク製作のためのマスク設計工程までの流れを図11により説明する。

【0038】

集積回路のマスクデータは、図11のマスク設計データの作成フローに一例を示すように、複数の段階を経て処理される。最終的に製造される製品の仕様により、システム設計、論理設計、回路設計およびレイアウト設計が行われる。

【0039】

機能システム設計は、設計、製造および検査に必要な基本仕様を決める工程である。ここでは、機能システム仕様を基に、半導体装置の機能仕様が作成され、動作が詳細に設計される。機能記述言語や状態遷移図にて、例えば論理ブロックの機能レジスタ数、ビット数などのアーキテクチャを含む半導体装置の動作が定められる。

【0040】

続く、論理設計は、論理シミュレーションを行い、論理ゲート等で表現する工程である。ここでは、システム設計データを基に、論理ゲート単位に具体化される。シミュレーションチェックにより論理誤りが訂正される。

【0041】

続く、回路設計は、回路シミュレーションを行うことにより、回路構成素子で表現する工程である。ここでは、半導体装置の製造条件を基に、トランジスタなどのような素子の電気的特性などが設計される。これを基に、基本回路、回路セル、全体回路が設計される。

【0042】

続く、レイアウト設計は、配線チェック、レイアウトルールチェックを行うことにより、回路パターンとして配置する工程である。ここでは、論理ゲートの配置、配線が行なわれ、設計マスクパターンデータが作成される。

【0043】

このような工程を経て設計(SF)データが作成され、出力される(工程105)。作成されたマスク設計データは、たとえばCAD(Computer Aided Design)などのような計算機処理システムを用いて、配線のチェックおよびレイアウトのチェックなど、設計仕様チェックを行う。その後、作成されたマスク設計パターンデータは、カルマストリームフォーマット形式(SF(Stream Format)データ)などのような集積回路パターンの標準データ形式で出力される。

【0044】

SFデータとして出力されたマスク設計データは、図形データの重なり除去、基本図形除去、フィールド分割およびマスクパターン寸法補正などの各処理が施される。これらの処理の際に、マスク描画データへ変換するための設定条件は、マスク上へのパターン描画装置によって異なる。

【0045】

現状、マスク描画データは、各マスク装置メーカのマスク描画装置の専用フォーマットとなっており、適用するマスク描画装置に合せて変換される。例えば、マスク描画装置として、米国ETEC社のMEBESがあり、この装置はラスター方式と呼ばれる描画方式で、マスクへの回路パターンの描画は、マスク設計データのアドレス寸法に近い寸法の電子ビーム照射のオンオフを繰り返すこと(微小スポットの電子ビームのオンオフ照射)により行われる。また、例えば(株)日立製作所のHL800では、ベクター方式と呼ばれる描画方式で、マスクへの回路パターンの描画は、マスクパターン設計アドレス単位に対応した可変寸法の電子ビームの照射により行われる。

【0046】

マスク描画データは、マスク設計パターンデータに対して、マスク描画方式、描画装置によるデータフォーマットを合せて、マスク描画のための基本図形分解、フィールド分割などの描画データ変換、マスクパターン形成時の歪み補正変換および投影露光時の歪み補正するための光近接効果補正変換などの変換がなされる。

【0047】

このようにして作成されたマスク描画データに基づいて、マスクへ回路パターンを描画することが可能となる。変換された複数のマスク描画データをマスク上に配置することにより、マスク上に回路パターン、集積回路テスト用パターン、マスクテストパターンおよび露光アライメントマークパターンなどを形成したマスクが製作される。

【0048】

マスクを新規に製作する場合、実施例1で示した露光装置で最も効果的なマスクの回路パターンとしては、露光光波長が193nm、157nmなど、投影レンズ開口数が1以上の第一縮小投影露光装置により、半導体ウエハ上のフォトレジストに露光してパターン形成できる寸法の回路パターンを要部とする集積回路パターンである。この集積回路パターンを形成したマスクを用い、実施例1で開示した露光装置にて、微細な回路パターンの転写が実現できる。

【0049】

上記のマスクは、露光光の波長より微細な回路パターンを含み、従来マスクに比べて投影露光の際に生じる転写パターンの歪を補正するためのマスク上の回路パターンに追加された近接効果補正(OPC)パターンが少なくできる。

上記したようにマスク設計パターンデータまで、新製品の開発には、回路の高集積化と共に膨大な回路設計の工数が掛かる。そこで、実施例1で示したウエハカバー露光方式で用いるマスクは、高集積化に対して効率良いことが必要である。

【0050】

マスクを新規に製作する場合においても、従来の集積回路チップの回路パターンデータを利用し、計算機による演算処理によって作成した集積回路パターンデータを利用する方法が有効である。図11に示した目的とするマスクの集積回路パターンデータを全て始めから作成するのでなく、それまでの回路設計資産である集積回路チップの回路パターンデータを利用する。目的とするマスクは、マスク上で縮小されたそれまでの複数の回路パターンデータと新規の回路パターンデータとを統合して作成する。ウエハカバー露光用のマスクは、例えばマスク製造メーカに製作依頼することで入手できる。

マスクの新規製作が簡単に済ますには、従来の縮小投影露光装置によって形成できた集積回路チップの回路パターンデータからルールに従ったデータ変換処理により目的とする集積回路チップの回路パターンを作成することである。ルールに従ったデータ変換処理であれば、設計工数が削減できる。データ変換処理による回路パターンを主要部とする集積回路チップの回路パターンからは、マスクの精度品質レベルに依存した所定の工数でマスクが作成できる。

ここで、従来の縮小投影露光装置として想定されるものは、投影レンズの開口数1以下である。この従来の縮小投影露光装置により、半導体ウエハ上のフォトレジストに露光してパターン形成できる寸法の回路パターンから構成される集積回路チップの回路パターンデータを利用する。本件発明の手法である屈折率が1以上の媒質をフォトレジスト面上に設けることでパターン形成できる寸法の回路パターンを実質的に含まない既設計の集積回路チップの回路パターンデータを利用する。

図12に示したように、ルールに従ったデータ変換処理としては、集積回路チップパターンデータに対して、データ領域を指定しての縮小処理、縮小したパターン幅の補正処理などである。マスク作成時のパターン寸法シフトの補正だけでなく、縮小投影露光法により、ウエハ上で露光量が不足する箇所のパターン幅を太らせる処理や、逆に露光量が過剰となる箇所のパターン幅を細らせる処理を含むものである。コンピュータによる回路パターンのデータ処理の手順が、コンピュータ上でルール化できれば良い。自動処理が可能となれば、集積回路パターン作成の工数が大幅に削減できる。

ルールに従ったデータ変換処理の特例として、形状を実質的に相似形に0.5倍程度まで縮小処理した回路パターンを主要部とする集積回路チップの回路パターンを用いることが有効である。この集積回路チップの回路パターンをマスクに形成することで、それに対応した微細なパターンをウエハ上に転写する。

縮小投影露光法により半導体ウエハ上に形成できる回路パターンは、露光光の波長、投影レンズの収差、レンズ開口数などを元に計算によってフォトレジスト面での光強度分布を求めることができる。確立された手法としては、マスクの回路パターンをフーリエ変換する手法があり、半導体ウエハ面に形成されるパターン形成できる寸法の回路パターンが求められる。この手法から、所望の回路パターンを形成したマスクが準備できる。

半導体集積回路マスク製作上、透過光に位相差を設ける位相シフトマスクは、従来の遮光マスクに比べてコストがかかる。製作に要する日時も3倍以上かかる。そこで、図13に示したように、従来位相シフトマスクを使って形成した回路パターンの一部は、これを使わないで、遮光マスクとウエハカバー露光を適用することができる。従来の縮小投影露光と位相シフトマスクとの組合で形成できる多くの回路パターンに適用できる。

想定される第一縮小投影露光装置の投影レンズ開口数が1以下で、透過光に位相差を設けるマスクにより、半導体ウエハ上のフォトレジストに露光してパターン形成できる寸法の回路パターンから構成される集積回路チップの回路パターンデータを準備する。

集積回路チップの回路パターンデータは、通常20層以上が用いられており、回路パターン寸法が微細で高精度が必要な工程の回路パターンに位相差マスクが用いられている。この位相差マスクを用いた回路パターンデータは、位相シフトパターンのデータと遮光パターンのデータである。透過光に位相差を設けないマスクの遮光パターンのデータを取り出す。位相シフトマスクのパターンデータと遮光マスクのパターンデータとは違うのでコンピュータによる演算処理が必要となる。コンピュータ処理した回路パターンデータを用いてマスクに回路パターンを形成する。

【0051】

以上のようにして準備したマスクを用いて、実施例1にて説明した縮小投影露光にて回路パターンを半導体ウエハ上に形成する。

【0052】

露光光を透過するウエハカバーを前記半導体ウエハ上のフォトレジスト面に接触させて設ける。露光光がマスク、縮小投影露光装置の投影レンズ、前記ウエハカバーを透過し、前記半導体ウエハ上のフォトレジストを露光させる。

【0053】

前記ウエハカバーを除去した後に、前記フォトレジストを現像することにより、半導体ウエハ上にフォトレジストの回路パターンを形成する。この方式により、上記マスクの回路パターンを精度良く半導体ウエハ上に転写することが可能となる。

【0054】

実施例2において説明した集積回路データの処理方式に関しては、液侵露光方式にも適用可能である。従来の集積回路マスクを更に縮小露光させる場合は、液侵露光方式においても縮小率を変更できるようにするための装置改造が必要である。

【実施例3】

【0055】

実施例3は、前記実施例1において説明したマスク縮小投影露光、前記実施例2において説明したマスク、マスクデータ作成法を用い、例えば相補MOS(CMOS:Complementary Metal Oxide Semiconductor)型のMOSFETの製造に適用した場合について説明する。

実施例1の露光方式を半導体装置の製造工程に適用することで、マスク上の微細な回路パターンを精度良く半導体ウエハ上に転写できる効果がある。半導体ウエハ上のフォトレジスト膜の表面に均一して接触状態とするには、半導体ウエハ表面を平坦化してフォトレジスト膜を形成する。ウエハカバーを用いる方式においては、半導体ウエハ表面を平坦化してフォトレジスト膜を形成することで、マスク上の微細な回路パターンを精度良く半導体ウエハ上に転写することが可能となる。

図14は、実施例3の半導体装置の製造工程におけるフォトリソグラフィ工程のフローチャートを示している。

【0056】

nウエル・フォト工程P1は、半導体ウエハW1上に窒化シリコン等の絶縁膜を堆積した後、その絶縁膜上にnウエル形成領域以外の領域が被覆されるようなフォトレジストパターンを形成する工程である。n-形の半導体ウエハW1のnウエルには、たとえばn形不純物のリン(P)またはヒ素(As)が導入される。

【0057】

フィールド・フォト工程P2は、半導体ウエハW1の主面上に窒化シリコン等の絶縁膜を堆積した後、その絶縁膜上に素子形成領域のみが被覆されるようなフォトレジストパターンを形成する工程である。半導体ウエハW1の主面に、酸化シリコン(SiO2)からなるフィールド絶縁膜をLOCOS(Local Oxidization of Silicon)法によって形成した後、そのフィールド絶縁膜に囲まれた素子形成領域に、酸化シリコン膜(SiO2)などからなるゲート絶縁膜11を熱酸化法によって形成する。このパターンは、ラフパターンである。

【0058】

pウエル・フォト工程P3は、pウエルのチャネルストッパ領域を形成するために、nウエル上を被覆するフォトレジストパターンを形成する工程である。pウエルには、例えばp形不純物のホウ素が導入される。

【0059】

ゲート・フォト工程P4は、半導体ウエハW1の主面上に導体膜のゲート電極形成領域を形成する工程である。低抵抗ポリシリコン等からなるゲート電極形成膜をCVD法等によって堆積した後、ゲート電極形成領域が被覆されるようなフォトレジストパターンを形成し、エッチング技術によりパターニングして、ゲート電極を形成する。

従来技術では、ゲートパターンの微細化、高精度化に応えるため、前記のハーフトーン型位相シフトマスクを用い、ネガ型フォトレジストへ露光する方式や、開口領域の透過光の位相を交互に反転させたオルタネイト型位相シフトマスクと位相反転境界部を遮蔽するトリム遮光マスクを用い、ポジ型フォトレジスト上へ重ね露光する方式が用いられている。

上記のゲート・フォト工程P4に対しては、フォトレジスト面に接触したウエハカバーを適用することで選択できる技術を多くすることができる。先端製品で、ゲートパターンの微細化と精度が必要な場合には、図15に示したように、ゲート用導電膜を形成する下地層を平坦化しておき、その後、絶縁膜と導電膜を形成し、ウエハカバーを用いてゲートパターン露光する。この半導体製造プロセスとすることで、ゲート用導電膜への転写パターン精度を向上させることができる。半導体ウエハW1の主面の半導体素子のアイソレーション形成などで生じた絶縁膜段差を化学的機械研磨法(Chemical Mechanical Polishing)により表面研磨し、平坦化する。平坦化後、酸化シリコン膜(SiO2)などからなるゲート絶縁膜を形成し、ポリシリコン等からなる導電膜を堆積する。前記の絶縁膜と導電膜は、ウエハ段差を生じさせないプロセスである。この後、フォトレジストを塗布形成した半導体ウエハは、平坦になっている。続けて、ウエハカバー付加し、縮小投影露光してゲート回路パターンを転写する。

従来ハーフトーン型位相シフトマスクを用いてゲートパターンを形成した製品では、遮光マスクとウエハカバーを併用した露光法に換えて、露光コストを削減することができる。さらに、位相シフトマスクとウエハカバーを用いることで、位相シフト効果とウエハカバー内で露光光の波長が短くした効果が相乗され、露光波長以下の転写パターンを形成することができる。

露光波長の半分より微細なゲートパターン形成に用いるマスクは、位相反転させた境界部を投影露光した時に生じる急峻な影を転写させる位相シフトマスク用いるのが有効である。この方式は同じフォトレジスト膜上に位相シフトマスク露光と遮光マスク露光とを重ねる必要があり、処理工数が増える。位相反転させたマスクパターンの光の干渉による極めて細い影を露光し、遮光マスクを用いて前記の細い影を残すように重ね露光することで微細ゲートパターンを形成することができる。

【0060】

nチャネル・フォト工程P5は、pチャネル側のMOSFET形成領域を被覆するようなフォトレジストパターンの形成工程である。nチャネル形のMOSFET形成領域に、例えばn形不純物のリンまたはヒ素をイオン注入法等により導入する。この際、ゲート電極をマスクとして自己整合的にn形不純物を半導体ウエハW1に導入できるので、転写パターンの精度は緩くできる。

【0061】

pチャネル・フォト工程P6は、逆に、nチャネル側のMOSFET形成領域を被覆するようなフォトレジストパターンを形成する工程である。pチャネル形のMOSFET形成領域に、例えばp形不純物のホウ素をイオン注入法等によって導入する。この際、ゲート電極をマスクとして自己整合的にp形不純物を半導体ウエハW1に導入できるので、転写パターンの精度は緩くできる。

【0062】

その後、半導体ウエハW1に対して熱処理を施すことにより、n形の半導体領域のソース領域およびドレイン領域、p形の半導体領域のソース領域およびドレイン領域を形成する。

【0063】

ポリシリコン・フォト工程P7は、配線または抵抗となる第2層ポリシリコン膜をパターニングするためのフォトレジストパターンを形成する工程である。半導体W1の主面上に、例えば酸化シリコン膜からなる層間絶縁膜をCVD法によって堆積し、その上面にポリシリコン膜をCVD法等によって堆積する。ポリシリコン・フォト工程P7により、配線および抵抗領域を被覆するようなフォトレジストパターンを形成する。

【0064】

R・フォト工程P8は、ポリシリコン膜に不純物を導入する際のマスクとなるフォトレジストパターンをパターニングする工程である。ポリシリコン膜をフォトリソグラフィ技術およびエッチング技術によってパターニングした後、そのパターニングされたポリシリコン膜の所定領域に不純物を導入することにより、ポリシリコン膜からなる配線および抵抗を形成する。

【0065】

コンタクト・フォト工程P9は、半導体ウエハW1の主面上に、例えば酸化シリコン膜(SiO2)からなる層間絶縁膜を堆積した後、コンタクトホール(孔)を形成する工程である。フォトレジストは、通常ポジ型フォトレジストを用いる。SOG(Spin On Glass)よる層間絶縁膜は、下層パターンの密度による膜厚変動を抑制させる事と下記のウエハカバーを用いた露光精度向上のため化学的機械研磨法(Chemical Mechanical Polishing)により表面研磨し、平坦化する。平坦化した層間絶縁膜に対し、CVD法などにより、層間絶縁膜を積層しても良い。

平坦化した層間絶縁膜に、前記の半導体領域および配線の一部が露出するようなコンタクトホールをフォトリソグラフィ技術およびエッチング技術によって穿孔する。コンタクトホールは、図16に示した半導体プロセスとすることで、絶縁膜にパターン転写する。このプロセスの特徴は、絶縁膜形成、平坦化処理した後、ポジ型フォトレジスト面形成、ウエハカバー露光、ウエハカバー除去、現像と続く処理フローとすることで、寸法バラツキの少ないコンタクトホールを形成することができる。

続いて、半導体ウエハW1の主面上に、例えば窒化チタン(TiN)、チタン(Ti)およびタングステン(W)を下層から順にスパッタリング法等によって堆積した後、前記堆積金属膜をエッチバック法または化学的機械研磨法によってコンタクトホール内のみに残されるようにエッチングすることで、コンタクトホールを埋め込む。

【0066】

Al−1・フォト工程P10は、例えばアルミニウム(Al)またはAl合金等からなる金属膜を第1層配線としてパターニングする工程である。チタン膜、AlまたはAl合金膜、チタン膜および窒化チタン膜等をスパッタリング法等によって下層から順に堆積した後、その積層金属膜およびその下層のチタン膜および窒化チタン膜をフォトリソグラフィ技術およびエッチング技術によってパターニングすることにより、第1層配線を形成する。

【0067】

第1層配線パターンは、図17に示したように、導電膜を平坦化し、ウエハカバー露光する。このプロセスの特徴は、導電膜(金属膜)の平坦化とウエハカバー露光とすることで、下地段差の影響を低減し、転写パターンの精度を向上させるものである。また、図18に示したように、絶縁膜を平坦化し、導電膜形成、ウエハカバー露光する半導体製造プロセスとするとしてもよい。このプロセスの特徴は、絶縁膜を平坦化した後、ウエハカバー露光することで、下地段差の影響を低減し、転写パターンの精度を向上させるものである。

マスクは、先端製品で回路パターンが露光光の波長より小さい場合、位相シフトマスクを用いる。更にウエハカバーを用いることで、ウエハカバー中の露光光の波長が短くなった効果が相乗され、転写パターンの寸法精度を向上させることが可能となる。

【0068】

スルーホール・フォト工程P11は、第1、第2層配線間を接続するスルーホール(孔)TH1を開口するためのフォトレジストパターンを形成する工程である。半導体ウエハW1上に、例えば酸化シリコン膜等の第1層間絶縁膜をCVD法等によって堆積し、これを化学機械研磨法により平坦化する。平坦化した絶縁膜上に、酸化シリコン膜等からなる第2層間絶縁膜を堆積した後、フォトリソグラフィ技術およびエッチング技術によってその一部に第1層配線の一部が露出するようなスルーホールTH1を穿孔する。

スルーホールTH1は、図16に示した半導体製造プロセスを採用して、絶縁膜の開口パターンを形成する。このプロセスの特徴は、絶縁膜の平坦化、ポジ型フォトレジスト面形成、ウエハカバー露光とすることで、転写パターンの精度を向上させるものである。

マスクは、先端製品で回路パターンが露光波長以下の場合、位相シフトマスクを用いる。マスクは、図9の遮光膜の代わりにハーフトーン型とし、更にウエハカバーを用いた露光とすることで、ウエハカバー中の露光光の波長が短くなり、相乗効果により解像度向上される。

【0069】

Al−2・フォト工程P12は、AlまたはAl合金等を含む金属膜をスパッタリング法等により堆積した後、この金属膜を第2層配線としてパターニングするための工程である。この工程は、第1層配線の形成工程と同じである。

【0070】

ボンディングパッド・フォト工程P13は、半導体ウエハW1の表面保護膜にボンディングパッドに対応する100μm程度の開口部を形成する工程であり、表面保護膜上にボンディングパッド形成領域以外を被覆するフォトレジストパターンを形成する工程である。半導体ウエハW1の主面上に、例えば酸化シリコン膜を含む表面保護膜をCVD法等により堆積して第3層配線を被覆した後に行う。

【0071】

これらの露光プロセスのうち、nウエル・フォト工程P1、nチャネル・フォト工程P5、pチャネル・フォト工程P6およびボンディングパッド・フォト工程P13は、ラフパターンに該当するパターンであり、最小寸法が比較的大きく、寸法精度も厳しくないので、マスク製作及びウエハ上へのパターン転写の制約はほとんどなく、従来のマスク露光方式を用いる。

露光波長より微細な寸法の配線形成工程では、図17または図18に示した半導体プロセスとすることで、導電膜(金属膜)に転写するパターン精度を向上させることができる。第1層配線は、マスクは、ハーフトーン型などの位相シフトマスクを用い、転写パターン精度を向上させることができる。図18において、平坦化直後に絶縁膜の開口のための第一露光は、ウエハカバーを用いた露光方式でも良いし、従来の露光方式でも良い。ポイントは、パターニングした絶縁膜上に導電膜を形成し、この導電膜を配線として用いる配線のパターン形成には、図18に示した導電膜パターンの形成プロセスとする。この方式により、より微細な導電膜パターンが形成でき、その精度を向上させることができる。

【0072】

コンタクト・フォト工程P9では、化学増幅系のポジ形フォトレジスト面を用いてコンタクトホールを形成する。先端製品の場合に用いるマスクは、図9の遮光膜の代わりにハーフトーン基板上に形成し、マスクカバーを重ねた位相シフトマスクを用いることで、転写パターンの寸法精度を向上させることができる。

【0073】

図19は、ウエハカバーを用いた回路パターンを形成する工程とウエハカバーを用いない回路パターンを形成する工程とを適用した半導体製造方法の説明図である。ファインパターンではウエハカバーを用い、ラフパターンではウエハカバーを用いる。

【0074】

実施例では、ウエハカバーの材質として、平板状の合成石英ガラスについて説明した。合成石英ガラスを選択したのは、露光光の光源としてアルゴンフロライド(ArF)エキシマレーザに対しても、十分な透過率を持つからである。例えばフッ素ダイマー(F2)レーザの場合は、ウエハカバーの材質として蛍石ガラスを用いることができる。マスクカバーの材質については、ウエハカバーの材質よりも透過率の制約が厳しく、上記と同じものを選択した。

ウエハカバーに関して、透過率が低い材質を選択した場合は、フォトレジストの露光時間が増加する。露光光に対して透過率が低い材質を用いると露光光はウエハカバーで吸収され、温度上昇する。従って、露光光に対して透過率が高い方が望ましいのであるが、露光光に対して透過率が80%程度あれば、プラスチックのような有機材を平板にしたものであっても良い。また、ビニールシートであっても良い。

また、半導体ウエハ上のフォトレジスト面にレジストと異なる有機膜を堆積させたものであっても良い。露光後、フォトレジスト膜の現像前に有機膜の除去できれば良い。

[0075] なお、半導体集積回路の製造プロセスへは、ウエハカバーを用いた縮小投影露光法、マスクカバーを用いたマスクを用いて、集積回路パターンを形成することに重点をおいて説明したが、この組み合せに限定されるものではない。

例えば、平坦化プロセスと液浸露光方式とを組み合わせてもよい。被露光試料表面を平坦にすることで、試料表面の微小段差による液浸用液体の不均一な流れに伴う微小泡の発生を抑えることができる。試料表面の段差が1ミクロン以下のごく微小段差であってもカルマン渦と呼ばれる渦状に分布した泡が生じることが多く、試料表面を平坦にすることで、その発生を抑制することができる。また、液浸用液体として純水を用いる場合は、沸騰冷却して気泡除去することで泡の発生をさらに抑制することができる。

[0076] また、半導体集積回路の平坦化プロセス手法として、化学的機械研磨法(Chemical Mechanical Polishing)を示したが、化学機械研削法(Chemical Mechanical Lapping)を用いても良い。

また、半導体ウエハに転写するための回路パターンが本投影露光方式によって生じる転写歪を逆に歪ませた回路パターンをマスク上に形成しておく手法、光近接効果補正(Optical Proximily Correclion)を付加したパターンをマスク上に形成してあっても良い。また、本発明マスクと液浸露光方式とを組み合わせて用いても良い。

[0077] マスクのパターン回に装着するマスクカバー、半導体ウエハのフォトレジスト面に装着するウエハカバーの投影レンズ側の表面には、露光光に対して反射防止膜を設けても良い。これにより、マスクカバー、ウエハカバー表面で反射の影響なくすることができる。

[0078] 本発明の半導体露光装置の縮小投影レンズとして説明したが、複数のレンズから構成されるレンズ群の中に、非球面ミラーを組み合わせて用いた縮小投影光学系であっても良い。また、マスクは、光透過型であるが、反射型であっても良い。

[0079] 以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0080】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野であるCMOS回路を有する半導体装置の製造方法に適用した場合について説明したが、それに限定されるものではなく、例えばDRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)またはフラッシュメモリ(EEPROM;Electric Erasable Programmable Read Only Memory)等のようなメモリ回路を有する半導体装置、マイクロプロセッサ等のような論理回路を有する半導体装置あるいはメモリ回路と論理回路とを同一基板に設けている半導体装置等、他の半導体装置の製造方法にも適用できる。また、マイクロマシンや液晶ディスプレイ等のような他の装置の製造方法にも適用できる。

【産業上の利用可能性】

【0081】

本発明は、半導体装置を製造する上で、超高集積に伴って生じる本質的な課題を解決する簡単な手法を提示するものであり、産業上の利用可能性は高い。

Claims (5)

- 集積回路パターンを形成したマスクを用い、半導体ウエハ上のフォトレジストに露光するための縮小投影露光装置であって、

前記マスクを縮小投影露光装置の所定の箇所に配置する手段と、

ガラス平板、高分子樹脂平板または高分子樹脂シートの内のいずれかからなる所定の厚さのウエハカバーを半導体ウエハ上のフォトレジスト表面に接触した状態で、縮小投影露光装置の投影レンズに対して平面移動できるように半導体ウエハと共に縮小投影露光装置の所定の箇所に配置する手段と、

前記縮小投影露光装置の露光光が前記マスクを照明すると前記投影レンズ、前記ウエハカバーを透過して、前記半導体ウエハ上のフォトレジストを露光し、この露光を繰り返して、半導体ウエハ上のフォトレジストに、同じ集積回路パターンのマスクを用いて複数露光する手段と、を備えたことを特徴とする縮小投影露光装置。 - 請求項1記載の縮小投影露光装置であって、

前記縮小投影露光装置の露光光が前記マスクを照明する際に、半導体ウエハ上のフォトレジストに露光によって形成されるパターンがより鮮明に結像させるように、マスクの回路パターンの方向と周期に対応して最適化した角度だけ傾けてマスクの回路パターン面を照明する手段を備えたことを特徴とする縮小投影露光装置。 - 集積回路パターンを形成したマスクと縮小投影露光装置とを用い、半導体ウエハ上のフォトレジストを露光することによって、半導体ウエハ上に回路パターンを形成する半導体装置の製造方法であって、

前記マスクを縮小投影露光装置の所定の箇所に配置するステップと、

露光光を透過し、所定の厚さのガラス平板、高分子樹脂平板または高分子樹脂シートの内のいずれかからなるウエハカバーを半導体ウエハのフォトレジスト表面に接触させて、半導体ウエハと共に縮小投影露光装置の所定の箇所に配置するステップと、

前記縮小投影露光装置の露光光が前記マスクを照明すると前記投影レンズ、前記ウエハカバーを透過して、前記半導体ウエハ上のフォトレジストを露光し、この露光を繰り返して、半導体ウエハ上のフォトレジストに、同じ集積回路パターンのマスクを用いて複数露光するステップと、

前記ウエハカバーを除去した後、前記フォトレジストを現像するステップと、を含み、

半導体ウエハ上に回路パターンを形成することを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法であって、

前記半導体ウエハ上のフォトレジストに、同じ集積回路パターンのマスクを用いて複数露光するステップは、

マスクの透過光の位相が部分的に反転するようにした手段を設けた位相シフトマスクを準備するステップと、

前記位相シフトマスクの透過光の干渉を利用して、露光波長より微細な回路パターンを半導体ウエハ上に形成すべく、露光するステップと、

を含むことを特徴とする半導体装置の製造方法。 - 請求項3記載の半導体装置の製造方法であって、

前記半導体ウエハ上のフォトレジストに、同じ集積回路パターンのマスクを用いて複数露光するステップは、

前記縮小投影露光装置の露光光が前記マスクを照明する際に、半導体ウエハ上のフォトレジストに露光によって形成されるパターンがより鮮明に結像させるように、マスクの回路パターンの方向と周期に対応して最適化した角度だけ傾けてマスクの回路パターン面を照明するステップを含むことを特徴とする半導体装置の製造方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004031528 | 2004-02-09 | ||

| JP2004031528 | 2004-02-09 | ||

| PCT/JP2005/001669 WO2005076322A1 (ja) | 2004-02-09 | 2005-02-04 | 露光装置及びそれを用いた半導体装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010080762A Division JP2010153922A (ja) | 2004-02-09 | 2010-03-31 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2005076322A1 JPWO2005076322A1 (ja) | 2008-02-21 |

| JP4529141B2 true JP4529141B2 (ja) | 2010-08-25 |

Family

ID=34836053

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005517741A Expired - Fee Related JP4529141B2 (ja) | 2004-02-09 | 2005-02-04 | 露光装置及びそれを用いた半導体装置の製造方法 |

| JP2010080762A Pending JP2010153922A (ja) | 2004-02-09 | 2010-03-31 | 半導体装置の製造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010080762A Pending JP2010153922A (ja) | 2004-02-09 | 2010-03-31 | 半導体装置の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8048614B2 (ja) |

| JP (2) | JP4529141B2 (ja) |

| KR (2) | KR101118787B1 (ja) |

| WO (1) | WO2005076322A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4450769B2 (ja) * | 2005-06-16 | 2010-04-14 | 富士フイルム株式会社 | 画像処理装置、画像描画装置及びシステム |

| JP6474655B2 (ja) * | 2014-09-30 | 2019-02-27 | エイブリック株式会社 | レチクル透過率測定方法、投影露光装置および投影露光方法 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0216717A (ja) * | 1988-07-05 | 1990-01-19 | Nikon Corp | パターン投影装置 |

| JPH06168866A (ja) * | 1992-11-27 | 1994-06-14 | Canon Inc | 液浸式投影露光装置 |

| JPH11260686A (ja) * | 1998-03-11 | 1999-09-24 | Toshiba Corp | 露光方法 |

| WO1999049504A1 (fr) * | 1998-03-26 | 1999-09-30 | Nikon Corporation | Procede et systeme d'exposition par projection |

| WO1999049366A1 (fr) * | 1998-03-20 | 1999-09-30 | Nikon Corporation | Photomasque et systeme d'exposition par projection |

| JP2000058436A (ja) * | 1998-08-11 | 2000-02-25 | Nikon Corp | 投影露光装置及び露光方法 |

| WO2001002908A1 (fr) * | 1999-06-30 | 2001-01-11 | Hitachi, Ltd. | Procede de fabrication d'un dispositif de circuit integre a semiconducteur, masque optique utilise a cet effet, son procede de fabrication, et ebauches de masque utilisees a cet effet |

| JP2001117213A (ja) * | 1999-08-10 | 2001-04-27 | Nikon Corp | フォトマスク、該フォトマスクの製造方法、該フォトマスクを扱う投影露光装置、及び投影露光方法 |

| JP2004191920A (ja) * | 2002-12-09 | 2004-07-08 | Cark Zeiss Smt Ag | マイクロリソグラフィ用等の投影対物レンズ及び投影対物レンズの調整方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57153433A (en) * | 1981-03-18 | 1982-09-22 | Hitachi Ltd | Manufacturing device for semiconductor |

| JPS63295350A (ja) | 1987-05-26 | 1988-12-01 | Ozen Corp | シ−ト重複検知装置 |

| JPH03137511A (ja) | 1989-10-24 | 1991-06-12 | Nkk Corp | 二重管式連通管 |

| JPH0852997A (ja) | 1991-03-29 | 1996-02-27 | Masaki Kawasaki | 積層板構造の象嵌模様入り製品及びその製造方法 |

| US5391441A (en) * | 1992-02-21 | 1995-02-21 | Hitachi, Ltd. | Exposure mask and method of manufacture thereof |

| JP3747566B2 (ja) | 1997-04-23 | 2006-02-22 | 株式会社ニコン | 液浸型露光装置 |

| JP3817836B2 (ja) * | 1997-06-10 | 2006-09-06 | 株式会社ニコン | 露光装置及びその製造方法並びに露光方法及びデバイス製造方法 |

| US6184083B1 (en) * | 1997-06-30 | 2001-02-06 | Kabushiki Kaisha Toshiba | Semiconductor device and method of manufacturing the same |

| JP2000183346A (ja) * | 1998-12-15 | 2000-06-30 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP3495983B2 (ja) * | 2000-12-28 | 2004-02-09 | キヤノン株式会社 | マスク及び投影露光装置 |

| US7092069B2 (en) * | 2002-03-08 | 2006-08-15 | Carl Zeiss Smt Ag | Projection exposure method and projection exposure system |

| US7014966B2 (en) * | 2003-09-02 | 2006-03-21 | Advanced Micro Devices, Inc. | Method and apparatus for elimination of bubbles in immersion medium in immersion lithography systems |

| US20050161644A1 (en) * | 2004-01-23 | 2005-07-28 | Peng Zhang | Immersion lithography fluids |

| EP1714192A1 (en) * | 2004-02-13 | 2006-10-25 | Carl Zeiss SMT AG | Projection objective for a microlithographic projection exposure apparatus |

-

2005

- 2005-02-04 KR KR1020067018448A patent/KR101118787B1/ko not_active IP Right Cessation

- 2005-02-04 KR KR1020117014358A patent/KR101118834B1/ko active IP Right Grant

- 2005-02-04 WO PCT/JP2005/001669 patent/WO2005076322A1/ja active Application Filing

- 2005-02-04 JP JP2005517741A patent/JP4529141B2/ja not_active Expired - Fee Related

-

2006

- 2006-08-09 US US11/463,467 patent/US8048614B2/en active Active

-

2010

- 2010-03-31 JP JP2010080762A patent/JP2010153922A/ja active Pending

- 2010-08-27 US US12/870,752 patent/US20110229824A1/en not_active Abandoned

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0216717A (ja) * | 1988-07-05 | 1990-01-19 | Nikon Corp | パターン投影装置 |

| JPH06168866A (ja) * | 1992-11-27 | 1994-06-14 | Canon Inc | 液浸式投影露光装置 |

| JPH11260686A (ja) * | 1998-03-11 | 1999-09-24 | Toshiba Corp | 露光方法 |

| WO1999049366A1 (fr) * | 1998-03-20 | 1999-09-30 | Nikon Corporation | Photomasque et systeme d'exposition par projection |

| WO1999049504A1 (fr) * | 1998-03-26 | 1999-09-30 | Nikon Corporation | Procede et systeme d'exposition par projection |

| JP2000058436A (ja) * | 1998-08-11 | 2000-02-25 | Nikon Corp | 投影露光装置及び露光方法 |

| WO2001002908A1 (fr) * | 1999-06-30 | 2001-01-11 | Hitachi, Ltd. | Procede de fabrication d'un dispositif de circuit integre a semiconducteur, masque optique utilise a cet effet, son procede de fabrication, et ebauches de masque utilisees a cet effet |

| JP2001117213A (ja) * | 1999-08-10 | 2001-04-27 | Nikon Corp | フォトマスク、該フォトマスクの製造方法、該フォトマスクを扱う投影露光装置、及び投影露光方法 |

| JP2004191920A (ja) * | 2002-12-09 | 2004-07-08 | Cark Zeiss Smt Ag | マイクロリソグラフィ用等の投影対物レンズ及び投影対物レンズの調整方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110229824A1 (en) | 2011-09-22 |

| KR20070019705A (ko) | 2007-02-15 |

| US20070117409A1 (en) | 2007-05-24 |

| JP2010153922A (ja) | 2010-07-08 |

| KR20110091015A (ko) | 2011-08-10 |

| WO2005076322A1 (ja) | 2005-08-18 |

| US8048614B2 (en) | 2011-11-01 |

| KR101118787B1 (ko) | 2012-03-20 |

| KR101118834B1 (ko) | 2012-03-21 |

| JPWO2005076322A1 (ja) | 2008-02-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100240522B1 (ko) | 반도체 집적 회로장치의 제조 방법 | |

| JP3197484B2 (ja) | フォトマスク及びその製造方法 | |

| US6556277B2 (en) | Photolithographic apparatus | |

| US6800421B2 (en) | Method of fabrication of semiconductor integrated circuit device | |

| US6551750B2 (en) | Self-aligned fabrication technique for tri-tone attenuated phase-shifting masks | |

| JP2002122980A (ja) | 半導体集積回路装置の製造方法およびフォトマスクの製造方法 | |

| JP3164039B2 (ja) | フォトマスク及びその製造方法 | |

| JP4529141B2 (ja) | 露光装置及びそれを用いた半導体装置の製造方法 | |

| US12087579B2 (en) | Method for forming semiconductor device | |

| CN110058484B (zh) | 拼接式光刻制作工艺的光掩模、半色调光掩模及其制法 | |

| US6593039B1 (en) | Photoresist mask that combines attenuated and alternating phase shifting masks | |

| US6910203B2 (en) | Photomask and method for qualifying the same with a prototype specification | |

| JPH06289590A (ja) | フォトマスク及び露光方法 | |

| US6576376B1 (en) | Tri-tone mask process for dense and isolated patterns | |

| JP3696982B2 (ja) | 半導体集積回路露光用のフォトマスク | |

| US7462426B2 (en) | Method for producing a phase mask | |

| JP3639726B2 (ja) | 計算装置及び計算方法 | |

| JP2004264385A (ja) | 露光マスクおよびその製造方法ならびに露光方法 | |

| JP3238732B2 (ja) | 半導体集積回路装置の製造方法 | |

| JPH05275303A (ja) | 露光方法およびそれに用いるフォトマスク | |

| JP2003282426A (ja) | 半導体装置の製造方法 | |

| JP2000019712A (ja) | マスク及びそれを用いた露光方法 | |

| US20100304278A1 (en) | Method for Fabricating a Phase Shift Mask Using a Binary Blank |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080131 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100202 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100331 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100518 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100527 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130618 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |