JP4457648B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4457648B2 JP4457648B2 JP2003390168A JP2003390168A JP4457648B2 JP 4457648 B2 JP4457648 B2 JP 4457648B2 JP 2003390168 A JP2003390168 A JP 2003390168A JP 2003390168 A JP2003390168 A JP 2003390168A JP 4457648 B2 JP4457648 B2 JP 4457648B2

- Authority

- JP

- Japan

- Prior art keywords

- terminal

- lsi chip

- package

- test

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/2851—Testing of integrated circuits [IC]

- G01R31/2884—Testing of integrated circuits [IC] using dedicated test connectors, test elements or test circuits on the IC under test

Landscapes

- Tests Of Electronic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

近年、高密度、高集積度、高機能を得るため、同図に示すように、複数のLSIチップ(LSIチップA51、LSIチップB52)を1つのパッケージ91に入れた半導体装置が開発されている。この種の半導体装置90のテストは、複数のLSIチップA51、LSIチップB52が接続された状態で行われていた(例えば、特許文献1参照)。

この為、LSIチップB52をテスト(例えば、動作テスト)する場合、一部の端子in1(62)がパッケージ91の外部端子として存在しない為、その端子in1(62)への信号入力は、LSIチップA51を動作させて与える必要がある。

この事は、LSIチップB52を単体でテストする場合に比べ、テストパターン数が増えてしまう可能性につながり、場合によっては十分なテストが行えない事も考えられる。テストパターン数の増加は、半導体装置の検査コストの上昇にもつながり、十分なテストを行えない事は、不良品を検出する選別ができない事を意味する。

同図に示すように、LSIチップA51及びLSIチップB52の全ての端子をパッケージ101の外部に露出させ、LSIチップA51とLSIチップB52との接続を波線で示すようにパッケージ101の外部で端子16、17間、端子20、21間をそれぞれ接続する場合、外部端子の増加による、パッケージ101の大型化につながる事が懸念される。

このため、テストパターン数を少なくすることができ、試験時間の短縮により製品コストの低減を図ることができる半導体集積回路が提案されている(例えば、特許文献2参照)。

そこで、本発明の目的は、一つのパッケージに内蔵された複数のLSIチップの個別テストを同時に行うことができる半導体装置を提供することにある。

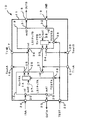

図1に示すように、本半導体装置10は、複数(図では二つであるが限定されない。)のLSIチップA12、LSIチップB13を一つのパッケージ11に内蔵し、各LSIチップA12、LSIチップB13間の接続をパッケージ11の内部で行った半導体装置である。本半導体装置10は、それぞれのLSIチップA12、LSIチップB13が個別にされるテストと同様のテストがパッケージ化された状態であっても、同時に実施することができる様にする為に、それぞれのLSIチップA、B内にセレクタ回路(以下「セレクタ」という。)を内蔵している事、通常使用時からテスト状態に切り替える為のテスト切り替え端子を1本設けている事、LSIチップA12、LSIチップB13のテスト時だけに使用するテスト用端子をパッケージの通常使用しない端子箇所に設けている事を特徴とする。

セレクタA14は、LSIチップA12の端子out2(37)に接続された一つの信号入力端子と、LSIチップA12の端子TESTAに接続された一つの制御信号入力端子と、LSIチップA12の出力端子25、26に接続された二つのデータ出力端子とを有する。セレクタA14は、例えば、入力端子を共通接続した二つのトライステート(登録商標)バッファからなっている。

セレクタA14は、制御信号入力端子に制御信号が入力されていないときは端子ToutA側の出力端子がハイインピーダンス状態(例えば、出力端子をオープンにした状態)になり、制御信号入力端子に制御信号が入力されているときは接続先のLSIチップB13側の出力端子がハイインピーダンス状態になる。

図1に示す装置は、LSIチップA12およびLSIチップB13の2つのLSIチップが、1つのパッケージ11に内蔵された半導体装置であり、それぞれのLSIチップA12およびLSIチップB13に設けられたテスト専用の端子(TESTA28、TESTB33)を制御することで、LSIチップA12とLSIチップB13とを並列にテスト出来るよう、セレクタA14、セレクタB15と、LSIチップA12、LSIチップB13のテスト時にのみ使用する端子(TinA21、ToutA16、TinB17、ToutB20)を設けている。

図2において、LSIチップA12とLSIチップB13とが内蔵されたパッケージ11の例として、BGA(Ball Grid Array )の端子配置を表した底面が示されており、パッケージ11の中心部分41の端子42が、LSIチップA12、LSIチップB13のテスト時にのみ使用する端子(TinA21、ToutA16、TinB17、ToutB20)として用いられている。この事は、通常時に使用される端子40はパッケージ11の外周に設けられている為、本発明の半導体装置10を、他の部品や他のLSIパッケージとプリント基板等に搭載して接続する場合などは、接続がし易くなり、検査効率が向上するので有利である。

尚、図2に示す半導体装置は端子数(ボール数)が計200個の場合を示しているが、本発明はこれに限定されるものではなく、ボール数が200個以上であっても200個未満であってもよい。また、本実施の形態では端子40がパッケージ11の外周部に設けられ、テスト用の端子42がパッケージ11の中央部に設けられた場合を示しているが、本発明はこれに限定されるものではなく、フルグリッドアレイタイプであってもよい。さらに、本実施の形態ではBGA型の半導体装置の場合で説明したが、本発明はこれに限定されるものではなく、PGA(Pin Grid Array)型の半導体装置であってもよい。

同様に、セレクタB15は、端子out1(29)からの信号を端子ToutB20に出力し、LSIチップA12の端子in2(27)に接続されるセレクタB15の出力端子は、ハイインピーダンスを出力する。

同様に、LSIチップB13の端子out1(38)からの信号をセレクタB15の切り替えによりLSIチップA12のin2(27)に接続するようにし、端子ToutB20に接続されるセレクタB15の出力は、ハイインピーダンス状態にする。

このように、テスト時に使用する端子は、通常動作時はハイインピーダンス状態となるので、端子処理としてもオープン扱いが可能となる。

複数のLSIチップを一つのパッケージに内蔵した半導体装置の状態においても、それぞれのLSIチップが1個づつ個別部品としてテストされる時と同じテストを同時に行う事を可能とし、十分なテストを行える状況にすることで、検査コストの上昇を防ぐ効果と、最終製品への不良品の混入を低減できる効果とが得られる。

第2の実施の形態について図3を用いて説明する。

図3は、本発明の半導体装置の他の実施の形態を示す概念図である。尚、図1に示した実施の形態と同様の部材には共通の符号を用いた。

第2の実施の形態は、第1の実施の形態においてのLSIチップA12に内蔵されていたセレクタA14をLSIチップA12の外部に出し、テスト専用の端子TESTA28(図1参照)を削除し、同様にLSIチップB13に内蔵されていたセレクタB15をLSIチップB13の外部に出し、テスト専用の端子TESTB3(図1参照)を削除し、LSIチップA51、LSIチップB52、セレクタA53およびセレクタB54をパッケージ11に内蔵したものである。図3に示す半導体装置50は、LSIチップA51およびLSIチップB52をテストする場合の動作及びテスト以外の通常の動作については、第1の実施の形態と同様である。

図4は、本発明の半導体装置の他の実施の形態を示す概念図である。

第3の実施の形態としての半導体装置70は、セレクタA53およびセレクタB54の機能を、LSIチップA51およびLSIチップB52とは別のLSIチップとして実現する事も可能である。

図5は、本発明の半導体装置の他の実施の形態を示す概念図である。

第4の実施の形態としての半導体装置80は、端子TinA21とLSIチップA51の端子in2(56)の間に新たに別のセレクタ82を設け、端子TEST22の制御にて通常動作時は、端子TinA21からの信号を電気的に切断し、端子TinA21にぶら下がる配線容量(分布容量)を少なくする事で、LSIチップB52の端子out1(61)とLSIチップA51の端子in2(56)との間の伝送信号を高速に送る事が可能となる。同様にTinB端子17とLSIチップB52の端子in1(62)との間に新たに別のセレクタ81を設け端子TEST22の制御にて通常動作時は、端子TinB17にぶら下がる配線容量(分布容量)を少なくし、LSIチップA51の端子out2(55)とLSIチップB52の端子in1(62)との間の伝送信号を高速に送る事が可能となる。

尚、本実施の形態では、セレクタ81、82がLSIチップA51、LSIチップB52の外部に設けられた場合で説明したが、本発明はこれに限定されるものではなく、第1の実施の形態のように各LSIチップA51、LSIチップB52にそれぞれ内蔵されていてもよく、第3の実施の形態のようにLSIチップ70の中に内蔵されていてもよい。

11 パッケージ

12 LSIチップA

13 LSIチップB

14 セレクタA(セレクタ回路A)

15 セレクタB(セレクタ回路B)

16 ToutA(端子)

17 TinB(端子)

18 OUTB(端子)

19 INB(端子)

20 ToutB(端子)

21 TinA(端子)

22 TEST(端子)

23 OUTA(端子)

24 INA(端子)

Claims (4)

- 複数のLSIチップ同士を電気的に接続して一つのパッケージ内に内蔵した半導体装置において、

前記各LSIチップの間に配置され、テスト時に前記パッケージの外部からの信号により前記各LSIチップの出力信号を接続先の他のLSIチップから前記パッケージの外部に出力自在に切り替えるセレクタ回路と、

前記パッケージの通常動作時用の端子とは異なる位置に配置され、テスト時に前記パッケージの外部と信号の授受が行われる複数のテスト用の端子と、

前記テスト用の端子のうち外部からの信号が入力される端子と前記各LSIチップの入力用の端子との間に配置され、通常動作時には前記テスト用の端子と前記各LSIチップの入力用の端子との間を切断する他のセレクタ回路を有し、前記テスト用の端子から前記各LSIチップとの間の分布容量を減少させることにより、前記各LSIチップ間の伝送信号を高速に送るようにしたことを特徴とする半導体装置。 - 前記セレクタ回路は、前記テスト用端子のうち出力端子に接続される出力端子が通常時にはハイインピーダンスを出力するような信号が入力されることを特徴とする請求項1記載の半導体装置。

- 前記パッケージはBGA用若しくはPGA用のパッケージであると共に、前記複数のテスト用端子はボールグリッド若しくはピンに包囲された面内に配置されていることを特徴とする請求項1または2記載の半導体装置。

- 前記パッケージはフルグリッドアレイのBGA用若しくはPGA用のパッケージであると共に、前記複数のテスト用端子は通常時には使用されないボール若しくはピングリッドに設定されていることを特徴とする請求項1から3のいずれか1項記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003390168A JP4457648B2 (ja) | 2003-11-20 | 2003-11-20 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003390168A JP4457648B2 (ja) | 2003-11-20 | 2003-11-20 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005148026A JP2005148026A (ja) | 2005-06-09 |

| JP4457648B2 true JP4457648B2 (ja) | 2010-04-28 |

Family

ID=34696640

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003390168A Expired - Fee Related JP4457648B2 (ja) | 2003-11-20 | 2003-11-20 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4457648B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5029073B2 (ja) * | 2007-03-07 | 2012-09-19 | 株式会社デンソー | 半導体装置および半導体装置のテスト方法 |

| CN118645442B (zh) * | 2024-06-11 | 2025-03-21 | 四川华尔科技有限公司 | 芯片集成化封装工艺 |

-

2003

- 2003-11-20 JP JP2003390168A patent/JP4457648B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005148026A (ja) | 2005-06-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4504783A (en) | Test fixture for providing electrical access to each I/O pin of a VLSI chip having a large number of I/O pins | |

| US7880491B2 (en) | Multilayer semiconductor device | |

| US20010039646A1 (en) | Structure having multiple levels of programmable integrated circuits for interconnecting electronic components | |

| JP5024740B2 (ja) | Lsiチップ試験装置 | |

| WO1988002553A2 (en) | Integrated circuit packaging configuration for rapid customized design and unique test capability | |

| KR20080036848A (ko) | 스택형 반도체 패키지 소켓 및 스택형 반도체 패키지테스트 시스템 | |

| EP1979757B1 (en) | An integrated circuit package, and a method for producing an integrated circuit package having two dies with input and output terminals of integrated circuits of the dies directly addressable for testing of the package | |

| US6356095B1 (en) | Semiconductor integrated circuit | |

| US6822474B2 (en) | On chip logic analyzer debug bus | |

| EP1358498B1 (en) | Input/output continuity test mode circuit | |

| JP4457648B2 (ja) | 半導体装置 | |

| JPH04250644A (ja) | マルチチップ実装ic | |

| US20080197872A1 (en) | Semiconductor chip, multi-chip semiconductor device, inspection method of the same, and electric appliance integrating the same | |

| US20080141089A1 (en) | Semiconductor Integrated Circuit and System Lsi | |

| JP2004037254A (ja) | スキャンテスト装置 | |

| US7564255B2 (en) | Semiconductor integrated circuit for reducing number of contact pads to be probed in probe test | |

| JP2003004808A (ja) | 半導体装置および半導体装置のテスト方法 | |

| JP2005274342A (ja) | マルチチップ型半導体装置 | |

| JPH04128666A (ja) | 半導体集積回路 | |

| JP2009085934A (ja) | ソケット基板上にスイッチ素子を有するテスト装置 | |

| KR20080061735A (ko) | 피시험 장치, 이를 테스트 하기 위한 시스템 및 방법 | |

| JP2000009800A (ja) | スキャンテスト回路およびそれを備えた半導体装置ならびにスキャンテスト方法 | |

| EP0502210B1 (en) | Semiconductor integrated circuit device with testing-controlling circuit provided in input/output region | |

| JP2558819B2 (ja) | 半田付不良検査用テスト回路を有する多ピンlsi | |

| JP2001305187A (ja) | 回路基板、および、回路基板の検査装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061013 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090511 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090519 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090717 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090804 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091002 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091027 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091222 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100119 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100201 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130219 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130219 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140219 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |