JP4374463B2 - 発振周波数制御回路 - Google Patents

発振周波数制御回路 Download PDFInfo

- Publication number

- JP4374463B2 JP4374463B2 JP2006349519A JP2006349519A JP4374463B2 JP 4374463 B2 JP4374463 B2 JP 4374463B2 JP 2006349519 A JP2006349519 A JP 2006349519A JP 2006349519 A JP2006349519 A JP 2006349519A JP 4374463 B2 JP4374463 B2 JP 4374463B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- control

- information

- circuit

- reference signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/14—Details of the phase-locked loop for assuring constant frequency when supply or correction voltages fail or are interrupted

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/095—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using a lock detector

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/093—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using special filtering or amplification characteristics in the loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/14—Details of the phase-locked loop for assuring constant frequency when supply or correction voltages fail or are interrupted

- H03L7/146—Details of the phase-locked loop for assuring constant frequency when supply or correction voltages fail or are interrupted by using digital means for generating the oscillator control signal

Description

周波数基準信号として、セシウム周波数基準発振器、ルビシウム周波数基準発振器、GPS信号による周波数同期型の基準発振器などが、放送、通信分野のシステムで利用されている。

具体的には、PLL(Phase Locked Loop)回路の位相比較のリファレンス信号、DSP(Digital Signal Processor)、FPGA(Field Programmable Gate Array)などの基準クロック信号、DA(Digital/Analog)コンバータ、AD(Analog/Digital)コンバータのサンプリングクロックとして使用される。

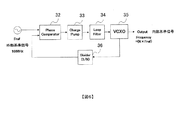

次に、従来のPLL回路について図6を参照しながら説明する。図6は、一般的PLL回路の構成ブロック図である。

PLL回路は、図6に示すように、外部基準信号(Fref )と1/N分周された信号を比較し、位相差信号を出力する位相比較器(Phase Comparator)32と、位相差をパルス幅の電圧で出力するチャージポンプ(Charge Pump)33と、チャージポンプ33からの出力電圧を平滑化するループフィルタ(Loop Filter)34と、ループフィルタ34からの制御電圧によって周波数を変更して希望する周波数(内部基準信号:Output Frequency)を発振出力する電圧制御機能付き水晶発振器(VCXO:Voltage Controlled Crystal Oscillator)35と、VCXO35の出力(内部基準信号)を1/Nに分周する分周器(Divider)36とを備えている。

尚、内部基準信号は、N×Fref の信号である。

PLL回路は、通信、放送装置などにおいて広く使用されている。

しかしながら、この場合、例えば、±0.5ppmの周波数安定度で動作するが、経年変化があるため、長期間性能を満足させることはできないものである。

尚、VCXOの制御電圧特性を図7に示す。図7は、電圧制御機能付き水晶発振器の制御電圧特性例を示す図である。図7において、横軸は制御電圧であり、縦軸は周波数偏差である。

図7の例のVCXOでは、制御電圧が0〜4Vであれば、動作可能であるが、4V以上では動作不能となる。

VCXOの場合でも、時間の経過に伴って、周波数偏差が上昇するため、適正な制御電圧が変化するものである。

本発明の実施の形態について図面を参照しながら説明する。

本発明の実施の形態に係る発振周波数制御回路は、電圧制御発振器と、電圧制御発振器からの出力を分周する分周器と、外部基準信号と分周器からの出力の位相を比較し、位相差信号を出力する位相比較器と、位相比較器からの出力を平滑化して出力するループフィルタと、外部基準信号を検波する検波回路と、パルス生成の情報が入力されるとパルスを生成してループフィルタに出力するパルス生成回路と、規定の電圧情報とそれに対応するパルス生成の情報を記憶するメモリと、位相比較器とループフィルタとの接続をオン/オフするスイッチと、検波回路で検出された外部基準信号のレベルが適正範囲内であればスイッチをオンとし、レベルが適正範囲外であればスイッチをオフとしてメモリに記憶されたパルス生成の情報をパルス発生回路に出力する制御部とを有するものであり、自己の周波数を補正し、高安定な基準信号の入力がなく、自走したときでも発振周波数を安定に保つことができるものである。

本発明の実施の形態に係る発振周波数制御回路について図1を参照しながら説明する。図1は、本発明の実施の形態に係る発振周波数制御回路の構成ブロック図である。

本発明の実施の形態に係る発振周波数制御回路(本回路)は、図1に示すように、フィルタ11と、位相比較器12と、スイッチ13と、ループフィルタ14と、電圧制御発振器15と、分周器16と、検波回路17と、増幅器18と、CPU(Central Processing Unit)20と、メモリ21と、PWM(Pulse Width Modulation)回路22と、レベル検出回路23と、ADコンバータ24と、ADコンバータ25とから構成されている。

フィルタ11は、例えば、10MHzの外部基準信号を帯域制限するフィルタである。基本構成として必須ではないが、外部基準信号の高周波成分を除去する働きがある。

位相比較器12は、フィルタ11から出力された基準信号と、分周器16で分周された信号の位相を比較し、位相差信号を出力する。

尚、位相比較器12は、外部基準信号と分周信号との位相を比較して同期(ロック)を検出した場合は、CPU20にロック検出信号を出力し、非同期(アンロック)を検出した場合は、CPU20にアンロック検出信号を出力する。

電圧制御発振器15は、ループフィルタ14からの制御電圧によって周波数を変更して希望する周波数(内部基準信号)を発振出力する。

尚、電圧制御発振器(VCO)の代わりに、電圧制御付き水晶発振器(VCXO)、電圧制御機能付き恒温槽水晶発振器(VC−OCXO)等を用いてもよい。

検波回路17は、フィルタ11からの出力信号のレベル検波を行う。

増幅器18は、検波回路17で検波された信号を増幅する。

制御電圧情報は、レベル検出回路23で検出され、変更となった場合にメモリ21で更新され、最新の値として保持される。

ここで、電圧・PWMデューティーサイクルテーブルについて図2を参照しながら説明する。図2は、電圧・PWMデューティーサイクルテーブルの概略図である。

電圧・PWMデューティーサイクルテーブルは、図2に示すように、電圧情報に対してパルス幅を特定するためのPWMデューティーサイクル(%)が記憶されている。

従って、レベル検出回路23で検出された制御電圧情報に対応するPWMデューティーサイクルを電圧・PWMデューティーサイクルテーブルから読み取り、そのサイクルに応じたパルスをPWM回路22がループフィルタ14に出力すると、ループフィルタ14から以前と同様の制御電圧が電圧制御発振器15に出力される。

ADコンバータ24は、増幅器18から出力された外部REFの検出レベルをアナログ信号からデジタル信号に変換してCPU20に出力する。

ADコンバータ25は、レベル検出回路23からの制御電圧情報をアナログ信号からデジタル信号に変換してCPU20に入力する。

本回路における動作について説明する。

本回路は、正常時、スイッチ13はオンで位相比較器12とループフィルタ14は接続された状態となっている。そして、位相比較器12は、外部基準信号と分周器16からの信号の位相差の信号を、ループフィルタ14を介して電圧制御発振器15に出力し、電圧制御発振器15における発振周波数を制御している。この際、レベル検出回路23は、最新の制御電圧を検出し、ADコンバータ25を介してCPU20に出力し、CPU20は、制御電圧情報に変更があれば、メモリ21で最新の制御電圧情報を更新する。

PWM回路22は、CPU20から入力されたパルス形成の情報に従ってパルスを生成し、ループフィルタ14を介して電圧制御発振器15に制御電圧を出力する。

つまり、位相比較器12の出力に代えて、PWM回路22からの出力を用いることで、これまでの状態を引き継いで電圧制御発振器15での周波数発振を適正化できるものである。

尚、上記例では、PWM回路22から出力されるパルスを、レベル検出回路23で検出された最新の制御電圧情報に基づいて生成するようにしたが、デフォルトの電圧情報を記憶し、そのデフォルトの電圧情報に対応するPWMデューティーサイクルに基づいてパルス生成の情報を出力するようにしてもよい。

デフォルトの電圧情報を用いれば、レベル検出回路23及びADコンバータ25の部品、メモリ21内の電圧・PMWデューティーサイクルテーブルを不要とすることができる。

本回路における校正について図3を参照しながら説明する。図3は、校正時の特性を示す図である。

本回路において、図3に示すように、外部基準信号が入力されない状態で時間が経過すると、周波数偏差が上昇又は下降する。図では上昇を示している。そこで、特定のタイミングで、適正な基準信号を入力して、その後、基準信号の入力を停止すると、自走制御により周波数偏差が中心周波数に戻ってきて校正が為されるようになっている。図3では、校正を2回繰り返している。

本回路によれば、校正時に特別な回路を接続しなくても、校正作業を行うことができる効果がある。

次に、本回路における経年変化に対する最適な制御電圧特性例を図4に示す。図4は、経年変化・制御電圧特性を示す図である。

図4に示すように、本回路においては、時間の経過と共に、最適な制御電圧が小さくなっている(但し、周波数偏差として上昇する場合を示している)。

更に、別の実施の形態(別の実施の形態2)として、本回路を上記経年変化に対応した構成とするものである。この別の実施の形態2について図5を参照しながら説明する。図5は、経年変化特性テーブルの概略図である。

本回路において、メモリ21には、電圧・PMWデューティーサイクルテーブルが格納されているが、そのテーブルの代わりに、図5の経年変化特性テーブルを利用するものである。

具体的には、時間の経過に対して適正な電圧情報が設定され、更にその電圧情報に対応してPWMデューティーサイクルが設定されてテーブルとして記憶されている。

CPU20は、内部にタイマーを備え、時間の経過を測定している。

この場合、CPU20は時間経過を計測しており、校正作業のときは経年変化特性テーブルを参照して時間経過に対応した電圧値を用いて周波数制御を行う。これにより、校正作業を周波数制御回路の経年変化に対応させることができる効果がある。

Claims (6)

- 電圧制御発振器と、前記電圧制御発振器からの出力を分周する分周器と、

外部基準信号と前記分周器からの出力の位相を比較し、位相差信号を出力する位相比較器と、

前記位相比較器からの出力を平滑化して前記電圧制御発振器に制御電圧を出力するループフィルタと、

前記ループフィルタからの出力について電圧レベルを検出して最新の制御電圧情報を出力するレベル検出回路と、

外部基準信号を検波する検波回路と、

パルス生成の情報が入力されるとパルスを生成して前記ループフィルタに出力するパルス生成回路と、

前記電圧制御発振器に出力される制御電圧の値を制御電圧情報として、複数の制御電圧情報とそれに対応するパルス生成の情報を記憶する電圧・パルス生成の情報テーブルを記憶し、前記レベル検出回路で検出された電圧レベルを最新の制御電圧情報として記憶するメモリと、

前記位相比較器と前記ループフィルタとの接続をオン/オフするスイッチと、

前記レベル検出回路で検出された電圧レベルを入力し、当該電圧レベルを最新の制御電圧情報として前記メモリに記憶されている最新の制御電圧情報を更新すると共に、前記検波回路で検出された外部基準信号のレベルが適正範囲内であれば前記スイッチをオンとし、前記レベルが適正範囲外であれば前記スイッチをオフとして前記メモリに記憶された更新された最新の制御電圧情報を読み取り、当該最新の制御電圧情報に対応するパルス生成の情報を前記電圧・パルス生成の情報テーブルから読み取り、当該パルス生成の情報を前記パルス生成回路に出力する制御部とを有し、

前記パルス生成回路は、パルス幅変調回路であり、前記制御部から出力されるパルス生成の情報は、パルス幅変調デューティーサイクルの情報であることを特徴とする発振周波数制御回路。 - メモリに記憶された制御電圧情報を、電圧制御発振器を制御可能な制御電圧において中心制御電圧の値としたことを特徴とする請求項1記載の発振周波数制御回路。

- メモリには、経年変化の時間に対する適正な制御電圧情報とそれに対応するパルス生成の情報を記憶する経年変化特性テーブルを記憶し、

制御部は、内部にタイマーを備えて時間を計測し、外部基準信号のレベルが適正範囲外であるときに、前記メモリの経年変化特性テーブルから計測した時間に応じた制御電圧情報を検索し、検索した制御電圧情報に対応するパルス生成の情報を読み取り、パルス生成回路に出力することを特徴とする請求項1記載の発振周波数制御回路。 - 電圧制御発振器の代わりに、電圧制御機能付き水晶発振器、温度補償型の水晶発振器又は電圧制御機能付き恒温槽水晶発振器を用いたことを特徴とする請求項1乃至3のいずれか記載の発振周波数制御回路。

- 請求項2記載の発振周波数制御回路を用いた校正方法において、外部基準信号が入力される端子から外部基準信号を入力させない状態とし、周波数偏差が上昇又は下降するタイミングで前記端子から外部基準信号を入力し、その後、外部基準信号の入力を停止することで、制御部が、中心制御電圧の値に従って自走制御し、周波数偏差が中心周波数に戻ってきて校正が為されることを特徴とする発振周波数制御回路の校正方法。

- 請求項3記載の発振周波数制御回路を用いた校正方法において、外部基準信号が入力される端子から外部基準信号を入力させない状態とし、周波数偏差が上昇するタイミングで前記端子から外部基準信号を入力し、その後、外部基準信号の入力を停止することで、制御部が、経年変化特性テーブルを参照し、計測した時間に応じた制御電圧の値に従って自走制御し、周波数偏差が中心周波数に戻ってきて校正が為されることを特徴とする発振周波数制御回路の校正方法。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006349519A JP4374463B2 (ja) | 2006-12-26 | 2006-12-26 | 発振周波数制御回路 |

| PCT/JP2007/071209 WO2008078452A1 (ja) | 2006-12-26 | 2007-10-31 | 発振周波数制御回路 |

| EP07830943A EP2066035B1 (en) | 2006-12-26 | 2007-10-31 | Oscillation frequency control circuit |

| BRPI0717254-0A BRPI0717254A2 (pt) | 2006-12-26 | 2007-10-31 | Circuto de controle de frequência de oscilação |

| CN2007800258242A CN101490960B (zh) | 2006-12-26 | 2007-10-31 | 振荡频率控制电路及其校正方法 |

| KR1020087030507A KR101077730B1 (ko) | 2006-12-26 | 2007-10-31 | 발진 주파수 제어 회로 |

| US12/320,321 US20090134946A1 (en) | 2006-12-26 | 2009-01-23 | Oscillation frequency control circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006349519A JP4374463B2 (ja) | 2006-12-26 | 2006-12-26 | 発振周波数制御回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008160677A JP2008160677A (ja) | 2008-07-10 |

| JP2008160677A5 JP2008160677A5 (ja) | 2008-11-06 |

| JP4374463B2 true JP4374463B2 (ja) | 2009-12-02 |

Family

ID=39562246

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006349519A Active JP4374463B2 (ja) | 2006-12-26 | 2006-12-26 | 発振周波数制御回路 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US20090134946A1 (ja) |

| EP (1) | EP2066035B1 (ja) |

| JP (1) | JP4374463B2 (ja) |

| KR (1) | KR101077730B1 (ja) |

| CN (1) | CN101490960B (ja) |

| BR (1) | BRPI0717254A2 (ja) |

| WO (1) | WO2008078452A1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101651456B (zh) | 2008-08-12 | 2012-03-21 | 博通集成电路(上海)有限公司 | 时钟信号恢复的电路 |

| JP5277919B2 (ja) * | 2008-12-10 | 2013-08-28 | 株式会社Jvcケンウッド | 基準信号発振装置及び基準信号発振方法 |

| JP5198316B2 (ja) * | 2009-02-19 | 2013-05-15 | 富士通セミコンダクター株式会社 | Pll回路及び発振装置 |

| US20100220006A1 (en) * | 2009-02-27 | 2010-09-02 | Amir Arab | Global positioning systems based disciplined reference clock |

| CN101841329A (zh) * | 2010-06-12 | 2010-09-22 | 中兴通讯股份有限公司 | 锁相环、压控装置及方法 |

| CN104467123B (zh) * | 2014-12-31 | 2017-08-08 | 展讯通信(上海)有限公司 | 充电方法、装置、充电器、电子装置及设备 |

| JP2017194789A (ja) * | 2016-04-19 | 2017-10-26 | ローム株式会社 | クロック発生装置、電子回路、集積回路、及び電気機器 |

| JP2018085563A (ja) | 2016-11-21 | 2018-05-31 | ソニーセミコンダクタソリューションズ株式会社 | 発振装置、および発振方法 |

| EP3573241B1 (fr) * | 2018-05-24 | 2022-08-03 | The Swatch Group Research and Development Ltd | Oscillateur de référence à rapport cyclique variable, synthétiseur de fréquence et récepteur de signaux avec l'oscillateur de référence |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01222519A (ja) * | 1988-03-01 | 1989-09-05 | Toyo Commun Equip Co Ltd | 発振回路の制御方式 |

| JPH0450935U (ja) * | 1990-09-06 | 1992-04-28 | ||

| FI91821C (fi) | 1991-02-22 | 1994-08-10 | Nokia Mobile Phones Ltd | Radiopuhelimen automaattinen taajuudensäätökytkentä |

| JPH04369927A (ja) * | 1991-06-19 | 1992-12-22 | Hitachi Ltd | Pll発振器 |

| US5334952A (en) * | 1993-03-29 | 1994-08-02 | Spectralink Corporation | Fast settling phase locked loop |

| JP2581398B2 (ja) * | 1993-07-12 | 1997-02-12 | 日本電気株式会社 | Pll周波数シンセサイザ |

| IL120119A0 (en) | 1997-01-31 | 1997-04-15 | Binder Yehuda | Method and system for calibrating a crystal oscillator |

| US6345079B1 (en) * | 1997-10-29 | 2002-02-05 | Victor Company Of Japan, Ltd. | Clock signal generation apparatus |

| US6313708B1 (en) * | 2000-07-26 | 2001-11-06 | Marconi Communications, Inc. | Analog phase locked loop holdover |

| US6914489B2 (en) * | 2002-09-26 | 2005-07-05 | Koninklijke Philips Electronics N.V. | Voltage-controlled oscillator presetting circuit |

| US7015762B1 (en) * | 2004-08-19 | 2006-03-21 | Nortel Networks Limited | Reference timing signal apparatus and method |

| JP2006121171A (ja) * | 2004-10-19 | 2006-05-11 | Matsushita Electric Ind Co Ltd | 周波数補正機能付きクロック供給装置 |

| JP4569572B2 (ja) * | 2004-12-17 | 2010-10-27 | 三菱電機株式会社 | クロック信号生成装置および無線基地局 |

| JP4424546B2 (ja) * | 2005-01-13 | 2010-03-03 | Okiセミコンダクタ株式会社 | パルス幅変調回路 |

| JP4625494B2 (ja) * | 2007-12-25 | 2011-02-02 | 日本電波工業株式会社 | 発振周波数制御回路 |

-

2006

- 2006-12-26 JP JP2006349519A patent/JP4374463B2/ja active Active

-

2007

- 2007-10-31 WO PCT/JP2007/071209 patent/WO2008078452A1/ja active Application Filing

- 2007-10-31 BR BRPI0717254-0A patent/BRPI0717254A2/pt not_active IP Right Cessation

- 2007-10-31 CN CN2007800258242A patent/CN101490960B/zh active Active

- 2007-10-31 KR KR1020087030507A patent/KR101077730B1/ko not_active IP Right Cessation

- 2007-10-31 EP EP07830943A patent/EP2066035B1/en active Active

-

2009

- 2009-01-23 US US12/320,321 patent/US20090134946A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| CN101490960A (zh) | 2009-07-22 |

| EP2066035A4 (en) | 2010-09-29 |

| KR20090026146A (ko) | 2009-03-11 |

| WO2008078452A1 (ja) | 2008-07-03 |

| EP2066035A1 (en) | 2009-06-03 |

| US20090134946A1 (en) | 2009-05-28 |

| BRPI0717254A2 (pt) | 2013-10-08 |

| EP2066035B1 (en) | 2012-09-12 |

| KR101077730B1 (ko) | 2011-10-27 |

| CN101490960B (zh) | 2013-01-02 |

| JP2008160677A (ja) | 2008-07-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4625494B2 (ja) | 発振周波数制御回路 | |

| JP4374463B2 (ja) | 発振周波数制御回路 | |

| US7332979B2 (en) | Low noise reference oscillator with fast start-up | |

| US8248113B2 (en) | Method and apparatus for accurate clock synthesis | |

| JP4355350B2 (ja) | 発振周波数制御回路 | |

| US8698568B2 (en) | Automatic self-calibrated oscillation method and apparatus using the same | |

| US8766736B2 (en) | Methods of frequency versus temperature compensation of existing crystal oscillators | |

| KR101515099B1 (ko) | 전하펌프, 전하펌프 보정 장치 및 이를 포함한 위상 동기 루프 | |

| JP5145398B2 (ja) | 発振周波数制御回路 | |

| US7151414B2 (en) | Method and circuit for frequency synthesis using a low drift current controlled oscillator with wide output frequency range | |

| JP5027265B2 (ja) | Pll装置 | |

| JP5426316B2 (ja) | 周波数シンセサイザ | |

| JP2011040967A (ja) | Pll回路 | |

| US11829198B2 (en) | Clock circuit portions | |

| JP5063833B2 (ja) | 時計の時間基準による高周波信号発生器 | |

| US20060034409A1 (en) | Digital vco and pll circuit using the digital vco | |

| JP2000323987A (ja) | Pll回路 | |

| JP2004172686A (ja) | 基準信号発生器 | |

| JPH1065528A (ja) | Pll回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080919 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080919 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20080919 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20081003 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081125 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090123 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090421 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090618 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090818 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090820 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4374463 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120918 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120918 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120918 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130918 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |