JP4366183B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4366183B2 JP4366183B2 JP2003419290A JP2003419290A JP4366183B2 JP 4366183 B2 JP4366183 B2 JP 4366183B2 JP 2003419290 A JP2003419290 A JP 2003419290A JP 2003419290 A JP2003419290 A JP 2003419290A JP 4366183 B2 JP4366183 B2 JP 4366183B2

- Authority

- JP

- Japan

- Prior art keywords

- gas

- chlorine

- silicon

- supplying

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Chemical Vapour Deposition (AREA)

Description

そのために特許文献1ではシリコン層上に付着した塩素もしくはフッ素を、ジシランもしくはモノゲルマンを使用して取り除いているが、このとき、シリコン窒化膜もしくはシリコン酸化膜上にも、ジシランもしくはモノゲルマンが供給される。シリコン窒化膜上もしくはシリコン酸化膜上では、シリコン膜の成長に対する塩素もしくはフッ素の影響がない。したがって、シリコン層上に付着した塩素もしくはフッ素を取り除いている間に、シリコン窒化膜上もしくはシリコン酸化膜上にもシリコン膜が成長するため、シリコン層上のみに選択成長させるという選択性が破れ易い。このため、特許文献1では選択性の低下を引き起こすという問題がある。

これによれば、塩素ガスもしくはフッ素ガスの供給後に、H2ガスを供給して絶縁層表面を非活性化させることにより、選択性の低下を防止できる。したがって、特許文献1での選択性の低下を抑制することが可能である。

第5ステップは成長温度を500℃より低くするとスループットが悪くなり実用的でない。また、成長温度を700℃より高い温度とすると、インキュベーションタイムが短くなり、選択性が悪くなる。したがって、スループットおよび選択性がともに良好になる500〜700℃がよく、好ましくは500〜650℃がよい。

第4ステップで供給するガスがH2であると、H2は、単独では成膜に寄与せず、成膜を生じないので最も好ましい。

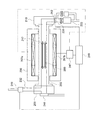

まず、図7を参照して、本発明の半導体装置の製造方法を実施するための二枚葉基板処理装置を構成する処理炉の概略を説明する。

ここではウェハ支持台217には2枚のウェハ200が載置され、2枚のウェハ200が同時に処理される。なお、同時に処理する2枚のウェハ200の熱履歴を等しくするためにウェハ200は2枚同時に反応管203内に搬送される。ウェハ200が反応管203内に搬入されると同時にウェハ200の処理温度までの昇温が開始される(プレヒート)。

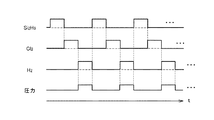

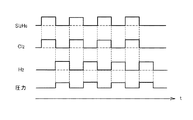

また、水素系ガス供給ステップでの反応管203内の圧力を、原料ガス供給ステップまたは塩素系ガス等供給ステップでの反応管203内圧力よりも大きくする。この圧力制御は圧力制御手段242によって行われる。

したがって、実施形態をMOSFETに適用すれば、そのソース/ドレインのリーク電流の低減化、および低抵抗化を実現でき、半導体デバイス特性の向上と微細化を両立できる。

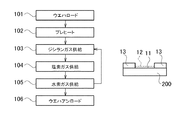

この時のプロセスシーケンス例を図1に示す。表面の一部に絶縁層13を有すると共にポリシリコン層11が露出したシリコンウェハ200を、図示しないウェハ搬送ロボットにより反応管203内にロードする(ステップ101)。

シリコンウェハ200が反応管203内に搬入されると、主制御部249下で制御される温度制御手段247によって上ヒータ207a、下ヒータ207bが制御されて、搬入と同時にウェハ200の処理温度までプレヒートする(ステップ102)。

ジシランガス供給後、主制御部249で流量制御手段241を制御して、反応管203内に所定流量の塩素ガスCl2を供給する(ステップ104)。

塩素ガス供給後、主制御部249で流量制御手段241を制御して、反応管203内に所定流量の水素ガスH2を供給する(ステップ105)。

図2に、上述した各種ガスの導入および圧力制御タイミング図を示す。

(a)Si2H6供給ステップ

図3(a)に示すように、露出したシリコン層11の表面にエピタキシャル膜12が成長する。絶縁層13上には膜は形成されないが、Si結晶核14が形成される。

図3(b)に示すように、絶縁層13上のSi結晶核14がCl2もしくはF215と反応して除去される。反応式を示せば次の通りである。

2Cl2+Si→SiCl4

2F2+Si→SiF4

その際エピタキシャル膜12、絶縁層13上にClもしくはFが付着する。

図3(c)に示すように、エピタキシャル膜12、絶縁層13上に付着したClもしくはFがH2と反応して除去される。反応式を示せば次の通りである。

H2+2Cl→2HCl

H2+2F→2HF

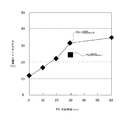

図4に、ポリシリコン層上でのエピタキシャル膜厚と塩素ガス供給後における水素ガス供給時間の依存性を示している。水素ガス供給は塩素ガス供給後に行っている。縦軸にはシリコンエピタキシャル膜厚を、横軸には塩素ガス供給後における水素供給時間をそれぞれとっている。

同図に示すように、塩素ガス供給後、水素ガスを供給しない場合には(H2ガス供給時間が0sec時参照)、シリコンエピタキシャル膜厚は薄いが、塩素ガス導入後に水素ガスを導入するとシリコンエピタキシャル膜厚は厚くなり、水素ガス流量および供給時間を増加させると、より厚いシリコンエピタキシャル膜が得られることがわかる。

(a)温度は、500〜700℃、好ましくは500〜650℃である。

500℃より低くするとスループットが悪くなり実用的ではない。

700℃より高い温度とするとインキュベーションタイムが短くなり、選択性が悪くなる。

H2供給時の圧力を0.1Paより低くするとH2とCl,Fとの反応速度が遅くなりスループットが低下する。安全性を考慮すると1000Pa以下とするのが好ましい。

実施例1では、H2供給時の圧力が、Si2H6,Cl2もしくはF2供給時の圧力よりも高くなるよう制御している。これは、H2供給時におけるH2と、ClもしくはFとの反応速度を上げるためであり、シリコン表面に付着したClもしくはFを素早く除去するためである。

特に近年、低温化の要請があるが、低温化に伴い絶縁層上でのインキュベーションタイムが長くなり選択性は向上するものの、成膜速度が低下する。その場合であっても、H2供給時の雰囲気を高圧にすることで、ClもしくはFの除去速度を上げることができ、その結果、スループットを向上させることができる。H2供給時の雰囲気を高圧にするには、例えば、大流量のH2を供給することにより行う。

具体的には、Si2H6ガスの供給時間を長くしたり、処理温度を高くしたりすることで、図6に示すように、シリコン層11上にエピタキシャル膜12を成長させると同時に、絶縁層13上にポリシリコン膜16を成長させることができる。

12 エピタキシャル膜

13 絶縁層

200 ウェハ

Claims (3)

- 表面の一部に絶縁層を有すると共にシリコン層が露出した基板を処理室内に搬入する第1ステップと、

前記処理室内にシラン系ガスを含む原料ガスを供給する第2ステップと、

前記処理室内に塩素系ガスもしくはフッ素系ガスを供給する第3ステップと、

前記処理室内に水素系ガスを供給する第4ステップと、

前記第2ステップと前記第3ステップと前記第4ステップとを順に複数回繰り返して前記露出したシリコン層上に膜を成長させる第5ステップとを有し、

前記第4ステップでの処理室内の圧力を、前記第2ステップまたは前記第3ステップでの処理室内圧力よりも大きくすることを特徴とする半導体装置の製造方法。 - 前記第5ステップは成長温度を500〜700℃として行うことを特徴とする請求項第1に記載の半導体装置の製造方法。

- 前記第2ステップで供給するガスはSiH4、Si2H6,SiH4およびGeH4、Si2H6およびGeH4からなる群から選択される少なくとも一つのガスであり、前記第3ステップで供給するガスはCl2,HCl,F2からなる群から選択される少なくとも一つのガスであり、前記第4ステップで供給するガスはH2であることを特徴とする請求項1に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003419290A JP4366183B2 (ja) | 2003-12-17 | 2003-12-17 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003419290A JP4366183B2 (ja) | 2003-12-17 | 2003-12-17 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005183514A JP2005183514A (ja) | 2005-07-07 |

| JP4366183B2 true JP4366183B2 (ja) | 2009-11-18 |

Family

ID=34781228

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003419290A Expired - Lifetime JP4366183B2 (ja) | 2003-12-17 | 2003-12-17 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4366183B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8466049B2 (en) * | 2005-07-29 | 2013-06-18 | Hitachi Kokusai Electric Inc. | Semiconductor device producing method with selective epitaxial growth |

| JP4832022B2 (ja) * | 2005-07-29 | 2011-12-07 | 株式会社日立国際電気 | 基板処理装置 |

| US7358194B2 (en) * | 2005-08-18 | 2008-04-15 | Tokyo Electron Limited | Sequential deposition process for forming Si-containing films |

| JP2008034462A (ja) * | 2006-07-26 | 2008-02-14 | Hitachi Kokusai Electric Inc | 基板処理装置 |

| KR100850120B1 (ko) | 2006-12-26 | 2008-08-04 | 동부일렉트로닉스 주식회사 | Soi웨이퍼 및 제조방법 |

| US9064960B2 (en) | 2007-01-31 | 2015-06-23 | Applied Materials, Inc. | Selective epitaxy process control |

| US8030147B2 (en) * | 2007-09-14 | 2011-10-04 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film transistor and display device including the thin film transistor |

| JP2010092979A (ja) * | 2008-10-06 | 2010-04-22 | Hitachi Kokusai Electric Inc | 半導体装置の製造方法 |

| US8012859B1 (en) * | 2010-03-31 | 2011-09-06 | Tokyo Electron Limited | Atomic layer deposition of silicon and silicon-containing films |

| WO2012029661A1 (ja) | 2010-09-01 | 2012-03-08 | 株式会社日立国際電気 | 半導体装置の製造方法及び基板処理装置 |

| JP6554438B2 (ja) * | 2016-03-30 | 2019-07-31 | 東京エレクトロン株式会社 | シリコン膜の形成方法および形成装置 |

| JP2019129161A (ja) * | 2018-01-19 | 2019-08-01 | 東京エレクトロン株式会社 | 基板処理方法と基板処理システム |

| JP7221187B2 (ja) * | 2019-09-30 | 2023-02-13 | 東京エレクトロン株式会社 | 成膜方法、及び成膜装置 |

| JP7065818B2 (ja) * | 2019-10-28 | 2022-05-12 | 株式会社Kokusai Electric | 半導体装置の製造方法、基板処理方法、基板処理装置、およびプログラム |

| JP7313402B2 (ja) | 2021-06-29 | 2023-07-24 | 株式会社Kokusai Electric | 半導体装置の製造方法、基板処理装置、プログラム及びエッチング方法 |

-

2003

- 2003-12-17 JP JP2003419290A patent/JP4366183B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005183514A (ja) | 2005-07-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4366183B2 (ja) | 半導体装置の製造方法 | |

| US9666430B2 (en) | Method of manufacturing semiconductor device and substrate processing apparatus | |

| TW202200823A (zh) | 半導體裝置之製造方法、基板處理方法、基板處理裝置及程式 | |

| KR100996689B1 (ko) | 반도체장치의 제조방법, 막생성방법 및 기판처리장치 | |

| US11788185B2 (en) | Film formation method and film formation device | |

| US10529560B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus and recording medium | |

| US11114297B2 (en) | Method for forming semiconductor film and film forming device | |

| JP4490760B2 (ja) | 半導体装置の製造方法及び基板処理装置 | |

| TWI837765B (zh) | 基板處理方法、半導體裝置之製造方法、程式及基板處理裝置 | |

| US8790463B2 (en) | Substrate processing apparatus and semiconductor device producing method | |

| KR102751818B1 (ko) | 고 종횡비 구조들을 세정하기 위한 방법들 및 시스템들 | |

| JP2007305730A (ja) | 半導体装置の製造方法 | |

| JPH09199424A (ja) | エピタキシャル成長方法 | |

| US12571125B2 (en) | Method for forming polycrystalline silicon film | |

| KR102935311B1 (ko) | 아몰퍼스 실리콘막의 결정화 방법 및 성막 장치 | |

| JP2006351582A (ja) | 半導体装置の製造方法及び基板処理装置 | |

| CN109891555B (zh) | 低温外延层形成方法 | |

| US20230307225A1 (en) | Method of processing substrate, method of manufacturing semiconductor device, recording medium, and substrate processing apparatus | |

| JP2005294690A (ja) | 半導体装置の製造方法及び基板処理装置 | |

| JPH06302566A (ja) | 半導体装置の製造方法および製造装置 | |

| JP2022087143A (ja) | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム | |

| JP2005243924A (ja) | 基板処理装置 | |

| JP2005268699A (ja) | 半導体装置の製造方法 | |

| WO2024062634A1 (ja) | 基板処理方法、半導体装置の製造方法、基板処理装置およびプログラム | |

| JP2022056735A (ja) | 半導体装置の製造方法、基板処理装置、およびプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090331 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090811 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090824 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120828 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4366183 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130828 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140828 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |