JP7313402B2 - 半導体装置の製造方法、基板処理装置、プログラム及びエッチング方法 - Google Patents

半導体装置の製造方法、基板処理装置、プログラム及びエッチング方法 Download PDFInfo

- Publication number

- JP7313402B2 JP7313402B2 JP2021107284A JP2021107284A JP7313402B2 JP 7313402 B2 JP7313402 B2 JP 7313402B2 JP 2021107284 A JP2021107284 A JP 2021107284A JP 2021107284 A JP2021107284 A JP 2021107284A JP 7313402 B2 JP7313402 B2 JP 7313402B2

- Authority

- JP

- Japan

- Prior art keywords

- gas

- film

- substrate

- group

- etching method

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/60—Wet etching

- H10P50/64—Wet etching of semiconductor materials

- H10P50/642—Chemical etching

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/24—Dry etching; Plasma etching; Reactive-ion etching of semiconductor materials

- H10P50/242—Dry etching; Plasma etching; Reactive-ion etching of semiconductor materials of Group IV materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/20—Dry etching; Plasma etching; Reactive-ion etching

- H10P50/26—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials

- H10P50/264—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means

- H10P50/266—Dry etching; Plasma etching; Reactive-ion etching of conductive or resistive materials by chemical means by vapour etching only

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/04—Apparatus for manufacture or treatment

- H10P72/0402—Apparatus for fluid treatment

- H10P72/0418—Apparatus for fluid treatment for etching

- H10P72/0421—Apparatus for fluid treatment for etching for drying etching

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Plasma & Fusion (AREA)

- Drying Of Semiconductors (AREA)

Description

(a)処理容器内に配置され、第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する工程と、

(b)(a)の後にハロゲンを含む第2ガスを供給する工程と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする工程と、

を有する技術が提供される。

基板処理装置10は、加熱手段(加熱機構、加熱系)としてのヒータ207が設けられた処理炉202を備える。ヒータ207は円筒形状であり、保持板としてのヒータベース(図示せず)に支持されることにより垂直に据え付けられている。

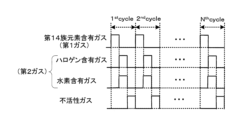

半導体装置(デバイス)の製造工程の一工程として、ウエハ200に形成されたシリコン(Si)等の第14族元素を含む第14族元素含有膜をエッチングする工程(エッチング方法)の一例について、図4及び図5(A)~図5(D)を用いて説明する。本工程は、上述した基板処理装置10の処理炉202を用いて実行される。以下の説明において、基板処理装置10を構成する各部の動作はコントローラ121により制御可能に構成される。

(a)処理容器内に配置され、第14族元素を含む膜が形成されたウエハ200に、第14族元素を含む第1ガスを、ウエハ200に形成された膜に含まれる第14族元素との反応により生じる反応副生成物がウエハ200に飽和吸着するように供給する工程と、

(b)(a)の後にハロゲンを含む第2ガスを供給する工程と、

(c)(a)と(b)を交互に繰り返し行うことにより、ウエハ200に形成された第14族元素を含む膜をエッチングする工程と、

を有する。

複数枚のウエハ200がボート217に装填(ウエハチャージ)されると、図1に示されているように、複数枚のウエハ200を支持したボート217は、ボートエレベータ115によって持ち上げられて処理室201内に搬入(ボートロード)され、処理容器内に配置される。この状態で、シールキャップ219はOリング220を介してアウタチューブ203の下端開口を閉塞した状態となる。

処理室201内、すなわち、ウエハ200が存在する空間が所望の圧力(真空度)となるように真空ポンプ246によって真空排気される。この際、処理室201内の圧力は、圧力センサ245で測定され、この測定された圧力情報に基づき、APCバルブ243がフィードバック制御される(圧力調整)。真空ポンプ246は、少なくともウエハ200に対する処理が完了するまでの間は常時作動させた状態を維持する。また、処理室201内が所望の温度となるようにヒータ207によって加熱される。この際、処理室201内が所望の温度分布となるように、温度センサ263が検出した温度情報に基づきヒータ207への通電量がフィードバック制御される(温度調整)。ヒータ207による処理室201内の加熱は、少なくともウエハ200に対する処理が完了するまでの間は継続して行われる。

バルブ314を開き、ガス供給管310内に第1ガスを流す。第1ガスは、MFC312により流量調整され、ノズル410のガス供給孔410aから処理室201内に供給され、排気管231から排気される。

第1ガスの供給を開始してから所定時間経過後に、バルブ314を閉じて、第1ガスの処理室201内への供給を停止する。このときバルブ324,344を開き、ガス供給管320内に、ハロゲン含有ガスと水素含有ガスを同時に流す。つまり、第1ガスの供給後にパージガスを供給しないで第2ガスの供給を開始する。

第2ガスの供給を開始してから所定時間経過後であって例えば1~30秒後にバルブ324,344を閉じ、第2ガスの供給を停止する。このとき、排気管231のAPCバルブ243は開いたままとして、真空ポンプ246により処理室201内を真空排気し、ウエハ200上から残留ガスを除去して、処理室201内に残留する未反応の第2ガスや反応副生成物を処理室201内から排除する。このとき、バルブ514,524,534を開き、パージガスとしての不活性ガスを処理室201内へ供給し、処理容器内をパージする。不活性ガスはパージガスとして作用し、ウエハ200上から残留ガスを除去して、処理室201内に残留する未反応の第2ガスや反応副生成物を処理室201内から排除する効果を高めることができる。MFC512,522,532で制御する不活性ガスの供給流量は、それぞれ例えば0.1~2.0slmとする。

上述した第1ステップ~第3ステップを順に行うサイクルを所定回数(N回)、1回以上実行することにより、ウエハ200に形成された第14族元素を含む膜がエッチングされる。すなわち、第1ステップ~第3ステップを交互に繰り返し行うことにより、ウエハ200に形成された第14族元素を含む膜をエッチングすることができる。

ガス供給管510~530のそれぞれから不活性ガスを処理室201内へ供給し、排気管231から排気する。不活性ガスはパージガスとして作用し、これにより処理室201内が不活性ガスでパージされ、処理室201内に残留するガスや反応副生成物が処理室201内から除去される(アフターパージ)。その後、処理室201内の雰囲気が不活性ガスに置換され(不活性ガス置換)、処理室201内の圧力が常圧に復帰される(大気圧復帰)。

その後、ボートエレベータ115によりシールキャップ219が下降されて、アウタチューブ203の下端が開口される。そして、処理済ウエハ200がボート217に支持された状態でアウタチューブ203の下端からアウタチューブ203の外部に搬出(ボートアンロード)される。その後、処理済のウエハ200は、ボート217より取り出される(ウエハディスチャージ)。

本実施形態によれば、以下に示す1つまたは複数の効果を得ることができる。

(a)第14族元素を含む膜のエッチングの制御性を向上させることができる。

(b)第14族元素を含む膜の微細加工を行うことができる。

以上、本開示の実施形態を具体的に説明した。しかしながら、本開示は上述の実施形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

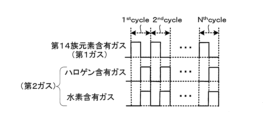

図6は、本開示の一実施形態における基板処理シーケンスの変形例を示す。

本変形例では、上述した第1ステップと第2ステップを順に行うサイクルを所定回数(N回)、1回以上実行することにより、ウエハ200に形成された第14族元素含有膜をエッチングする。すなわち、上述した第3ステップのパージを行わない。この場合であっても、第14族元素を含む膜をエッチングすることができる。

図7は、本開示の一実施形態における基板処理シーケンスの変形例を示す。

本変形例では、上述した第1ステップ~第3ステップを順に行うサイクルを所定回数(N回)行った後に、酸素含有ガス供給系から酸素含有ガスを供給する。そして、不活性ガス(パージガス)を供給した後、第1ステップ~第3ステップを順に行うサイクルを所定回数(M回)行う。すなわち、上述した第1ステップ~第3ステップを繰り返し行う途中で、酸素含有ガスを供給して、表面を酸化させる。これにより、エッチングの途中でウエハ200表面が酸化され、過剰なエッチングを抑制することができる。また、エッチング量(エッチング膜厚)を調整することができ、エッチングの制御性を高めることができる。

図8(A)及び図8(B)は、本開示の一実施形態における基板処理シーケンスの変形例を示す。

本変形例では、図8(A)に示すように、上述した第1ステップにおける第1ガスとして、第14族元素含有ガスに加えて水素含有ガスを供給する。すなわち、上述した第1ステップにおける第14族元素含有ガス供給と並行して、水素含有ガスを供給する。そして、第2ステップにおける第2ガスとしてハロゲン含有ガスを供給する。すなわち、第2ステップでは、水素含有ガスを供給しない。

次に、エッチング対象である第14族元素を含む膜を、所定元素であるリン(P)がドープされたドープSi膜と、PがドープされていないノンドープSi膜とし、ドープSi膜とノンドープSi膜が表面に形成されたウエハ200に対して、上述した第1ステップ~第3ステップを行った場合の、上述したエッチングの効果について説明する。

次に、エッチング対象である第14族元素を含む膜を、単結晶Si膜又は多結晶Si膜である結晶性Si膜と、アモルファスSi膜である非結晶性Si膜とし、結晶性Si膜と非結晶性Si膜が表面に形成されたウエハ200に対して、上述した第1ステップ~第3ステップを行った場合の、上述したエッチングの効果について説明する。

次に、エッチング対象である第14族元素を含む膜を、酸化膜であるシリコン酸化(SiO2)膜と、非酸化膜であるSi膜とし、SiO2膜とSi膜が表面に形成されたウエハ200に対して、上述した第1ステップ~第3ステップを行った場合の、上述したエッチングの効果について説明する。

次に、エッチング対象である第14族元素を含む膜を、窒化膜であるSiN膜と、非窒化膜であるSi膜とし、SiN膜とSi膜が表面に形成されたウエハ200に対して、上述した第1ステップ~第3ステップを行った場合の、上述したエッチングの効果について説明する。

次に、エッチング対象である第14族元素を含む膜を、非酸化膜であるSi膜とし、酸化膜であるSiO2膜の上に非酸化膜であるSi膜が形成された積層膜が形成されたウエハ200に対して、上述した第1ステップ~第3ステップを行った場合の、上述したエッチングの効果について説明する。

以下に、本開示の好ましい態様について付記する。

本開示の一態様によれば、

(a)処理容器内に配置され、第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する工程と、

(b)(a)の後にハロゲンを含む第2ガスを供給する工程と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする工程と、

を有する半導体装置の製造方法が提供される。

付記1に記載の方法であって、

(a)では、前記第1ガスが分解する雰囲気下で、前記第1ガスを供給する。

付記1又は2に記載の方法であって、

(b)では、前記第2ガスが分解しない雰囲気下で、前記第2ガスを供給する。

付記1から3のいずれか記載の方法であって、

(d)(c)では、(b)の後に前記処理容器内をパージする工程をさらに有する。

付記1から3のいずれか記載の方法であって、

(d)(c)では、(b)の後に前記処理容器内をパージする工程を有さない。

付記1から5のいずれか記載の方法であって、

(a)と(b)の間でパージを行わない。

付記1から6のいずれか記載の方法であって、

前記第14族元素は、シリコンであり、

前記第1ガスは、シラン系ガス又はクロロシラン系ガスである。

付記1から6のいずれか記載の方法であって、

前記第14族元素は、シリコンであり、

前記第1ガスは、クロロシラン系ガスである。

付記8に記載の方法であって、

前記クロロシラン系ガスは、ジクロロシラン、ヘキサクロロジシラン、四塩化ケイ素の少なくとも1つ以上を含むガスである。

付記1から9のいずれか記載の方法であって、

前記ハロゲンは、塩素を含むガスである。

付記10に記載の方法であって、

前記第2ガスは、塩素ガス、塩化水素ガス、三塩化ホウ素ガス、四塩化ケイ素ガス、モノシランガスと塩素ガスの混合ガスの少なくとも1つ以上である。

付記1から11のいずれか記載の方法であって、

前記第14族元素を含む膜は、シリコンを主成分とする膜である。

付記1から12のいずれか記載の方法であって、

前記基板の表面には、所定元素がドープされたシリコン膜と、所定元素がドープされていないシリコン膜が形成され、

(c)では、前記所定元素がドープされていないシリコン膜をエッチングする。

付記1から8のいずれか記載の方法であって、

前記基板の表面には、結晶性シリコン膜と、非結晶性シリコン膜が形成され、

(c)では、前記結晶性シリコン膜と、前記非結晶性シリコン膜との両方をエッチングする。

付記1から14のいずれか記載の方法であって、

前記基板の表面には、酸化膜と、非酸化膜が形成され、

(c)では、前記非酸化膜をエッチングする。

付記1から15のいずれか記載の方法であって、

前記基板の表面には、窒化膜と、非窒化膜が形成され、

(c)では、前記非窒化膜をエッチングする。

付記1から16のいずれか記載の方法であって、

(d)(c)の途中で、酸素含有ガスを供給する。

本開示の他の態様によれば、

処理容器内の第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスと、ハロゲンを含む第2ガスと、を供給するガス供給系と、

(a)前記基板に前記第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する処理と、

(b)(a)の後に前記基板に前記第2ガスを供給する処理と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする処理と、を行わせるように、前記ガス供給系を制御することが可能なように構成される制御部と、

を有する基板処理装置が提供される。

本開示のさらに他の態様によれば、

(a)基板処理装置の処理容器内に配置され、第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する手順と、

(b)(a)の後にハロゲンを含む第2ガスを供給する手順と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする手順と、

をコンピュータによって前記基板処理装置に実行させるプログラムが提供される。

本開示のさらに他の態様によれば、

(a)処理容器内に配置され、第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する工程と、

(b)(a)の後にハロゲンを含む第2ガスを供給する工程と、を有し、

(a)と(b)をこの順序で所定回数行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする

エッチング方法が提供される。

121 コントローラ

200 ウエハ(基板)

201 処理室

Claims (20)

- (a)第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する工程と、

(b)(a)の後にハロゲンを含む第2ガスを供給する工程と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする工程と、

を有するエッチング方法。 - (a)では、前記第1ガスが分解する雰囲気下で、前記第1ガスを供給する請求項1記載のエッチング方法。

- (b)では、前記第2ガスが分解しない雰囲気下で、前記第2ガスを供給する請求項1又は2に記載のエッチング方法。

- (d)(c)では、(b)の後に前記基板が配置される処理容器内をパージする工程をさらに有する請求項1から3のいずれか一項に記載のエッチング方法。

- (d)(c)では、(b)の後に前記基板が配置される処理容器内をパージする工程を有さない請求項1から3のいずれか一項に記載のエッチング方法。

- (a)と(b)の間でパージを行わない請求項1から5のいずれか一項に記載のエッチング方法。

- 前記第14族元素は、シリコンであり、

前記第1ガスは、シラン系ガス又はクロロシラン系ガスである

請求項1から6のいずれか一項に記載のエッチング方法。 - 前記第14族元素は、シリコンであり、

前記第1ガスは、クロロシラン系ガスである

請求項1から6のいずれか一項に記載のエッチング方法。 - 前記クロロシラン系ガスは、ジクロロシラン、ヘキサクロロジシラン、四塩化ケイ素の少なくとも1つ以上を含むガスである請求項8に記載のエッチング方法。

- 前記ハロゲンは、塩素である請求項1から9のいずれか一項に記載のエッチング方法。

- 前記第2ガスは、塩素ガス、塩化水素ガス、三塩化ホウ素ガス、四塩化ケイ素ガス、モノシランガスと塩素ガスの混合ガスの少なくとも1つ以上である請求項1から9のいずれか一項に記載のエッチング方法。

- 前記第14族元素を含む膜は、シリコンを主成分とする膜である請求項1から11のいずれか一項に記載のエッチング方法。

- 前記第14族元素を含む膜が形成された基板は、所定元素がドープされたシリコン膜と、所定元素がドープされていないシリコン膜が表面に形成された基板であり、

(c)では、前記所定元素がドープされていないシリコン膜をエッチングする

請求項1から12のいずれか一項に記載のエッチング方法。 - 前記第14族元素を含む膜が形成された基板は、結晶性シリコン膜と、非結晶性シリコン膜が表面に形成された基板であり、

(c)では、前記結晶性シリコン膜と、前記非結晶性シリコン膜との両方をエッチングする

請求項1から8のいずれか一項に記載のエッチング方法。 - 前記第14族元素を含む膜が形成された基板は、酸化膜と、非酸化膜が表面に形成された基板であり、

(c)では、前記非酸化膜をエッチングする

請求項1から12のいずれか一項に記載のエッチング方法。 - 前記第14族元素を含む膜が形成された基板は、窒化膜と、非窒化膜が表面に形成された基板であり、

(c)では、前記非窒化膜をエッチングする

請求項1から12のいずれか一項に記載のエッチング方法。 - (d)(c)の途中で、酸素含有ガスを供給する請求項1から16のいずれか一項に記載のエッチング方法。

- (a)第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応

により生じる反応副生成物が前記基板に飽和吸着するように供給する工程と、

(b)(a)の後にハロゲンを含む第2ガスを供給する工程と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする工程と、

を有する半導体装置の製造方法。 - 第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスと、ハロゲンを含む第2ガスと、を供給するガス供給系と、

(a)前記基板に前記第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する処理と、

(b)(a)の後に前記基板に前記第2ガスを供給する処理と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする処理と、を行わせるように、前記ガス供給系を制御することが可能なように構成される制御部と、

を有する基板処理装置。 - (a)第14族元素を含む膜が形成された基板に、前記第14族元素を含む第1ガスを、前記基板に形成された膜に含まれる前記第14族元素との反応により生じる反応副生成物が前記基板に飽和吸着するように供給する手順と、

(b)(a)の後にハロゲンを含む第2ガスを供給する手順と、

(c)(a)と(b)を交互に繰り返し行うことにより、前記基板に形成された前記第14族元素を含む膜をエッチングする手順と、

をコンピュータによって基板処理装置に実行させるプログラム。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021107284A JP7313402B2 (ja) | 2021-06-29 | 2021-06-29 | 半導体装置の製造方法、基板処理装置、プログラム及びエッチング方法 |

| TW111113973A TWI892000B (zh) | 2021-06-29 | 2022-04-13 | 基板處理方法、基板處理裝置、程式及半導體裝置的製造方法 |

| CN202210523752.0A CN115547822A (zh) | 2021-06-29 | 2022-05-13 | 衬底处理方法、衬底处理装置、记录介质及半导体器件的制造方法 |

| EP22175744.6A EP4117023A1 (en) | 2021-06-29 | 2022-05-27 | Method of processing substrate, substrate processing apparatus, and recording medium |

| KR1020220065314A KR102754079B1 (ko) | 2021-06-29 | 2022-05-27 | 기판 처리 방법, 기판 처리 장치, 프로그램 및 반도체 장치의 제조 방법 |

| US17/826,332 US12255072B2 (en) | 2021-06-29 | 2022-05-27 | Method of processing substrate, substrate processing apparatus, recording medium, and method of manufacturing semiconductor device |

| KR1020250002842A KR20250010734A (ko) | 2021-06-29 | 2025-01-08 | 기판 처리 방법, 기판 처리 장치, 프로그램 및 반도체 장치의 제조 방법 |

| US19/081,283 US20250218786A1 (en) | 2021-06-29 | 2025-03-17 | Method of processing substrate, substrate processing apparatus, recording medium, and method of manufacturing semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021107284A JP7313402B2 (ja) | 2021-06-29 | 2021-06-29 | 半導体装置の製造方法、基板処理装置、プログラム及びエッチング方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2023005410A JP2023005410A (ja) | 2023-01-18 |

| JP7313402B2 true JP7313402B2 (ja) | 2023-07-24 |

Family

ID=81851696

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021107284A Active JP7313402B2 (ja) | 2021-06-29 | 2021-06-29 | 半導体装置の製造方法、基板処理装置、プログラム及びエッチング方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US12255072B2 (ja) |

| EP (1) | EP4117023A1 (ja) |

| JP (1) | JP7313402B2 (ja) |

| KR (2) | KR102754079B1 (ja) |

| CN (1) | CN115547822A (ja) |

| TW (1) | TWI892000B (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2025006544A (ja) * | 2023-06-29 | 2025-01-17 | 株式会社Kokusai Electric | 基板処理方法、半導体装置の製造方法、プログラム及び基板処理装置 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7174016B2 (ja) | 2020-07-16 | 2022-11-17 | 株式会社Kokusai Electric | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61278146A (ja) * | 1985-06-03 | 1986-12-09 | Toshiba Corp | 光処理方法 |

| JP2918892B2 (ja) | 1988-10-14 | 1999-07-12 | 株式会社日立製作所 | プラズマエッチング処理方法 |

| JPH07104571B2 (ja) * | 1990-02-05 | 1995-11-13 | 松下電器産業株式会社 | 光記録媒体の製造方法 |

| KR0157536B1 (ko) | 1994-11-18 | 1998-12-01 | 모리시다 요이치 | 드라이 에칭 방법 |

| JP3233835B2 (ja) | 1994-11-18 | 2001-12-04 | 松下電器産業株式会社 | ドライエッチング方法 |

| JP3444327B2 (ja) * | 1996-03-04 | 2003-09-08 | 信越半導体株式会社 | シリコン単結晶薄膜の製造方法 |

| KR100373853B1 (ko) | 2000-08-11 | 2003-02-26 | 삼성전자주식회사 | 반도체소자의 선택적 에피택시얼 성장 방법 |

| JP4366183B2 (ja) | 2003-12-17 | 2009-11-18 | 株式会社日立国際電気 | 半導体装置の製造方法 |

| KR100593736B1 (ko) * | 2004-06-17 | 2006-06-28 | 삼성전자주식회사 | 단결정 반도체 상에 선택적으로 에피택시얼 반도체층을형성하는 방법들 및 이를 사용하여 제조된 반도체 소자들 |

| KR100707983B1 (ko) | 2005-11-28 | 2007-04-16 | 주식회사 에이이티 | 산화막의 원자층 에칭방법 |

| JP4464949B2 (ja) | 2006-11-10 | 2010-05-19 | 株式会社日立国際電気 | 基板処理装置及び選択エピタキシャル膜成長方法 |

| JP5018156B2 (ja) * | 2007-03-19 | 2012-09-05 | Jnc株式会社 | 多結晶シリコンの製造方法 |

| JP2010189693A (ja) * | 2009-02-17 | 2010-09-02 | Tokyo Electron Ltd | Cu膜の成膜方法および記憶媒体 |

| US8802572B2 (en) | 2012-07-10 | 2014-08-12 | Applied Materials, Inc. | Method of patterning a low-k dielectric film |

| JP6334369B2 (ja) | 2014-11-11 | 2018-05-30 | 株式会社日立ハイテクノロジーズ | プラズマ処理装置およびプラズマ処理方法 |

| CN105609406B (zh) * | 2014-11-19 | 2018-09-28 | 株式会社日立国际电气 | 半导体器件的制造方法、衬底处理装置、气体供给系统 |

| US9425094B2 (en) * | 2014-12-26 | 2016-08-23 | Taiwan Semiconductor Manufacturing Co., Ltd | Mechanisms for forming semiconductor device structure with feature opening |

| US9425041B2 (en) * | 2015-01-06 | 2016-08-23 | Lam Research Corporation | Isotropic atomic layer etch for silicon oxides using no activation |

| US9502238B2 (en) * | 2015-04-03 | 2016-11-22 | Lam Research Corporation | Deposition of conformal films by atomic layer deposition and atomic layer etch |

| US9984858B2 (en) * | 2015-09-04 | 2018-05-29 | Lam Research Corporation | ALE smoothness: in and outside semiconductor industry |

| US10727073B2 (en) | 2016-02-04 | 2020-07-28 | Lam Research Corporation | Atomic layer etching 3D structures: Si and SiGe and Ge smoothness on horizontal and vertical surfaces |

| JP6778139B2 (ja) * | 2017-03-22 | 2020-10-28 | 株式会社Kokusai Electric | 半導体装置の製造方法、基板処理装置およびプログラム |

| JP6812284B2 (ja) * | 2017-03-28 | 2021-01-13 | 東京エレクトロン株式会社 | エッチング方法及び記録媒体 |

| JP6789257B2 (ja) * | 2018-02-28 | 2020-11-25 | 株式会社Kokusai Electric | 半導体装置の製造方法、基板処理装置、およびプログラム |

| JP6843087B2 (ja) * | 2018-03-12 | 2021-03-17 | 株式会社Kokusai Electric | 半導体装置の製造方法、基板処理装置およびプログラム |

| JP7022651B2 (ja) | 2018-05-28 | 2022-02-18 | 東京エレクトロン株式会社 | 膜をエッチングする方法及びプラズマ処理装置 |

| JP7114554B2 (ja) * | 2019-11-22 | 2022-08-08 | 株式会社Kokusai Electric | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム |

| CN111243948B (zh) * | 2020-01-17 | 2023-03-21 | 北京北方华创微电子装备有限公司 | 用于半导体加工的原子层刻蚀方法 |

-

2021

- 2021-06-29 JP JP2021107284A patent/JP7313402B2/ja active Active

-

2022

- 2022-04-13 TW TW111113973A patent/TWI892000B/zh active

- 2022-05-13 CN CN202210523752.0A patent/CN115547822A/zh active Pending

- 2022-05-27 KR KR1020220065314A patent/KR102754079B1/ko active Active

- 2022-05-27 US US17/826,332 patent/US12255072B2/en active Active

- 2022-05-27 EP EP22175744.6A patent/EP4117023A1/en active Pending

-

2025

- 2025-01-08 KR KR1020250002842A patent/KR20250010734A/ko active Pending

- 2025-03-17 US US19/081,283 patent/US20250218786A1/en active Pending

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7174016B2 (ja) | 2020-07-16 | 2022-11-17 | 株式会社Kokusai Electric | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20250010734A (ko) | 2025-01-21 |

| US20220415659A1 (en) | 2022-12-29 |

| KR20230002048A (ko) | 2023-01-05 |

| US20250218786A1 (en) | 2025-07-03 |

| TWI892000B (zh) | 2025-08-01 |

| KR102754079B1 (ko) | 2025-01-14 |

| CN115547822A (zh) | 2022-12-30 |

| EP4117023A1 (en) | 2023-01-11 |

| US12255072B2 (en) | 2025-03-18 |

| JP2023005410A (ja) | 2023-01-18 |

| TW202303707A (zh) | 2023-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI819348B (zh) | 半導體裝置之製造方法、基板處理方法、基板處理裝置及程式 | |

| US20210272803A1 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US12365987B2 (en) | Method of processing substrate, method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US12033852B2 (en) | Method of processing substrate, method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| TW202101649A (zh) | 半導體裝置之製造方法、基板處理裝置及記錄媒體 | |

| JP6606476B2 (ja) | 半導体装置の製造方法、基板処理装置およびプログラム | |

| US11705326B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| JP2018157095A (ja) | 半導体装置の製造方法、基板処理装置およびプログラム | |

| US20220301851A1 (en) | Method of manufacturing semiconductor device, substrate processing method, recording medium, and substrate processing apparatus | |

| US20250218786A1 (en) | Method of processing substrate, substrate processing apparatus, recording medium, and method of manufacturing semiconductor device | |

| US20220301854A1 (en) | Method of processing substrate, method of manufacturing semiconductor device, substrate processing system, and recording medium | |

| JP6559902B2 (ja) | 半導体装置の製造方法、基板処理装置およびプログラム | |

| US11728162B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| US11965240B2 (en) | Cleaning method, method of manufacturing semiconductor device, and substrate processing apparatus | |

| JP7305013B2 (ja) | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム | |

| JP7135190B2 (ja) | 半導体装置の製造方法、基板処理方法、基板処理装置、およびプログラム | |

| JP7186909B2 (ja) | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220323 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220323 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230327 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230613 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230711 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7313402 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |