JP4329505B2 - 磁気メモリを用いた磁気メモリ装置 - Google Patents

磁気メモリを用いた磁気メモリ装置 Download PDFInfo

- Publication number

- JP4329505B2 JP4329505B2 JP2003389105A JP2003389105A JP4329505B2 JP 4329505 B2 JP4329505 B2 JP 4329505B2 JP 2003389105 A JP2003389105 A JP 2003389105A JP 2003389105 A JP2003389105 A JP 2003389105A JP 4329505 B2 JP4329505 B2 JP 4329505B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- layer

- magnetic

- stage

- magnetization

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 title claims description 346

- 230000005291 magnetic effect Effects 0.000 title claims description 244

- 230000005415 magnetization Effects 0.000 claims description 107

- 230000008859 change Effects 0.000 claims description 46

- 239000011159 matrix material Substances 0.000 claims description 9

- 239000010410 layer Substances 0.000 description 298

- 229910003321 CoFe Inorganic materials 0.000 description 71

- 239000010408 film Substances 0.000 description 43

- 229910001030 Iron–nickel alloy Inorganic materials 0.000 description 36

- 229910019041 PtMn Inorganic materials 0.000 description 30

- 239000004020 conductor Substances 0.000 description 26

- 238000000034 method Methods 0.000 description 22

- 239000000758 substrate Substances 0.000 description 9

- 230000008878 coupling Effects 0.000 description 8

- 238000010168 coupling process Methods 0.000 description 8

- 238000005859 coupling reaction Methods 0.000 description 8

- 238000001514 detection method Methods 0.000 description 8

- 229910052742 iron Inorganic materials 0.000 description 8

- 230000010354 integration Effects 0.000 description 7

- -1 PtPdMn Inorganic materials 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 230000014509 gene expression Effects 0.000 description 6

- 229910052720 vanadium Inorganic materials 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 229910052804 chromium Inorganic materials 0.000 description 5

- 230000000052 comparative effect Effects 0.000 description 5

- 150000001875 compounds Chemical class 0.000 description 5

- 229910052733 gallium Inorganic materials 0.000 description 5

- 229910052735 hafnium Inorganic materials 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 229910052758 niobium Inorganic materials 0.000 description 5

- 229910052757 nitrogen Inorganic materials 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- 229910052726 zirconium Inorganic materials 0.000 description 5

- 230000005290 antiferromagnetic effect Effects 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 229910052731 fluorine Inorganic materials 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- 229910002546 FeCo Inorganic materials 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000001965 increasing effect Effects 0.000 description 3

- 238000010884 ion-beam technique Methods 0.000 description 3

- 229910052741 iridium Inorganic materials 0.000 description 3

- 229910052747 lanthanoid Inorganic materials 0.000 description 3

- 150000002602 lanthanoids Chemical class 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229910052703 rhodium Inorganic materials 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 229910052684 Cerium Inorganic materials 0.000 description 2

- 229910002441 CoNi Inorganic materials 0.000 description 2

- 229910005335 FePt Inorganic materials 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 238000007737 ion beam deposition Methods 0.000 description 2

- 229910052746 lanthanum Inorganic materials 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000000696 magnetic material Substances 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000001451 molecular beam epitaxy Methods 0.000 description 2

- 229910052762 osmium Inorganic materials 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 229910052717 sulfur Inorganic materials 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- BSYNRYMUTXBXSQ-UHFFFAOYSA-N Aspirin Chemical compound CC(=O)OC1=CC=CC=C1C(O)=O BSYNRYMUTXBXSQ-UHFFFAOYSA-N 0.000 description 1

- 229910000531 Co alloy Inorganic materials 0.000 description 1

- 229910019222 CoCrPt Inorganic materials 0.000 description 1

- 229910019233 CoFeNi Inorganic materials 0.000 description 1

- 229910018979 CoPt Inorganic materials 0.000 description 1

- 229910019586 CoZrTa Inorganic materials 0.000 description 1

- 229910052692 Dysprosium Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910015372 FeAl Inorganic materials 0.000 description 1

- 229910015136 FeMn Inorganic materials 0.000 description 1

- 229910005347 FeSi Inorganic materials 0.000 description 1

- 229910005435 FeTaN Inorganic materials 0.000 description 1

- 229910000604 Ferrochrome Inorganic materials 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- 229910018279 LaSrMnO Inorganic materials 0.000 description 1

- 229910052765 Lutetium Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 229910003289 NiMn Inorganic materials 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- 101100484930 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) VPS41 gene Proteins 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- 229910000287 alkaline earth metal oxide Inorganic materials 0.000 description 1

- 239000002885 antiferromagnetic material Substances 0.000 description 1

- 229910052789 astatine Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- FWZTTZUKDVJDCM-CEJAUHOTSA-M disodium;(2r,3r,4s,5s,6r)-2-[(2s,3s,4s,5r)-3,4-dihydroxy-2,5-bis(hydroxymethyl)oxolan-2-yl]oxy-6-(hydroxymethyl)oxane-3,4,5-triol;iron(3+);oxygen(2-);hydroxide;trihydrate Chemical compound O.O.O.[OH-].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[Na+].[Na+].[Fe+3].[Fe+3].[Fe+3].[Fe+3].[Fe+3].O[C@H]1[C@H](O)[C@@H](CO)O[C@@]1(CO)O[C@@H]1[C@H](O)[C@@H](O)[C@H](O)[C@@H](CO)O1 FWZTTZUKDVJDCM-CEJAUHOTSA-M 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000005293 ferrimagnetic effect Effects 0.000 description 1

- 230000005294 ferromagnetic effect Effects 0.000 description 1

- 239000003302 ferromagnetic material Substances 0.000 description 1

- 239000002223 garnet Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 238000007733 ion plating Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 230000006386 memory function Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 229910052596 spinel Inorganic materials 0.000 description 1

- 239000011029 spinel Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000000992 sputter etching Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 229910000859 α-Fe Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5607—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using magnetic storage elements

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Hall/Mr Elements (AREA)

- Mram Or Spin Memory Techniques (AREA)

Description

1.素子間隔の減少に伴う磁気クロストークにより生じる記録エラー。

2.磁性体の微細化に伴う磁化反転磁界の増加および記録電流の増大。

3.配線の微細化に伴う記録電流の制限。

4.配線の微細化に伴う抵抗上昇により生じる読み出し時のS/Nの低下。

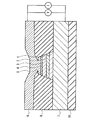

磁気メモリを平面視においてマトリックス状に複数個配置した磁気メモリ装置であって、

前記磁気メモリは、

固定磁性層、トンネル層、およびメモリ層(すなわち、自由磁性層)が順に積層された第1段の磁気抵抗素子、および

固定磁性層、トンネル層、およびメモリ層(すなわち、自由磁性層)が順に積層された第1段の磁気抵抗素子、

を具備し、

前記第1段のメモリ層と前記第2段のメモリ層とが層の厚さ方向に積層されており、

前記層の厚さ方向に積層されている第1段のメモリ層と第2段のメモリ層が電気的に直列に接続されており、

前記第1段のメモリ層の磁化反転により生じる抵抗変化と、前記第2段のメモリ層の磁化反転により生じる抵抗変化とが互いに相違し、

前記第1段のメモリ層の長手方向は、前記第2段のメモリ層の長手方向と異なっており、

前記平面視において隣接する2つの磁気メモリにおける第1段のメモリ層同士も、互いに異なる長手方向を有しており、

前記平面視において隣接する2つの磁気メモリにおける第2段のメモリ層同士も、互いに異なる長手方向を有している、

前記第1段のメモリ層の長手方向と、前記第2段のメモリ層の長手方向とがなす角度は、20°以上90°以下であることが好ましい。

前記平面視において隣接する2つの磁気メモリにおける第1段のメモリ層の2つの長手方向がなす角度は、20°以上90°以下であることが好ましい。

式(1)の関係が成立すると、2つのメモリ層群からの出力の分離が容易となる。

ただし、Nは2以上の整数である。

ただし、Mは1以上(N−1)以下の整数である。

CMOS基板上に、図3に示したように3段の磁気抵抗素子からなる磁気メモリで集積メモリを作製した。集積メモリはセラミックパッケージに封入し、パッケージ全体には、厚さ100μmのNiFe膜を磁気シールドとしてメッキした。

ここで、カッコ内の数値は、単位はnmとする膜厚であるが、AlOの膜厚は、酸化前の金属Alの膜厚である(以下において、同様)。

mV、2段目が80 mV、3段目が160 mVであった。

CMOS基板上に、図7に示したような2つのメモリ層3,73を有する磁気抵抗素子からなる磁気メモリを、マトリックス状に配列して集積メモリを作製した。集積メモリには、実施例1と同様の磁気シールドを施した。ただし、図7に示した層のうち、両端のバイアストンネル層4,74の形成は省略した。

この素子では、トンネル層がAlOにより、メモリ層がNiFeにより、それぞれ形成されている。

ワード線とビット線の合成磁界により、2つのメモリ層3,73に個別に書き込みを行った。これらメモリ層の磁化スイッチ曲線は、いずれも、ほぼ図14(a)に示した形状である。しかし、メモリ層3,73とビット線21またはワード線31との相対的な距離の相違により、電流に基づく磁化スイッチ曲線は、相対的に近い記録導線の方向に引き伸ばされた形状となる(図25)。従って、点Aに相当する合成電流を印加すると、磁化反転するのは磁化スイッチング曲線pを有するメモリ層3のみである。点Bの合成電流の印加によると、磁化スイッチング曲線qを有するメモリ層73のみにおいて磁化方向が反転する。

ガラス基板上に、図9に示したように3段の磁気抵抗素子からなる磁気メモリで集積メモリを作製した。集積メモリには、実施例1と同様の磁気シールドを施した。

この素子では、トンネル層がAlOにより、メモリ層がFeにより、それぞれ形成されている。Taに接するAlOはバイアストンネル層である。

ガラス基板上に、図10に示した2つのメモリ層を有する磁気抵抗素子で集積メモリを作製した。集積メモリには、実施例1と同様の磁気シールドを施した。

この素子では、トンネル層がAlOにより、メモリ層がFeにより、それぞれ形成されている。Taに接するAlOは、バイアストンネル層である。

CMOS基板上に、図3に示したような多段の磁気抵抗素子からなる磁気メモリで集積メモリを作製した。ただし、ここでは、素子の段数は2とした。集積メモリには、実施例1と同様の磁気シールドを施した。

引き続き、第2段の磁気抵抗素子として、以下に示す積層構造を作製した。

これらの素子では、トンネル層はAlOにより、メモリ層はCoFe(0.5) /NiFe(2)/CoFe(0.5)により、それぞれ形成されている。

・メモリI

第1段

下部電極/Ta(3)/PtMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.0) /NiFe(2)/Ru(0.9)/NiFe(4)/AlO(1.0)/CoFe(3)/PtMn(20) /Ta(3)/上部電極

第2段

下部電極/Ta(3)/IrMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.06) /NiFe(2)/Ru(0.9)/ NiFe(4)/AlO(1.06)/CoFe(3)/PtMn(20) /Ta(3)/上部電極・メモリII

第1段

下部電極/Ta(3)/PtMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.0) /NiFe(2)/Ru(0.9)/NiFe(2)/Ru(0.9)/NiFe(2)/AlO(1.0)/CoFe(3)/Ru(0.9)/CoFe(3) /PtMn(20)/Ta(3)/上部電極

第2段

下部電極/Ta(3)/IrMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.06) /NiFe(2)/Ru(0.9)/NiFe(2)/Ru(0.9)/NiFe(2)/AlO(1.06)/CoFe(3)/Ru(0.9)/CoFe(3)/PtMn(20)/Ta(3)/上部電極・メモリIII

第1段

下部電極/Ta(3)/PtMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.0) /NiFe(1)/CoFe(1) /AlO(1.0)/CoFe(3)/Ru(0.9)/CoFe(3)/PtMn(20)/Ta(3)/上部電極

第2段

下部電極/Ta(3)/IrMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.06) /NiFe(1)/CoFe(1)/AlO(1.06)/CoFe(3)/Ru(0.9)/CoFe(3)/PtMn(20)/Ta(3)/上部電極・メモリIV

第1段

下部電極/Ta(3)/PtMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.0)/NiFe(2) /AlO(1.0)/CoFe(3)/Ru(0.9)/CoFe(3)/PtMn(20) /Ta(3)/上部電極

第2段

下部電極/Ta(3)/IrMn(20)/CoFe(3)/Ru(0.9)/CoFe(3)/AlO(1.06)/NiFe(2) /AlO(1.06)/CoFe(3)/Ru(0.9)/CoFe(3)/PtMn(20) /Ta(3)/上部電極

メモリI〜IIIでは多層膜がメモリ層として用いられている。メモリIにおいてメモリ層はNiFe(2)/Ru(0.9)/ NiFe(4)であり、メモリIIにおいてメモリ層はNiFe(2)/Ru(0.9)/ NiFe(4)/Ru(0.9)/ NiFe(4)であり、メモリIIIにおいてメモリ層はNiFe(1)/CoFe(1)である。これに対し、メモリIVにおけるメモリ層はNiFe(2)である。

CMOS基板上に、図27に示した構成の磁気抵抗素子をマトリックス状に配置したMRAMを作製し、記録方法について検討した。

ここで、AlO(1.3)はバイアストンネル層4であり、Fe(2)はメモリ層3であり、AlO(1.0)はトンネル層2であり、CoFe(3)/Ru(0.9)/CoFe(3)は固定磁性層1である。PtMn(3)は、図示を省略する反強磁性層である。

Claims (3)

- 磁気メモリを平面視においてマトリックス状に複数個配置した磁気メモリ装置であって、

前記磁気メモリは、

固定磁性層、トンネル層、およびメモリ層が順に積層された第1段の磁気抵抗素子、および

固定磁性層、トンネル層、およびメモリ層が順に積層された第2段の磁気抵抗素子からなる第2段のメモリ層面、

を具備し、

前記第1段のメモリ層と前記第2段のメモリ層とが層の厚さ方向に積層されており、

前記層の厚さ方向に積層されている第1段のメモリ層と第2段のメモリ層が電気的に直列に接続されており、

前記第1段のメモリ層の磁化反転により生じる抵抗変化と、前記第2段のメモリ層の磁化反転により生じる抵抗変化とが互いに相違し、

前記第1段のメモリ層の長手方向は、前記第2段のメモリ層の長手方向と異なっており、

前記平面視において隣接する2つの磁気メモリにおける第1段のメモリ層同士も、互いに異なる長手方向を有しており、

前記平面視において隣接する2つの磁気メモリにおける第2段のメモリ層同士も、互いに異なる長手方向を有している、

磁気メモリ装置。 - 前記第1段のメモリ層の長手方向と、前記第2段のメモリ層の長手方向とがなす角度は、20°以上90°以下である請求項1に記載の磁気メモリ装置。

- 前記平面視において隣接する2つの磁気メモリにおける第1段のメモリ層の2つの長手方向がなす角度は、20°以上90°以下である請求項1に記載の磁気メモリ装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003389105A JP4329505B2 (ja) | 2001-06-19 | 2003-11-19 | 磁気メモリを用いた磁気メモリ装置 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001184480 | 2001-06-19 | ||

| JP2003389105A JP4329505B2 (ja) | 2001-06-19 | 2003-11-19 | 磁気メモリを用いた磁気メモリ装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002178745A Division JP3527230B2 (ja) | 2001-06-19 | 2002-06-19 | 磁気メモリの駆動方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004140386A JP2004140386A (ja) | 2004-05-13 |

| JP2004140386A5 JP2004140386A5 (ja) | 2005-09-15 |

| JP4329505B2 true JP4329505B2 (ja) | 2009-09-09 |

Family

ID=32472439

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003389105A Expired - Fee Related JP4329505B2 (ja) | 2001-06-19 | 2003-11-19 | 磁気メモリを用いた磁気メモリ装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4329505B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7611912B2 (en) * | 2004-06-30 | 2009-11-03 | Headway Technologies, Inc. | Underlayer for high performance magnetic tunneling junction MRAM |

| JP4828807B2 (ja) * | 2004-07-20 | 2011-11-30 | ルネサスエレクトロニクス株式会社 | 磁気記憶装置およびその製造方法 |

| JP2008192634A (ja) * | 2007-01-31 | 2008-08-21 | Fujitsu Ltd | トンネル磁気抵抗効果膜および磁気デバイス |

-

2003

- 2003-11-19 JP JP2003389105A patent/JP4329505B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004140386A (ja) | 2004-05-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6950333B2 (en) | Magnetic memory and method for driving the same, and magnetic memory device using the same | |

| JP4371781B2 (ja) | 磁気セル及び磁気メモリ | |

| US6914807B2 (en) | Magnetic logic element and magnetic logic element array | |

| US7119410B2 (en) | Magneto-resistive effect element and magnetic memory | |

| KR100413174B1 (ko) | 자기 저항 소자 | |

| JP3660927B2 (ja) | 磁気抵抗効果素子とこれを用いた磁気抵抗効果型磁気ヘッド、磁気記録装置および磁気抵抗効果型メモリー装置 | |

| US8456898B2 (en) | Magnetic element having perpendicular anisotropy with enhanced efficiency | |

| US7126848B2 (en) | Magnetic cell and magnetic memory | |

| KR101055595B1 (ko) | 자기저항 소자 및 자기 메모리 장치 | |

| US6593608B1 (en) | Magneto resistive storage device having double tunnel junction | |

| JP2009094104A (ja) | 磁気抵抗素子 | |

| JP3699954B2 (ja) | 磁気メモリ | |

| JP2009521807A (ja) | スピントランスファー方式により電流書き込みを行ない、かつスピントランスファートルクによる書き込み電流密度を小さくした磁性素子 | |

| KR20080029852A (ko) | 자기저항 효과 소자 및 자기저항 랜덤 액세스 메모리 | |

| JP2004179183A (ja) | 磁気抵抗効果素子および磁気メモリ | |

| JP2004179219A (ja) | 磁気デバイスおよびこれを用いた磁気メモリ | |

| JP6434103B1 (ja) | 磁気メモリ | |

| JP4005832B2 (ja) | 磁気メモリ及び磁気メモリ装置 | |

| JP3527230B2 (ja) | 磁気メモリの駆動方法 | |

| JP2004014806A (ja) | 磁気抵抗素子および磁気メモリ | |

| JP3949900B2 (ja) | 磁気記憶素子、磁気記憶装置および携帯端末装置 | |

| JP4387955B2 (ja) | 磁気抵抗効果素子 | |

| US20050122828A1 (en) | Magnetic switching device and memory using the same | |

| JP4329505B2 (ja) | 磁気メモリを用いた磁気メモリ装置 | |

| JP2002270922A (ja) | 磁気抵抗素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050601 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050601 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20050713 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090406 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090414 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090428 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090526 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090608 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4329505 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120626 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120626 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130626 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |