JP4298189B2 - 液晶表示装置及びその製造方法 - Google Patents

液晶表示装置及びその製造方法 Download PDFInfo

- Publication number

- JP4298189B2 JP4298189B2 JP2001246288A JP2001246288A JP4298189B2 JP 4298189 B2 JP4298189 B2 JP 4298189B2 JP 2001246288 A JP2001246288 A JP 2001246288A JP 2001246288 A JP2001246288 A JP 2001246288A JP 4298189 B2 JP4298189 B2 JP 4298189B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- pattern

- liquid crystal

- pixel electrode

- crystal display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 129

- 238000004519 manufacturing process Methods 0.000 title description 135

- 239000000758 substrate Substances 0.000 claims description 267

- 125000006850 spacer group Chemical group 0.000 claims description 47

- 238000002679 ablation Methods 0.000 claims description 28

- 239000000463 material Substances 0.000 claims description 22

- 238000009413 insulation Methods 0.000 claims description 6

- 238000005520 cutting process Methods 0.000 claims description 5

- 230000007423 decrease Effects 0.000 claims 1

- 239000010408 film Substances 0.000 description 242

- 239000010409 thin film Substances 0.000 description 119

- 239000010410 layer Substances 0.000 description 98

- 238000000034 method Methods 0.000 description 72

- 238000010586 diagram Methods 0.000 description 58

- 239000004065 semiconductor Substances 0.000 description 57

- 230000008569 process Effects 0.000 description 55

- 239000011347 resin Substances 0.000 description 38

- 229920005989 resin Polymers 0.000 description 38

- 229920000642 polymer Polymers 0.000 description 34

- 239000003990 capacitor Substances 0.000 description 22

- 239000011810 insulating material Substances 0.000 description 19

- 239000004020 conductor Substances 0.000 description 17

- 239000012535 impurity Substances 0.000 description 17

- 239000011159 matrix material Substances 0.000 description 17

- 229910052751 metal Inorganic materials 0.000 description 16

- 239000002184 metal Substances 0.000 description 16

- 238000003860 storage Methods 0.000 description 15

- 230000001681 protective effect Effects 0.000 description 14

- 238000001259 photo etching Methods 0.000 description 12

- 238000002834 transmittance Methods 0.000 description 12

- 230000008859 change Effects 0.000 description 11

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 10

- 238000005530 etching Methods 0.000 description 10

- 239000007769 metal material Substances 0.000 description 10

- 238000000206 photolithography Methods 0.000 description 10

- 229910052710 silicon Inorganic materials 0.000 description 10

- 239000010703 silicon Substances 0.000 description 10

- 206010034972 Photosensitivity reaction Diseases 0.000 description 9

- 230000036211 photosensitivity Effects 0.000 description 9

- 238000000059 patterning Methods 0.000 description 8

- 229910021417 amorphous silicon Inorganic materials 0.000 description 7

- 230000005540 biological transmission Effects 0.000 description 6

- 150000002751 molybdenum Chemical class 0.000 description 6

- 239000004925 Acrylic resin Substances 0.000 description 5

- 229920000178 Acrylic resin Polymers 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 5

- 210000004027 cell Anatomy 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- AZDRQVAHHNSJOQ-UHFFFAOYSA-N alumane Chemical class [AlH3] AZDRQVAHHNSJOQ-UHFFFAOYSA-N 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 239000011368 organic material Substances 0.000 description 4

- 238000000635 electron micrograph Methods 0.000 description 3

- 230000014509 gene expression Effects 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 238000004380 ashing Methods 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 150000001844 chromium Chemical class 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 230000001965 increasing effect Effects 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 230000001939 inductive effect Effects 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 150000003608 titanium Chemical class 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229910001182 Mo alloy Inorganic materials 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 1

- 206010047571 Visual impairment Diseases 0.000 description 1

- 230000001154 acute effect Effects 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 229910000423 chromium oxide Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 210000002858 crystal cell Anatomy 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1337—Surface-induced orientation of the liquid crystal molecules, e.g. by alignment layers

- G02F1/133707—Structures for producing distorted electric fields, e.g. bumps, protrusions, recesses, slits in pixel electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133345—Insulating layers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1339—Gaskets; Spacers; Sealing of cells

- G02F1/13394—Gaskets; Spacers; Sealing of cells spacers regularly patterned on the cell subtrate, e.g. walls, pillars

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78663—Amorphous silicon transistors

- H01L29/78669—Amorphous silicon transistors with inverted-type structure, e.g. with bottom gate

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1339—Gaskets; Spacers; Sealing of cells

- G02F1/13398—Spacer materials; Spacer properties

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134336—Matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134372—Electrodes characterised by their geometrical arrangement for fringe field switching [FFS] where the common electrode is not patterned

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136231—Active matrix addressed cells for reducing the number of lithographic steps

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F2201/00—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00

- G02F2201/12—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00 electrode

- G02F2201/123—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00 electrode pixel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

Description

【発明の属する技術分野】

本発明は液晶表示装置及びその製造方法に係り、特に、液晶表示装置での2枚の基板のギャップを維持するスペーサを含む液晶表示装置及びその製造方法に関する。

【0002】

【従来の技術】

液晶表示装置は共通電極、色フィルター、ブラックマトリックスなどが形成されている色フィルター基板と薄膜トランジスタ及び画素電極が形成されている薄膜トランジスタ基板との間に液晶物質を注入し、画素電極と共通電極との間に電圧を印加して電気場を形成し、液晶分子の配列を変更させ、これを通じて光の透過量を調節することにより画像を表示する装置である。

【0003】

このような液晶表示装置は、視野角を広くするための方法の一つとして、多重領域(multi−domain)を有する垂直配向方式(PVA:patterned vertical alignment)を採用する。このような垂直配向方式では、画素電極及び共通電極に切除パターンまたは突起を形成し、これによって形成されるフリンジフィールド(fringe field)を利用して液晶分子の傾く方向を複数個の方向に分散させることによって広視野角を確保する。

【0004】

一方、液晶表示装置の2枚の基板の間隔を一定に維持するために弾性を有するスペーサが介される。しかし、液晶表示装置に衝撃が加わる場合にはスペーサの弾性によって2枚の基板の間のギャップが激しく変わるようになり、これによって画面に染みが発生する。

【0005】

また、このようなスペーサを形成するためには別途の作業を追加的に実施するようになるので、工程追加による生産性低下が問題になっている。

【0006】

【発明が解決しようとする課題】

本発明が目的とする技術的課題は、液晶表示装置の画質を向上させると共に輝度の変化を最小化することである。

【0007】

本発明の他の技術的課題は、液晶表示装置の製造工程を単純化することである。

【0008】

【課題を解決するための手段】

このような技術的課題を達成するために、本発明による液晶表示装置には、第1絶縁基板上に第1切除パターンを有する画素電極が形成されている第1基板と;第1絶縁基板と対向している第2絶縁基板上に第2切除パターンを有する共通電極が形成され、第2切除パターンは第1切除パターンと互いに平行で、相互交互に配置されている第2基板とが形成されている。また、第1基板と第2基板との間には液晶が注入されており、第1基板と第2基板との間隔を維持し第2切除パターンの端部に位置するスペーサを含む。

【0009】

ここで、第1切除パターンは画素電極の上部領域で第1方向に形成されている第1切除部と、画素電極の下部領域で第1方向と直角をなす第2方向に形成されている第2切除部とを含み;第2切除パターンは画素電極の上部領域と対応する位置に第1方向に形成されている第1幹切除部と、画素電極の下部領域と対応する位置に第2方向に形成されている第2幹切除部とを含む。

【0010】

この時、第1方向は画素電極の辺に対して斜線方向であるのが好ましい。

【0011】

また、第2切除パターンは画素電極の上下辺と重複する第1枝切除部と、画素電極の左右辺と重複する第2枝切除部とを含み;第1切除パターンは画素電極の上下中央に位置し画素電極の上下辺と平行な第3切除部を含み;第1切除パターン及び第2切除パターンは画素電極を多数の閉鎖された多角形に分割していることを特徴とする。

【0012】

この時、第2枝切除部は幹切除部より幅が広いのが好ましく、第1方向は画素電極の辺のうちのいずれかの一つと平行な方向であるのが好ましい。

【0013】

また、本発明による液晶表示装置では、第1絶縁基板上に第1切除パターンを有する画素電極が形成され、第1切除パターンは画素電極の第1辺から横方向に形成されている第1切除部、斜線方向に形成されており第1切除部に対して互いに対称をなしており第1辺から第1辺と対向する第2辺に接近するほど互いに間隔が狭くなる第2及び第3切除部からなる第1基板が形成されている。そして、第1絶縁基板と対向している第2絶縁基板上に第1切除パターンと交互に配置されている第2切除パターンを有する共通電極が形成され、第2切除パターンは横方向に形成されている幹部、幹部から各々斜線方向に形成されており幹部から離れるほど互いに離れる第1及び第2枝部、第1及び第2枝部から縦方向に形成されており互いに反対方向にのびている第1及び第2枝端部を含む第4切除部と、第1枝部と平行な第1中央部、第1中央部の両端から各々横方向及び縦方向に形成されている第1及び第2屈折部を含む第5切除部と、第4切除部に対して第5切除部と対称をなす第6切除部とからなる第2基板が形成されている。また、第1基板と第2基板との間には液晶が注入されており、第1基板と第2基板との間隔を維持し第2切除パターンの端部に位置するスペーサを含む。

【0014】

また、本発明による液晶表示装置には、第1絶縁基板上に第1切除パターンを有する画素電極が形成され、第1切除パターンは画素電極の上面を縦に分割する第1切除部と、第1切除部の下に位置しており画素電極を横に分割する第2切除部とを含む第1基板が形成されている。また、第1絶縁基板と対向している第2絶縁基板上に第2切除パターンを有する共通電極が形成され、第2切除パターンは縦方向に形成されている第3切除部及び第3切除部の下に横方向に形成されている第4切除部を含み、第3切除部は第1切除部と交互に位置し画素電極の上面を縦に多数の領域に分割し、第4切除部は第2切除部と交互に位置し画素電極の下面を横に多数の領域に分割する第2基板が形成されている。また、第1基板と第2基板との間に液晶が注入されており、第1基板と第2基板の間隔を維持するスペーサを含む。

【0015】

また、本発明による液晶表示装置用色フィルター基板は絶縁基板上にブラックマトリックスが形成されており、ブラックマトリックス上に色フィルターが形成されている。また、基板の全面に共通電極が形成されており、共通電極上には第1厚さを有する第1突起及び第1厚さより厚い第2厚さを有する第2突起が形成されている。

【0016】

ここで、第1及び第2突起は感光性有機絶縁膜、感光膜、ケイ素を含む絶縁膜のうちのいずれかの一つ以上を含むことができる。共通電極はITO及びIZOのうちのいずれかの一つからなることができる。

【0017】

また、本発明による液晶表示装置用色フィルター基板を製造するために、絶縁基板上にブラックマトリックスを形成し、ブラックマトリックス上に色フィルターを形成する。その次に、基板の全面に共通電極を形成し、共通電極上部に絶縁膜を塗布する。その次に、絶縁膜をパターニングして第1厚さを有する第1突起及び第1厚さより厚い第2厚さを有する第2突起を形成する。

【0018】

ここで、絶縁膜は感光性有機絶縁膜、感光膜、ケイ素を含む絶縁膜のうちのいずれかの一つ以上を含むことができる。また、共通電極はITO及びIZOのうちのいずれかの一つからなることができる。

【0019】

この時、絶縁膜は陰性感光性を有する有機絶縁膜であることができ、この場合、第1及び第2突起は第1突起に対応するスリットパターン及び第2突起に対応する透明パターンを含むマスクを用いて形成することができる。

【0020】

また、絶縁膜は陽性感光性を有する有機絶縁膜であることができ、この場合、第1及び第2突起は第1突起に対応する反透過膜パターン及び第2突起に対応する不透明パターンを含むマスクを用いて形成することができる。

【0021】

ここで、絶縁膜上に一回の写真工程で位置によって厚さが異なる感光膜パターンを形成する段階をさらに含むことができる。

【0022】

また、本発明による液晶表示装置を製造するために、配線パターン、スイッチング素子、切除パターンを有する画素電極を含む薄膜トランジスタ基板を製造した後、共通電極、カラーフィルター、高分子柱、突起パターンを含む色フィルター基板を製造する。その次に、薄膜トランジスタ基板及び色フィルター基板を接合した後、2枚の基板の間に液晶物質を注入する。

【0023】

また、本発明による液晶表示装置を製造するために、透明基板上にブラックマトリックスと色フィルターを順次に形成した後、色フィルター上部にオーバーコート膜を形成する。その次に、オーバーコート膜上部に透明導電物質からなる共通電極を形成した後、共通電極上部に感光樹脂を塗布する。その次に、露光器の解像度より狭い幅を有するパターン及び露光器の解像度より広い幅を有するパターンを有するマスクに感光樹脂を露光し現像して高さが異なる突起及び高分子柱を同時に形成する。

【0024】

ここで、突起の幅は4μm〜14μmであり、高分子柱の幅は15μm〜45μmであり、突起の高さは1.0μm〜1.2μmであり、高分子柱の高さは3.0μm〜4.5μmであるのが好ましい。

【0025】

この時、突起及び高分子柱が一定の強度を有するようにするハードベーク段階をさらに含み、このハードベーク段階での温度調節によって突起及び高分子柱の高さを調節することができる。ここで、ハードベークの温度は200〜240℃であることができる。

【0026】

また、本発明による薄膜トランジスタ基板を製造するために、基板上にゲート線及びゲート電極を含むゲート配線を形成した後、ゲート配線を覆うゲート絶縁膜を形成する。その次に、ゲート絶縁膜上に半導体パターンを形成した後、ゲート絶縁膜及び半導体パターン上にデータ線、ソース電極、ドレーン電極を含むデータ配線を形成する。その次に、半導体パターン上に第1厚さを有する突出パターン及びドレーン電極を露出させる接触孔が形成されており、突出パターン及び接触孔以外の他の部分は第2厚さを有する有機絶縁膜パターンを形成した後、有機絶縁膜パターン上に接触孔を通じてドレーン電極に連結される画素電極を形成する。

【0027】

ここで、有機絶縁膜パターンを形成するための工程はデータ配線を含む基板の露出された全面を覆う感光性有機絶縁膜を形成する段階と;感光性有機絶縁膜を選択的に露光し、スペーサが形成される第1部分は露光せず、接触孔が形成される第2部分は全面露光し、第1及び第2部分以外の部分は部分露光する段階と;選択的に露光された有機絶縁膜を現像する段階とを含むことができる。

【0028】

この時、有機絶縁膜を選択的に露光する作業は、有機絶縁膜の第1部分に非露光領域が位置し、有機絶縁膜の第2部分に露光領域が位置し、有機絶縁膜の第3部分に所定の透過率を有する選択透過領域が位置するマスクを用いることができる。ここで、マスクの選択透過領域はスリットパターンまたは反透過パターンが形成されるのが好ましい。

【0029】

また、有機絶縁膜を選択的に露光する作業は、有機絶縁膜の第2部分を露光する第1マスク及び有機絶縁膜の第3部分を所定の透過率で露光する第2マスクを用いて進行することができる。

【0030】

【発明の実施の形態】

以下、添付図面を参考にして本発明の実施例を詳細に説明する。

【0031】

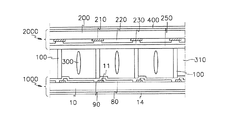

図1は本発明の第1実施例による液晶表示装置の概略的構造を示す構成図である。

【0032】

液晶表示装置は、互いに平行に対向している下部基板1000及び上部基板2000と、下部基板1000と上部基板2000との間に注入されており2枚の基板1000、2000の面に対して垂直に配向されている液晶分子300を含む液晶物質層310と、2枚の基板1000、2000の間に形成されており2枚の基板1000、2000の間隔を平行に維持するためのスペーサ100とを含む。

【0033】

下部基板1000はガラスなどの透明な絶縁物質からなる第1絶縁基板10上にITO(indium tin oxide)またはIZO(indium tin oxide)などの透明な導電物質からなり切除パターン(図示せず)を有している画素電極80が形成されており、各画素電極80はスイッチング素子11に連結されて画像信号電圧を印加される。

【0034】

また、第1絶縁基板10上には液晶分子300を配向するための配向膜90が形成されている。この時、スイッチング素子11としては通常薄膜トランジスタが用いられ、薄膜トランジスタは走査信号を伝達するゲート線(図示せず)及び画像信号を伝達するデータ線(図示せず)に各々連結されて走査信号によってオン(on)/オフ(off)される。

【0035】

下部基板1000の下面には下部偏光板14が付着されている。ここで、反射型液晶表示装置の場合には、画素電極80を透明でない物質で構成することができ、この場合には下部偏光板14も不必要になる。

【0036】

上部基板2000は、ガラスなどの透明な絶縁物質からなる第2絶縁基板200の下面に光漏れを防止するためのブラックマトリックス210と、赤、緑、青の色フィルター220と、ITOまたはIZOなどの透明な導電物質からなり切除パターン(図示せず)を有している共通電極230と、液晶分子を配向するための配向膜250とが形成されている。この時、ブラックマトリックス210や色フィルター220は下部基板1000に形成することもできる。上部基板2000の上面には上部偏光板400が付着されている。

【0037】

下部偏光板14及び上部偏光板400の偏光方向はノーマリーブラックモード(normally black mode)では互いに直交するように配置し、ノーマリーホワイトモード(normally white mode)では互いに平行に配置する。以下ではノーマリーブラックモードのみを考慮する。

【0038】

以下、図面を参照して本発明の実施例による液晶表示装置における画素電極及び共通電極の切除パターン及びスペーサの位置について具体的に説明する。

【0039】

図2は本発明の第2実施例による液晶表示装置の構造を示した配置図である。

【0040】

図2には、切除パターンを有する画素電極が形成されている下部基板と、切除パターンを有する共通電極が形成されている上部基板が整列されている。

【0041】

図2に示されているように、本発明の第2実施例による液晶表示装置の下部基板には、ゲート信号を伝達するゲート線22及びゲート線22に連結されている薄膜トランジスタのゲート電極26を含むゲート配線が形成されている。

【0042】

また、下部基板には、ゲート線22と交差して単位画素を定義しデータ信号を伝達するデータ線62と、データ線に連結されている薄膜トランジスタのソース電極65と、ゲート電極26を中心にしてソース電極65と対向する薄膜トランジスタのドレーン電極66とを含むデータ配線が形成されている。この時、画素電極80及びドレーン電極66は電気的に連結されており、画素電極80はデータ配線62、65、66からデータ信号を受信する。

【0043】

また、単位画素の縁周には画素電極80と重複して保持容量を形成し、単位画素の端部で漏れる光を遮断する保持配線27、28が形成されている。

【0044】

この時、図2に示されているように、画素電極80には画素電極80の中間部の右辺から左側に細く凹入した第1切除部821が形成されており、第1切除部821の入口の両側は角部が切取られて緩やかな角度に曲がっている。

【0045】

第1切除部821を中心にして画素電極80を上部及び下部に区分する時、上部及び下部には各々第2及び第3切除部822、823が形成されている。第2及び第3切除部822、823は各々画素電極80の上部及び下部に対角線方向に凹入形成されており、互いに対称をなしている。第2及び第3切除部822、823は第1切除部821と同じ方向に凹入形成されており、凹入するほど第1切除部821と近くなる形態である。

【0046】

ここで、第2及び第3切除部822、823が終わる部分は画素電極80を外部に突出させて形成する。これは切除部822、823によって画素電極80の各部分の連結が不良になるのを防止するためである。

【0047】

一方、上部基板に全面的に形成されている共通電極230の単位画素には、横方向に形成されている幹部211と、幹部211から各々斜線方向に上下にのびている第1及び第2枝部212、214と、第1及び第2枝部212、214から各々縦方向に上下にのびている第1及び第2枝端部213、215とを含む第4切除部211、212、213、214、215が形成されている。

【0048】

また、共通電極には、第1枝部212と平行に斜線方向に形成されている中央部221と、中央部221から横方向にのびている横断部222と、中央部221から縦方向にのびている縦断部223とを含む第5切除部221、222、223と、第4切除部に対して第5切除部と対称をなしている第6切除部231、232、233とが形成されている。このような配置の第4、第5及び第6切除部は共通電極230の単位画素に反復的に形成されている。

【0049】

図2に示すような画素電極80と共通電極230とが重畳することにより、画素電極80の第1乃至第3切除部821、822、823と共通電極230の第4乃至第6切除部とにより、画素電極80を多数の領域に分割している。この時、画素電極80の切除部821、822、823及び共通電極23の切除部212、214、221、231は交互に平行に配置されている。第1乃至第6切除部は画素電極80の中央を分割する第1切除部821、第4切除部の幹部211、画素電極80の辺と重畳する第4切除部の枝端部213、215、第2及び第3切除部の横断部222、232及び縦断部223、233を除いては殆どの領域で中央部が互いに平行に交互に形成されている。

【0050】

これによって、電気場の印加によって再配列された液晶分子は切除部パターンによって形成されるフリンジフィールドの方向に沿って一つの画素領域内で四つの方向に分類される。従って、四方向の全てで広い視野角を得ることができる。

【0051】

この時、互いに隣接する単位画素の間の共通電極230の切除部パターン211、213、215、222、223、232、233の端部には有機物質からなり2枚の基板1000、2000の間隔を一定に維持するスペーサ100が形成されている。このスペーサ100は互いに隣接する画素の切除部パターン211、213、215、222、223、232、233の端部で液晶分子の方向子が一定の方向に配列されないで多様な方向をとって転傾が発生するのを防止するために形成される。

【0052】

液晶分子を駆動するために画素電極80及び共通電極230に駆動電圧が印加された時、切除部パターン211、213、215、222、223、232、233の端部では電気場が均一に形成されないで電気場の傾きが激しく変わって液晶分子の配列が壊れるようになる。

【0053】

このように有機物質からなるスペーサ100を形成する場合には前述のように所望の位置に形成することによって転傾の発生を防止することができるだけでなく、一定の高さを維持しているため外部から衝撃が加えられても液晶表示装置の2枚の基板間隔を一定に維持することができるので輝度の減少を防止することができる。

【0054】

このような切除部パターンは液晶分子を分割配向するために多様な形態に変形することができ、次のような条件を満たすものが好ましい。

【0055】

第1に、最も良い視野角を得るためには4分割配向された領域が一つの画素内に位置するのが良い。

【0056】

第2に、安定した分割配向を得るためには分割された微小領域の境界以外の箇所で転傾(disclination)や不規則な組織(texture)が発生してはならない。転傾は狭い領域で液晶分子の方向子が一定の方向に配列されないで多様な方向をとっている場合に発生し、特に一つの領域で液晶分子が互いにぶつかる方向に倒れる場合に発生する。従って、安定した分割配向を得るためには上下基板のパターンが反復的に現れるのが有利で、上板のパターン及び下板のパターンの端部は近いほど良い。つまり、液晶表示装置を上から見る時に上板のパターン及び下板のパターンによって形成される領域が閉じた多角形に近似した形態になるのが良い。そして、一つの領域を形成するために一側の基板に形成されたパターンが鋭角をなす場合は転傾が発生しやすいのでパターンは鈍角のみで形成するのが良い。また、安定した分割配向は輝度にも影響を及ぼす原因になる。配向が乱れた領域ではオフ状態で光が漏れるだけでなく、オン状態では周囲の他の部分に比べて暗い状態に示されるようになり、液晶分子の配列が変わる時に配列が乱れた部分が移動して残像などの原因になることもある。

【0057】

第3に、高輝度を得るためには次のような条件を満たさなければならない。まず、隣接した領域の液晶方向子(director)がなす角は90度になるのが最も良い。このようになる時に最も狭い領域の転傾のみが発生するためであり、偏光板の透過軸と液晶方向子とがなす角が45度をなす時に最も高い輝度を得ることができる。そして、上板及び下板に各々形成されている切除部パターンができる限り多く曲がったり折れたりしないようにするのが良い。

【0058】

最後に、速い応答速度を得るためには上板及び下板に各々形成されている切除部パターンができる限り多く曲がったり折れたりしないようにするのが良い。

【0059】

以下、他の形態の切除部パターンを有する本発明の第3実施例について図3を参照して説明する。

【0060】

図3は本発明の第3実施例による液晶表示装置の構造を示した配置図である。

【0061】

図3に示したように、ゲート配線及びデータ配線の構造は第2実施例と同一である。

【0062】

この時、保持配線27、28、29は単位画素の端部を有して画素電極80の切除部パターン111、112に対応する形態に形成されている。

【0063】

画素電極80の上面を左右に半分する垂直な第1切除部111及び画素電極80の下面を四つの領域に分割する第2切除部112が画素電極80に形成されている。

【0064】

また、単位画素の共通電極230には縦方向に互いに平行な第1及び第2垂直部241、242と、第1及び第2垂直部241、242の下部に連結されており単位画素の共通電極230を上部及び下部の二つの領域に分割する水平部243とを含む第3切除部241、242、243が形成されている。

【0065】

また、共通電極230の下部には横方向に互いに平行な第4及び第5切除部244、245が共通電極230に形成されている。この時、第3乃至第5切除部241、242、243、244、245の端部は端に行くほど幅が広くなっていて三角形に形成されている。

【0066】

また、図3に示されているように、画素電極80の第1切除部111と共通電極230の第1及び第2垂直部241、242とは中央部が互いに平行に交互に配置されて画素電極80の上面を縦に4等分しており、第2切除部112と第3切除部の水平部243及び第4乃至第5切除部244、245とは中央部が互いに平行に交互に配置されて画素電極80の下面を横に6等分している。

【0067】

この時にも、図3に示されているように、互いに隣接する単位画素の間で共通電極230の切除部パターン241、242、243、244、245の端部には有機物質からなるスペーサ100を形成することにより、本発明の第1実施例のような効果を得ることができる。

【0068】

以上では共通電極及び画素電極の両方に切除パターンを形成することについて説明したが、共通電極に切除パターンを形成する代わりに画素電極に切除パターンと共に突起を形成する方法を使用することもできる。この場合、突起はゲート絶縁膜または保護膜等で形成する。突起を形成する時には配線との間で寄生静電容量が形成されることに留意しなければならない。また、他の方法としては画素電極には切除パターンを形成し共通電極に突起を形成する方法がある。

【0069】

上述のような本発明の第1、第2及び第3実施例によると、液晶表示装置の2枚の基板の間隔を維持する有機物質のスペーサを所望の位置に配置することができて転傾(disclination)が発生するのを防止することができ、液晶表示装置の輝度が低下するのを防止することができる。

【0070】

図4は本発明の第4実施例による液晶表示装置の薄膜トランジスタ基板と色フィルター基板を整列して示した断面図である。

【0071】

図4に示されているように、下部基板は第1絶縁基板10上に薄膜トランジスタ11及び薄膜トランジスタ11と電気的に連結されており切除部6を有する画素電極80が形成されており、これを薄膜トランジスタ基板という。また、下部基板1000と対向する上部基板2000には第2絶縁基板200上にブラックマトリックス210、色フィルター220及び共通電極230が形成されており、これを色フィルター基板という。

【0072】

以下、まず、上部基板2000である色フィルター基板について説明する。

【0073】

第2絶縁基板200上にブラックマトリックス210が形成されており、ブラックマトリックス210の間には赤、緑及び青色の色フィルター220が形成されている。色フィルター220上にはITOまたはIZO(indium zinc oxide)のような透明導電物質からなる共通電極230が全面に形成されている。この時、共通電極230はブラックマトリックス210上にも形成されており、ブラックマトリックス210上に形成されている共通電極230は色フィルター220上に形成されている部分に比べて凹入している。共通電極230上には感光性有機絶縁膜パターン160、170がパターニングされて形成されている。この時、有機絶縁膜パターン160、170は位置によって異なる厚さで形成されており、共通電極230の凹入した部分に形成されている有機絶縁膜パターン170、即ち第1有機絶縁膜パターン170より色フィルター220上部の共通電極230上に形成されている有機絶縁膜パターン160、即ち第2有機絶縁膜パターン160の厚さが薄い。

【0074】

次に、上部基板である色フィルター基板に対応する下部基板である薄膜トランジスタ基板について説明する。

【0075】

第1絶縁基板10上には切除部6を有する画素電極80が形成されており、画素電極80に印加される信号をスイッチングする役割を果たす薄膜トランジスタ11も形成されている。薄膜トランジスタ11の一部であるドレーン電極は画素電極80と電気的に連結されている。

【0076】

このような2枚の基板1000、2000を整列してその間に液晶を注入した後、上板の共通電極230及び下板の画素電極80に電圧を印加すると、図4のようにフリンジフィールド(f)が形成される。このようなフリンジフィールドに対して配列される液晶300が四方向に配向され上部基板2000の共通電極230をパターニングせずに所望の多重領域を形成することができる。

【0077】

この時、有機絶縁膜パターン160、170として感光性有機絶縁膜、陽性または陰性感光膜、ケイ素が含まれたケイ素絶縁膜などを用いることが可能である。

【0078】

このように、薄い厚さを有する第2有機絶縁膜パターン160によって形成されるフリンジフィールド(f)により多重領域を形成して液晶表示装置の広視野角を確保することができる。ここで、厚い厚さを有する第1有機絶縁膜パターン170が下部基板1000の薄膜トランジスタ11に対応する部分に位置して、2枚の基板1000、2000を整列する時に2枚の基板の間のギャップを維持するスペーサとしての役割を果たす。この時、スペーサの機能を果たす第1有機絶縁膜パターン170が薄膜トランジスタ11に対応する部分に位置することにより薄膜トランジスタ基板1000と色フィルター基板2000との間の間隔であるセルギャップ(cell gap)を均一に維持することができ、セルギャップの厚さを3μm乃至4μmと低くできるので応答速度を向上させることができる。

【0079】

また、フリンジフィールド(f)を形成する第2有機絶縁膜パターン160及びスペーサとして用いられる第1有機絶縁膜パターン170を一度の写真工程で形成できるので工程の数を減少させることができる。

【0080】

以下、このような色フィルター基板の製造方法について図5乃至図14を参照して説明する。

【0081】

まず、図5に示されているように、絶縁基板200上にブラックマトリックス210を形成した後、その上に赤、緑、青の色フィルター220を形成する。

【0082】

その次に、図6に示されているように、ITOまたはIZOのような透明導電物質からなる共通電極230を全面に形成する。

【0083】

その次に、図7に示されているように、共通電極230上に感光性有機絶縁膜150を塗布する。この時、感光性有機絶縁膜150の代りに陰性または陽性の感光膜、ケイ素が含まれたケイ素絶縁膜などを塗布することもできる。

【0084】

その次に、図8に示されているように、マスクを利用して感光性有機絶縁膜150をパターニングして厚さの異なる感光性有機絶縁膜パターン160、170を形成する。この時、使用するマスクはスリットパターンまたは反透過膜を含むのが好ましい。

【0085】

以下、まず、スリットパターンが形成されているマスクを用いて有機絶縁膜パターンを形成する方法について図9及び図8を参照して説明する。

【0086】

ここで、有機絶縁膜は陰性型感光性及び陽性型感光性を有する物質を全て用いることができるが、ここでは陰性型感光性有機絶縁膜の場合のみについて説明する。有機絶縁膜は陰性型感光特性を有するので、現像後に露光部分は残り露光されない部分は残らない。

【0087】

まず、図9に示されているように、マスクM1は色フィルター220上の共通電極230上部に位置する部分Bに形成されているスリットパターンと、ブラックマトリックス210と共通電極230とが当接しており凹入している部分Aに形成されている透明パターンと、その他の部分Cに位置する不透明パターンとを含んでいる。

【0088】

このようなマスクMを用いて露光すると、透明パターンを通じて入射される光の量よりスリットパターンを通じて入射される光の量が少ない。従って、露光後に現像すると、図8に示されているように、B部分に残る陰性有機絶縁膜160の厚さはA部分に残る陰性有機絶縁膜170の厚さより薄く、C部分には陰性有機絶縁膜が残らない。

【0089】

この時、陰性型感光性を有する有機絶縁膜を用いる場合には現像後に上部が下部よりさらに広く形成される逆テーパ(taper)形態に残るが、以後の工程で上部が切取られてほぼ直角に近いパターンが形成される。

【0090】

次に、反透過膜が含まれたマスクを用いて有機絶縁膜パターンを形成する方法について図10及び図8を参照して説明する。

【0091】

有機絶縁膜は陰性型感光性及び陽性型感光性を有する物質を全て用いることができるが、ここでは陽性型感光性を有する有機絶縁膜の場合のみについて説明する。有機絶縁膜が陽性であるので現像後に露光部分は残らないで露光されない部分が残る。

【0092】

図10に示されているように、マスクM2は色フィルター220上の共通電極230上部に位置する部分Bに形成されている反透過膜パターンと、ブラックマトリックス210と共通電極230とが当接しており凹入している部分Aに形成されている不透明パターンと、その他の部分Cに位置する透明パターンとを含んでいる。

【0093】

このようなマスクM2を用いて露光すると、透明パターンを通じて入射される光の量より反透過膜パターンを通じて入射される光の量が少ない。従って、露光後に現像すると、B部分に残る陽性有機絶縁膜の厚さはA部分に残る陽性有機絶縁膜の厚さより薄く、C部分には陽性有機絶縁膜が残らない。

【0094】

ここで、現像後に光を受けた部分が残る陰性有機絶縁膜を用いる場合には、反透過膜により光を少なく受けた部分に現像後に形成されるパターンを所望の厚さにすることが難しいので、陽性有機絶縁膜を用いるのが有利である。

【0095】

このように、スリットパターンまたは反透過膜を含むマスクを用いて厚さの異なる有機絶縁膜パターン160、170を形成する。薄い有機絶縁膜パターン160を突起パターンとしてフリンジフィールドを形成して広視野角を確保することができ、厚い有機絶縁膜パターン170をスペーサとする。

【0096】

このように、本発明では互いに異なる厚さを有する有機絶縁膜パターン160、170を一度の写真工程で形成することにより工程の数を減らすことができる。

【0097】

一方、本発明では、感光性有機絶縁膜の代りにケイ素を含む絶縁膜を使用することもできる。この時はケイ素を含む絶縁膜を塗布し、その上に感光膜を塗布した後、前述のスリットパターンまたは反透過膜を含むマスクを用いて写真エッチング工程を実施すれば良い。この実施例では感光膜として陽性感光膜を使用した場合について説明する。

【0098】

これについて図11乃至図14及び図8を参照して説明する。

【0099】

図11乃至図14は共通電極230上にケイ素を含む絶縁膜151を蒸着し感光膜152を塗布した後にスリットパターンまたは反透過膜を含むマスクM3を用いて露光及び現像した後の色フィルター基板を工程順序によって示した断面図である。

【0100】

図11に示されているように、ケイ素を含む絶縁膜151上に感光膜152を塗布した後、マスクM3を用いて現像して、図12に示したような厚さの異なる感光膜パターン116、117を形成する。

【0101】

この時、マスクM3はB部分に位置するスリットパターンと、A部分に位置する不透明パターンと、C部分に位置する透明パターンとを含んでいる。このようなマスクM3を用いて露光した後に現像すると、B部分に残る感光膜の厚さはA部分に残る感光膜の厚さより薄く、C部分には感光膜が残らない。

【0102】

ここで、B部分に対応するスリットパターンの代わりに反透過膜パターンを含むマスクで形成することもできる。

【0103】

陽性型感光膜の代わりに陰性型感光膜を使用する場合、A部分には透明パターンを含みC部分には不透明パターンを含むマスクを使用すれば良い。

【0104】

その次に、図13に示されているように、感光膜パターン116、117で覆われない絶縁膜151をエッチングして共通電極230が露出されるようにする。

【0105】

その次に、図14に示されているように、感光膜パターン116の下に位置する絶縁膜151が露出するまで、感光膜パターン116、117を除去すると、A部分にのみ感光膜パターン117が所定の厚さで残ることとなる。

【0106】

その次に、感光膜パターン117の残留物を除去すると、図8に示したような厚さが互いに異なる絶縁膜パターン160、170が形成される。

【0107】

前述のような本発明の第4実施例によると、色フィルター基板の共通電極をパターニングせずに感光性有機絶縁膜からなる突起パターンによるフリンジフィールドを用いて多重領域を形成するために、液晶表示装置の広視野角を確保することができ、突起パターンより厚い厚さを有する有機絶縁膜をスペーサとしてセルギャップの均一性を確保することができ、セルギャップの厚さを薄くすることができ、応答速度を向上させることができる。また、突起パターン及びスペーサを一度の写真工程で形成するので工程の数を減らすことができるという長所がある。

【0108】

図15a乃至図23bは本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板の製造工程断面図を示したものである。

【0109】

まず、薄膜トランジスタ基板の製造工程を図15a乃至19bを参照して説明する。

【0110】

図15a及び図15bに示したように、絶縁基板10上にゲート配線用導電体をスパッタリング(sputtering)などの方法で1000Å乃至3000Åの厚さで蒸着した後、マスクを用いた写真エッチング工程でパターニングしてゲート線22、ゲートパッド24、ゲート電極26を含むゲート配線22、24、26と、保持容量線21、保持電極23、25、27、保持電極連結部28、29を含む保持容量配線21、23、25、27、28、29を形成する。

【0111】

保持容量配線21、23、25、27、28、29の形状はこの実施例以外に多様な形状で形成することができる。

【0112】

その次に、図16a及び図16bに示したように、露出された全面上にゲート絶縁膜30、非晶質ケイ素層及び不純物がドーピングされた非晶質ケイ素層を化学気相蒸着法(CVD:chemical vapor deposition)などを用いて各々1500Å乃至5000Å、500Å乃至1500Å、300Å乃至600Åの厚さで順次に蒸着した後、上部の二つの層である不純物がドーピングされた非晶質ケイ素層及び非晶質ケイ素層をマスクを用いた写真エッチング工程でパターニングして抵抗性接触層52及び半導体層42を形成する。

【0113】

その次に、図17a及び図17bに示したように、データ配線用導電体または金属をスパッタリングなどの方法で1500Å乃至3000Åの厚さで蒸着した後、マスクを用いた写真エッチング工程でパターニングしてデータ線62、データパッド64、ソース電極65、ドレーン電極66を含むデータ配線62、64、65、66を形成する。

【0114】

その次に、ソース電極65及びドレーン電極66をマスクにしてその下段の抵抗性接触層52をエッチングして、ソース電極65に連結される抵抗性接触層55及びドレーン電極66に接触する抵抗性接触層56に分離する。

【0115】

その次に、図18a及び図18bに示したように、窒化ケイ素を化学気相蒸着法などを用いて蒸着したり、有機絶縁物質をスピンコーティングして3000Å以上の厚さで保護膜70を形成する。

【0116】

その次に、保護膜70及びゲート絶縁膜30をマスクを用いた写真エッチング工程でパターニングして、ドレーン電極66を露出させる第1接触孔72、データパッド64を露出させる第2接触孔74、ゲートパッド24を露出させる第3接触孔76を形成する。

【0117】

ここで、ゲート絶縁膜30形成用物質と同一な物質で保護膜70を形成した場合、二つの絶縁膜30、70を一度のエッチング工程でエッチングして接触孔72、74、76を形成することができる。また、ゲート絶縁膜30形成用物質と異なる物質で保護膜70を形成した場合、写真エッチング工程によって保護膜70を先にパターニングし、パターニングされた保護膜70をマスクにしてその下段のゲート絶縁膜30をエッチングして接触孔72、74、76を形成することができる。

【0118】

その次に、図19a及び図19bに示したように、保護膜70を含む基板の露出された全面上にITOまたはIZOのような透明導電物質層をスパッタリングなどの方法で400Å乃至500Åの厚さで蒸着する。その次に、マスクを用いた写真エッチング工程で透明導電物質層をパターニングして第1接触孔72を通じてドレーン電極66と連結される画素電極、第2及び第3接触孔74、76を通じてデータ及びゲートパッド64、24に接触する補助データ及び補助ゲートパッド84、86を形成する。

【0119】

この時、画素電極80は第1乃至第3小部分81、82、83に分離され、これら小部分は連結部85、87を通じて互いに連結されるようにパターニングする。ここで、画素電極80はこの実施例以外に多様な形状で形成されることができる。

【0120】

以下、色フィルター基板の製造工程を図20a乃至図23bを参照して説明する。

【0121】

図20a及び図20bに示したように、絶縁基板200上にクロム/酸化クロム二重層からなるブラックマトリックス210を形成し、赤、緑、青の色フィルター220を形成する。

【0122】

その次に、図21に示したように、色フィルター220上にオーバーコート膜225を形成し、ITOまたはIZOなどの透明導電物質からなる共通電極230を基板全面に形成する。

【0123】

その次に、図22に示したように、基板全面に陽性型(positive)感光樹脂(PR)を塗布する。

【0124】

この時、使用される感光樹脂(PR)は高分子柱及び突起の材料として用いられる。また、感光樹脂の塗布は、例えば、感光樹脂(PR)を400rpmの回転速度でスピンコーティング(spin coating)して3.8μm程度の厚さで塗布する。

【0125】

その次に、図23a及び図23bに示したように、突起160及び高分子柱170を形成する。ここで、突起160及び高分子柱170は基板の多様な位置に形成されることができる。

【0126】

この時、高さが互いに異なる突起160及び高分子柱170を一つのマスクを用いて一回の写真エッチング工程で同時に形成することができる。

【0127】

この場合、突起160を形成する部分に対応するマスクのパターンは露光器の解像度より小さい幅を有するように形成し、高分子柱170を形成する部分に対応するマスクのパターンは露光器の解像度より広い幅を有するように形成するのが好ましい。このようなマスクを用いて基板に塗布された感光樹脂を露光し現像して高さの異なる突起160及び高分子柱170を同時にパターニングする。

【0128】

ここで、突起160は1.0μm〜1.2μm、高分子柱170は3.0μm〜4.5μm程度の高さで形成するのが好ましく、露光工程時の露光量は300mJ/cm2程度が好ましい。また、突起160の幅は4μm〜14μm、高分子柱170の幅は15μm〜45μm程度で形成することができる。

【0129】

その次に、適正温度で40分間ハードベークを実施して突起160及び高分子柱170が一定の強度を有するように硬化する。ハードベーク時の温度によって突起160及び高分子柱170の高さが変わるが、ここではハードベーク時の温度は200〜240℃が好ましい。

【0130】

このような方式で、感光樹脂のパターン幅及びハードベーク時の温度を調節して所望の高さの突起及び高分子柱を形成し、所望の突起及び高分子柱の高さに応ずる感光樹脂のパターン幅及びハードベークの温度は実験によるデータ及び後述する数式によって設定される。

【0131】

その次に、完成した薄膜トランジスタ基板及び色フィルター基板の接合のために次のような段階を経る。

【0132】

色フィルター基板の端部に封止剤を塗布した後、薄膜トランジスタ基板と対応させ加熱プレスして2枚の基板を接着する。

【0133】

その次に、2枚の基板の間に液晶物質を注入する。

【0134】

その次に、液晶注入状態及び液晶セル検査を実施し良品のみを選別し偏光板を付着して液晶表示装置を完成する。

【0135】

以下、パターン幅の調節及びハードベーク時の温度調節を通じて一度の露光で互いに異なる高さの突起及び高分子柱を形成することができる理由について図24乃至図28を参照して説明する。

【0136】

図24はパターン幅及びハードベーク温度による写真工程後に残留する感光樹脂パターンの高さ変化を示すグラフである。

【0137】

図24に示されているように、パターン幅を狭くするほど残留する感光樹脂パターンの高さが低くなることが分かる。

【0138】

これは露光器の解像度と関連があり、マスクのパターン幅を露光器の解像度より狭く形成すると、光の回折によって感光樹脂のマスクで光を遮断した領域にも強度が弱くなった光が入射され、現像後に残留している感光樹脂の厚さが最初の厚さより小さくなることにより発生する。

【0139】

従って、突起を形成させるマスクのパターン幅を露光器の解像度より狭くし、高分子柱を形成させるマスクのパターン幅を露光器の解像度より広くすると、露光器の解像度よりパターン幅を狭く形成した側で残留する感光樹脂の厚さが最初の厚さより小さくなるので、異なる高さを有する感光樹脂パターン、即ち、突起及び高分子柱を同時に形成することができる。

【0140】

一方、感光樹脂パターンを200℃以上でハードベークすると、パターン幅が小さい場合、残留するパターンの高さがさらに小さくなり突起に適した高さを得ることができる。

【0141】

図24に示されているように、パターン幅を4μmとして210℃でハードベークを実施した場合、突起に適した1.3μmの高さを得ることができる。また、この条件でパターン幅を10μm以上にすると、高分子柱に適した3.0μm〜3.5μmの高さを得ることができる。

【0142】

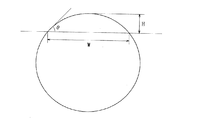

図25は写真工程後に残留する感光樹脂の断面を示す電子顕微鏡写真であり、図26は残留する感光樹脂の断面積、幅、広さなどを数式に誘導するための図面である。図27はハードベーク実施後に変わる残留感光樹脂の断面プロファイルを示した図面であり、図28は与えられた各θでパターン幅Wの変化による感光樹脂の高さHの変化を本発明の数式に代入して示したグラフである。

【0143】

図25の電子顕微鏡写真から分かるように、残留する感光樹脂は円弧の形態を有し、これを図26に対応して数式を誘導すると次の通りである。

【数式1】

【数式2】

【数式3】

【数式4】

ここで、各θはハードベーク温度による感光樹脂のテーパアングル(taper angle)であり、Hは感光樹脂の高さ、Wは解像度と関連する感光樹脂のパターン幅であり、Aは感光樹脂の断面積である。

【0144】

一方、露光及び現像が終わった感光樹脂をハードベークすると残留する感光樹脂の高さがさらに低くなり、これは図24のグラフを通じて確認することができる。従って、図27に示したように各θの変化で示すことができ、この時、各θの変化程度はハードベークの時の温度によって変わる。

【0145】

図27でθ1はハードベークの実施以前の残留する感光樹脂の断面に該当するものであり、θ2は適正温度でハードベークを実施することにより変形された感光樹脂の断面に該当するものである。つまり、ハードベーク後、残留する感光樹脂の断面がθ1からθ2に変わりながらパターンの高さが変わる。

【0146】

同じハードベーク時の温度で各θの値が同一であると仮定し、この与えられた各θでパターン幅Wによる感光樹脂の高さHの変化を上記の数式に代入して図28のグラフに示した。

【0147】

これは実験を通じた図24のグラフとよく一致する。

【0148】

上記の数式から、感光樹脂の高さ、幅、断面積、テーパアングルの四種類のうちの2種類のみ決定すると残りの2種類は従属的に決定することが分かる。従って、所望の高さの感光樹脂を前記式で決定することができる。

【0149】

前述の本発明の第5実施例のように、ドメイン分割手段である突起パターン及びセルギャップ固定のための高分子柱を一つのマスクで同時に形成することにより工程過程を減らすことができ、生産性を増大させることができる。

【0150】

図29は本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板の配置図を示したものであって、図30は図29に示した切断線XXX−XXX'によって示した薄膜トランジスタ基板の断面図を示したものである。

【0151】

絶縁基板10上に低抵抗金属物質、例えばアルミニウム系列、モリブデン系列、クロム系列、チタニウム系列からなるゲート配線22、24、26が形成されている。ゲート配線22、24、26は横方向にのびているゲート線22、ゲート線22の端に連結されており外部からのゲート信号の印加を受けてゲート線に伝達するゲートパッド24、ゲート線22に連結されている薄膜トランジスタのゲート電極26を含む。

【0152】

ゲート配線22、24、26は単一層構造以外に二重層以上の構造で形成することもできる。ゲート配線22、24、26を二重層構造で形成する場合、二つの層のうちの少なくとも一つの層は低抵抗特性を有する金属物質で形成するのが有利である。

【0153】

絶縁基板10上には絶縁物質、例えば窒化ケイ素からなるゲート絶縁膜30がゲート配線22、24、26を覆っている。

【0154】

ゲート絶縁膜30上には半導体物質、例えば非晶質ケイ素からなる半導体パターン42がゲート電極26に重畳するように形成されており、半導体パターン42上には不純物がドーピングされた半導体物質、例えばn形不純物が高濃度にドーピングされている非晶質ケイ素からなる抵抗性接触層(ohmic contact layer)55、56が形成されている。

【0155】

抵抗性接触層55、56及びゲート絶縁膜30上には半導体層との接触特性が優れており低抵抗特性を有する金属物質、例えばモリブデンまたはモリブデン合金のようなモリブデン系列からなるデータ配線62、64、65、66が形成されている。

【0156】

データ配線62、64、65、66は縦方向に形成されているデータ線62、データ線62の端に連結されており外部からのデータ信号の印加を受けてデータ線に伝達するデータパッド64、データ線62から突出して一つの抵抗性接触層55に接触して薄膜トランジスタの一部を構成するソース電極65、ソース電極65に対応して他の一つの抵抗性接触層56に接触して薄膜トランジスタの一部を構成するドレーン電極66を含む。

【0157】

データ配線62、64、65、66を含む基板の露出された全面にはアクリルレジン(Acrylic Resin)またはBCB(BenzoCycloButene)のような有機絶縁物質からなる有機絶縁膜パターン70が形成されている。この時、有機絶縁膜パターン70は薄膜トランジスタ(TFT)上で4.5〜5.5μmの高さで突出しているスペーサ71、ドレーン電極66の一部を露出させる第1接触孔72、データパッド64を露出させる第2接触孔74、ゲート絶縁膜30と共にゲートパッド24を露出させる第3接触孔76を有しており、これら部分を除いては全面にかけて2〜3μmの高さで平坦に形成されている。

【0158】

保護膜70上にはIZOまたはITOからなる画素電極82、補助データパッド84及び補助ゲートパッド86が形成されている。画素電極82は第1接触孔72を通じてドレーン電極66と電気的に連結されデータ線62から画像信号の伝達を受ける。そして、補助ゲートパッド84及び補助データパッド86は第2及び第3接触孔74、76を通じてデータパッド24及びゲートパッド64に電気的に連結されている。

【0159】

以下、本発明の第6実施例による薄膜トランジスタ基板の製造方法について図29及び図30、図31a乃至図35を参照して説明する。

【0160】

まず、図31a及び図31bに示されているように、基板10上に低抵抗特性を有する金属物質層、例えばアルミニウム系列層を蒸着し、写真エッチング工程によってパターニングしてゲート線22、ゲートパッド24、ゲート電極26を含むゲート配線22、24、26を形成する。

【0161】

その次に、図32a及び図32bに示されているように、基板10上にゲート配線22、24、26を覆う絶縁物質、例えば窒化ケイ素からなるゲート絶縁膜30を蒸着する。

【0162】

その次に、ゲート絶縁膜30上に半導体層及び不純物がドーピングされた半導体層を各々順次に積層した後、写真エッチング工程によって不純物がドーピングされた半導体層及び半導体層をパターニングして抵抗性接触層パターン52及び半導体パターン42を形成する。

【0163】

その次に、図33a及び図33bに示されているように、基板全面に半導体層との接触特性が優れており低抵抗特性を有する金属物質層、例えばモリブデン系列層を蒸着した後、写真エッチング工程によってパターニングしてデータ線62、データパッド64、ソース電極65、ドレーン電極66を含むデータ配線62、64、65、66を形成する。

【0164】

その次に、ソース電極65及びドレーン電極66をマスクとして一体形の島形の抵抗性接触層52をエッチングしてソース電極65に接触する抵抗性接触層55及びドレーン電極66に接触する抵抗性接触層56に分離する。

【0165】

その次に、図34a及び図34bに示されているように、基板全面を覆い、薄膜トランジスタ(TFT)上で突出しているスペーサ71、ドレーン電極66の一部を露出させる第1接触孔72、データパッド64を露出させる第2接触孔74、ゲート絶縁膜30と共にゲートパッド24を露出させる第3接触孔76を有する有機絶縁膜パターン70を形成する。

【0166】

このような有機絶縁膜パターン70は一つのマスクを使用する一度の写真エッチング工程を通じて形成することができる。これについて図35を参照して説明する。

【0167】

まず、データ配線62、64、65、66を含む基板の露出された全面に感光性有機絶縁物質からなる有機絶縁膜Lを塗布する。感光性有機絶縁物質はアクリルレジンまたはBCBのような有機絶縁物質と感光性物質とを混合して製造することができる。

【0168】

その次に、部分的に異なる透過率を有するマスク(図示せず)を通じて感光性有機絶縁膜Lに光を照射する。この時、光透過量を調節するために主にスリット(slit)または格子形態のパターン、あるいは半透明膜が部分的にパターン化されているマスクを使用する。この時、スリットの間に位置したパターンの線幅またはパターンの間の間隔、即ちスリットの幅は露光時に使用する露光器の分解能より小さいのが好ましく、半透明膜を用いる場合にはマスクを製作する時に透過率を調節するために異なる透過率を有する薄膜を用いたり厚さが異なる薄膜を用いることができる。

【0169】

この時、感光性有機絶縁膜Lで、第1、第2、第3接触孔72、74、76が形成される部分Cには光が全部露出されるマスクの露光領域が位置するようにし、スペーサ71が形成される部分Aにはマスクの非露光領域が位置するようにし、その他の部分Bはマスクのスリットパターンまたは半透明パターンが位置するようにマスクを使用する。

【0170】

このようなマスクを通じて感光性有機絶縁膜Lに光を照射するとマスクの露光領域に対応される部分Cでは高分子が完全に分解され、マスクのスリットパターンまたは半透明膜に対応される部分Bでは光の照射量が少ないので高分子が適正厚さ、例えば有機絶縁膜の厚さの半分程度のみに分解され、マスクの非露光領域に対応される部分Aでは高分子が殆ど分解されない。この時、露光時間を長くすると全ての分子が分解されるのでそのようにならないようにしなければならない。

【0171】

ここで、前述のように一つのマスクを使用する代わりに、その他の実施例として、2個のマスクを用いて有機絶縁膜に二重露光を進行することができる。

【0172】

このために、第1、第2、第3接触孔72、74、76が形成される有機絶縁膜部分Cを露光する第1マスクを用いる第1露光工程と、スペーサが形成される有機絶縁膜部分Aを除いた残りの部分B、Cを露光する第2マスクを用いる第2露光工程とをそれぞれ進行した後、現像して有機絶縁膜パターン70を形成することができる。この時、第2露光工程で有機絶縁膜が全部分解されないで適正厚さだけ露光されるように露光量を調節するのが好ましい。

【0173】

このように選択露光された有機絶縁膜を現像すると、高分子が分解されない部分のみが残り、光が少なく照射された中央部分には光が全く照射されない部分より薄い厚さの有機絶縁膜が残り、図34bに示したような有機絶縁膜パターン70を得ることができる。

【0174】

前述の実施例では光に接触されると分解されて現像過程で除去される陽性型感光性有機絶縁物質を使用して有機絶縁膜パターン70を形成した場合を例として挙げたが、光に接触されると硬化されて現像過程で露光された部分のみが残る陰性型感光性有機絶縁物質を使用して有機絶縁膜パターン70を形成することができる。この場合、第1、第2、第3接触孔72、74、76が形成される有機絶縁膜部分Cにはマスクの非露光領域が位置するようにし、スペーサ71が形成される部分Aにはマスクの露光領域が位置するようにし、その他の部分Bはマスクのスリットパターンまたは半透明パターンが位置するようにマスクを使用する。

【0175】

その次に、有機絶縁膜パターン70をマスクにしてその下段に位置するゲート絶縁膜30をエッチングしてゲートパッド24を露出させる第3接触孔76を形成する。

【0176】

その後、有機絶縁膜パターン70の光透過率を高めるために、有機絶縁膜パターンを硬化する作業を追加的に進行することができる。

【0177】

その次に、再び、図29及び図30に示されているように、IZO層またはITO層を蒸着した後、写真エッチング工程によってパターニングして第1接触孔72を通じてドレーン電極66に接触する画素電極82、第2及び第3接触孔74、76を通じてデータパッド64及びゲートパッド24に各々接触する補助データパッド84及び補助ゲートパッド86を形成する。

【0178】

その次に、後続工程を進行して薄膜トランジスタ基板の製造を完了する。

【0179】

このように、本発明の第6実施例による薄膜トランジスタ基板ではスペーサを別途の写真エッチング工程を進行せずに、有機絶縁膜に接触孔を形成するための写真エッチング工程を通じて形成するので、工程単純化に有利である。

【0180】

図36は本発明の第7実施例による薄膜トランジスタ基板の配置図を示したものであり、図37及び図38は図36に示した切断線XXXVII−XXXVII'及びXXXVIII−XXXVIII'によって各々示した断面図である。

【0181】

絶縁基板10上に低抵抗金属物質、例えばアルミニウム系列、モリブデン系列、クロム系列、チタニウム系列からなるゲート配線22、24、26、28が形成されている。ゲート配線22、24、26、28は横方向にのびているゲート線22、ゲート線22の端に連結されており外部からのゲート信号の印加を受けてゲート線に伝達するゲートパッド24、ゲート線22に連結されている薄膜トランジスタのゲート電極26を含むゲート線部22、24、26と、ゲート線22と平行な保持蓄電器用保持電極28とを含んでいる。

【0182】

保持電極28は後述する画素電極82と連結された保持蓄電器用導電体パターン68と重畳して画素の電荷保存能力を向上させる保持蓄電器をなし、後述する画素電極82及びゲート線22の重畳によって発生する保持容量が十分である場合には形成しないこともある。

【0183】

ゲート配線22、24、26、28は単一層構造以外に二重層以上の構造で形成することもできる。ゲート配線22、24、26、28を二重層構造で形成する場合、二つの層のうちの少なくとも一つの層は低抵抗特性を有する金属物質で形成するのが有利である。

【0184】

絶縁基板10上には絶縁物質、例えば窒化ケイ素からなるゲート絶縁膜30がゲート配線22、24、26、28を覆っている。

【0185】

ゲート絶縁膜30上には半導体物質、例えば、非晶質ケイ素からなる半導体パターン42、48が形成されており、半導体パターン42、48上には不純物がドーピングされている半導体物質、例えば不純物がドーピングされている非晶質ケイ素からなる抵抗性接触層パターン55、56、58が形成されている。

【0186】

抵抗性接触層パターン55、56、58上には半導体層との接触特性が優れており低抵抗特性を有する金属物質、例えばモリブデン系列からなるデータ配線62、64、65、66、68が形成されている。

【0187】

データ配線62、64、65、66、68は縦方向に形成されてゲート線22と交差するデータ線62、データ線62の端に連結されており外部からのデータ信号の印加を受けてデータ線に伝達するデータパッド64、データ線62から突出し一つの抵抗性接触層55に接触して薄膜トランジスタの一部を構成するソース電極65、ソース電極65に対応し他の一つの抵抗性接触層56に接触して薄膜トランジスタの一部を構成するドレーン電極66を含むデータ線部62、64、65、66と、保持電極28上に位置している保持軸電気用導電体パターン68とを含んでいる。

【0188】

半導体パターン42、48は薄膜トランジスタ用半導体パターン42及び保持蓄電器用半導体パターン48を含み、ソース電極65とドレーン電極66との間の領域、即ち薄膜トランジスタのチャンネル領域以外はデータ配線62、64、65、66、68及び抵抗性接触層パターン55、56、58と同一な形態を有している。つまり、保持蓄電器用半導体パターン48は保持蓄電器用導電体パターン68及び保持蓄電器用接触層パターン58と同一であるが、薄膜トランジスタ用半導体パターン42は後述されるデータ線62、データパッド64、ソース電極65、ドレーン電極66からなるデータ線部62、64、65、66とは同一であり、ソース電極65とドレーン電極66との間に位置する薄膜トランジスタのチャンネルに定義される領域をさらに含んでいる。

【0189】

ここで、抵抗性接触層パターン55、56、58は下部の半導体パターン42、48と上部のデータ配線62、64、65、66、68との接触抵抗を低くする役割を果たし、データ配線62、64、65、66、68と同一な形態を有する。この時、一つの抵抗性接触層パターン55は一体をなすデータ線62、データパッド64、ソース電極65に接触しており、他の抵抗性接触層パターン56はドレーン電極66に接触しており、他の接触層パターン58は保持蓄電器用導電体パターン68に接触している。

【0190】

データ配線62、64、65、66を含む基板の露出された全面にはアクリルレジン(Acrylic Resin)またはBCBのような有機絶縁物質からなる有機絶縁膜パターン70が形成されている。この時、有機絶縁膜パターン70は薄膜トランジスタ(TFT)上で4.5〜5.5μmの高さで突出しているスペーサ71、ドレーン電極66の一部を露出させる第1接触孔72、データパッド64を露出させる第2接触孔74、ゲート絶縁膜30と共にゲートパッド24を露出させる第3接触孔76、保持蓄電器用導電体パターン68を露出させる第4接触孔78を有しており、これら部分を除いては全面にかけて2〜3μmの高さで平坦に形成されている。

【0191】

有機絶縁膜パターン70上にはIZOまたはITOからなる画素電極82、補助ゲートパッド84、補助データパッド86が形成されている。画素電極82は第1及び第4接触孔72、78を通じてドレーン電極66及び保持蓄電器用導電体パターン68に接触する。そして、補助データパッド84及び補助ゲートパッド86は第2及び第3接触孔74、76を通じてデータパッド24及びゲートパッド64に接触している。

【0192】

以下、本発明の第7実施例による薄膜トランジスタ基板の製造方法について図39a乃至図47b、図36乃至図38を参照して説明する。

【0193】

まず、図39a、図39b、図39cに示されているように、基板10上に低抵抗特性を有する金属物質層、例えばアルミニウム系列層を蒸着し、写真エッチング工程によってパターニングしてゲート線22、ゲートパッド24、ゲート電極26、保持蓄電器用導電体パターン28を含むゲート配線22、24、26、28を形成する。

【0194】

その次に、基板10上にゲート配線22、24、26、28を覆う絶縁物質、例えば窒化ケイ素からなるゲート絶縁膜30を蒸着する。

【0195】

その次に、図40a、図40b、図40cに示されているように、ゲート絶縁膜30上に半導体層、不純物がドーピングされた半導体層、データ配線用金属層を連続的に蒸着し、この多重層を写真エッチング工程でパターニングして半導体パターン42、48と、抵抗性接触層パターン55、56、58と、データパッド64、ソース電極65、ドレーン電極66、保持蓄電器用保持電極68を含むデータ配線62、64、65、66、68とを形成する。データ配線用金属層は半導体層との接触特性が優れており低抵抗特性を有する金属物質層、例えばモリブデン系列で形成するのが好ましい。

【0196】

データ配線62、64、65、66、68の下段にはそれと同一なパターンを有する抵抗性接触層パターン55、56、58が接触しており、抵抗性接触層パターン55、56、58の下段には薄膜トランジスタ用半導体パターン42及び保持蓄電器用半導体パターン48を含む半導体パターン42、48が接触している。薄膜トランジスタ用半導体パターン42はデータ線部62、64、65、66と同一で、ソース電極65とドレーン電極66との間に位置する薄膜トランジスタのチャンネルに定義される領域をさらに含む。

【0197】

このようなデータ配線62、64、65、66、68、抵抗性接触層55、56、58、半導体パターン42、48は一つのマスクのみを用いて形成することができる。これを図41a乃至図45bを参照して説明する。

【0198】

まず、図41a及び図41bに示されているように、ゲート絶縁膜30上に半導体層40、不純物がドーピングされた半導体層50を化学気相蒸着法を用いて連続蒸着する。次いで、データ配線用金属層60を蒸着する。

【0199】

その次に、図42a及び図42bに示されているように、データ配線用金属層60上に感光膜を塗布した後、マスク(図示せず)を通じて感光膜に光を照射し、現像して感光膜パターン112、114を形成する。この時、感光膜パターン112、114はデータ配線部分Aに位置した感光膜の第1部分112が薄膜トランジスタのチャンネル部C、即ちソース電極65とドレーン電極66との間に位置した感光膜の第2部分114より厚く形成されるようにし、その他の部分Bは残留しないように形成する。感光膜の第2部分114と感光膜の第1部分112の厚さの比は後述するエッチング工程の工程条件に応じて異なるようにしなければならず、第2部分114の厚さを第1部分112厚さの1/2以下とするのが好ましい。

【0200】

このように、部分的に異なる厚さを有する感光膜パターンは部分的に異なる透過率を有する一つのマスクを用いて形成する。光透過量を調節するために主にスリット(slit)または格子形態のパターン、あるいは半透明膜を有するマスクを使用する。この時、スリットの間に位置したパターンの線幅やパターンの間の間隔、つまり、スリットの幅は露光時に使用する露光器の分解能より小さいのが好ましく、半透明膜を用いる場合にはマスクを製作する時に透過率を調節するために異なる透過率を有する薄膜または厚さの異なる薄膜を用いることができる。

【0201】

このようなマスクを通じて感光膜に光を照射すると光に直接露出される部分Cでは高分子が完全に分解され、スリットパターンまたは半透明膜に対応される部分Bでは光の照射量が少ないので高分子が完全分解されない状態であり、遮光膜で覆われた部分Aでは高分子が殆ど分解されない。この時、露光時間を長くすると全ての分子が分解されるのでそのようにならないようにしなければならない。

【0202】

このように選択露光された感光膜を現像すると、高分子分子が分解されない部分のみが残り、光が少なく照射された中央部分には光に全く照射されない部分より薄い厚さの感光膜が残る。

【0203】

その次に、図43a及び図43bに示されているように、感光膜パターン112、114をマスクにしてその他の部分Bの露出されている金属層60をエッチングして、その下部の不純物がドーピングされた半導体層50を露出させる。

【0204】

このようにすると、チャンネル部C及びデータ配線部Aにある金属層パターン67、68のみが残り、その他の部分Bの金属層が除去されその下部に位置する不純物がドーピングされた半導体層50が露出される。金属層パターン68は保持蓄電器用導電体パターンであり、金属層パターン67はソース電極65及びドレーン電極66がまだ分離されずに一体である状態で存在するデータ配線金属層である。

【0205】

その次に、図44a及び図44bに示されているように、その他の部分Bの露出された不純物がドーピングされた半導体層50及びその下部の半導体層40を感光膜の第2部分114と共に乾式エッチング方法で同時に除去する。この時のエッチングは感光膜パターン112、114、不純物がドーピングされた半導体層50、半導体層40が同時にエッチングされゲート絶縁膜30はエッチングされない条件下で行う。この時、感光膜パターン112、114と半導体層40に対するエッチング比がほぼ同一な条件でエッチングするのが好ましい。例えば、SF6及びHClの混合気体またはSF6及びO2の混合気体を用いるとほぼ同一な厚さに二つの膜をエッチングすることができる。

【0206】

感光膜パターン112、114と半導体層40に対するエッチング比が同一な場合、感光膜の第2部分114の厚さは半導体層40と不純物がドーピングされた半導体層50の厚さを合せたものと同一であるかそれより小さく形成しなければならない。

【0207】

このようにすると、チャンネル部Cに位置した感光膜の第2部分114が除去されてチャンネル部Cの金属層パターン67が露出され、その他の部分Bの不純物がドーピングされた半導体層50及び半導体層40が除去されてその下部のゲート絶縁膜30が露出される。一方、データ配線部Aの感光膜の第1部分112もエッチングされるので厚さが薄くなる。

【0208】

この段階で薄膜トランジスタ用半導体パターン42及び保持蓄電器用半導体パターン48を含む半導体パターン42、48が完成される。

【0209】

また、薄膜トランジスタ用半導体パターン42上には抵抗性接触層57が半導体パターン42と同一なパターンに形成されており、保持蓄電器用半導体パターン48上にも抵抗性接触層58が半導体パターン48と同一なパターンに形成されている。

【0210】

その次に、アッシング(ashing)を通じてチャンネル部Cの金属層パターン67表面に残っている感光膜の第2部分の残留物を除去する。

【0211】

その次に、図45a及び45bに示されているように、残っている感光膜パターンの第1部分112をマスクにしてチャンネル部Cに位置する金属層パターン67及びその下部の抵抗性接触層パターン57部分をエッチングする。

【0212】

この時、半導体パターン42の一部を除去して厚さを薄くすることができ、感光膜パターンの第1部分112も所定の厚さでエッチングされることとなる。この時のエッチングはゲート絶縁膜30がエッチングされない条件で行わなければならず、感光膜パターンの第1部分112がエッチングされてその下部のデータ配線62、64、65、66、68が露出されることがないように感光膜パターンを厚く形成するのが好ましい。

【0213】

このようにすると、金属層パターン67でソース電極65とドレーン電極66とが分離されてデータ線62、ソース電極65、ドレーン電極68が完成され、その下部の抵抗性接触層パターン55、56、58が完成される。

【0214】

その次に、図46a、図46b、図46cに示されているように、基板上に残留している感光膜パターンの第1部分112をアッシングを通じて除去する。

【0215】

その次に、基板全面を覆い、薄膜トランジスタ(TFT)上で突出しているスペーサ71、ドレーン電極66の一部を露出させる第1接触孔72、データパッド64を露出させる第2接触孔74、ゲート絶縁膜30と共にゲートパッド24を露出させる第3接触孔76、保持蓄電器用導電体パターン68を露出させる第4接触孔78を有する有機絶縁膜パターン70を形成する。

【0216】

このような有機絶縁膜パターン70は一つのマスクを用いて一度の写真エッチング工程を通じて形成することができる。これについて図47a及び図47bを参照して説明する。

【0217】

まず、データ配線62、64、65、66、68を含む基板の露出された全面には感光性有機絶縁物質からなる有機絶縁膜Lを塗布する。感光性有機絶縁物質はアクリルレジンまたはBCBのような有機絶縁物質と感光性物質とを混合して製造することができる。

【0218】

その次に、部分的に異なる透過率を有するマスク(図示せず)を通じて感光性有機絶縁膜Lに光を選択的に照射する。この時、光透過量を調節するために本発明の第1実施例による薄膜トランジスタ基板を説明する過程で言及したような部分的に異なる透過率を有するマスクを使用する。

【0219】

この時、感光性有機絶縁膜Lで、第1、第2、第3及び第4接触孔72、74、76、78が形成される部分Cには光が全部露出されるマスクの露光領域が位置するようにし、スペーサ71が形成される部分Aにはマスクの非露光領域が位置するようにし、その他の部分Bはマスクのスリットパターンまたは半透明パターンが位置するようにマスクを使用する。

【0220】

このようなマスクを通じて感光性有機絶縁膜Lに光を照射するとマスクの露光領域に対応する部分Cでは高分子が完全に分解され、マスクのスリットパターンまたは半透明膜に対応する部分Bでは光の照射量が少ないので高分子が適正厚さ、例えば有機絶縁膜の厚さの半分程度のみ分解され、マスクの非露光領域に対応する部分Aでは高分子が殆ど分解されない。この時、露光時間を長くすると全ての分子が分解されるのでそのようにならないようにしなければならない。

【0221】

ここで、一つのマスクを用いる代わりに、他の実施例として、2個のマスクを用いて有機絶縁膜に二重露光を進行することができる。

【0222】

このために、第1、第2、第3、第4接触孔72、74、76、78が形成される有機絶縁膜部分Cを露光する第1マスクを使用する第1露光工程と、スペーサが形成される有機絶縁膜部分Aを除いた残りの部分B、Cを露光する第2マスクを使用する第2露光工程をそれぞれ進行した後、現像して有機絶縁膜パターン70を形成することができる。この時、第2露光工程で有機絶縁膜が全部分解されないで適正厚さだけ露光されるように露光量を調節するのが好ましい。

【0223】

このように選択露光された有機絶縁膜を現像すると、高分子が分解されない部分のみが残り、光が少なく照射された中央部分には光に全く照射されない部分より薄い厚さの有機絶縁膜が残るようになって、図46b及び図46cに示したような有機絶縁膜パターン70を得ることができる。

【0224】

前述の実施例では光に接触されると分解されて現像過程で除去される陽性型感光性有機絶縁物質を使用して有機絶縁膜パターン70を形成した場合を例として上げたが、光に接触されると硬化されて現像過程で露光された部分のみが残るようになる陰性型感光性有機絶縁物質を使用して有機絶縁膜パターン70を形成することができる。この場合、第1、第2、第3、第4接触孔72、74、76、78が形成される有機絶縁膜部分Cにはマスクの非露光領域が位置するようにし、スペーサ71が形成される部分Aにはマスクの露光領域が位置するようにし、その他の部分Bはマスクのスリットパターンまたは半透明パターンが位置するようにマスクを使用する。

【0225】

その次に、有機絶縁膜パターン70をマスクとしてその下段に位置するゲート絶縁膜30をエッチングして、ゲートパッド24を露出させる第3接触孔76を形成する。

【0226】

その後、有機絶縁膜パターン70の光透過率を高めるために、有機絶縁膜パターンを硬化する作業を追加的に進行することができる。

【0227】

その次に、再び、図36、図37、図38に示されているように、IZO層またはIZO層を蒸着した後、写真エッチング工程によってパターニングして第1及び第4接触孔72、78を通じてドレーン電極66及び保持蓄電器用導電体パターン68に接触する画素電極82、第2及び第3接触孔74、76を通じてデータパッド64及びゲートパッド24に各々接触する補助データパッド84及び補助ゲートパッド86を形成する。

【0228】

その次に、後続工程を進行して薄膜トランジスタ基板の製造を完了する。

【0229】

このように、本発明の第7実施例による薄膜トランジスタ基板ではスペーサを別途の写真エッチング工程を進行せず有機絶縁膜に接触孔を形成するための写真エッチング工程を通じて形成するため、工程単純化に有利である。また、一つのマスクを用いてデータ配線及び半導体層を同時に形成するので、工程単純化においてさらに有利である。

【0230】

このような本発明は多様な構造の薄膜トランジスタ基板を製造することに適用することができる。

【0231】

図48は本発明の第8実施例による薄膜トランジスタ基板の配置図であり、図49は図48に示した切断線XLIX−XLIX'による薄膜トランジスタ基板の断面図である。

【0232】

本発明の第8実施例による薄膜トランジスタ基板の基本構造は保護膜70のパターン形状以外は、図19a及び図19bに示したような本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板の構造と同一である。

【0233】

本発明の第5実施例によると、薄膜トランジスタ基板にスペーサが形成されずそれに対応する色フィルター基板に形成されているが、本発明の第8実施例によると、薄膜トランジスタ基板にスペーサ71が保護膜70と共に形成されている。

【0234】

つまり、図49に示されているように、有機絶縁膜からなる保護膜70は薄膜トランジスタ(TFT)上で4.5〜5.5μmの高さで突出しているスペーサ71、ドレーン電極66の一部を露出させる第1接触孔72、データパッド64を露出させる第2接触孔74、ゲート絶縁膜30と共にゲートパッド24を露出させる第3接触孔76を有しており、これら部分以外は全面にかけて2〜3μmの高さで平坦に形成されている。

【0235】

このような保護膜70上に第1接触孔72を通じてドレーン電極66に接触する画素電極81、82、83、85、87及び第2及び第3接触孔74、76を通じてデータ及びゲートパッド64、24に接触する補助データ及び補助ゲートパッド84、86が形成されている。

【0236】

このような構造を有する薄膜トランジスタ基板に、図48で点線で示したような切除パターンを有する共通電極(図示せず)が形成された上部基板を合着して液晶表示装置を製造する。このような液晶表示装置では画素電極81、82、83、85、87のパターン及び共通電極の切除パターン(点線で示す)が液晶を分割配向する機能を果たすことにより一つの画素領域に多数の液晶ドメインを実現するので広視野角具現が可能である。

【0237】

本発明の第8実施例による薄膜トランジスタ基板の製造工程は保護膜70の形成工程以外は、本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板の製造工程と同一である。

【0238】

また、スペーサ71及び接触孔72、74、76を有する保護膜70は本発明の第6及び第7実施例による薄膜トランジスタの製造工程を通じて説明したものと同一である。

【0239】

前述のような本発明の第5、第6、第7実施例によると、スペーサを有機絶縁膜に接触孔をパターニングする過程を通じて接触孔を形成することと同時に形成するため、スペーサを形成するための写真エッチング工程、例えば感光膜塗布、感光膜露光及び現像する全ての工程を省略することができ薄膜トランジスタ基板の製造工程を単純化することができる。

【0240】

【発明の効果】

以上のように、本発明は液晶表示装置の2枚の基板に固定されるスペーサを形成するため液晶表示装置の画質を向上させると同時に輝度の変化を最小化することができる。また、本発明は有機絶縁膜を用いて有機絶縁膜パターンと共にスペーサを形成するため製造工程を単純化することができる。

【図面の簡単な説明】

【図1】本発明の第1実施例による液晶表示装置の概略的構造を示す構成図である。

【図2】本発明の第2実施例による液晶表示装置の構造を示した配置図である。

【図3】本発明の第3実施例による液晶表示装置の構造を示した配置図である。

【図4】本発明の第4実施例による液晶表示装置の断面図である。

【図5】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図6】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図7】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図8】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図9】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図10】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図11】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図12】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図13】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図14】本発明の第4実施例による液晶表示装置の色フィルター基板を製造するための製造工程図である。

【図15a】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図15b】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図16a】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図16b】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図17a】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図17b】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図18a】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図18b】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図19a】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図19b】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図20a】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図20b】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図21】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図22】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図23a】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図23b】本発明の第5実施例による液晶表示装置の薄膜トランジスタ基板及び色フィルター基板を製造するための製造工程図である。

【図24】パターン幅及びハードベーク温度によって写真工程を経た後に残留する感光樹脂パターンの高さ変化を示すグラフである。

【図25】写真工程後に、残留する感光樹脂の断面を示す電子顕微鏡写真である。

【図26】残留する感光樹脂の断面積、幅、広さなどを数式に誘導するための図面である。

【図27】ハードベーク実施後の変わる残留感光樹脂の断面プロファイルを示した図面である。

【図28】与えられた各θでパターン幅(W)の変化による感光樹脂の高さ(H)変化を本発明の数式に代入して示したグラフである。

【図29】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板の配置図を示したものである。

【図30】図29に示した切断線XXX−XXX'によって示した薄膜トランジスタ基板の断面図である。

【図31a】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図31b】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図32a】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図32b】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図33a】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図33b】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図34a】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図34b】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図35】本発明の第6実施例による液晶表示装置の薄膜トランジスタ基板を製造するための製造工程図である。

【図36】本発明の第7実施例による薄膜トランジスタ基板の配置図を示したものである。

【図37】図36に示した切断線XXXVII−XXXVII'によって示した断面図である。

【図38】図36に示した切断線XXXVIII−XXXVIII'によって示した断面図である。

【図39a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図39b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図39c】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図40a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図40b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図40c】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図41a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図41b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図42a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図42b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図43a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図43b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図44a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図44b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図45a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図45b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図46a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図46b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図46c】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図47a】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図47b】本発明の第7実施例による薄膜トランジスタ基板を製造するための製造工程図である。

【図48】本発明の第8実施例による液晶表示装置での薄膜トランジスタ基板の配置図を示したものである。

【図49】図48に示した切断線XLIX−XLIX'によって示した薄膜トランジスタ基板の断面図である。

【符号の説明】

10 第1絶縁基板

11 スイッチング素子

12 画素電極

14 下部偏光板

22 ゲート線

26 ゲート電極

62 データ線

65 ソース電極

66 ドレイン電極

80 画素電極

90 配向膜

210 ブラックマトリックス

220 色フィルタ

230 共通電極

250 配向膜

300 液晶分子

310 液晶物質層

400 上部偏光板

1000 下部基板

2000 上部基板

Claims (16)

- 第1絶縁基板上に第1切除パターンを有する画素電極が形成されている第1基板と、

前記第1絶縁基板と対向している第2絶縁基板上に共通電極が形成され、前記共通電極内または共通電極上に切除パターンまたは突起パターンで形成された第2パターンは前記第1切除パターンと互いに平行で、交互に配置されている第2基板と、

前記第1基板と第2基板との間に注入されており、負の誘電率異方性を有し、かつ電圧未印加時、垂直に配向されている液晶物質と、

前記第2パターンの端部に位置し、前記第1基板と前記第2基板との間隔を維持する第1スペーサとを含み、

前記第1切除パターンは前記画素電極の上部領域で第1方向に形成されている第1切除部と、前記画素電極の下部領域で前記第1方向と直角をなす第2方向に形成されている第2切除部と、前記画素電極の中央に位置し前記画素電極の上下辺と平行な第3切除部とを含み、

前記第2パターンは、前記画素電極の上部領域と対応する位置に前記第1方向に形成されている第1枝部と、前記画素電極の下部領域と対応する位置に前記第2方向に形成されている第2枝部と、前記画素電極の中央に対応する位置に前記画素電極の上下辺と平行な幹部と、前記画素電極の上下辺と重複する複数の横断部と、前記画素電極の左右辺と重複する第1枝端部、第2枝端部及び複数の縦断部とを含み、

前記第3切除部と前記第2パターンは部分的に重複する液晶表示装置。 - 前記第1方向は前記画素電極の辺に対して斜線方向であることを特徴とする請求項1に記載の液晶表示装置。

- 複数の前記第2枝部は前記幹部より幅が広いことを特徴とする請求項2に記載の液晶表示装置。

- 前記幹部と同一の直線上に第2スペーサを更に含むことを特徴とする請求項2に記載の液晶表示装置。

- 第1絶縁基板上に第1切除パターンを有する画素電極が形成され、前記第1切除パターンは前記画素電極の第1辺から横方向に形成されている第1切除部と、斜線方向に形成されており前記第1切除部に対して互いに対称をなしており前記第1辺から前記第1辺と対向する第2辺に接近するほど互いに間隔が狭くなる第2及び第3切除部とからなる第1基板と、

前記第1絶縁基板と対向している第2絶縁基板上に前記第1切除パターンと交互に配置されている第2切除パターンを有する共通電極が形成され、前記第2切除パターンは横方向に形成されている幹部、前記幹部からそれぞれ斜線方向に形成されており前記幹部から離れるほど互いに離れる第1及び第2枝部、及び前記第1及び第2枝部から縦方向に形成されており互いに反対方向にのびている第1及び第2枝端部を含む第4切除部と、前記第1枝部と平行な第1中央部及び前記第1中央部の両端からそれぞれ横方向及び縦方向に形成されている第1及び第2屈折部を含む第5切除部と、前記第4切除部に対して前記第5切除部と対称をなす第6切除部とからなる第2基板と、

前記第1基板と第2基板との間に注入されており、負の誘電率異方性を有し、かつ電圧未印加時、垂直に配向されている液晶物質と、

前記第1基板と前記第2基板との間隔を維持し、前記第1中央部と第1屈折部とが接する領域に位置するスペーサとを含む液晶表示装置。 - 第1基板及び第2基板と、

前記第1基板及び第2基板の間に注入されており、負の誘電率異方性を有し、かつ電圧未印加時、垂直に配向されている液晶物質と、

前記第1基板上に形成されたゲート線及びデータ線と、

前記ゲート線とデータ線に接続されたスイッチング素子と、

前記第1基板上に形成された複数の画素電極と、

前記第2基板上に配列され、前記ゲート線に対して斜線方向に形成された複数の本体部と、前記画素電極のいずれか1辺に沿って複数の前記本体部から延長された複数の枝部とを備える複数のパターンと、

2つの隣接する複数のパターンの一部の枝部の間の空間に隣接した位置に形成される第1スペーサとスイッチング素子と、

を備え、前記第1基板は、画素電極上に形成された複数の切除パターンまたは突起パターンを備えており、前記複数の切除パターンまたは突起パターンと前記本体部とが交互に形成されている、液晶表示装置。 - 前記第1スペーサは2つの隣接する複数のパターンの枝部の間の空間に隣接する外側及び本体部の端部に形成されている、請求項6に記載の液晶表示装置。

- 前記第2基板上に配列され前記本体部のうちの一つから延長された幹をさらに備え、前記幹と切除パターンの1つとは同一の直線上に形成されている、請求項6に記載の液晶表示装置。

- 前記第1基板は画素電極の1辺または画素電極の中央部に配列された第1保持配線をさらに備えている、請求項8に記載の液晶表示装置。

- 前記第1基板は前記第1保持配線から延長され前記データ線に平行に配列された第2保持配線を更に含む、請求項9に記載の液晶表示装置。

- 前記幹に隣接する位置に形成される第2スペーサをさらに備える、請求項8に記載の液晶表示装置。

- 本体部の一部は直線形状であり、本体部の他の部分はシェブロン形状であり、シェブロン形状の本体部から延長された幹をさらに備える、請求項6に記載の液晶表示装置。

- 前記第1基板は、前記画素電極の1辺または前記画素電極の中央部に配列された第1保持配線をさらに備えている、請求項12に記載の液晶表示装置。

- 前記第1基板は、前記第1保持配線から延長され、前記データ線に平行に配列された第2保持配線を更に含む、請求項13に記載の液晶表示装置。

- 前記第2基板上であって前記幹に隣接する位置に形成される第2スペーサをさらに備える、請求項12に記載の液晶表示装置。

- 前記幹が形成された本体部と、前記幹と同一の直線上の切除パターンは、部分的に重複する、請求項8に記載の液晶表示装置。

Applications Claiming Priority (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR2000-47001 | 2000-08-14 | ||

| KR1020000047001A KR100670062B1 (ko) | 2000-08-14 | 2000-08-14 | 액정 표시 장치용 색 필터 기판 및 그 제조 방법 |

| KR2001-1791 | 2001-01-12 | ||

| KR1020010001791A KR100345961B1 (en) | 2001-01-12 | 2001-01-12 | Liquid crystal display with wide viewing angle |

| KR2001-47318 | 2001-08-05 | ||

| KR1020010047318A KR20030013035A (ko) | 2001-08-06 | 2001-08-06 | 수직 배향형 액정 표시 장치와 그 색 필터 기판의 제조 방법 |

| KR1020010047489A KR20030013151A (ko) | 2001-08-07 | 2001-08-07 | 박막 트랜지스터 기판의 제조 방법 |

| KR2001-47489 | 2001-08-07 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002122869A JP2002122869A (ja) | 2002-04-26 |

| JP2002122869A5 JP2002122869A5 (ja) | 2008-07-17 |

| JP4298189B2 true JP4298189B2 (ja) | 2009-07-15 |

Family

ID=39274355

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001246288A Expired - Lifetime JP4298189B2 (ja) | 2000-08-14 | 2001-08-14 | 液晶表示装置及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (12) | US7057695B2 (ja) |

| JP (1) | JP4298189B2 (ja) |

| TW (1) | TW573190B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7679684B2 (en) | 2004-02-10 | 2010-03-16 | Panasonic Corporation | White balance adjusting device and video display device |

Families Citing this family (96)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW573190B (en) * | 2000-08-14 | 2004-01-21 | Samsung Electronics Co Ltd | Liquid crystal display and fabricating method thereof |

| KR100345961B1 (en) * | 2001-01-12 | 2002-08-01 | Samsung Electronics Co Ltd | Liquid crystal display with wide viewing angle |

| KR100720093B1 (ko) * | 2000-10-04 | 2007-05-18 | 삼성전자주식회사 | 액정 표시 장치 |

| JP2002141512A (ja) * | 2000-11-06 | 2002-05-17 | Advanced Display Inc | 薄膜のパターニング方法およびそれを用いたtftアレイ基板およびその製造方法 |

| JP3992922B2 (ja) * | 2000-11-27 | 2007-10-17 | シャープ株式会社 | 液晶表示装置用基板及びその製造方法及びそれを備えた液晶表示装置 |

| KR100413668B1 (ko) * | 2001-03-29 | 2003-12-31 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이기판 제조방법 |

| US6841797B2 (en) * | 2002-01-17 | 2005-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device formed over a surface with a drepession portion and a projection portion |

| KR20030078355A (ko) * | 2002-03-29 | 2003-10-08 | 삼성전자주식회사 | 수직 배향형 액정 표시 장치 |

| JP2004118200A (ja) * | 2002-09-26 | 2004-04-15 | Samsung Electronics Co Ltd | 液晶表示装置用表示板及びその製造方法とこれを利用した液晶表示装置 |

| TWI263091B (en) * | 2003-02-27 | 2006-10-01 | Innolux Display Corp | A black matrix, color filter and method for manufacturing the same, liquid crystal display |

| KR100945579B1 (ko) * | 2003-03-17 | 2010-03-08 | 삼성전자주식회사 | 표시 장치용 표시판 및 그의 제조 방법과 그 표시판을포함하는 액정 표시 장치 |

| JP4505192B2 (ja) * | 2003-03-31 | 2010-07-21 | シャープ株式会社 | 液晶パネルの製造方法 |

| TWI256514B (en) * | 2003-04-04 | 2006-06-11 | Innolux Display Corp | In-plane switching mode LCD |

| CN1322361C (zh) * | 2003-04-18 | 2007-06-20 | 鸿富锦精密工业(深圳)有限公司 | 横向电场液晶显示器 |

| JP2004341465A (ja) * | 2003-05-14 | 2004-12-02 | Obayashi Seiko Kk | 高品質液晶表示装置とその製造方法 |

| KR100968566B1 (ko) * | 2003-07-24 | 2010-07-08 | 삼성전자주식회사 | 액정 표시 장치 및 이에 포함된 표시판의 제조 방법 |

| KR100995020B1 (ko) * | 2003-12-27 | 2010-11-19 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| KR101012718B1 (ko) * | 2003-12-30 | 2011-02-09 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이기판 제조방법 |

| KR101121211B1 (ko) | 2004-02-17 | 2012-03-23 | 치 메이 옵토일렉트로닉스 코포레이션 | Lcd 장치, 컬러 필터 기판, 및 돌출 구조체, 및 이들의제조방법 |

| KR100984363B1 (ko) * | 2004-03-31 | 2010-09-30 | 삼성전자주식회사 | 액정 표시 장치 및 그 제조 방법 |

| TWI261716B (en) * | 2004-05-13 | 2006-09-11 | Quanta Display Inc | Liquid crystal display apparatus and fabrication thereof |

| WO2005116745A1 (en) * | 2004-05-27 | 2005-12-08 | Sharp Kabushiki Kaisha | Active matrix substrate, method for correcting a pixel deffect therein and manufacturing method thereof |

| KR101090252B1 (ko) * | 2004-09-24 | 2011-12-06 | 삼성전자주식회사 | 박막 트랜지스터 표시판 및 그의 제조 방법 |

| KR101018754B1 (ko) * | 2004-10-04 | 2011-03-04 | 삼성전자주식회사 | 액정 표시 장치 및 영상 신호 보정 방법 |

| KR20060104707A (ko) * | 2005-03-31 | 2006-10-09 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그 제조방법 |

| KR100971089B1 (ko) * | 2005-05-31 | 2010-07-16 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| CN100371798C (zh) * | 2005-06-02 | 2008-02-27 | 友达光电股份有限公司 | 显示面板与其中的彩色滤光基板及其制造方法 |

| TWI281064B (en) * | 2005-09-29 | 2007-05-11 | Au Optronics Corp | Array substrate, display devices using the same and methods for assembling the same |

| TWI338172B (en) * | 2005-12-30 | 2011-03-01 | Au Optronics Corp | Method of forming spacers and alignment protrusions simultaneously on color filter substrate |

| KR101229053B1 (ko) * | 2006-05-15 | 2013-02-04 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그의 제조 방법 |

| KR101274025B1 (ko) * | 2006-05-18 | 2013-06-12 | 삼성디스플레이 주식회사 | 표시패널 |

| TWM303386U (en) * | 2006-05-19 | 2006-12-21 | Wintek Corp | Multi-domain vertically aligned liquid crystal display |

| US20070285608A1 (en) * | 2006-06-13 | 2007-12-13 | Au Optronics Corporation | Placement of spacers in a liquid crystal display panel |

| KR20080001941A (ko) * | 2006-06-30 | 2008-01-04 | 삼성전자주식회사 | 표시패널 |

| KR20080010159A (ko) * | 2006-07-26 | 2008-01-30 | 삼성전자주식회사 | 액정 표시 장치 |

| TWI383224B (zh) * | 2007-01-10 | 2013-01-21 | Chimei Innolux Corp | 液晶顯示面板及其基板之製作方法以及液晶顯示裝置、液晶顯示面板及其基板 |

| TWI361291B (en) | 2007-03-19 | 2012-04-01 | Au Optronics Corp | Color filter and black matrix thereof |

| TWI398689B (zh) * | 2007-03-20 | 2013-06-11 | Au Optronics Corp | 液晶顯示面板 |

| TWI344035B (en) * | 2007-08-02 | 2011-06-21 | Au Optronics Corp | Multi-domain liquid crystal display |

| KR20090026576A (ko) * | 2007-09-10 | 2009-03-13 | 삼성전자주식회사 | 표시 장치 및 그 제조 방법 |

| US8154703B2 (en) * | 2007-10-23 | 2012-04-10 | Toshiba Matsushita Display Technology Co., Ltd. | Liquid crystal display panel |

| TWI362544B (en) | 2007-11-07 | 2012-04-21 | Au Optronics Corp | Liquid crystal display panel and manufacturing method thereof |

| ES2694573T3 (es) * | 2007-11-21 | 2018-12-21 | Cosmosid Inc. | Sistema de identificación de genomas |