JP4201436B2 - 多層配線基板の製造方法 - Google Patents

多層配線基板の製造方法 Download PDFInfo

- Publication number

- JP4201436B2 JP4201436B2 JP19969099A JP19969099A JP4201436B2 JP 4201436 B2 JP4201436 B2 JP 4201436B2 JP 19969099 A JP19969099 A JP 19969099A JP 19969099 A JP19969099 A JP 19969099A JP 4201436 B2 JP4201436 B2 JP 4201436B2

- Authority

- JP

- Japan

- Prior art keywords

- double

- sided circuit

- hole

- solder

- circuit board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4611—Manufacturing multilayer circuits by laminating two or more circuit boards

- H05K3/4614—Manufacturing multilayer circuits by laminating two or more circuit boards the electrical connections between the circuit boards being made during lamination

- H05K3/462—Manufacturing multilayer circuits by laminating two or more circuit boards the electrical connections between the circuit boards being made during lamination characterized by laminating only or mainly similar double-sided circuit boards

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0302—Properties and characteristics in general

- H05K2201/0305—Solder used for other purposes than connections between PCB or components, e.g. for filling vias or for programmable patterns

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09536—Buried plated through-holes, i.e. plated through-holes formed in a core before lamination

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/44—Manufacturing insulated metal core circuits or other insulated electrically conductive core circuits

- H05K3/445—Manufacturing insulated metal core circuits or other insulated electrically conductive core circuits having insulated holes or insulated via connections through the metal core

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S428/00—Stock material or miscellaneous articles

- Y10S428/901—Printed circuit

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T156/00—Adhesive bonding and miscellaneous chemical manufacture

- Y10T156/10—Methods of surface bonding and/or assembly therefor

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24273—Structurally defined web or sheet [e.g., overall dimension, etc.] including aperture

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24802—Discontinuous or differential coating, impregnation or bond [e.g., artwork, printing, retouched photograph, etc.]

- Y10T428/24917—Discontinuous or differential coating, impregnation or bond [e.g., artwork, printing, retouched photograph, etc.] including metal layer

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/26—Web or sheet containing structurally defined element or component, the element or component having a specified physical dimension

- Y10T428/266—Web or sheet containing structurally defined element or component, the element or component having a specified physical dimension of base or substrate

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/31504—Composite [nonstructural laminate]

- Y10T428/31678—Of metal

- Y10T428/31681—Next to polyester, polyamide or polyimide [e.g., alkyd, glue, or nylon, etc.]

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、多層配線基板の製造方法に関するものである。

【0002】

【従来の技術】

近年の電子機器の小型化,高性能化に伴い、電子機器を構成する半導体装置およびこれを実装する多層配線基板には、小型薄型化,高性能化,高信頼性が要求されている。これらの要求を受けて、実装方法はピン挿入型パッケージから表面実装型パッケージへと移行してきており、最近では半導体素子を直接プリント基板に実装するベアチップ実装と呼ばれる実装方法が研究されている。また、半導体素子の多ピン化に伴い、これを搭載する基板の多層化の必要性が増している。この多層化の方法として、基体の片面もしくは両面に、感光性樹脂を用いた絶縁層と、めっきや蒸着により形成した導体層を交互に積み重ねたビルトアップ方式の多層配線基板が提案されている。ところが、このものでは、製造工程が複雑で工程数が多いこと、しかも歩留りが低いことや納期がかかること等の問題があった。また、ガラスエポキシ片面銅張り積層板の片面(銅張り面)に電導性ペーストをディスペンサー等により突起として形成し、接着シートと銅箔を重ねて加圧し、それを繰り返すことにより多層化する方法も提案されている(特開平8−288649号公報)。しかしながら、このものでは、接続の信頼性,接続抵抗等の面に問題があるうえ、ファイン回路への応用が困難であり、しかも多層化するために層数の分だけプレスを繰り返す必要があり、製造に時間がかかる等の種々の問題があった。

【0003】

一方、ベアチップ実装では、熱膨張係数:3〜4ppm/℃のシリコンチップを熱膨張係数:10〜20ppm/℃のプリント基板上に直接接着剤を介して接着するため、両者の熱膨張の差により応力がかかり、接続信頼性が低下するという問題が生じている。また、上記応力は接着剤にクラックを生じさせて耐湿性を低下させる等の問題をも引き起こしている。このような応力を緩和するために、接着剤の弾性率を下げて応力の拡散効果を図る方法等も実施されているが、これらの方法によっても、接続信頼性を充分に確保することができず、さらに高い接続信頼性を確保するには、基体自体の熱膨張係数を下げることが必要不可欠となっている。

【0004】

このような背景の中、本発明らは、メタルコアを基体とした有機高分子樹脂からなる絶縁層の両面に配線導体を設け、これら表裏両面の配線導体をスルーホールにより電気的に接続してなる低熱膨張両面回路基板を複数枚用意し、これら両面回路基板を接着剤層を介して積層一体化した多層配線基板およびその製造方法を提案している(特願平9−260201号公報)。

【0005】

【発明が解決しようとする課題】

しかしながら、上記多層配線基板を構成する複数の両面回路基板において、その表裏両面の配線導体を電気的に接続するスルーホールは、温度サイクル試験等の環境加速試験においてスルーホール内部もしくはスルーホールコーナー部に亀裂が生じる等信頼性に問題がある。このため、上記スルーホールのめっき厚みを厚くすることにより信頼性を向上させることが考えられるが、この場合には、エッチングによる回路形成工程において微細配線を設けることができない。一方、微細配線を形成するためには、表裏両面の導体層の厚みを小さくする必要があるが、スルーホールの信頼性は低下する。しかも、上記複数の両面回路基板を接着剤層を介して積層一体化する工程において、隣り合う(積み重なる)2つの両面回路基板の配線導体を半田製導電体により電気的に接続することを行っているが、上記両面回路基板のスルーホール上に半田製導電体を設けることができないため、配線の自由度が大きく阻害されている。

【0006】

本発明は、このような事情に鑑みなされたもので、熱膨張率が極めて小さく、しかも、接続信頼性が高く、配線の自由度が大きい多層配線基板の製造方法の提供をその目的とする。

【0007】

【課題を解決するための手段】

上記の目的を達成するため、本発明の多層配線基板の製造方法は、メタルコアを基体とした有機高分子樹脂からなる絶縁層の両面に配線導体が設けられこれら両配線導体が低融点金属が充填されたビアホールにより電気的に接続された複数の両面回路基板が、接着剤層を介して積層一体化され、上記接着剤層には、これを挟む2つの両面回路基板の配線導体に当接する部分のうち、上記2つの両面回路基板の少なくとも1つのビアホールに対面する位置に孔が穿設され、上記穿孔部に半田製導電体が設けられ、上記半田製導電体により上記2つの両面回路基板の配線導体が電気的に接続されている多層配線基板を製造する方法であって、メタルコアを基体とした有機高分子樹脂からなる絶縁層を有し上記メタルコアの所定の位置に孔が開けられた基材を準備し、その基材の上記孔に対応する部分に、上記孔の内周面と離間するよう上記孔より小さいビアホールを開けてこのビアホールに低融点金属粉末もしくはペースト状低融点金属をスクリーン印刷により供給しプレスにより圧入し、この圧入後に上記基材の両面に配線導体を設け両面回路基板を形成する工程と、上記両面回路基板のビアホールに対応する位置に開孔した接着シートを準備する工程と、上記両面回路基板のビアホールに上記接着シートの開孔部を位置合わせした状態で上記両面回路基板に接着シートを仮接着する工程と、接着シート仮接着後に各接着シートの開孔部に印刷により半田ペーストを充填し加熱溶融させて半田バンプを形成する工程と、半田バンプ形成後に上記両面回路基板の配線導体が所定の電気的接続を行えるよう位置合わせして上記両面回路基板を複数枚積み重ね加熱加圧して全体を一体化させる工程を備えているという構成をとる。

【0008】

すなわち、本発明者らは、熱膨張率が極めて小さく、しかも、接続信頼性が高く、配線の自由度が大きい多層配線基板を得るため、一連の研究を行った結果、メタルコアを基体とし、かつ、表裏両面の配線導体を低融点金属を充填したビアホールで電気的に接続すると、熱膨張率が極めて小さく、しかも、接続信頼性が高く、配線の自由度が大きい多層配線基板を得ることができることを見出し、本発明に到達した。本発明で得られる多層配線基板のように、メタルコアを基体とすることにより、低熱膨張両面回路基板を得ることができ、これらを多層に積層一体化することにより、低熱膨張多層配線基板を得ることができる。また、本発明で得られる多層配線基板のように、スルーホールを設ける代りに、低融点金属を充填したビアホールを設けると、温度サイクル試験等の環境加速試験においても内部やコーナー部に亀裂が生じず、接続信頼性が高い。また、低融点金属を充填したビアホール上に半田製導電体を設けて、積み重なる(上下に隣り合う)2つの両面回路基板の配線導体を電気的に接続することができるため、配線の自由度が大きい。また、本発明では、両面回路基板に接着シートを位置合わせして仮接着し、この接着シートに開けた開孔部に半田バンプを形成したのち、各両面回路基板を位置合わせして積重し加熱加圧して全体を一体化させているため、一回の加熱加圧により複数の両面回路基板を一体化することができる。と同時に、配線導体の層数が何層であっても、上記一回の加熱加圧により各配線導体間の電気的接続が行える。本発明において、「両面回路基板のビアホールに対応する位置に開孔した接着シートとを準備する」とは、接着シートを両面回路基板上に載せたのち開孔する場合を含む意味である。

【0009】

また、本発明において、上記両面回路基板を製造する際に、メタルコアを基体とした有機高分子樹脂からなる絶縁層の両面に導体層が設けられ上記メタルコアの所定位置に孔が開けられた基材を準備する工程と、上記孔に対応する上記基材の部分に、上記孔より小さい貫通孔を開ける工程と、上記貫通孔に低融点金属を充填する工程と、上記充填後に上記基材の両面にめっきを行い低融点金属で上記基材の両面の導体層を電気的に接続する工程と、上記めっき後に上記両面の導体層に回路を形成する工程とを設けるようにした場合には、上記基材の貫通孔に充填した低融点金属に直接めっきを行い、表裏両面の導体層を電気的に接続することができ、薄い導体層にすることができる。

【0010】

つぎに、本発明を詳しく説明する。

【0011】

本発明により製造される多層配線基板を構成する両面回路基板において、絶縁層として用いられる有機高分子材料としては、ポリイミド系樹脂が好適に用いられるが、これに限定するものではなく、ポリエーテルイミド,ポリエーテルサルフォン,エポキシ系等が用いられる。また、上記絶縁層の表裏両面の配線導体を構成する金属材料としては、銅が好適に用いられるが、これに限定するものではなく、金,銀等が用いられる。

【0012】

また、絶縁層にビアホール(貫通孔)を開ける手段としては、孔の大きさにより適切な方法を選択すればよいが、ドリル,パンチ,レーザー等が挙げられる。また、貫通孔を充填する低融点金属としては、Sn,Pb,Ag,Bi,Zn,Sb,Cuから選ばれた半田製導電体、例えば、Sn−Pb系,Sn−Ag系,Sn−Sb系,Sn−Bi系,Sn−Ag−Bi系,Sn−Zn系,Sn−Cu系等半田組成に限定されず、基板に求められる耐熱性に応じて最適であるものを選択すればよい。

【0013】

上記貫通孔内への低融点金属の充填においては、この低融点金属が上記貫通孔の全空間を満たすように充填すればよい。上記低融点金属の充填法としては、例えば、過度量の低融点金属粉末、もしくは必要に応じて有機剤と混合しペースト状とした低融点金属材料を上記貫通孔上部に印刷したのちに上面からプレスにより圧入する方法が挙げられる。さらに、融点以上の温度で加熱加圧することにより充填を確実なものとすることができる。また、必要に応じて、上記低融点金属の過度量を上記両面基板の表裏両面を研磨し、取り除いてもよい。

【0014】

上記貫通孔内に低融点金属が充填された両面基板における回路形成は、電解めっき,パターニングにより行う。回路層の厚みは、36μm以下に設定され、好ましくは18μm以下がよい。この範囲以上では、回路配線の微細化が難しい。また、パターニング後に低融点金属の融点以上の温度で加熱加圧して回路層と金属接合を図ることにより電気的接続を確実なものとする。また、予め接着剤層に貫通孔を設け、低融点金属を充填したのち、この接着剤層の表裏両面に銅箔を貼り合わせてパターニングを行ってもよい。もしくは、上記貫通孔を設けた接着剤層に低融点金属を充填したのち、無電解めっき,蒸着,電解めっき等を組み合わせることにより回路形成を行ってもよい。このように、上記貫通孔に低融点金属を充填した場合には、低融点金属に直接めっきを施すことができるという利点がある。

【0015】

基板の低熱膨張化を実現するために用いられる芯材としては、Fe,Ni,Cr,Al,Ti,Cu,Coあるいはこれらを含む合金箔、もしくはセラミック材料が用いられる。上記金属箔もしくはセラミック材料は、導体層および絶縁層の膨張を抑制する働きをするため、それ自体の熱膨張率は充分に小さい必要がある。芯材がNi−Fe系合金箔の場合、その比率により熱膨張率が変化するため、Ni含有率(重量%)は31〜50重量%、好ましくは31〜45重量%の範囲が好適に用いられる。この範囲以上もしくは以下であると、熱膨張係数が大きく、チップと同等の熱膨張係数を得られない。また、上記金属箔の厚みは、10〜300μm、好ましくは、10〜200μm、さらに好ましくは、10〜100μmの範囲がよい。この厚みより小さいと、回路基板とシリコンチップの熱膨張差を抑えることができない。

【0016】

上記両面回路基板を多層化するには、上記両面回路基板の必要な場所に対応する位置に開孔した接着シートを、上記両面回路基板の両面もしくは片面に位置合わせして仮接着し、上記開孔部に印刷で半田ペーストを入れ、加熱溶融させて半田バンプを形成した上記半田バンプ付き両面回路基板を位置合わせして複数枚重ね、加熱加圧し一体化させることにより実現できる。ここで、上記開孔部は、両面回路基材の表裏両面の配線導体を電気的に接続しているビア上回路においても適用することができる。

【0017】

上記接着シートは積層一体化後に絶縁層となるため、これを構成する接着剤としては、耐熱性,電気的特性等からポリイミド系,エポキシ系またはその混合系等が好ましい。上記接着シートの厚みとしては、0.01mmから1.0mm程度とするのがよい。この範囲より小さいと作業性が悪い。この範囲以上であると半田ペーストがうまく上記開孔部に充填されず信頼性を低下させる原因となる。上記接着シートに孔を開ける手段としては、孔の大きさにより適切な方法を選択すればよいが、例えば、ドリル,パンチ,レーザー等が挙げられる。

【0018】

上記接着シートを仮固定する工程において、上記低熱膨張両面回路基板の両面もしくは片面の任意の位置に、開孔した接着シートを熱プレスを用いて仮接着すればよい。また、予め接着シートを上記両面回路基板の両面もしくは片面に仮接着したのち、レーザーを用いて開孔してもよい。レーザーとしては、炭酸ガス,エキシマ,YAG等が好適に用いられる。

【0019】

上記半田バンプを形成するにあたり、半田ペーストは一般に市販されているものが用いられるが、半田粒子の大きさは100μm以下、好ましくは50μm以下、さらに好ましくは10μm以下に設定される。また、半田組成は特に限定されず、基板に求められる耐熱性に応じて選択すればよい。積層後の半田バンプは対局電極に接触して導通されるが、必要であれば、半田の融点以上に基板を加熱して金属接合させてもよい。この金属接合させる方法は、加熱加圧による基板の一体化と同時に行うか、もしくは一体化したのちに再度加熱しても良い。

【0020】

【発明の実施の形態】

つぎに、本発明の実施の形態を図面にもとづいて説明する。

【0021】

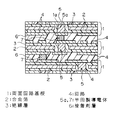

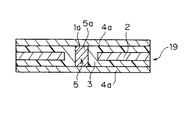

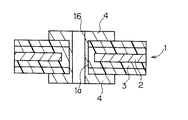

図1は本発明により製造される多層配線基板の一実施の形態を示している。図において、1はNi−Fe系合金箔2を基体としたポリイミド樹脂からなる絶縁層3の表裏両面に銅箔からなる回路(配線導体)4が形成された両面回路基板である。この実施の形態では、3枚の両面回路基板1が用いられており、これにより、多層配線基板として6層配線基板が作製されている。5は上記各両面回路基板1に穿設された貫通孔(ビアホール)1aに半田製導電体5aを充填してなるビアであり、表裏両面の回路4を電気的に接続している。6は上記各両面回路基板1同士を接着するポリイミド系接着剤層である。7は積み重なる(上下に隣り合う)2つの両面回路基板1の回路4を電気的に接続する半田製導電体である。

【0022】

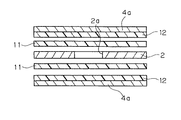

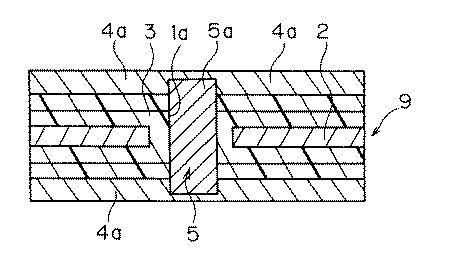

上記両面回路基板1を、つぎのようにして製造することができる。すなわち、まず、図2に示すように、Ni−Fe系合金箔2の所定位置(半田製導電体5aを充填するビア5を設ける位置)に孔2aを開け、ついで、Ni−Fe系合金箔2の表裏両面からポリイミド系接着シート11(後述する基材8の絶縁層3となる)を用いて銅箔からなる導体層4aを張り合わせ、図3に示すような基材8を作製する(図2において、12は導体層4aの片面に形成したポリイミド系樹脂層である)。つぎに、図4に示すように、上記基材8のNi−Fe系合金箔2の開孔部2aに対応する部分に、この開孔部2aより小さい貫通孔1aを開ける。つぎに、図5に示すように、この貫通孔1aに半田製導電体5aを充填したのち、表裏両面の導体層4aに電解銅めっきを行い、表裏両面の導体層4aを電気的に接続する(図6参照)。このようにして得られた基材9の熱膨張率は芯材の材料であるNi−Fe系合金に支配されているため、Ni−Feの比率や箔の厚みを変えることにより上記熱膨張率を調節することができる。つぎに、図6に示す基材9の表裏両面の導体層4aに回路4を形成して両面回路基板1(図7参照)を作製する。

【0023】

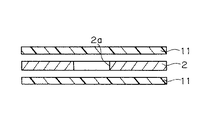

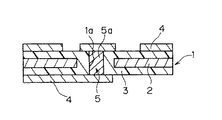

また、上記両面回路基板1を、つぎのようにして製造することができる。すなわち、まず、図8に示すように、Ni−Fe系合金箔2の所定位置(半田製導電体5aを充填するビア5を設ける位置)に孔2aを開け、ついで、Ni−Fe系合金箔2の表裏両面からポリイミド系接着シート11(後述する基材18の絶縁層3となる)を貼り合わせ、図9に示すような基材18を作製する。つぎに、図10に示すように、上記基材18のNi−Fe系合金箔2の開孔部2aに対応する部分に、この開孔部2aより小さい貫通孔1aを開ける。つぎに、図11に示すように、この貫通孔1aに半田製導電体5aを充填したのち、表裏両面から、銅箔からなる導体層4aを貼り合わせ、表裏両面の導体層4aを電気的に接続する(図12参照)。ここで、半田製導電体5aの融点以上で加熱加圧することにより接続を確実なものにする。つぎに、図12に示す基材19の表裏両面の導体層4aに回路4を形成して両面回路基板1(図13参照)を作製する。

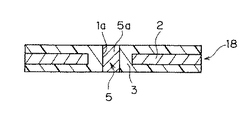

【0024】

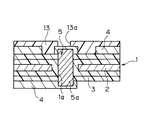

上記多層配線基板を、つぎのようにして製造することができる。すなわち、まず、ポリイミド樹脂からなる絶縁層3の表裏両面に銅箔よりなる回路4が形成された3枚の両面回路基板1(図7もしくは図13参照)と、ポリイミド系接着剤からなる2枚の接着シート(図14参照)13とを準備する。ついで、図15に示すように、上記各接着シート13を(3枚のうちの)2枚の両面回路基板1の上面に、各接着シート13の開孔部13aを各両面回路基板1の回路4の所定位置(図1の半田製導電体7を設ける位置)に位置合わせして仮接着する。つぎに、図16に示すように、上記各接着シート13の開孔部13aにスクリーン印刷により半田ペーストを入れ、加熱溶融させて各両面回路基板1の回路4上に半田バンプ14を形成する。つぎに、半田バンプ14を設けた2枚の両面回路基板1と、回路4を形成しただけの1枚の両面回路基板1をそれぞれ位置合わせして複数枚重ねたのち(図17参照)、加熱加圧し一体化させる。この状態では、各接着シート13は接着剤層6となり、各半田バンプ14は半田製導電体7となる。これにより、3枚の両面回路基板1が積層一体化された6層配線基板を得ることができる。

【0025】

上記のように、この実施の形態では、一回の加熱加圧により3枚の両面回路基板1の一体化が行えると同時に、6層間の電気的接続が行える。しかも、2層の回路4に対して、1層の割合でNi−Fe系合金箔2が配設されているため、銅箔で回路4を構成する場合にも、6層配線基板全体の熱膨張率を低くすることができ、極めて高い接続信頼性を得ることができる。また、6層の電気的接続(6層間の電気的接続)には、いずれも半田製導電体5a,7を用いているため、接続抵抗が低く、信頼性の高い接続が行える。さらに、各半田製導電体7の接合部の位置は、ビア5の半田製導電体5aの影響を受けず、任意の位置に配置できるため、設計の自由度が上がり、高密度配線が実現できる。

【0026】

以下、実施例により、本発明の効果を示す。

【0027】

【実施例1】

所定位置に直径150μmのパンチで300μmピッチにて孔2aを開けた厚み50μmの36アロイ箔2(Ni:36重量%,Fe:64重量%、熱膨張係数1.5ppm/℃)の表裏両面に、厚み18μmの銅箔4aを厚み35μmのポリイミド系接着シート11(新日鐡化学社製:SPB−035A)を用いて加圧加熱接着(40kg/cm2 、200℃、60min)し、低熱膨張両面基板8を作製した(図3参照)。つぎに、36アロイ箔2の孔2aと同じ位置に直径100μmのパンチを用いて貫通孔1aを開けた(図4参照)。上記貫通孔1a上部にメタルマスク(直径200μm,厚み100μm)を用いて、半田粉末(平均粒径10μm)をスクリーン印刷したのち、プレス(100kg/cm2 、30℃、5min)により圧入し、過度量の半田をバフ研磨により取り除くことにより半田製ビア5を設けた(図5参照)。そののち、めっきの厚み10μmの電解銅めっきを行い(図6参照)、従来のエッチング法により表裏両面の銅箔4aに回路4を形成して両面回路基板1を作製した(図7参照)。

【0028】

上記方法により製造した低熱膨張両面回路基板1に対して、直径150μmのパンチで孔13aを開けたポリイミド系接着シート13(新日鐡化学社製:SPB−035A)(図14参照)を所定の位置に合わせて載せ、その状態で加熱加圧接着(20kg/cm2 、175℃、30min)した(図15参照)。つぎに、接着シート13の開孔部13aに半田ペースト(タムラ化研社製:SQ10−11)をスクリーン印刷で充填し、220℃でリフローしたのち、フラックスを洗浄除去し半田バンプ14を形成した(図16参照)。同様の方法により、もう一枚の半田バンプ14付き両面回路基板1と、回路4形成まで行った両面回路基板1を製造し、これら3枚を位置合わせして重ね、加熱加圧(50kg/cm2 、175℃、60min)により一体化し(図17参照)、6層構造の低熱膨張多層配線基板を作製した(図1参照)。

【0029】

【実施例2】

所定位置に直径150μmのパンチで300μmピッチにて孔2aを開けた厚み50μmの36アロイ箔2(Ni:36重量%,Fe:64重量%、熱膨張係数1.5ppm/℃)の表裏両面に、厚み35μmのポリイミド系接着シート11(新日鐡化学社製:SPB−035A)を用いて、加圧加熱接着(40kg/cm2 、200℃、5min)を行い(図8参照)、低熱膨張基板18を作製した(図9参照)。つぎに、36アロイ箔2の孔2aと同じ位置に直径100μmのパンチを用いて貫通孔1aを開けた(図10参照)。上記貫通孔1a上部にメタルマスク(直径200μm,厚み100μm)を用いて、半田粉末(平均粒径10μm)をスクリーン印刷したのち、プレス(100kg/cm2 、30℃、5min)により圧入し、過度量の半田をバフ研磨により取り除くことにより半田製ビア5を設けた(図11参照)。つぎに、上記低熱膨張基板18の表裏両面に、厚み18μmの銅箔4aを加圧加熱接着(40kg/cm2 、200℃、60min)を行い(図12参照)、従来のエッチング法により表裏両面の銅箔4aに回路4を形成して両面回路基板1を作製した(図13参照)。

【0030】

そののち、上記実施例1と同様にして、接着シート13を仮接着し、半田バンプ14を形成し、加熱加圧して全体を一体化し、層間の電気的接続を行い、6層構造の低熱膨張多層配線基板を作製した。

【0031】

【比較例1】

所定位置に直径150μmのパンチで300μmピッチにて孔2aを開けた厚み50μmの36アロイ箔2(Ni:36重量%,Fe:64重量%、熱膨張係数1.5ppm/℃)の表裏両面に、厚み35μmのポリイミド系接着シート11(新日鐡化学社製:SPB−035A)を加圧加熱接着(40kg/cm2 、200℃、5min)し、低熱膨張両面基板18を作製した(図9参照)。つぎに、36アロイ箔2の孔2aと同じ位置に直径100μmのパンチを用いて貫通孔1aを開けた。上記貫通孔1a上部に導電性ペーストをスクリーン印刷により充填したのち、硬化(175℃、60min)を行い、導電性ビア15を設けた(図18参照)。このとき、導電性ペーストは、導電性のフィラーとして平均粒径5μmの球状銅粉末を、樹脂として熱硬化エポキシ樹脂を、硬化剤として酸無水物系の硬化剤をそれぞれ85重量%、12.5重量%、2.5重量%の割合で混合したものを使用した。つぎに、上記低熱膨張基板の表裏両面に、厚み18μmの銅箔4aを加熱加圧接着(40kg/cm2 、200℃、60min)を行い、従来のエッチング法により表裏両面の銅箔4aに回路4を形成して両面回路基板1を作製した。

【0032】

そののち、上記実施例と同様にして、接着シート13を仮接着し、半田バンプ14を形成し、加熱加圧して全体を一体化し、層間の電気的接続を行い、6層構造の低熱膨張多層配線基板を作製した。

【0033】

【比較例2】

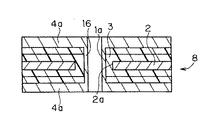

所定位置に直径150μmのパンチで300μmピッチにて孔2aを開けた厚み50μmの36アロイ箔2(Ni:36重量%,Fe:64重量%,熱膨張係数1.5ppm/℃)の表裏両面に、厚み18μmの銅箔4aを厚み35μmのポリイミド系接着シート11(新日鐡化学社製:SPB−035A)を用いて加圧加熱接着(40kg/cm2 、200℃、60min)し、低熱膨張両面基板8を作製した(図19参照)。さらに、36アロイ箔2の孔2aと同じ位置に直径100μmのパンチを用いて貫通孔1aを開けた(図20参照)。つぎに、図21に示すように、めっきの厚み10μmの銅のスルーホールめっきを行い(スルーホールめっき部16を形成し)、従来のエッチング法により表裏両面の銅箔4aに回路4を形成して両面回路基板1を作製した(図22参照)。

【0034】

そののち、上記実施例と同様にして、接着シート13を仮接着し、半田バンプ14を形成し、加熱加圧して全体を一体化し、層間の電気的接続を行い、6層構造の低熱膨張多層配線基板を作製した。

【0035】

【比較例3】

ポリイミド樹脂からなる絶縁層21(厚み50μm)の表裏両面に銅箔層22(厚み18μm)を設けてなる両面銅張ポリイミド基材23(三井東圧社製:NEOFLEX−231R)の所定の位置に直径100μmのパンチで貫通孔23aを開けた(図23参照)。つぎに、上記実施例と同様にして、半田製ビア24を設けたのち(図24参照)、めっき、回路25形成を行い、両面回路基板26を作製した(図25参照)。そののち、上記実施例と同様にして、接着シート13を仮接着し、半田バンプ14を形成し、加熱加圧して全体を一体化し、層間の電気的接続を行い、6層構造の多層配線基板を作製した。

【0036】

【比較例4】

比較例3で使用した半田製ビア24の代わりに、上記比較例1の導電性ビア15を用いた以外は、比較例3と同様にして、6層配線基板を作製した。

【0037】

上記のようにして作製した実施例1,2、比較例1〜4に記載した6層配線基板における各ビア5,15,24の電気的接続信頼性を熱衝撃試験(液層:−65℃⇔150℃、各5min)を用いて評価した。下記の表1には、各ビア5,15,24において導通不良が発生したサイクル数を示した。ここでは、抵抗値変化で±10%以上の場合を導通不良と見なした。

【0038】

【表1】

【0039】

上記の表1から明らかなように、比較例2(従来のスルーホール構造を有した6層配線基板)においては、100サイクル以下で導通不良が生じる。これに対して、実施例1,2、比較例3に示した6層配線基板は、1000サイクルまで各ビア5の抵抗値変化は±10%以内を維持しており、各回路4間の電気的接続が半田製導体5aが充填されたビア5,24により行われている6層配線基板の接続信頼性が高いことが明白である。また、各回路4間の電気的接続が導電性ビア15により行われている比較例1と比較例4を比較したところ、芯材として、Ni−Fe系合金箔2を使用することにより信頼性が大幅に向上している。Ni−Fe系合金箔2により、ビア15周辺のZ軸方向の変形量が抑制されたために比較例1の信頼性が向上したと考えられる。

【0040】

また、実施例1,2、比較例1、比較例3〜4に関しては、任意の層間を微細なビア5,15,24で自由に接続できるため、設計の自由度が上がり、高密度配線を容易に実現できることは明白である。

【0041】

さらに、上記両面回路基板1の絶縁層には、導体層4aに対して1層の割合でNi−Fe系合金箔2からなる低熱膨張の芯材が含まれている。実施例1,2および比較例1〜4に記載した6層配線基板の熱膨張率を室温(25℃)から200℃の範囲で測定したところ、下記の表2のようになった。

【0042】

【表2】

【0043】

上記の表2に示すように、芯材として、Ni−Fe系合金箔2を使用した実施例1,2および比較例1,2の6層配線基板の熱膨張率は極めて小さく、ベアチップ実装に適した基板であることが明白である。このように、実施例の低熱膨張多層配線基板は、ベアチップ実装に適した極めて電気的接続信頼性の高い基板であることは言うまでもない。

【0044】

【発明の効果】

以上のように、本発明により製造される多層配線基板によれば、スルーホールを設ける代りに、低融点金属を充填したビアホールを設けているため、温度サイクル試験等の環境加速試験においても内部やコーナー部に亀裂が生じず、接続信頼性が高い。また、低融点金属を充填したビアホール上に半田製導電体を設けて、積み重なる(上下に隣り合う)2つの両面回路基板の配線導体を電気的に接続することができるため、配線の自由度が大きい。また、本発明では、両面回路基板に接着シートを位置合わせして仮接着し、この接着シートに開けた開孔部に半田バンプを形成したのち、各両面回路基板を位置合わせして積重し加熱加圧して全体を一体化させているため、一回の加熱加圧により複数の両面回路基板を一体化することができる。と同時に、配線導体の層数が何層であっても、上記一回の加熱加圧により各配線導体間の電気的接続が行える。

【図面の簡単な説明】

【図1】 本発明の多層配線基板の製造方法により製造される多層配線基板の一実施の形態を示す断面図である。

【図2】 両面回路基板の製造工程を示す断面図である。

【図3】 上記両面回路基板の製造工程を示す断面図である。

【図4】 上記両面回路基板の製造工程を示す断面図である。

【図5】 上記両面回路基板の製造工程を示す断面図である。

【図6】 上記両面回路基板の製造工程を示す断面図である。

【図7】 上記両面回路基板の断面図である。

【図8】 両面回路基板の変形例の製造工程を示す断面図である。

【図9】 上記変形例の製造工程を示す断面図である。

【図10】 上記変形例の製造工程を示す断面図である。

【図11】 上記変形例の製造工程を示す断面図である。

【図12】 上記変形例の製造工程を示す断面図である。

【図13】 上記変形例の断面図である。

【図14】 接着シートを示す断面図である。

【図15】 両面回路基板に接着シートを仮接着した状態を示す断面図である。

【図16】 接着シートに半田バンプを形成した状態を示す断面図である。

【図17】 各両面回路基板を積層する状態を示す断面図である。

【図18】 比較例1の製造工程を示す断面図である。

【図19】 比較例2の製造工程を示す断面図である。

【図20】 比較例2の製造工程を示す断面図である。

【図21】 比較例2の製造工程を示す断面図である。

【図22】 比較例2の製造工程を示す断面図である。

【図23】 比較例3の製造工程を示す断面図である。

【図24】 比較例3の製造工程を示す断面図である。

【図25】 比較例3の製造工程を示す断面図である。

【符号の説明】

1 両面回路基板

2 合金箔

3 絶縁層

4 回路

5a,7 半田製導電体

6 接着剤層

Claims (4)

- メタルコアを基体とした有機高分子樹脂からなる絶縁層の両面に配線導体が設けられこれら両配線導体が低融点金属が充填されたビアホールにより電気的に接続された複数の両面回路基板が、接着剤層を介して積層一体化され、上記接着剤層には、これを挟む2つの両面回路基板の配線導体に当接する部分のうち、上記2つの両面回路基板の少なくとも1つのビアホールに対面する位置に孔が穿設され、上記穿孔部に半田製導電体が設けられ、上記半田製導電体により上記2つの両面回路基板の配線導体が電気的に接続されている多層配線基板を製造する方法であって、メタルコアを基体とした有機高分子樹脂からなる絶縁層を有し上記メタルコアの所定の位置に孔が開けられた基材を準備し、その基材の上記孔に対応する部分に、上記孔の内周面と離間するよう上記孔より小さいビアホールを開けてこのビアホールに低融点金属粉末もしくはペースト状低融点金属をスクリーン印刷により供給しプレスにより圧入し、この圧入後に上記基材の両面に配線導体を設け両面回路基板を形成する工程と、上記両面回路基板のビアホールに対応する位置に開孔した接着シートを準備する工程と、上記両面回路基板のビアホールに上記接着シートの開孔部を位置合わせした状態で上記両面回路基板に接着シートを仮接着する工程と、接着シート仮接着後に各接着シートの開孔部に印刷により半田ペーストを充填し加熱溶融させて半田バンプを形成する工程と、半田バンプ形成後に上記両面回路基板の配線導体が所定の電気的接続を行えるよう位置合わせして上記両面回路基板を複数枚積み重ね加熱加圧して全体を一体化させる工程を備えていること特徴とする多層配線基板の製造方法。

- 上記低融点金属が、Sn,Pb,Ag,Bi,Zn,Sb,Cuから選ばれた少なくとも1種類からなる半田製導電体である請求項1記載の多層配線基板の製造方法。

- 上記メタルコアが、Fe,Ni,Al,Ti,Cu,Coあるいはこれらを含む合金からなる金属箔である請求項1記載の多層配線基板の製造方法。

- 上記メタルコアが、Ni−Fe系合金箔であり、Ni含有量が31〜50重量%で、かつ、その厚みが10μm〜100μmの範囲である請求項1記載の多層配線基板の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP19969099A JP4201436B2 (ja) | 1999-07-14 | 1999-07-14 | 多層配線基板の製造方法 |

| DE60032067T DE60032067T2 (de) | 1999-07-14 | 2000-07-13 | Mehrschichtige Leiterplatte und Verfahren zu deren Herstellung |

| US09/615,761 US6335076B1 (en) | 1999-07-14 | 2000-07-13 | Multi-layer wiring board and method for manufacturing the same |

| EP00115237A EP1069811B1 (en) | 1999-07-14 | 2000-07-13 | Multi-layer wiring board and method for manufacturing the same |

| TW089114072A TW493367B (en) | 1999-07-14 | 2000-07-14 | Multi-layer wiring board and method for manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP19969099A JP4201436B2 (ja) | 1999-07-14 | 1999-07-14 | 多層配線基板の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001028482A JP2001028482A (ja) | 2001-01-30 |

| JP4201436B2 true JP4201436B2 (ja) | 2008-12-24 |

Family

ID=16412001

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP19969099A Expired - Fee Related JP4201436B2 (ja) | 1999-07-14 | 1999-07-14 | 多層配線基板の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6335076B1 (ja) |

| EP (1) | EP1069811B1 (ja) |

| JP (1) | JP4201436B2 (ja) |

| DE (1) | DE60032067T2 (ja) |

| TW (1) | TW493367B (ja) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6159586A (en) * | 1997-09-25 | 2000-12-12 | Nitto Denko Corporation | Multilayer wiring substrate and method for producing the same |

| US20040094771A1 (en) * | 2001-03-26 | 2004-05-20 | Adolf Bernds | Device with at least two organic electronic components and method for producing the same |

| JP2003023248A (ja) | 2001-07-05 | 2003-01-24 | Nitto Denko Corp | 多層フレキシブル配線回路基板およびその製造方法 |

| JP3461172B2 (ja) * | 2001-07-05 | 2003-10-27 | 日東電工株式会社 | 多層配線回路基板の製造方法 |

| US6459047B1 (en) * | 2001-09-05 | 2002-10-01 | International Business Machines Corporation | Laminate circuit structure and method of fabricating |

| US6899815B2 (en) | 2002-03-29 | 2005-05-31 | Intel Corporation | Multi-layer integrated circuit package |

| US20050233161A1 (en) * | 2002-04-02 | 2005-10-20 | Masaaki Takeda | Thermosetting adhesive sheet with electroconductive and thermoconductive properties |

| JP2003332752A (ja) * | 2002-05-14 | 2003-11-21 | Shinko Electric Ind Co Ltd | メタルコア基板およびその製造方法 |

| US7485812B2 (en) * | 2002-06-27 | 2009-02-03 | Ppg Industries Ohio, Inc. | Single or multi-layer printed circuit board with improved via design |

| US7358289B2 (en) * | 2002-10-22 | 2008-04-15 | 3M Innovative Properties Company | Heat-curable adhesive composition |

| JP2006024751A (ja) * | 2004-07-08 | 2006-01-26 | Three M Innovative Properties Co | 平面多導体の接続方法及び該接続方法で接続される部分を含む電気電子部品 |

| KR100632560B1 (ko) * | 2004-08-05 | 2006-10-09 | 삼성전기주식회사 | 병렬적 인쇄회로기판 제조 방법 |

| JP4287458B2 (ja) * | 2005-11-16 | 2009-07-01 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | ペーストバンプを用いた印刷回路基板およびその製造方法 |

| EP2129201B1 (en) * | 2007-03-01 | 2017-04-12 | Murata Manufacturing Co. Ltd. | Multilayer wiring substrate |

| CN101470298B (zh) | 2007-12-29 | 2012-01-11 | 富士迈半导体精密工业(上海)有限公司 | 背光模组 |

| CN101937852B (zh) * | 2010-08-19 | 2012-07-04 | 日月光半导体制造股份有限公司 | 线路基板制造方法 |

| US8921703B2 (en) * | 2012-02-17 | 2014-12-30 | Htc Corporation | Circuit board, structural unit thereof and manufacturing method thereof |

| KR101438915B1 (ko) | 2012-11-02 | 2014-09-11 | 엘지이노텍 주식회사 | 인쇄회로기판 및 그의 제조 방법 |

| US20150122532A1 (en) * | 2013-11-04 | 2015-05-07 | Teledyne Technologies Incorporated | High temperature multilayer flexible printed wiring board |

| US9832866B2 (en) * | 2015-06-29 | 2017-11-28 | Samsung Electro-Mechanics Co., Ltd. | Multilayered substrate and method of manufacturing the same |

| US10455708B2 (en) | 2015-06-29 | 2019-10-22 | Samsung Electro-Mechanics Co., Ltd. | Multilayered substrate and method for manufacturing the same |

| JP7381323B2 (ja) * | 2019-12-17 | 2023-11-15 | 日東電工株式会社 | 両面配線回路基板の製造方法および両面配線回路基板 |

| CN111182713A (zh) * | 2020-01-15 | 2020-05-19 | 深圳市信维通信股份有限公司 | 高频线路板及其制作方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB1310880A (en) * | 1969-06-13 | 1973-03-21 | Microponent Dev Ltd | Multi-layer printed circuit board assemblies |

| JPS61212096A (ja) | 1985-03-18 | 1986-09-20 | 株式会社日立製作所 | 多層配線板 |

| JPS62251136A (ja) * | 1986-04-25 | 1987-10-31 | 三菱樹脂株式会社 | 金属複合積層板 |

| US4942076A (en) * | 1988-11-03 | 1990-07-17 | Micro Substrates, Inc. | Ceramic substrate with metal filled via holes for hybrid microcircuits and method of making the same |

| JPH05259600A (ja) | 1992-03-11 | 1993-10-08 | Hitachi Chem Co Ltd | 配線板およびその製造法 |

| JPH0697665A (ja) | 1992-09-14 | 1994-04-08 | Toshiba Corp | 多層印刷配線基板の製造方法 |

| JPH06268381A (ja) | 1993-03-11 | 1994-09-22 | Hitachi Ltd | 多層配線構造体及びその製造方法 |

| US6159586A (en) * | 1997-09-25 | 2000-12-12 | Nitto Denko Corporation | Multilayer wiring substrate and method for producing the same |

-

1999

- 1999-07-14 JP JP19969099A patent/JP4201436B2/ja not_active Expired - Fee Related

-

2000

- 2000-07-13 EP EP00115237A patent/EP1069811B1/en not_active Expired - Lifetime

- 2000-07-13 US US09/615,761 patent/US6335076B1/en not_active Expired - Lifetime

- 2000-07-13 DE DE60032067T patent/DE60032067T2/de not_active Expired - Lifetime

- 2000-07-14 TW TW089114072A patent/TW493367B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| EP1069811A3 (en) | 2003-05-07 |

| DE60032067D1 (de) | 2007-01-11 |

| US6335076B1 (en) | 2002-01-01 |

| TW493367B (en) | 2002-07-01 |

| JP2001028482A (ja) | 2001-01-30 |

| EP1069811B1 (en) | 2006-11-29 |

| DE60032067T2 (de) | 2007-03-08 |

| EP1069811A2 (en) | 2001-01-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4201436B2 (ja) | 多層配線基板の製造方法 | |

| US6373000B2 (en) | Double-sided circuit board and multilayer wiring board comprising the same and process for producing double-sided circuit board | |

| KR100517009B1 (ko) | 다층배선기판및이의제조방법 | |

| JP3709882B2 (ja) | 回路モジュールとその製造方法 | |

| JP3429734B2 (ja) | 配線基板、多層配線基板、回路部品実装体及び、配線基板の製造方法 | |

| JP3826731B2 (ja) | 多層プリント配線基板及び多層プリント配線基板の製造方法 | |

| WO2007126090A1 (ja) | 回路基板、電子デバイス装置及び回路基板の製造方法 | |

| TW200938020A (en) | Part built-in wiring board, and manufacturing method for the part built-in wiring board | |

| KR20060126832A (ko) | 다층 적층 배선판 | |

| JPH11354684A (ja) | 低熱膨張配線基板および多層配線基板 | |

| JP4509550B2 (ja) | 中継基板、半導体素子付き中継基板、中継基板付き基板、半導体素子と中継基板と基板とからなる構造体 | |

| JP2020102593A (ja) | 基板、基板の製造方法及び電子装置 | |

| JP4183708B2 (ja) | 部品内蔵基板の製造方法 | |

| JP2001332828A (ja) | 両面回路基板およびそれを用いた多層配線基板 | |

| JP4694007B2 (ja) | 三次元実装パッケージの製造方法 | |

| JPH10190232A (ja) | 多層配線基板及びその製造方法 | |

| JP5170570B2 (ja) | 樹脂多層モジュール及び樹脂多層モジュールの製造方法 | |

| JP2002151853A (ja) | 多層配線基板とその製造方法 | |

| JPH11163522A (ja) | 多層配線基板およびその製造方法 | |

| WO2004012489A1 (ja) | 回路基板、多層配線板、回路基板の製造方法および多層配線板の製造方法 | |

| JP4786914B2 (ja) | 複合配線基板構造体 | |

| JP4718890B2 (ja) | 多層配線基板及びその製造方法、多層配線基板構造体 | |

| JP3107535B2 (ja) | 配線基板、回路部品実装体、および配線基板の製造方法 | |

| JP2001028481A (ja) | 多層配線基板およびその製造方法 | |

| JP2004228521A (ja) | 配線基板およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051114 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070927 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080414 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080930 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081007 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111017 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141017 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |