JP4024990B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4024990B2 JP4024990B2 JP2000130705A JP2000130705A JP4024990B2 JP 4024990 B2 JP4024990 B2 JP 4024990B2 JP 2000130705 A JP2000130705 A JP 2000130705A JP 2000130705 A JP2000130705 A JP 2000130705A JP 4024990 B2 JP4024990 B2 JP 4024990B2

- Authority

- JP

- Japan

- Prior art keywords

- resistance

- resistance element

- semiconductor device

- insulating film

- semiconductor substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 121

- 239000010410 layer Substances 0.000 claims description 154

- 239000000758 substrate Substances 0.000 claims description 65

- 239000007858 starting material Substances 0.000 claims description 35

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 27

- 229920005591 polysilicon Polymers 0.000 claims description 22

- 239000011229 interlayer Substances 0.000 claims description 19

- 239000012535 impurity Substances 0.000 claims description 12

- 229910052751 metal Inorganic materials 0.000 claims description 8

- 239000002184 metal Substances 0.000 claims description 8

- 230000015556 catabolic process Effects 0.000 description 58

- 230000002093 peripheral effect Effects 0.000 description 30

- 238000004519 manufacturing process Methods 0.000 description 21

- 238000010586 diagram Methods 0.000 description 20

- 230000005684 electric field Effects 0.000 description 20

- 238000000034 method Methods 0.000 description 20

- 239000004020 conductor Substances 0.000 description 16

- 238000012986 modification Methods 0.000 description 14

- 230000004048 modification Effects 0.000 description 14

- 238000001514 detection method Methods 0.000 description 11

- 230000020169 heat generation Effects 0.000 description 10

- 238000003079 width control Methods 0.000 description 9

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 239000003990 capacitor Substances 0.000 description 8

- 238000009792 diffusion process Methods 0.000 description 8

- 230000017525 heat dissipation Effects 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 238000006731 degradation reaction Methods 0.000 description 7

- 230000004913 activation Effects 0.000 description 6

- 230000008859 change Effects 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 230000005855 radiation Effects 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 238000009499 grossing Methods 0.000 description 4

- 230000008018 melting Effects 0.000 description 4

- 238000002844 melting Methods 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 230000007935 neutral effect Effects 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 238000007740 vapor deposition Methods 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 230000001629 suppression Effects 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000006378 damage Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 239000005368 silicate glass Substances 0.000 description 1

- SBEQWOXEGHQIMW-UHFFFAOYSA-N silicon Chemical compound [Si].[Si] SBEQWOXEGHQIMW-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/201—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits

- H10D84/204—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors

- H10D84/209—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of only components covered by H10D1/00 or H10D8/00, e.g. RLC circuits of combinations of diodes or capacitors or resistors of only resistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/811—Combinations of field-effect devices and one or more diodes, capacitors or resistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/40—Resistors

- H10D1/47—Resistors having no potential barriers

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Dc-Dc Converters (AREA)

Description

【発明の属する技術分野】

本発明は半導体装置及びその製造方法に係わり、特に、直流安定化電源であるスイッチングレギュレータのIC(Integrated Circuit)化技術に適用して有効な技術に関するものである。

【0002】

【従来の技術】

パーソナルコンピュータ,携帯電話等の電子機器(電子回路)を高精度にかつ仕様通りに駆動するために直流安定化電源が使用されている。この直流安定化電源の一つとして、スイッチング方式直流安定化電源(スイッチングレギュレータ)が知られている。スイッチングレギュレータは、交流入力電圧を一度整流した後、トランジスタのオン・オフ回路を用いて、交流に変換し、その後、再び整流回路により直流に変換して出力電圧とする。スイッチングレギュレータの制御方式には、一定時間で発振するパルスの幅を制御するパルス幅制御方式、負荷に応じて発振するパルス数を変化させる周波数制御方式等がある。

【0003】

スイッチングレギュレータについては、例えば、電子情報通信学会発行「電子情報通信ハンドブック」、昭和63年3月30日発行、P246に記載されている。

また、IEEE Transactions on Electron Devices,vol.,44,No.11,November 1997,pp2002-2010 には、スイッチングレギュレータの一部を集積回路化した技術について記載されている。この文献には、スイッチングレギュレータの集積回路化に際して、スパイラル状に抵抗素子を形成し、その中心部分を高電位に接続し、外周部分を接地電位に接続する構造(SJT:Spiral Junction Termination )が開示されている。このスパイラル状の抵抗素子はアクティブ領域に形成されている。

【0004】

一方、特開平9−186315号公報には、耐圧の低下を抑制するインバータ用絶縁ゲートバイポーラトランジスタ(IGBT)が開示されている。この文献には、半導体チップの周辺(周辺領域)の半導体基板(ドリフト層)の表層部にFLR(Field Limitting Ring)を設け、このドリフト層上に酸化膜を介して過電圧抑制ダイオードを形成した例が示されている。この例では、FLRの素子寸法を過電圧抑制ダイオードの素子の寸法の4/5とすることにより、電位分布を最適化し、耐圧の低下を抑制している。

【0005】

【発明が解決しようとする課題】

現在、商用電源の交流電圧は国ごとに異なっており、例えば日本では100Vまたは200Vであるが、米国では115V、欧州では220V〜240Vとなっている。

【0006】

スイッチングレギュレータは、メインスイッチと、このメインスイッチを起動させる起動回路を有している。起動回路はスタータースイッチと起動抵抗(抵抗素子)で構成されている。

240Vの交流を整流した直流電源と接続するスイッチングレギュレータでは、使用されるトランジスタの最大耐圧は700V程度が必要となり、製品値としてこの数字を保証するために、メインスイッチとスタータースイッチは最大耐圧750V程度の設計値が必要となる。

【0007】

メインスイッチ及びスタータースイッチを構成するトランジスタの高電圧印加時の降伏は、面積が大きい素子にてその表面部分以外にて行なわれるのが望ましい。具体的には、面積が小さく表面で降伏しやすい起動抵抗素子での降伏を回避し、面積が大きく表面で降伏し難いパワーMISFET(Metal Insulator Semiconductor Field Effect Transistor )やMOSFET(Metal Oxide Semiconductor FET)にて降伏させるのが望ましい。このため、パワーMISFETの耐圧を750V〜800Vとすれば、起動抵抗の耐圧は800V以上とすることが望ましい。

しかし、このような800V以上の高耐圧の起動抵抗は、これまでIC化されておらず他に例がないため、新たに開発を進める必要がある。

【0008】

本出願人においては、前記文献に示されているように抵抗素子を渦巻き状に形成することを検討した。しかし、この抵抗素子は印加電圧が高くなると抵抗値が下がり大きな電流が流れてしまうということを実験によって知見した。

また、この抵抗素子は、ICが形成される半導体基板の活性領域に形成されるため、ICチップのサイズの拡大を招き、製造コストが高くなる。また、抵抗素子のレイアウトによっては、隣接する他の素子等との間で寄生動作を起こすことが考えられる。

【0009】

そこで、本出願人においては、半導体チップの周辺領域に設けられるフィールド絶縁膜上に半導体チップの中心から外周に向かう方向に蛇行した抵抗層を有する抵抗素子を設ける構成とし、高電圧印加時に前記フィールド絶縁膜が破壊するのを防止する技術を提案(特願平11−47607号公報)している。前記蛇行部分は、半導体チップのアクティブ領域を多重に囲む複数のFLRの各リング部分を横切るように延在している。

【0010】

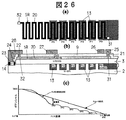

しかし、このような蛇行構造抵抗素子では、以下のような問題があることが判明した。図26(a)〜(c)は既に提案(特願平11−47607号公報)した技術を分析検討した結果を示す図表である。図26(a)は起動抵抗(抵抗素子)SRを構成する抵抗層の蛇行パターンを示す模式図、図26(b)は駆動パワーICのFLRや抵抗層等を含む部分の断面図、図26(c)はFLRを含む半導体基板表面のポテンシャルと、抵抗層のポテンシャルを示すグラフである。なお、この分析検討では、FLRをP1〜P5で示すように5本として記載してあるが、これに限定されるものではない。

【0011】

図26(b)には、駆動パワーICが形成された半導体チップの周辺部分の断面を示す。同図には主面にn-型のエピタキシャル層2が設けられたn+型シリコンからなる半導体基板1が示されている。

【0012】

半導体チップは、トランジスタ等の素子が形成される半導体基板のアクティブ領域の周辺に周辺領域が位置し、この周辺領域のエピタキシャル層2の主面にはLOCOS(Local Oxidation of Silicon)からなるフィールド絶縁膜3が形成されている。そして、周辺領域の半導体基板の主面、即ちエピタキシャル層2の主面には、p型拡散層からなるP1〜P5で示されるフィールド・リミッティング・リング(FLR)13が図示しないアクティブ領域を囲むように形成されている。なお、P1の内側にはグランド(GND)電位にされるp型拡散層(P0)が形成されている。

【0013】

また、半導体チップの周縁にはガードリング14が設けられている。このガードリング14はフィールド絶縁膜3から外れたフィールド絶縁膜3よりも薄い絶縁膜24の下のエピタキシャル層2表面に設けられている。このガードリング14はエピタキシャル層2の主面に高濃度に不純物を拡散したn+型のリング状の拡散領域で形成されている。

【0014】

前記フィールド絶縁膜3上にはポリシリコン層で形成される抵抗層20が設けられている。この抵抗層20はその表面を層間絶縁膜9で被われている。また、前記P0上の層間絶縁膜9及びフィールド絶縁膜3の外周部分には、それぞれコンタクト孔21,22,23が設けられている。コンタクト孔23はフィールド絶縁膜3から外れた薄い絶縁膜24をも貫通するように形成されている。

【0015】

また、層間絶縁膜9上には半導体チップの周辺に沿って延在するリング状の導体膜25〜28が形成されている。導体膜25は周辺領域の内側、即ち、アクティブ領域側に設けられるとともに、コンタクト孔21にも充填されて抵抗層20に電気的に接続されている。導体膜26は導体膜25に近接して設けられ、基準電位(GND)になるp型拡散層(P0)に電気的に接続されている。導体膜27は最外周のFLR13上に形成され、最外周のFLR13に電気的に接続されている。導体膜28はコンタクト孔22及びコンタクト孔23内にも充填され、抵抗層20とガードリング14を電気的に接続している。

【0016】

前記FLR13群では、印加電圧の増加につれて、アバランシェ降伏が起きる前に内周のFLR13から外周のFLR13に空乏層が延びてパンチスルーする構成になっており、最終的には最外周のFLR13のpn接合部分で降伏するようになっている。FLR13を設けることによって、パンチスルー耐圧とFLR13の数との積の分耐圧が向上することになる。従って、起動抵抗SRの耐圧は前記FLR13部分の耐圧と、フィールド絶縁膜3厚さ等に起因する耐圧との和となり、総合的な耐圧は800V以上とさせるものである。

【0017】

コンタクト孔21に対応する抵抗層部分が抵抗素子(起動抵抗)SRの始端31となり、コンタクト孔22に対応する抵抗層部分が起動抵抗SRの終端32となる。始端31から終端32に至る起動抵抗SRとしての抵抗層20のパターンは、図26(a)に示すように、一定ピッチで一定振幅の蛇行パターンとなっている。図26(b)では特に蛇行状態は明記せず簡略化してある。

【0018】

このように抵抗層20を蛇行させるパターンとすることによって、抵抗層20を長くして放熱面積の増大と電界強度の緩和を図っている。従って、抵抗素子の発熱による破壊及び過電界による破壊を防止することができる。

また、抵抗層20は、蛇行パターンとすることにより、始端31と終端32を直線的に結ぶ線分に置き換えた抵抗素子の単位長さ当たりの抵抗値を大きくして所定の抵抗値を得る構造になっている。

【0019】

このようにFLR13が配置される領域を含むフィールド絶縁膜3上に起動抵抗SRを設けることによって、起動抵抗SRに高電位が加わった際、起動抵抗SRに発生する電界とFLR13に発生する電界との差が小さくなり、フィールド絶縁膜3に加わる電界が緩和され、フィールド絶縁膜3の破壊が防止される。

【0020】

しかし、本発明者等による分析によれば、起動抵抗SRのポテンシャルと、FLR13が設けられる半導体基板表面のポテンシャルは、図26(c)に示すように、相互に近似するものではなく、最外周のFLR13部分で最も大きくなることが判明した。これは、抵抗層20が始端31から終端32に至る同じ太さとなる抵抗層20を同一蛇行幅で等ピッチで形成してあることから、起動抵抗SRの始端31から終端32に至る直線に置き換えた状態での抵抗のポテンシャルは、図26(c)に示すように直線になる。しかし、半導体基板の表面、即ちフィールド絶縁膜3と半導体基板1との界面でのポテンシャルは、図26(c)に示すように、FLR13部分では段階的に変化し、最外周のFLR13を外れた領域では曲線を描くようにポテンシャルが変化することが判明した。

【0021】

最外周のFLR13部分では高電界が発生する。この電界により、バルクで発生した電子・正孔対のうちの電子が強く抵抗層20であるポリシリコン層側に引き付けられ、その下のフィールド絶縁膜3中に多量にトラップされる。この電荷により半導体基板の表面のFLR13間のn-型のエピタキシャル層2の表面がp型に反転してチャネルリークが発生して耐圧低下が起きる。

【0022】

本発明者等は、駆動パワーICの測定試験を行った。図28は駆動パワーIC(PW MOSチップ)の測定回路である。駆動パワーICは、特に限定はされないが、メインスイッチMS,スタータースイッチSS及び起動抵抗SRがシリコン半導体基板にモノリシックに組み込まれた構造となっている。メインスイッチMSは、セル数が2270となるメインMOS(MAIN−MOS)と、セル数が2セルとなる電流検出(Current Sence )を行うCS−MOSで構成されている。また、メインスイッチMSの4つの電極はそれぞれドレイン端子(DRAIN),ソース端子(SOURCE),ゲート端子(GATE),電流検出端子(CS)にそれぞれ接続されている。

【0023】

スタータースイッチSSは、特に限定はされないが、セル数が60となるMOS(Start-MOS)からなり、3つの電極はそれぞれドレイン端子,起動回路用制御端子(Start-MOS Gate ),起動回路用ソース端子(Start-MOS Source)にそれぞれ接続されている。スタータースイッチSSのゲートとドレイン端子間には起動抵抗SR(例えば、2MΩ)が直列に接続されている。

【0024】

このような駆動パワーICのドレイン端子と他の端子間にVdsを印加し、電流計でIdsを測定して得た特性が図27のグラフである。

図27は駆動パワーICを室温150℃,Vds=750Vなる環境下で試験した初期(0時間)と試験後(48時間)の耐圧劣化波形の比較を示すものである。同グラフは、横軸が電圧(Vds)で、縦軸が電流(Ids)である。

初期特性では、印加電圧が800V程度でアバランシェ降伏が発生しているのに対し、試験後の特性では印加電圧が600V程度を越すとチャネル性のリーク電流が発生して電流の増大が起き、印加電圧が800V程度でアバランシェ降伏に至ることが判明した。

そして、このような不良現象を防止する構造検討に先立って、抵抗素子のポテンシャルと、半導体基板の表面のポテンシャルをシュミレーションによって得たのが、図26(c)ポテンシャル図である。

【0025】

そこで、本発明者は、起動抵抗(抵抗素子)SRのポテンシャルと、これに対応する半導体基板の表面のポテンシャルを一致または近似させることを考え本発明をなした。

【0026】

本発明の目的は、高耐圧高抵抗の抵抗素子を内蔵した半導体装置及びその製造方法を提供することにある。

本発明の他の目的は、スイッチングレギュレータ用の高耐圧高抵抗の起動抵抗を内蔵した半導体装置(駆動パワーIC)及びその製造方法を提供することにある。

本発明の他の目的は、高耐圧高抵抗の抵抗素子を半導体装置を大きくすることなく製造できる技術を提供することにある。

本発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面からあきらかになるであろう。

【0027】

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記のとおりである。

【0028】

(1)トランジスタが形成されるアクティブ領域及び前記アクティブ領域を囲み表面がフィールド絶縁膜で被われる周辺領域を有する半導体基板と、

前記周辺領域の半導体基板表面に設けられ前記アクティブ領域を多重に囲む複数のフィールド・リミッティング・リング(FLR)と、

前記フィールド絶縁膜上に形成され前記FLR群の内側から外側に向かって延在し、前記FLR群の内側の始端が前記トランジスタの低電位となる電極に接続され、前記FLR群の外側の終端が前記トランジスタの高電位となる電極に接続される抵抗素子と、

前記抵抗素子を被う層間絶縁膜と、

前記最外周のFLRに対応して前記層間絶縁膜上に形成され、最外周のFLRに電気的に接続されるフィールドプレートとを有する半導体装置であって、

前記抵抗素子の始端と終端を直線的に結ぶ線分に置き換えた抵抗素子の抵抗値は、前記線分の一部の単位長さ当たりの抵抗値が他の部分の単位長さ当たりの抵抗値と異なっている。

【0029】

例えば、前記抵抗素子の始端と終端を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致または近似するようになっている。抵抗素子のシート抵抗は10kΩ/□以下である。

【0030】

半導体装置は、例えば、

信号が供給される第1端子と、

基準電位が供給される第2端子と、

制御端子と、

電流検出端子と、

起動回路用制御端子と、

起動回路用の基準電位が供給される起動回路用第2端子とを有し、

前記第1端子に接続される第1電極と、前記第2端子に接続される第2電極と、前記制御端子に接続される制御電極と、前記電流検出端子に接続され前記第1電極の出力電流を検出する電流検出電極を有するメインスイッチ用トランジスタと、

前記第1端子に接続される起動用第1電極と、前記起動回路用第2端子に接続される起動用第2電極と、前記起動回路用制御端子に接続される起動用制御電極とを有するスタータースイッチ用トランジスタと、

前記第1端子と前記起動用制御電極との間に直列に接続される起動抵抗とを有する半導体装置であって、前記起動抵抗が前記構成になっている。

【0031】

具体的には、前記抵抗素子は、抵抗素子の始端と終端との間に蛇行部分を有するとともに、前記蛇行部分の1乃至複数箇所では蛇行ピッチが異なっている。また、最外周の前記フィールド・リミッティング・リング部分を隔ててその内側と外側の前記線分における単位長さ当たりの抵抗値は相互に異なっている。

【0032】

抵抗素子の他の構成としては、

(a)抵抗素子は、蛇行部分を有するとともに、蛇行する幅が広い広蛇行部分と、蛇行する幅が狭い狭蛇行部分とを有する。

(b)抵抗素子は、抵抗素子の始端と終端との間に蛇行する蛇行部分と、前記線分に沿う直線部分とを有する。

(c)抵抗素子は、1乃至複数箇所で抵抗線幅が異なっている。

(d)抵抗素子は、前記線分に沿う直線形状の抵抗素子となるとともに、線幅が一部で異なっている。

(e)抵抗素子は不純物が添加されたポリシリコン層で形成されている。

(f)抵抗素子は、金属部分と、この金属部分に電気的に接続される不純物が添加されたポリシリコン層で形成されている。

(g)抵抗素子は、1乃至複数箇所でシート抵抗が異なっている。

(h)抵抗素子各部と前記半導体基板表面各部の電界が小さくなるように、前記フィールド絶縁膜の厚さは3〜5μm程度になっている。

【0033】

このような半導体装置は以下の方法で製造される。

半導体基板の主面のアクティブ領域にトランジスタが設けられるとともに、前記アクティブ領域を囲む周辺領域に前記アクティブ領域を多重に囲むように複数のフィールド・リミッティング・リングが設けられた半導体装置の製造方法であって、

前記半導体基板の主面の周辺領域に前記アクティブ領域を多重に囲むようにフィールド・リミッティング・リングを複数形成する工程と、

前記半導体基板の周辺領域上及び所定箇所にフィールド絶縁膜を形成する工程と、

前記フィールド絶縁膜上に前記トランジスタに接続される抵抗素子を構成するための抵抗層を、前記フィールド・リミッティング・リング群の内側の始端から外側の終端に向かって延在するように形成する工程とを有する。

【0034】

前記抵抗素子の始端と終端を直線的に結ぶ線分に置き換えた抵抗素子の抵抗値が、前記線分の一部の単位長さ当たりの抵抗値が他の部分の単位長さ当たりの抵抗値と異なるようなパターンに前記抵抗層を形成する。

前記抵抗素子の始端と終端を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致または近似するようなパターンに前記抵抗層を形成する。

【0035】

前記抵抗層を導体層形成とパターニングにより、またはマスクを使用した蒸着法により形成し、その抵抗層パターンを、蛇行パターン,一部で蛇行ピッチが異なる蛇行パターン,一部で蛇行幅が異なる蛇行パターン,前記各蛇行パターンと直線部分との組み合わせパターン,前記各パターンで1乃至複数箇所で抵抗線幅が異なるパターン,直線でかつ1乃至複数箇所で抵抗線幅が異なるパターンに形成する。

【0036】

前記トランジスタを電界効果トランジスタで形成するとともに、トランジスタのゲート電極をポリシリコン層で形成する際、前記抵抗層を同時にポリシリコン層で形成し、必要に応じて不純物を添加してシート抵抗を調整する。

【0037】

(2)上記(1)の構成において、前記抵抗素子の始端と終端を直線的に結ぶ線分に置き換えた抵抗素子の抵抗値が、前記線分における単位長さ当たりの抵抗値は段階的に変化し、前記抵抗素子の各部のポテンシャルと前記半導体基板表面各部のポテンシャルは一致または近似するようになっている。

【0038】

(3)上記(1)または(2)の構成において、前記各フィールド・リミッティング・リングと、各フィールド・リミッティング・リングに重なる前記抵抗素子部分はそれぞれ電気的に接続されている。

【0039】

このような半導体装置の製造においては、前記フィールド・リミッティング・リングを形成し、前記フィールド絶縁膜を形成し、前記抵抗層を形成し、前記抵抗層を被う層間絶縁膜を形成した後、前記層間絶縁膜にコンタクト孔を開けるとともに、導体を選択的に前記層間絶縁膜上に形成して前記各フィールド・リミッティング・リングと、各フィールド・リミッティング・リングに重なる前記抵抗素子部分を電気的に接続する。

【0040】

前記(1)の手段によれば、(a)抵抗素子の始端と終端を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致または近似するようになっている。従って、抵抗素子(起動抵抗)に高電圧が印加された状態でも、バルクで発生した電子・正孔対も電界によってどこか特定の箇所に引きつけられることもない。この結果、発生した電子・正孔対は再結合して電気的に中性化することになり、フィールド・リミッティング・リング間にチャネルができることもなく、耐圧は安定し耐圧劣化を抑止することができる。

【0041】

(b)起動抵抗を形成する抵抗層のシート抵抗は10kΩ/□以下とすることにより、温度上昇によるシート抵抗の低下を防止できるため、ある印加電圧における発熱量の一定化ができる。また、抵抗層を蛇行させて長くすることから放熱面積も増大して熱放散効率が増大する。これらのことから、高電圧が起動抵抗に印加されても、発熱に起因する抵抗層であるポリシリコン層の溶融による破壊事故が防止できる。

【0042】

(c)上記(a),(b)により、信頼性の高い半導体装置、即ちスイッチングレギュレータ用の駆動パワーICを提供することができる。

【0043】

(d)起動抵抗はアクティブ領域ではなく周辺領域のフィールド絶縁膜上に形成されることから、起動抵抗をアクティブ領域に形成する構造に比較して半導体チップの小型化が可能になり、半導体装置の製造コストの低減が達成できる。

【0044】

前記(2)の手段によれば、前記(1)の手段の場合と同様に耐圧劣化を抑止できるとともに、抵抗層であるポリシリコン層の発熱に起因する破壊事故を防止できる。

【0045】

前記(3)の手段によれば、各フィールド・リミッティング・リングと、各フィールド・リミッティング・リングに重なる前記抵抗素子部分はそれぞれ電気的に接続されていて、それぞれの部位において等電位になることから、前記(1)の手段の場合と同様に、抵抗素子のポテンシャルと半導体基板の表面のポテンシャルは各部で一致または近似するため、耐圧劣化を抑止できるとともに、抵抗層であるポリシリコン層の発熱に起因する破壊事故を防止できる。

【0046】

【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。なお、発明の実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

【0047】

(実施形態1)

図1乃至図16は本発明の一実施形態(実施形態1)である半導体装置及びその製造方法に係わる図である。

本実施形態1の半導体装置は、スイッチングレギュレータの駆動パワーICを構成するものである。駆動パワーICはメインスイッチMSと、このメインスイッチMSを起動させる起動回路からなり、起動回路はスタータースイッチSSと起動抵抗(抵抗素子)SRからなる。メインスイッチMS及びスタータースイッチSSはMISFET(MOSFET)で構成されている。起動抵抗SRはシート抵抗を10kΩ/□として発熱量の増加を抑え、かつ蛇行させるなどして長くし放熱面積の増大を図り、抵抗層を構成するポリシリコン層の熱に起因する破壊を防止するようになっている。

【0048】

図2はスイッチングレギュレータの回路図である。この回路は必要箇所だけ簡単に説明すると、商用電源(例えば交流240V)が供給される入力端子(ACINPUT)とトランス40の1次側コイル41との間には、ダイオードブリッジ整流回路42と平滑コンデンサ43等によって全波整流回路が形成されている。トランス40の2次側コイル44にはダイオード45と平滑コンデンサ46等によって構成される半波整流回路が接続され出力端子(OUTPUT)から直流電圧を出力する。

【0049】

1次側コイル41はパルス幅制御回路(コントロールIC)50のドレイン(Drain)端子に接続されている。パルス幅制御回路50は、他に電源(VDD)端子,ソース(Source)端子,コンパレータ(COMP)端子,キャパシタオブタイミング(CT)端子,フィードバック(FB)端子を有する。Drain端子とSource端子との間には、メインスイッチMSが接続される。Drain端子とVDD端子との間にはスタータースイッチSSが接続されるとともに、スタータースイッチSSのゲート電極とDrain端子との間には起動抵抗SRが接続され、起動回路を構成している。ドレイン電圧がある程度上昇すると起動回路が動作を開始する。

【0050】

また、スタータースイッチSSの出力電極にはUVL(Under Voltage Lockout )回路が接続されている。このUVL回路は前記スタータースイッチSSのゲート電極に接続されたUVLスイッチに接続され、UVL回路が動作するとUVLスイッチが動作してスタータースイッチがオフ状態となる。

【0051】

CT端子には発振器(Osc.)が接続されている。また、FB端子とCOMP端子との間にはエラーアンプ(E−AMP)が接続されている。このE−AMPの出力信号と、メインスイッチMSの検出信号CSは比較増幅器(C−AMP)に入力される。検出信号CSは抵抗RCSに電流として入力され、電圧に変換される。バックアップ出力電圧(≒VDD端子電圧)をエラーアンプのFB端子で帰還をかける構成になっている。

【0052】

発振器(Osc.)とC−AMPの出力信号はフリップフロップ回路(FF)に入力される。フリップフロップ回路の出力信号はメインスイッチMSのゲート電極に印加されてメインスイッチMSをオン・オフ制御する。

【0053】

パルス幅制御回路50のVDD端子は、バックアップ電源回路に接続されている。このバックアップ電源回路は、トランス40の3次側コイル(バックアップコイル)47に直列に接続されるダイオードDc ,抵抗Rc とコンデンサCc で構成されている。この電位チャージ回路は、1次側コイル41に直流電圧が印加されることにより、パルス幅制御回路50の起動回路(Starter Circuit )が動作しコンデンサCc を充電する。コンデンサCc の充電が続き、解除電圧に達すると、UVL回路が動作し、UVLスイッチをオンさせてスタータースイッチSSをオフにするとともにメインスイッチMSのオン・オフが開始する。それと同時にバックアップコイル47に電圧が誘起され、これが電源となってパルス幅制御回路50の動作が継続する。

【0054】

このフライバック方式のバックアップ出力電圧帰還型の特徴は、バックアップ出力電圧と2次側出力電圧がトランス40の1次側コイルとそれぞれのコイルの巻数比に比例しているという特性を利用したものである。

【0055】

パルス幅制御回路50がカレントモードの場合、エラーアンプの出力端子電圧に応じてパワーMOSFETの電流検出レベルを調整してパルスデューティを制御する。

【0056】

図3は全波整流回路によって得られる電圧Vb+を始めとするDrain,Istart,VDD,CT,COMP,DC OUTPUT部分の電圧変化を示す起動タイミング図である。

このようなスイッチングレギュレータでは、商用電源240Vの交流を整流して得られたVb+により、パルス幅制御回路50を、図3の起動タイミング図で示すように動作させて所定の直流電圧を出力する。図2にはDrain端子部分でのドレイン電圧波形の1例を示してある。

【0057】

図4は本実施形態1による半導体装置、即ち、スイッチングレギュレータの高電圧部を構成するメインスイッチMS,スタータースイッチSS及び起動抵抗SRをシリコン半導体基板1にモノリシックに形成した駆動パワーIC(半導体装置)の模式的平面図である。

駆動パワーICが形成された半導体チップにおいて、周辺領域の内側がアクティブ領域になり、このアクティブ領域にメインスイッチMS及びスタータースイッチSSが形成されている。周辺領域と、メインスイッチMSとスタータースイッチSSとの間にはLOCOS膜によるフィールド絶縁膜3が設けられている。また、フィールド絶縁膜3の下の半導体基板1の主面にはアクティブ領域を多重に囲む複数のFLR13が設けられている。そして、起動抵抗(抵抗素子)SRは多重に設けられたFLR13群の内側の始端から外側の終端に向けて延在するように設けられている。

【0058】

図6は駆動パワーICの等価回路図である。駆動パワーICは▲1▼〜▲6▼で示されるように6個の端子を有している。即ち、信号が出力される第1端子(ドレイン端子:DRAIN )▲1▼と、制御端子(ゲート端子:GATE)▲2▼と、基準電位(GND)が供給される第2端子(ソース端子:SOURCE)▲3▼と、電流検出端子(CS端子:Current Sence )▲4▼と、制御回路の起動を行う起動回路用第2端子(Start-MOS Source 端子)▲5▼と、起動回路用制御端子(Start-MOS Gate 端子)▲6▼とを有している。

【0059】

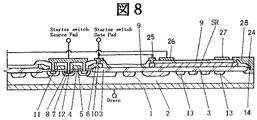

メインスイッチMS及びスタータースイッチSSは、図5,図7,図8に示すように、多数のセルを配置した縦型MISFET(MOSFET)で構成されている。そして、例えば、セル構造はメッシュゲート構造となっている。

【0060】

メインスイッチMSは、特に限定はされないが、セル数が2270となるメインMOS(MAIN−MOS)と、セル数が2セルとなる電流検出(Current Sence )を行うCS−MOSで構成されている。ドレイン電極(第1電極)はドレイン端子に接続され、MAIN−MOSのソース電極(第2電極)はソース端子に接続され、CS−MOSのソース電極は電流検出端子(CS端子)に接続され、ゲート電極はゲート端子に接続されている。

【0061】

スタータースイッチSSは、特に限定はされないが、セル数が60となるMOS(Start-MOS)からなり、ドレイン電極(起動用第1電極)はドレイン端子に接続され、ソース電極(起動用第2電極)はStart-MOS Source 端子に接続され、ゲート電極(起動用制御電極)はStart-MOS Gate 端子に接続されている。

起動抵抗SR(例えば、2MΩ)はドレイン端子とスタータースイッチSSのゲート電極に接続されている。

【0062】

つぎに、図5,図7及び図8を参照しながら駆動パワーICの構造について説明する。図5は駆動パワーIC全体の断面図であり、図7はメインスイッチMSが設けられる図5の左半分の断面図、図8はスタータースイッチSSと起動抵抗(抵抗素子)SRが設けられる図5の右半分の断面図である。なお、図5では符号は一部にのみ示す。

【0063】

これらの図に示すように、n+型のシリコンからなる半導体基板1はその主面にn-型のエピタキシャル層2を有している。そして、前記エピタキシャル層2に所定の不純物を選択的に順次形成すること等によってメインスイッチMS,スタータースイッチSSが形成される。即ち、アクティブ領域にはプレーナ構造のセルを規則的に複数配置し、半導体基板1の主面にゲート絶縁膜4を介して設けた隣接するセルの各ゲート5が互いに接続され、各セルを並列接続したメッシュゲート構造で構成される。外周のセルの各ゲート5はセル領域の外周部にて、例えば多結晶珪素(ポリシリコン)を用いたゲート配線6と接続され、このゲート配線6がゲート5の接続領域であるゲートパッドと接続されている。

【0064】

各セルでは、エピタキシャル層2がドレイン領域となり、半導体基板主面に形成されたp型層7がチャネルの形成されるベース領域となり、p型層7内に形成されたn+型層8がソース領域となり、MOSFETは縦型FET構造となっている。半導体基板1はドレインとなることから、図示しないが半導体基板1の裏面全体にドレイン電極が形成される。このドレイン電極は、例えばニッケル,チタン,ニッケル,銀を積層した積層膜で形成される。

【0065】

ゲート配線6は、層間絶縁膜9を介して上層に形成され、例えばシリコンを含有させたアルミニウムを用いたゲートガードリング10と電気的に接続されている。ソースとなるn+型層8は、例えばシリコンを含有させたアルミニウムを用いたソース配線11と電気的に接続されており、ソース配線11は半導体基板主面上に層間絶縁膜9を介して形成されている。このソース配線11は、ソースとなるn+型層8の他に、ベース電位を一定とするために、p型層7に設けられたp+型のコンタクト層12にも電気的に接続されている。

【0066】

フィールド絶縁膜3の下部には、半導体基板の外周に沿って角部を円弧状とした矩形環状に設けられた、p型拡散層からなるフィールド・リミッティング・リング(FLR)13が同心環状に複数配置されている。このFLRは、印加電圧の増加に連れて、アバランシェ降伏が起きる前に内周のFLR13から外周のFLR13に空乏層が延びてパンチスルーする構成となっており、最終的には最外周のFLR13の接合部分にて降伏する。

【0067】

また、前述の如く、高電圧印加時の降伏は、面積が大きい素子にてその表面部分以外にて行なわれるのが望ましい。このため、面積が小さく表面で降伏しやすいFLRでの降伏を回避し、面積が大きく表面で降伏し難いパワーMISFET(MOSFET)にて降伏させるため、パワーMISFETの耐圧を750V〜800Vとすれば、FLRの耐圧は800V以上とする。

【0068】

このFLRの降伏電圧は、理論上各FLR13間のパンチスルー耐圧及び最外周リングの降伏電圧の和となるため、FLR13の本数を増やすことによって高耐圧化することができるが、ターミネーション長を考慮して本数を決定する。FLR13は図1では5本、他の図では4本としてあるがこれに限定されない。

【0069】

FLR13が形成されたフィールド絶縁膜3上の一部分には起動抵抗SRが形成されている。図1(a)に示すように、起動抵抗SRを構成する抵抗層20は、FLR13群の内側の始端31から外側の終端32に向けて延在するように設けられ、かつ放熱面積を大きくして熱放散性を高めるべく蛇行させて長くなるようになっている。FLR13はP1〜P5で示すように5本としてあるが、これに限定されるものではない。

【0070】

図1(a)は起動抵抗(抵抗素子)SRを構成する抵抗層の蛇行パターンを示す模式図、図1(b)は駆動パワーICのFLRや抵抗層等を含む部分の断面図、図1(c)はFLRを含む半導体基板表面のポテンシャルと、抵抗層のポテンシャルを示すグラフである。

【0071】

ここで、図1(b)を参照しながら駆動パワーICが形成された半導体チップの周辺部分の断面部分について簡単に説明する。周辺領域のエピタキシャル層2の表面には、アクティブ領域側から周辺領域に向かってp型拡散層からなるP1〜P5で示されるフィールド・リミッティング・リング(FLR)13が図示しないアクティブ領域を囲むように形成されている。なお、P1の内側にはグランド(GND)電位にされるp型拡散層(P0)が形成されている。

【0072】

また、半導体チップの周縁にはガードリング14が設けられている。このガードリング14はフィールド絶縁膜3から外れたフィールド絶縁膜3よりも薄い絶縁膜24の下のエピタキシャル層2表面に設けられている。このガードリング14はエピタキシャル層2の主面に高濃度に不純物を拡散したn+型のリング状の拡散領域で形成されている。

【0073】

前記フィールド絶縁膜3上にはポリシリコン層で形成される抵抗層20が設けられている。この抵抗層20はその表面を層間絶縁膜9で被われている。また、前記P0上の層間絶縁膜9及びフィールド絶縁膜3の外周部分には、それぞれコンタクト孔21,22,23が設けられている。コンタクト孔23はフィールド絶縁膜3から外れた薄い絶縁膜24をも貫通するように形成されている。

【0074】

また、層間絶縁膜9上には半導体チップの周辺に沿って延在するリング状の導体膜25〜28が形成されている。導体膜25は周辺領域の内側、即ち、アクティブ領域側に設けられるとともに、コンタクト孔21にも充填されて抵抗層20に電気的に接続されている。導体膜26は導体膜25に近接して設けられ、メインスイッチMSのソース端子に接続されている。導体膜27は最外周のFLR13上に形成され、最外周のFLR13に電気的に接続されている。導体膜28はコンタクト孔22及びコンタクト孔23内にも充填され、抵抗層20とガードリング14を電気的に接続している。

【0075】

前記FLR13群では、印加電圧の増加につれて、アバランシェ降伏が起きる前に内周のFLR13から外周のFLR13に空乏層が延びてパンチスルーする構成になっており、最終的には最外周のFLR13のpn接合部分で降伏するようになっている。FLR13を設けることによって、パンチスルー耐圧とFLR13の数との積の分耐圧が向上することになる。従って、起動抵抗SRの耐圧は前記FLR13部分の耐圧と、フィールド絶縁膜3の厚さ等に起因する耐圧との和となり、総合的な耐圧は800V以上とさせるものである。

【0076】

コンタクト孔21に対応する抵抗層部分が抵抗素子(起動抵抗)SRの始端31となり、コンタクト孔22に対応する抵抗層部分が起動抵抗SRの終端32となる。始端31から終端32に至る起動抵抗SRとしての抵抗層20のパターンは、図1(a)に示すように、蛇行パターンとなっている。図1(b)では特に蛇行状態は明記せず簡略化してある。

【0077】

このように抵抗層20を蛇行させるパターンとすることによって、抵抗層20を長くして放熱面積の増大を図っている。また、抵抗層20のシート抵抗を10kΩ/□とすることによって、ある電圧における発熱量の一定化を図り、抵抗層20を形成するポリシリコン層の溶けによる破壊を防止するようにもなっている。抵抗層20は放熱を考慮して断面面積に対して表面積を増加させるために扁平形状となっている。抵抗層20は、例えば、ポリシリコン層からなり、抵抗値(シート抵抗)を調整するため、p導電型用の不純物であるボロンやn導電型用の不純物であるリン等を含有させる。

【0078】

本発明は、抵抗素子(起動抵抗)の始端と終端を直線的に結ぶ線分における抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致または近似するようにして耐圧劣化を抑止するものである。

【0079】

従って、最も望ましい形態は、抵抗素子を形成する抵抗層においては、材質(シート抵抗),パターン,幅,厚さを変え、フィールド絶縁膜では厚さを変える等を行い、抵抗素子の始端と終端を直線的に結ぶ線分における抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致するようにすることである。

【0080】

本実施形態1では抵抗層20の蛇行ピッチを一部で変えた構造になっている。即ち、図1(a)に示すように、始端31から最外周のFLR13に至る領域Aの抵抗層20の蛇行ピッチを、最外周のFLR13から終端32に至る領域Bの蛇行のピッチよりも広く形成した構造になっている。

【0081】

このような構造にすると、図1(c)に示すように、抵抗素子の始端と終端を直線的に結ぶ線分における抵抗素子各部のポテンシャル曲線が、始端31から最外周のFLR13に至る間の緩い勾配の直線eと、最外周のFLR13から終端32に至る前記緩い勾配の直線eよりも勾配が急になる急な勾配の直線fとなり、半導体基板の表面のポテンシャル曲線dに一部で一致し、一部で近接するようになる。また、抵抗素子に高電圧が印加された場合でも、不一致の箇所においても電位差が、例えば、50V程度以下と低くなる。この結果、フィールド絶縁膜の高電界に起因する破壊が防止できる。

【0082】

この点について、さらに説明を加える。抵抗素子の始端と終端を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致または近似するようになっている。従って、抵抗素子(起動抵抗)に高電圧が印加された状態でも、バルクで発生した電子・正孔対も電界によってどこか特定の箇所に引きつけられることもない。この結果、発生した電子・正孔対は再結合して電気的に中性化することになり、フィールド・リミッティング・リング間にチャネルができることもなく、耐圧は安定し耐圧劣化を抑止することができる。

【0083】

本実施形態1では、先に提案した技術に係わる図26(c)に示すように、高電界の発生箇所は、最外周のFLR13(P5)部分であることから、この最外周のFLR13(P5)部分で、抵抗素子ポテンシャルと半導体基板の表面のポテンシャルが一致するようにして、抵抗素子ポテンシャルと半導体基板の表面のポテンシャルの一致及び近似を図っている。即ち、最外周のFLR13部分を隔ててその内側と外側の前記線分における単位長さ当たりの抵抗値を相互に異なるようにしている。

【0084】

また、本実施形態1では、抵抗層20のシート抵抗を小さくして、熱による溶断を防止するようになっている。即ち、抵抗層20のシート抵抗を小さくして発熱量の増加を防止するとともに、抵抗層20を蛇行させて全長を長くして放熱面積の増大を図り、熱による溶断を防止している。

【0085】

図9は、シート抵抗を変えて本発明の抵抗素子を形成し、電圧−電流特性を測定した結果を示すグラフである。シート抵抗が高い場合には、印加電圧が高くなるに連れて、抵抗素子の発熱によって抵抗値が下降する。従って、電圧−電流特性をリニアにするためには、シート抵抗を10kΩ/□以下にする必要がある。

【0086】

図10は、不純物濃度を変えて本発明の抵抗素子を形成し、温度−シート抵抗特性を測定した結果を示すグラフである。このグラフからシート抵抗が大きな抵抗素子が負の温度特性をもち、シート抵抗が高いほど温度による抵抗変化が大きくなることが分かる。

【0087】

また、本実施形態では、スイッチングレギュレータの高電圧部を集積回路化し、制御回路については別チップとする半導体装置について説明を行なった。この構成によって、高電圧部と制御回路のそれぞれに適した半導体基板を用いることが可能となる。しかし、より集積回路化を進める場合には、図11に示すように、制御回路を一体化したスイッチングレギュレータの半導体装置として、本発明を適用することも可能である。

【0088】

つぎに、駆動パワーIC(半導体装置)の製造方法を図12乃至図16を用いて説明する。各図において、左側にはMOSFET部分を示し、右側には同一工程での抵抗素子(起動抵抗)部分を示す。

【0089】

先ず、例えばヒ素(As)が導入された単結晶珪素(シリコン)からなるn+型半導体基板1上に、エピタキシャル成長によってn-型からなるエピタキシャル層2を形成する。そして、このエピタキシャル層2の周辺領域にアクティブ領域を囲むようにp型ウエルを多重に形成してFLR13を形成し、この半導体基板の主面に酸化珪素膜を、例えば熱酸化法で形成し、この酸化珪素膜上に窒化珪素(SiN)膜のマスクを形成し、この窒化珪素膜をマスクとした選択的熱酸化によりフィールド絶縁膜3を形成する。この状態を図12に示す。

【0090】

つぎに、半導体基板主面に、熱酸化膜或いは熱酸化膜にCVD(Chemical VaporDiposition)による酸化珪素膜を積層したゲート絶縁膜4を形成し、半導体基板主面全面にゲート5或いは抵抗素子SRの導電膜となる多結晶珪素膜(ポリシリコン膜)5’をCVDにより形成し、この多結晶珪素膜5’に、ゲート5となる領域には例えばリンを、抵抗素子SRの導電膜となる領域には例えばボロンを導入する。この状態を図13に示す。

【0091】

つぎに、多結晶珪素膜5’を、選択的にエッチング除去してパターニングし、ゲート5及び抵抗素子SRの抵抗層20を形成し、MISFETのp型層7、n+型層8,コンタクト層12をホトリソグラフィによるマスクを用いたイオン注入によって形成する。この際に抵抗素子SRの導電膜の両端に接続抵抗を低減するためのp+型層(導電膜がn型の場合には、n+型層)を形成する。この状態を図14に示す。

前記多結晶珪素膜5’の選択エッチング時、所定のマスクを使用して、図1(a)に示すような蛇行ピッチが最外周のFLR13で変わる抵抗層20を形成する。

【0092】

つぎに、半導体基板主面上の全面に例えばPSG(Phosphorus Silicate Glass)膜を堆積させ、SOG(Spin On Glass )膜を塗布形成して層間絶縁膜9を形成し、この層間絶縁膜9に、ソース領域となるn+型層8,ゲート配線6,抵抗素子SRの接続領域を露出させる開口を設ける。この状態を図15に示す。

【0093】

つぎに、前記開口内を含む半導体基板主面上の全面に例えばシリコンを含むアルミニウムからなる導電膜(金属膜)を形成し、この金属膜をパターニングして、ゲートガードリング10,ソース配線11,ガードリング14を形成し、例えばソースガスの主体としてテトラエトキシシラン(TEOS)ガスを用いたプラズマCVDによる酸化珪素膜にポリイミドを塗布積層し、半導体基板主面の全面を覆う保護絶縁膜15を形成し、n+型半導体基板1の裏面に研削処理を施し、この裏面に例えば蒸着によりニッケル,チタン,ニッケル,銀を順次積層したドレイン電極16を形成する。この状態を図16に示す。

その後、説明は省略するが、常用の工程を経て駆動パワーICを形成する。

【0094】

このように、本実施形態1では、起動抵抗(抵抗素子)SRは、その製造においてはメインスイッチMSやスタータースイッチSSの形成工程を利用して形成することができるので、工程数を増加させることがない。また、起動抵抗SRはアクティブ領域に設けることなく既存のフィールド絶縁膜上に形成することから、駆動パワーICのチップサイズの小型化が図れる。

【0095】

本発明における抵抗素子の製造においては、抵抗素子の始端と終端を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致するように製造することが望ましいが、便宜的方法として、一部で一致させ一部が近似するようにする便法が考えられる。そこで、変形例について図17乃至図23を参照しながら説明する。

【0096】

図17は変形例1であり、蛇行パターンの蛇行幅は始端31から終端32に至るまで一定であるが、始端31から最外周のFLR13(P5)に至る部分の蛇行ピッチ及び抵抗層幅(抵抗線幅)が、最外周のFLR13(P5)から終端32に至る部分の蛇行ピッチ及び抵抗層幅に比較して広くかつ太くした例である。この例においても高電界に対する耐圧劣化を防止することができる。

【0097】

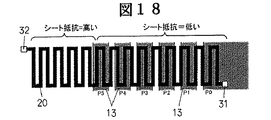

図18は変形例2であり、蛇行パターンの蛇行幅及び蛇行ピッチは始端31から終端32に至るまで一定であるが、シート抵抗をP5のFLR13の内外で変えた例である。始端31からP5のFLR13に至る部分のシート抵抗を低くし、P5のFLR13から終端32に至る部分のシート抵抗を高くした例である。この例においても高電界に対する耐圧劣化を防止することができる。

【0098】

図19は変形例3であり、蛇行ピッチは始端31から終端32に至るまで一定であるが、蛇行幅をP5のFLR13の内外で変えた例である。始端31からP5のFLR13に至る部分の蛇行幅を狭くし、P5のFLR13から終端32に至る部分の蛇行幅を高くした例である。この例においても高電界に対する耐圧劣化を防止することができる。

【0099】

図20は変形例4であり、P5のFLR13の内外で蛇行ピッチを変えるとともに、始端31からP5に至る部分では抵抗素子のポテンシャルが階段状に変化するようにし、P5から終端32に至る部分では蛇行幅が順次狭くなるようにして、図1(c)の半導体基板の表面のポテンシャル曲線dに一致させるようにしたものである。この例においては高電界に対する耐圧劣化は防止できる。

【0100】

図21は変形例5であり、始端31からP5に至る部分は直線とさせて、図1(c)の始端31から最外周のFLR13に至る間の緩い勾配の直線eのようにし、P5から終端32に至る部分では蛇行パターンとした例である。この例においても高電界に対する耐圧劣化を防止することができる。

【0101】

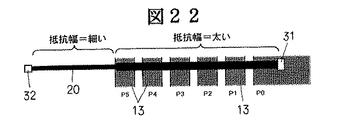

図22は変形例6であり、始端31から終端32までを直線パターンとするが、始端31からP5に至る部分の抵抗層幅は太く、P5から終端32に至る部分の抵抗層幅は細くした例である。抵抗層幅を適宜選択することにより、高電界に対する耐圧劣化を防止することができる。

【0102】

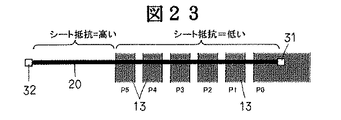

図23は変形例7であり、始端31から終端32までを抵抗層幅が一定の直線パターンとするが、始端31からP5に至る部分のシート抵抗を低くし、P5から終端32に至る部分のシート抵抗を高くした例である。シート抵抗を適宜選択することにより、高電界に対する耐圧劣化を防止することができる。

また、以上の各変形例同士の組み合わせも可能である。

【0103】

これら抵抗層20は、その製造において、▲1▼導体層を形成した後、エッチングによってパターニングして形成するか、▲2▼マスクを使用した選択的な蒸着法等によって形成する。

また、MOSFETの製造におけるポリシリコンによるゲート電極形成時に抵抗層20を形成することができる。

【0104】

シート抵抗は不純物の添加量によって制御可能である。また、抵抗層20を長さ域を分けて異なる材料で形成してもよい。例えば、金属線とポリシリコン層を途中で接続する構造でもよい。

【0105】

また、抵抗素子の始端と終端を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに近似するようにフィールド絶縁膜の厚さを従来の〜1.5μmに比較して、3〜5μmと厚くするようにしてもよい。

【0106】

本実施形態1によれば以下の効果を有する。

(1)抵抗素子(起動抵抗)SRの始端31と終端32を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致または近似するようになっている。従って、抵抗素子に高電圧が印加された状態でも、バルクで発生した電子・正孔対も電界によってどこか特定の箇所に引きつけられることもない。この結果、発生した電子・正孔対は再結合して電気的に中性化することになり、フィールド・リミッティング・リング間にチャネルができることもなく、耐圧は安定し耐圧劣化を抑止することができる。

【0107】

(2)起動抵抗を形成する抵抗層のシート抵抗は10kΩ/□以下と低いことから発熱量の一定化ができる。また、抵抗層を蛇行させて長くすることから放熱面積も増大して熱放散効率が増大する。これらのことから、高電圧が起動抵抗に印加されても、発熱に起因する抵抗層であるポリシリコン層の溶融による破壊事故が防止できる。

【0108】

(3)上記(1),(2)により、信頼性の高い半導体装置、即ちスイッチングレギュレータ用の駆動パワーICを提供することができる。

【0109】

(4)起動抵抗はアクティブ領域ではなく周辺領域のフィールド絶縁膜上に形成されることから、起動抵抗をアクティブ領域に形成する構造に比較して半導体チップの小型化が可能になり、半導体装置の製造コストの低減が達成できる。

【0110】

(実施形態2)

図24及び図25は本発明の他の実施形態(実施形態2)に係わる図であり、図24はスタータースイッチと起動抵抗部分を示す模式的断面図、図25は抵抗素子の模式的平面図と一部の断面図である。

【0111】

本実施形態1の駆動パワーICは、前記実施形態1の駆動パワーICにおいて、図24に示すように、各FLR13をその上の抵抗層20部分に電気的に接続させた構成になっている。図24は概念的な図であり、抵抗層20の下のフィールド絶縁膜3に直接コンタクト孔を設け、抵抗層20をこのコンタクト孔に埋め込んでFLR13と電気的に接続させた図としてあるが、フィールド絶縁膜3が厚く微細加工が難しいことから、実際には図25に示すように、層間絶縁膜9とFLR13が延在する箇所で薄い絶縁膜が存在する部分にそれぞれコンタクト孔を設け、このコンタクト孔部分を含め両者のコンタクト孔間に配線17を設けてFLR13と対応する抵抗層20を電気的に接続するようになる。

図25は起動抵抗SR部分を示す平面図であり、この図のA−A’,B−B’,C−C’に沿う部分の断面を右側にそれぞれ示してある。

【0112】

本実施形態2によれば、各FLR13と、各FLR13に重なる前記抵抗層20はそれぞれ電気的に接続されていて、それぞれの部位において等電位になることから、前記実施形態1の場合と同様に、抵抗素子のポテンシャルと半導体基板の表面のポテンシャルは各部で一致または近似するため、耐圧劣化を抑止することができる。

【0113】

以上本発明者によってなされた発明を実施形態に基づき具体的に説明したが、本発明は上記実施形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0114】

【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記のとおりである。

(1)抵抗素子の始端と終端を直線的に結ぶ線分の抵抗素子各部のポテンシャルが、前記始端と終端を直線的に結ぶ線分に対応する前記半導体基板表面各部のポテンシャルに一致または近似するようになっていることから抵抗素子(起動抵抗)に高電圧が印加された状態でも、耐圧劣化を抑止することができる。

(2)起動抵抗を構成する抵抗層のシート抵抗は10kΩ/□以下と低く発熱量の変動が小さいとともに、抵抗層を蛇行して長くなっていることから放熱面積も増大するため、効率的な熱放散が可能になることから、発熱に起因する抵抗層であるポリシリコン層の溶融による破壊事故が防止できる。

(3)上記(1),(2)により、信頼性の高い半導体装置、即ちスイッチングレギュレータ用の駆動パワーICを提供することができる。

(4)起動抵抗はアクティブ領域ではなく周辺領域のフィールド絶縁膜上に形成されることから、起動抵抗をアクティブ領域に形成する構造に比較して半導体チップの小型化が可能になり、半導体装置の製造コストの低減が達成できる。

【図面の簡単な説明】

【図1】本発明の一実施形態(実施形態1)による半導体装置(駆動パワーIC)の起動抵抗及び起動抵抗部分のポテンシャルを示す図表である。

【図2】実施形態1の駆動パワーICが組み込まれたスイッチングレギュレータを示す回路図である。

【図3】実施形態1のスイッチングレギュレータの起動タイミングを示すタイムチャートである。

【図4】実施形態1の駆動パワーICの模式的平面図である。

【図5】前記駆動パワーICの模式的断面図である。

【図6】前記駆動パワーICの等価回路図である。

【図7】前記駆動パワーICのメインスイッチ用トランジスタを含む一部の断面図である。

【図8】前記駆動パワーICのスタータースイッチ及び起動抵抗を含む一部の断面図である。

【図9】実施形態1の抵抗素子の特性を示すグラフである。

【図10】実施形態1の抵抗素子の温度特性を示すグラフである。

【図11】実施形態1の駆動パワーICをスイッチングレギュレータのコントロールICにモノリシックに組み込んだ例を示す模式図である。

【図12】実施形態1の駆動パワーICの製造において、半導体基板表面にFLR等やフィールド絶縁膜を形成した状態を示す要部の模式的断面図である。

【図13】実施形態1の駆動パワーICの製造において、トランジスタのゲート電極や抵抗素子の抵抗層となるポリシリコン層を形成した状態を示す要部の模式的断面図である。

【図14】実施形態1の駆動パワーICの製造において、トランジスタのゲート電極やソース領域及び抵抗層を形成した状態を示す要部の模式的断面図である。

【図15】実施形態1の駆動パワーICの製造において、層間絶縁膜及びコンタクト孔を形成した状態を示す要部の模式的断面図である。

【図16】実施形態1の駆動パワーICの製造において、保護絶縁膜を形成した状態を示す要部の模式的断面図である。

【図17】実施形態1の駆動パワーICにおける抵抗層の変形例1の模式図である。

【図18】実施形態1の駆動パワーICにおける抵抗層の変形例2の模式図である。

【図19】実施形態1の駆動パワーICにおける抵抗層の変形例3の模式図である。

【図20】実施形態1の駆動パワーICにおける抵抗層の変形例4の模式図である。

【図21】実施形態1の駆動パワーICにおける抵抗層の変形例5の模式図である。

【図22】実施形態1の駆動パワーICにおける抵抗層の変形例6の模式図である。

【図23】実施形態1の駆動パワーICにおける抵抗層の変形例7の模式図である。

【図24】本発明の他の実施形態(実施形態2)によるスタータースイッチと起動抵抗部分を示す模式的断面図である。

【図25】実施形態2による抵抗素子の模式的平面図と一部の断面図である。

【図26】本出願人の提案による半導体装置(駆動パワーIC)の起動抵抗及び起動抵抗部分のポテンシャルを示す図表である。

【図27】前記提案による駆動パワーICの耐圧劣化波形比較を示すグラフである。

【図28】耐圧測定回路図である。

【符号の説明】

1…半導体基板、2…エピタキシャル層、3…フィールド絶縁膜、4…ゲート絶縁膜、5…ゲート、6…ゲート配線、7…p型層、8…n+型層、9…層間絶縁膜、10…ゲートガードリング、11…ソース配線、12…p+型のコンタクト層、13…フィールド・リミッティング・リング(FLR)、14…ガードリング、15…保護絶縁膜、16…ドレイン電極、17…配線、20…抵抗層、21,22,23…コンタクト孔、24…絶縁膜、25〜28…導体膜、31…始端、32…終端、40…トランス、41…1次側コイル、42…ダイオードブリッジ整流回路、43…平滑コンデンサ、44…2次側コイル、46…平滑コンデンサ、47…3次側コイル、50…パルス幅制御回路(コントロールIC)。

Claims (15)

- スイッチングレギュレータの高電圧部を含む半導体装置であって、

(a)エピタキシャル層を主面に有する半導体基板と、

(b)前記半導体基板の主面上に形成され、前記高電圧部を構成し、前記エピタキシャル層をドレインとするメインスイッチ用MOSFETと、

(c)前記半導体基板の主面上に前記エピタキシャル層をドレインとして形成された、前記メインスイッチ用MOSFETのスタータースイッチ用MOSFETと、

(d)前記半導体基板の主面上に形成され、前記メインスイッチ用MOSFETおよびスタータースイッチ用MOSFETの周辺を多重に囲む複数のフィールド・リミッティング・リングと、

(e)前記フィールド・リミッティング・リング上に形成された、フィールド絶縁膜と、

(f)前記フィールド絶縁膜上に形成され、一方端が前記スタータースイッチ用MOSFETのゲートと電気的に接続され、他方端が前記スタータースイッチ用MOSFETのドレインと電気的に接続された抵抗素子と、

(g)前記抵抗素子を被う層間絶縁膜と、

(h)前記層間絶縁膜上に形成され、前記メインスイッチ用MOSFETのゲートおよびソース、前記スタータースイッチ用MOSFETのゲートおよびソースとそれぞれ電気的に接続される複数の配線と、

(i)前記半導体基板の裏面に形成され、前記メインスイッチ用MOSFETおよびスタータースイッチ用MOSFETのドレインと電気的に接続される裏面電極と、

(j)前記半導体基板の主面周縁に形成され、前記エピタキシャル層と電気的に接続される導電性のガードリングと、

を含み、

前記抵抗素子の一方端と他方端を結ぶ仮想線の方向において、前記仮想線の単位長さに相当する前記抵抗素子の抵抗が、前記抵抗素子の位置により異なり、前記仮想線に沿う前記抵抗素子各部のポテンシャルが、前記仮想線に沿う前記半導体基板表面各部のポテンシャルに近似するようになっていることを特徴とする半導体装置。 - 前記仮想線の単位長さ当たりの前記抵抗素子の抵抗値は最外周の前記フィールド・リミッティング・リングの内側と外側で相互に異なる請求項1に記載の半導体装置。

- 前記仮想線の単位長さ当たりの前記抵抗素子の抵抗値は段階的に変化している請求項1に記載の半導体装置。

- 前記抵抗素子は、抵抗素子の一方端と他方端との間に蛇行部分を有する請求項1に記載の半導体装置。

- 前記抵抗素子は、抵抗素子の一方端と他方端との間に蛇行部分を有するとともに、前記蛇行部分の蛇行ピッチが異なっている請求項1に記載の半導体装置。

- 前記抵抗素子は、蛇行部分を有するとともに、蛇行する幅が広い部分と、蛇行する幅が狭い部分とを有する請求項1に記載の半導体装置。

- 前記抵抗素子は、抵抗素子の一方端と他方端との間に蛇行する蛇行部分と、前記仮想線に沿う直線部分とを有する請求項1に記載の半導体装置。

- 前記抵抗素子は、線幅が異なっている請求項1に記載の半導体装置。

- 前記抵抗素子は、前記仮想線に沿う直線形状の抵抗素子となるとともに、線幅が一部で異なっている請求項1に記載の半導体装置。

- 前記抵抗素子は不純物が添加されたポリシリコン層で形成されている請求項1に記載の半導体装置。

- 前記抵抗素子は、金属部分と、この金属部分に電気的に接続される不純物が添加されたポリシリコン層で形成されている請求項1に記載の半導体装置。

- 前記抵抗素子は、その位置によりシート抵抗が異なっている請求項1に記載の半導体装置。

- 前記抵抗素子のシート抵抗は10kΩ/□以下である請求項1に記載の半導体装置。

- 前記抵抗素子の下に位置する前記フィールド絶縁膜の厚さは3〜5μm程度になっている請求項1に記載の半導体装置。

- 前記各フィールド・リミッティング・リングと、各フィールド・リミッティング・リングに重なる前記抵抗素子部分はそれぞれ電気的に接続されている請求項1に記載の半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000130705A JP4024990B2 (ja) | 2000-04-28 | 2000-04-28 | 半導体装置 |

| US09/842,015 US6492689B2 (en) | 2000-04-28 | 2001-04-26 | Semiconductor device switching regulator used as a DC regulated power supply |

| KR1020010023248A KR100626786B1 (ko) | 2000-04-28 | 2001-04-28 | 반도체 장치 및 그 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000130705A JP4024990B2 (ja) | 2000-04-28 | 2000-04-28 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001313367A JP2001313367A (ja) | 2001-11-09 |

| JP2001313367A5 JP2001313367A5 (ja) | 2005-02-10 |

| JP4024990B2 true JP4024990B2 (ja) | 2007-12-19 |

Family

ID=18639745

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000130705A Expired - Fee Related JP4024990B2 (ja) | 2000-04-28 | 2000-04-28 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6492689B2 (ja) |

| JP (1) | JP4024990B2 (ja) |

| KR (1) | KR100626786B1 (ja) |

Families Citing this family (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100535062B1 (ko) * | 2001-06-04 | 2005-12-07 | 마츠시타 덴끼 산교 가부시키가이샤 | 고내압 반도체장치 |

| US6552597B1 (en) * | 2001-11-02 | 2003-04-22 | Power Integrations, Inc. | Integrated circuit with closely coupled high voltage output and offline transistor pair |

| US20040235258A1 (en) * | 2003-05-19 | 2004-11-25 | Wu David Donggang | Method of forming resistive structures |

| JP2005268249A (ja) * | 2004-03-16 | 2005-09-29 | Philtech Inc | 半導体装置およびその製造方法 |

| TW200634375A (en) * | 2005-03-28 | 2006-10-01 | Elan Microelectronics Corp | Power line structure for liquid crystal display panel |

| JP4762663B2 (ja) * | 2005-10-14 | 2011-08-31 | 三菱電機株式会社 | 半導体装置 |

| JP5343306B2 (ja) | 2006-03-24 | 2013-11-13 | 富士電機株式会社 | スイッチング電源用icおよびスイッチング電源 |

| JP4895104B2 (ja) * | 2006-07-06 | 2012-03-14 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR100734328B1 (ko) * | 2006-07-24 | 2007-07-02 | 삼성전자주식회사 | 파워 게이팅 트랜지스터 스위치의 레이 아웃 구조 및 레이아웃 방법 |

| JP5564749B2 (ja) | 2006-11-20 | 2014-08-06 | 富士電機株式会社 | 半導体装置、半導体集積回路、スイッチング電源用制御icおよびスイッチング電源装置 |

| JP4974653B2 (ja) * | 2006-11-21 | 2012-07-11 | ローム株式会社 | 昇圧型スイッチングレギュレータの制御回路、それを用いた昇圧型スイッチングレギュレータ、およびそれらを用いた電子機器 |

| US8897039B2 (en) * | 2007-06-12 | 2014-11-25 | Bcd Semiconductor Manufacturing Limited | Method and system for pulse frequency modulated switching mode power supplies |

| KR100887884B1 (ko) * | 2007-10-01 | 2009-03-06 | 주식회사 동부하이텍 | 반도체 소자 |

| JP5104878B2 (ja) * | 2007-12-14 | 2012-12-19 | 富士電機株式会社 | 集積回路および半導体装置 |

| TWM351555U (en) * | 2008-05-06 | 2009-02-21 | Bcd Semiconductor Mfg Ltd | Method and apparatus for reducing standby power of switching mode power supplies |

| US8125799B2 (en) | 2009-10-23 | 2012-02-28 | Bcd Semiconductor Manufacturing Limited | Control circuits and methods for switching mode power supplies |

| JP2010239832A (ja) * | 2009-03-31 | 2010-10-21 | Panasonic Corp | 電流制限回路 |

| US8045348B2 (en) * | 2009-04-09 | 2011-10-25 | Bcd Semiconductor Manufacturing Limited | Switching mode power supply controller with high voltage startup circuits |

| US8242013B2 (en) * | 2010-03-30 | 2012-08-14 | Alpha & Omega Semiconductor Inc. | Virtually substrate-less composite power semiconductor device and method |

| JP5575610B2 (ja) * | 2010-11-09 | 2014-08-20 | 本田技研工業株式会社 | 電源装置 |

| US8482029B2 (en) * | 2011-05-27 | 2013-07-09 | Infineon Technologies Austria Ag | Semiconductor device and integrated circuit including the semiconductor device |

| CN102354703B (zh) * | 2011-10-19 | 2013-01-23 | 扬州杰利半导体有限公司 | 一种平面结构型超高压二极管芯片 |

| JP5637154B2 (ja) * | 2012-02-22 | 2014-12-10 | トヨタ自動車株式会社 | 半導体装置 |

| JP6079456B2 (ja) | 2013-06-07 | 2017-02-15 | 三菱電機株式会社 | 半導体装置の検査方法 |

| CN103746002B (zh) * | 2013-12-17 | 2016-04-20 | 西安理工大学 | 一种台阶形沟槽-场限环复合终端结构 |

| DE112014006442T5 (de) * | 2014-03-06 | 2016-11-24 | Mitsubishi Electric Corporation | Halbleitervorrichtung und Verfahren zum Testen derselben |

| DE102016120301A1 (de) * | 2016-10-25 | 2018-04-26 | Infineon Technologies Ag | Leistungshalbleitervorrichtungs-Abschlussstruktur |

| WO2019065049A1 (ja) * | 2017-09-28 | 2019-04-04 | ローム株式会社 | 電源ic |

| DE102021117826A1 (de) | 2021-07-09 | 2023-01-12 | Infineon Technologies Ag | Leistungshalbleitervorrichtung Verfahren zur Herstellung einer Leistungshalbleitervorrichtung |

| CN117116915B (zh) * | 2023-10-25 | 2024-01-19 | 合肥晶合集成电路股份有限公司 | 半导体结构及其制备方法、方块电阻的测量方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2167229B (en) * | 1984-11-21 | 1988-07-20 | Philips Electronic Associated | Semiconductor devices |

| JPH0612654B2 (ja) * | 1985-04-29 | 1994-02-16 | ソニー株式会社 | 陰極線管の内蔵抵抗器 |

| GB9207860D0 (en) * | 1992-04-09 | 1992-05-27 | Philips Electronics Uk Ltd | A semiconductor component |

| JP3207615B2 (ja) * | 1992-06-24 | 2001-09-10 | 株式会社東芝 | 半導体装置 |

| JP2850694B2 (ja) * | 1993-03-10 | 1999-01-27 | 株式会社日立製作所 | 高耐圧プレーナ型半導体装置 |

| JPH07297368A (ja) * | 1994-04-25 | 1995-11-10 | Rohm Co Ltd | 抵抗体および半導体素子 |

| JP3331846B2 (ja) | 1995-12-28 | 2002-10-07 | 株式会社日立製作所 | 半導体装置 |

| JPH10163429A (ja) * | 1996-11-29 | 1998-06-19 | Mitsubishi Electric Corp | 半導体装置 |

-

2000

- 2000-04-28 JP JP2000130705A patent/JP4024990B2/ja not_active Expired - Fee Related

-

2001

- 2001-04-26 US US09/842,015 patent/US6492689B2/en not_active Expired - Lifetime

- 2001-04-28 KR KR1020010023248A patent/KR100626786B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR20010098965A (ko) | 2001-11-08 |

| US20010035554A1 (en) | 2001-11-01 |

| KR100626786B1 (ko) | 2006-09-22 |

| US6492689B2 (en) | 2002-12-10 |

| JP2001313367A (ja) | 2001-11-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4024990B2 (ja) | 半導体装置 | |

| JP4469584B2 (ja) | 半導体装置 | |

| JP5321768B1 (ja) | 半導体装置 | |

| US8860145B2 (en) | Semiconductor device, integrated circuit including the semiconductor device, control IC for switching power supply and the switching power supply | |

| JP5104878B2 (ja) | 集積回路および半導体装置 | |

| JP6083464B2 (ja) | 半導体装置 | |

| US10043872B2 (en) | Semiconductor device | |

| US20030218220A1 (en) | Power semiconductor device and method of manufacturing the same | |

| JP2005005443A (ja) | 高耐圧半導体装置 | |

| CN105590922B (zh) | 半导体装置 | |

| JPH0669423A (ja) | 半導体部品 | |

| TWI750626B (zh) | 雙向功率器件 | |

| JPH0832031A (ja) | 高電圧のプレーナ端部終端構造物とその製造方法 | |

| JP3929643B2 (ja) | 半導体装置 | |

| JP4894097B2 (ja) | 半導体装置 | |

| JP2016042542A (ja) | 半導体装置及びその製造方法 | |

| US7091559B2 (en) | Junction electronic component and an integrated power device incorporating said component | |

| JP2019161181A (ja) | 半導体装置、パワーモジュールおよび電力変換装置 | |

| JP2000252426A (ja) | 半導体装置及びその製造方法 | |

| JP2001507524A (ja) | ハーフブリッジ回路を具える半導体デバイス | |

| JP3906504B2 (ja) | 絶縁分離型半導体装置 | |

| JP2007123926A (ja) | 半導体装置 | |

| WO2015097581A1 (en) | Power semiconductor devices having semi-insulating field plate | |

| US20120286829A1 (en) | Semiconductor device and driving circuit | |

| US11502073B2 (en) | Semiconductor device and power source control IC |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040303 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040303 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20051014 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051101 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061003 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061204 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070619 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070816 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071002 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071004 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101012 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111012 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111012 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111012 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111012 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121012 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121012 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131012 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |