JP3879463B2 - 液晶表示パネル,液晶表示装置、及び液晶テレビ - Google Patents

液晶表示パネル,液晶表示装置、及び液晶テレビ Download PDFInfo

- Publication number

- JP3879463B2 JP3879463B2 JP2001284356A JP2001284356A JP3879463B2 JP 3879463 B2 JP3879463 B2 JP 3879463B2 JP 2001284356 A JP2001284356 A JP 2001284356A JP 2001284356 A JP2001284356 A JP 2001284356A JP 3879463 B2 JP3879463 B2 JP 3879463B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- liquid crystal

- signal

- crystal display

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 348

- 230000005684 electric field Effects 0.000 claims description 156

- 239000000758 substrate Substances 0.000 claims description 97

- 230000004044 response Effects 0.000 description 65

- 239000010408 film Substances 0.000 description 45

- 238000010586 diagram Methods 0.000 description 43

- 206010047571 Visual impairment Diseases 0.000 description 38

- 239000000463 material Substances 0.000 description 24

- 230000000694 effects Effects 0.000 description 17

- 230000008859 change Effects 0.000 description 16

- 238000000034 method Methods 0.000 description 16

- 239000011521 glass Substances 0.000 description 12

- 239000011159 matrix material Substances 0.000 description 10

- 229910021417 amorphous silicon Inorganic materials 0.000 description 9

- 125000004093 cyano group Chemical group *C#N 0.000 description 5

- 229910052731 fluorine Inorganic materials 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 4

- 239000011737 fluorine Substances 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 230000006872 improvement Effects 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 230000001629 suppression Effects 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910004205 SiNX Inorganic materials 0.000 description 2

- VNTLIPZTSJSULJ-UHFFFAOYSA-N chromium molybdenum Chemical compound [Cr].[Mo] VNTLIPZTSJSULJ-UHFFFAOYSA-N 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 239000007772 electrode material Substances 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000004744 fabric Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 239000011324 bead Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229920005575 poly(amic acid) Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134363—Electrodes characterised by their geometrical arrangement for applying an electric field parallel to the substrate, i.e. in-plane switching [IPS]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/043—Compensation electrodes or other additional electrodes in matrix displays related to distortions or compensation signals, e.g. for modifying TFT threshold voltage in column driver

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0252—Improving the response speed

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0257—Reduction of after-image effects

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Computer Hardware Design (AREA)

- Geometry (AREA)

- Theoretical Computer Science (AREA)

- Liquid Crystal (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Transforming Electric Information Into Light Information (AREA)

Description

【発明の属する技術分野】

本発明はアクティブマトリクス型液晶表示パネル、及びアクティブマトリクス型液晶表示装置、及び液晶テレビに関わる。

【0002】

【従来の技術】

液晶表示装置は2枚のガラス基板を所定の間隔をあけて配置し、そのすき間に液晶を注入して構成する。ガラス基板と液晶層の間には配向膜と呼ばれる高分子薄膜を配置し、液晶分子を配列させるために配向処理を施している。表示はこの配列された液晶分子に電界を印加することにより、その配向方向を変化させ、それにより生じる液晶層の光学特性の変化を利用して行う。

【0003】

従来のアクティブ駆動型液晶表示装置では、TN方式に代表されるように、液晶を挟持する一対の基板においてそれぞれの内側に透明電極を設け、これら電極間に生じる基板面に垂直な方向の電界により液晶分子を駆動する。すなわち、この基板に垂直な電界により液晶分子が立ちあがることにより光のスイッチを行う。このような方式では、特に中間調において、液晶パネルを見る方向により色調の反転などを生じ、視野角が狭いことが大きな問題である。

【0004】

これを解決する一つの手段として、特公昭63−21907号公報によりIPS方式が開示されている。図32及び図33にIPS方式液晶表示装置の画素部の電極構造及び断面図を示した。なお、ここでは特に画素内2分割の電極構造を示した。また、図34には液晶表示装置を駆動するシステム概略図を示した。この方式では、液晶を挟持する一対の基板のうち、一方の基板上に2つの異なる電極、すなわち画素電極106及び共通電極103を形成し、これら電極間に生じる均一な、基板面にほぼ平行な電界5によって、液晶分子を基板面にほぼ平行な面内で回転させることにより光をスイッチする方式である。そのために画面を見る角度(視野角)によって階調,色調の反転が生じることがなく、従来のTN方式に比べ視野角が広い。このような視角特性に優れたIPS方式は、従来のTN方式に変わる新しい液晶表示装置として期待され、今後の大画面液晶モニタや液晶テレビにとって重要な技術である。しかし、現状のIPS液晶表示装置において、今後の液晶テレビやDVDビデオ再生対応モニタなど動画対応ディスプレイへの展開を考えると、応答速度の向上が最大の課題である。

【0005】

IPS方式液晶表示装置の高速応答化については主に液晶材料からの検討が進められてきた。その中で、液晶材料の開発は大きく2つの方向で進められてきた。すなわち、液晶材料の高極性化(高Δε化)と低粘度化である。しかしながら、一般に液晶材料は極性が高くなると粘度も高くなるというトレードオフの関係や、液晶材料の特性が液晶表示装置の表示特性やその信頼性に直接影響することから、材料開発の裕度が制限され、液晶材料開発だけによる高速応答化には限度がある。そこで、現在ではこれら液晶材料の開発に加えて、駆動方法や画素構造の観点から高速応答化へのアプローチも並行して進められている。

【0006】

駆動法による高速応答化については特開2001−34238号公報で提案されている。これは、階調変化分を超える表示データ(オーバードライブ電圧)を画素に入力することで、電圧変化量を大きくし、応答速度の向上を図る方法である。このような方法は一般にオーバードライブ駆動と呼ばれ、階調変化直後に目標透過率を達成するために必要な電圧より高い電圧を一時的に印加することで目的透過率まで到達する時間(応答時間)を早める手段である。なお、後述するがこの手段は中間調でのみ有効である。

【0007】

また、画素構造を変えることによって高速応答化を実現しようとする手段が特開平11−231344号公報や特開平11−316383号公報で提案されている。特開平11−231344号公報では従来のIPS方式液晶表示装置において、画素電極及び共通電極が形成されたアレイ基板(電極基板)の対向基板側に第2の共通電極を形成した構造である。これは、画素電極と第2の共通電極間に生じる電界により、対向基板近傍の液晶分子を有効的に駆動することによって応答速度の向上を図る方法である。また、特開平11−316383号公報では画素電極及び共通電極の電極間距離をセルギャップ(液晶層の厚み)以下に狭めた構造、もしくは画素電極と共通電極を重畳させた構造を用いることにより、特に電極端部で強電界を発生させることにより応答速度を向上させる方法である。

【0008】

【発明が解決しようとする課題】

しかしながら、上記で述べた各手段にはそれぞれ以下に述べる課題を有する。

【0009】

オーバードライブ駆動は中間調でのみ有効な手段であり、全ての階調における応答速度を改善することができないことが、この駆動における最大の課題である。液晶表示装置の液晶層に印加している電圧は通常、交流電圧であり、低電圧側は電圧無印加(V=0V)より下の電圧というものは存在しないことから、電圧無印加状態が表現する階調への応答速度を速めることはできない。また、高電圧側においても、信号線ドライバの電気的耐圧により、画素に印加できる電圧は限られており、通常その電圧は液晶を十分に駆動する電圧(動作電圧)とほぼ等しい。そのため高電圧側においては階調の応答速度を速めるために使える電圧幅(ΔV:オーバードライブ電圧)がほとんどないために、高電圧側が表現する階調への応答速度を速めることはできない。すなわち、オーバードライブ駆動では中間調での応答速度を向上することが可能であり、応答速度の階調依存を平坦化できるが、特に高電圧側の応答速度を改善することはドライバ耐圧の制限により不可能である。

【0010】

一方、画素構造による高速化応答技術については、特に表示性能を劣化させる課題を有する。特開平11−231344号公報に提案されている対向基板側に第2の共通電極を形成する手段では、横電界成分に加え、縦電界成分が増加するために正の誘電率異方性を有する液晶分子においては基板面に対して分子が立ちあがることから、色調など色再現性に問題を生じる。

【0011】

また、特開平11−316383号公報に提案されている電極間隔をセルギャップ(液晶層厚み)以下に狭めた構造では、表示性能を著しく低下させる要因の一つである残像現象を生じる。この残像現象は、本発明者らの検討から、応答速度の向上に有効的に作用している電極端部で生じる強電界が主原因であることがわかった。液晶分子は、電界強度に応じて基板面に平行な面内で回転するが、電極が重畳しているなど極度に電極間隔が狭い場合には、電極端部での電界集中により発生する強電界により液晶層中の液晶分子の平均的な回転角度よりも数倍大きく回転している。例えば、白色を表示させる場合には液晶層中の平均的な液晶分子長軸が偏光板の透過軸に対しておよそ45°回転する必要がある。この液晶分子の回転角には分布があり、実際には電界強度が極度に大きい電極端部近傍では45°以上捻れている。この時、特に電極端部近傍では、この極度に大きな液晶分子の回転により生じた回転トルクが負荷として配向膜表面に伝わり、その結果として配向膜表面の塑性変形が主原因と考えられる残像・焼付き現象を生じる。この残像現象は強電界が保持される時間と大きく相関があり、その保持時間が長いほど悪化する。

【0012】

本発明の目的は、高速応答を実現できる液晶表示パネル、及び液晶表示装置を提供するものである。

【0013】

本発明の別の目的は、表示性能を大きく左右する残像現象を抑制した高品質な液晶表示パネル、及び液晶表示装置を提供することである。

【0014】

【課題を解決するための手段】

本発明の一つの実施態様によれば、一対の基板と、これら一対の基板間に配置した液晶層とを有する液晶表示パネルで、一対の基板の一方の基板に、ある方向に伸びた第1の電極,第2の電極、及び第3の電極を配置し、1フレーム期間内の初期段階と途中段階で、それぞれ第1の電極,第2の電極、または第3の電極に与える電位を変えて表示を制御するというものである。

【0015】

具体的には、第1の電極,第2の電極、及び第3の電極間のそれぞれの電位差について、少なくとも2つの電位差の関係が、1フレーム期間内の初期段階と途中段階で異なるように制御するというものである。

【0016】

さらに、上述の制御をより有効に行う手段として、第3の電極を、第1の電極と第2の電極間の第1の電極により近い位置に配置したというものである。

【0017】

さらに具体的な構成は、第1の電極または第2の電極の一方の電極が第1の能動素子を介して第1の信号線に接続され、第1の電極または第2の電極のうち第1の能動素子に接続されていない他方の電極が共通配線に接続され、第3の電極が第2の能動素子を介して第2の信号線に接続されているというものである。

【0018】

さらには、第1の信号線に交差するように配置され第1の能動素子に接続された第1の走査線を有し、第2の信号線に交差するように配置され第2の能動素子に接続された第2の走査線を有し、第1の信号線,第1の走査線,第2の信号線、及び第2の走査線に囲まれた領域に対応して画素を構成し、この画素を複数配置して表示領域を形成しているというものである。

【0019】

さらには、この表示領域の外側に、第1の信号線に接続された第1の信号駆動回路と、第2の信号線に接続された第2の信号駆動回路と、第1の走査線に接続された第1の走査駆動回路と、第2の走査線に接続された第2の走査駆動回路と、共通配線に接続された共通配線駆動回路を有しているというものである。

【0020】

さらには、この表示領域の外側に、第1の信号駆動回路,第2の信号駆動回路,第1の走査駆動回路,第2の走査駆動回路、及び共通配線駆動回路に接続された表示制御回路を有しているというものである。

【0021】

さらに、具体的な別の構成は、第1の電極または第2の電極の一方の電極が第1の能動素子を介して、及び第3の電極が第2の能動素子を介して信号線に接続され、第1の電極または第2の電極のうち、第1の能動素子に接続されていない他方の電極が共通配線に接続されて、信号線に交差するように配置され第1の能動素子及び第2の能動素子に接続された走査線を有し、信号線,走査線に囲まれた領域に対応して画素を構成し、これらの画素を複数配置して表示領域を形成しており、これらの画素に対応するそれぞれの走査線は、1フレーム期間内に2回走査されるというものである。この2回の走査は、異なる走査電圧値で行うものであり、また第1の能動素子および第2の能動素子は異なる閾値特性を有するというものである。

【0022】

本発明の別の実施態様によれば、少なくとも一方の基板が透明基板である一対の基板と、この一対の基板間に配置した液晶層とを有する液晶表示パネルで、一対の基板の一方の基板には複数の画素により構成される表示領域を有し、この画素内には、ある方向に伸びた第1の電極,第2の電極、及び第3の電極を配置し、1フレーム期間内の初期段階と途中段階で、それぞれ第1の電極,第2の電極、または第3の電極に与える電位を変えて表示を制御するというものである。

【0023】

さらに、これらの第1の電極,第2の電極、及び第3の電極は、独立して電位が与えられ、第1の電極,第2の電極、及び第3の電極間のそれぞれの電位差について、少なくとも2つの電位差の関係が、1フレーム期間内の初期段階と途中段階で異なっているというものである。

【0024】

さらに、この第3の電極は、第1の電極と第2の電極間の第1の電極により近い位置に配置され、第1の電極と第3の電極の電位差と、第2の電極と第3の電極の電位差が、1フレーム期間内の初期段階と途中段階で異なっているというものである。

【0025】

本発明の別の実施態様は、少なくとも一方の基板が透明基板である一対の基板と、この一対の基板間に配置した液晶層とを有する液晶表示パネルで、1フレーム期間内の初期段階と途中段階で、液晶層中に形成される電界を変えて表示を制御するというものである。

【0026】

さらに、1フレーム期間内の初期段階では強電界を形成し、途中段階では初期段階の電界よりも弱い電界を形成するよう電界を変えるというものである。

【0027】

本発明の別の実施態様は、液晶表示装置が、一対の基板と、この一対の基板間に配置した液晶層と、この一対の基板の一方の基板に配置したある方向に伸びた第1の電極,第2の電極、及び第3の電極とを有し、1フレーム期間内の初期段階と途中段階で、それぞれ第1の電極,第2の電極、または第3の電極に与える電位を変えて表示を制御するように構成した液晶表示パネルと、光源と、を有するというものである。

【0028】

本発明の別の実施態様は、液晶テレビが、一対の基板と、この一対の基板間に配置した液晶層と、この一対の基板の一方の基板に配置したある方向に伸びた第1の電極,第2の電極、及び第3の電極とを有し、1フレーム期間内の初期段階と途中段階で、それぞれ第1の電極,第2の電極、または第3の電極に与える電位を変えて表示を制御するように構成した液晶表示パネルと、光源と、この光源を制御するインバータ回路と、チューナーを有するというものである。

【0029】

【発明の実施の形態】

図1を用いて、本発明について説明する。図1(a)は本発明の概要を説明するための液晶パネルの画素部の断面概略図であり、図1(b)は図1(a)で示した各電極の1フレーム周期内における電位変化の例を示している。

【0030】

図1(a)の構成は、例えばガラス基板やプラスチック基板、またはガラス基板とプラスチック基板を張り合わせた基板のような少なくとも一方が透明な一対の基板7及び8に液晶層14を挟持して構成されている。基板7,8にはそれぞれ偏光板15が配置されており、基板7には後述する電極を配置し、さらにこれらの電極上には絶縁膜9,10及び配向膜11が形成されている。また、基板8にはカラーフィルタ12及びカラーフィルタ12の保護膜となるオーバーコート膜13,配向膜11が形成された構成である。尚、このカラーフィルタは特に基板8側に形成する必要がなく、基板7側に配置しても良い。

【0031】

基板7には複数の画素により構成された表示領域が形成されており、図1(a)は、これらの各画素の断面図を示したものである。即ち、本発明では、基板7に形成された表示領域中の各画素内に線状若しくは櫛歯状の形状をした第1の電極1,第2の電極2、及び第3の電極を配置した電極構成であり、各電極(第1の電極1,第2の電極2、及び第3の電極3)には独立に電位を与えることができるようにしているというものである。さらに、1フレーム期間内の初期段階と途中段階で、それぞれ第1の電極,第2の電極、または第3の電極に与える電位を変えて表示を制御するというものである。即ち、1フレーム期間内で各電極に与える電位を変えることによって、液晶層中に形成される電界を変化させるというものである。詳しくは、第1の電極,第2の電極、及び第3の電極間のそれぞれの電位差について、少なくとも2つの電位差の関係が、1フレーム期間内の初期段階と途中段階で異なるようにするこで、この電界の変化を実現しようというものである。

【0032】

具体的には、図1(a)のように、1フレーム期間内の初期段階(t0 <t<t1 )では、第1の電極1と第3の電極3との間に電界4が発生するように電位を与え、この電界4によって液晶層14の第1の電極1及び第3の電極3付近の液晶分子を制御し、次に、図(b)のように、1フレーム期間内の途中段階(t0<t<t1 )では、第1の電極1と第3の電極3との間に電界4を発生させないように電位を与え、液晶層中には電界5のみで液晶層14の液晶分子を制御するというものである。

【0033】

即ち、1フレーム周期内の初期段階(t0<t<t1)では、液晶層中に強電界を発生させ、1フレーム期間内の途中段階(t0<t<t1)で、初期段階に発生させた電界よりも小さい電界を発生させるというものである。

【0034】

また、後述する残像現象の抑制を考えれば、初期段階から途中段階の切り替えは、長くとも1フレーム周期の半分以下の時間(0<t<(t2−t0)/2)内に行うことが望ましい。

【0035】

尚、第1の電極1は画素電極もしくは共通電極のどちらか一方の電極であり、第2の電極2は第1の電極と異なる電極、即ち、第1の電極1が画素電極の場合には第2の電極2は共通電極であり、第1の電極1が共通電極の場合は第2の電極2は画素電極である。

【0036】

また、上述したような1フレーム期間中の電界制御は、第1の電極1,第2の電極2、及び第3の電極3の各電極に所望の電位を与えれば制御可能であるので特に第1の電極1,第2の電極2、及び第3の電極3の配置位置の関係は問題ではない。しかし、電界は各電極間の距離に応じて強さが決まるものであり、より有効に上述の電界の制御を行う場合には、第1の電極1,第2の電極2、及び第3の電極3の配置位置の関係は重要である。

【0037】

よって、図1(a),(b)では有効に上述の電界制御を行うための電極配置として、3つの電極のうち1つの電極(例えば第3の電極)を、残りの2つの電極(この場合には第1の電極と第2の電極)のうちのどちらか一方(例えば第1の電極)により近づけて配置している。このように配置することで、より有効に上述の電界制御が可能となる。

【0038】

さらに、第1の電極1と第3の電極3との電位差をΔV1 ,第1の電極1と第3の電極3との距離をdL ,第2の電極2と第3の電極3との電位差をΔV2 ,第2の電極2と第3の電極3との距離dH とした場合に、1フレーム周期内の初期段階(t0<t<t1)には下記に示した(式1)を満足し、1フレーム周期の途中段階(t1<t<t2)では(式2)を満足するように駆動する。

【0039】

【数1】

【0040】

【数2】

【0041】

また、後述する残像現象の抑制を考えれば、電位差ΔV1 が、長くとも1フレーム周期の半分以下の時間(0<t<(t2−t0)/2)内に小さくなるように駆動することが望ましい。

【0042】

この電極構造及び第3の電極電位を1表示期間内で変化させることにより残像現象を抑制した高速応答が可能な液晶表示装置を実現できる。以下、高速応答を実現できる理由と残像現象を抑制できる理由について詳しく説明する。

【0043】

図1(b)に示した各電極の電位変化の例に基づき説明する。1フレーム周期内での初期段階(t0<t<t1)においては、第2の電極と第3の電極が実質的にほぼ同電位(V2≒V3)であり、液晶層中には第1の電極1と第2の電極2の間に印加されるほぼ均一な横電界5と、第1の電極1と第3の電極3の間に印加される電界4により液晶分子を駆動する。第2の電極2と第3の電極3の電位は実質的にほぼ同電位であるが、第1の電極1までの距離が異なる(dL<dH)ことから、第3の電極と第1の電極との間に生じる電界4の強度は、第2の電極と第1の電極との間に生じる電界5の強度よりも大きくなる。

【0044】

液晶分子は電界により従って回転して向きを変え、その回転は電界強度が大きいほど高速かつ大きい。そのために、第1の電極と第3の電極近傍に存在する液晶分子は、これら電極間に生じるより大きな電界4により高速かつ大きく回転する。一方、第1の電極と第2の電極間に存在する液晶分子は、基本的にこれら電極間に生じるほぼ均一な横電界5により駆動される。しかしながら、液晶は連続体として考えられ、液晶の弾性効果により、大きな電界4で高速に駆動された液晶分子が、均一横電界5で緩やかに駆動している液晶分子を引きずる効果を有する。そのために、第1の電極1と第2の電極2の間にある液晶分子は、均一な横電界5に応じて回転するのに加えて、より大きな電界4により高速に駆動された液晶分子に引きずられ、従来の均一な横電界だけで液晶分子を駆動する横電界方式の液晶表示装置に比べ高速応答を実現することが可能である。

【0045】

さらに、強電界の効果を考え液晶分子の高速応答化を実現するためには次のような構造が有効である。

【0046】

一つは、第1の電極1と第2の電極2のうち、第3の電極3との距離が近い側に配置された電極(図中では第1の電極1)と、第3の電極との距離(dL )をより近づける構造である。

【0047】

また一つは、図2(a)に示したように第1の電極と第2の電極のうち、第3の電極との距離が近い側に配置された電極(図中では第1の電極1)と、第3の電極3とが画素表示領域内で少なくとも一部分が重畳している構造が望ましく、さらには部分的に重畳している電極の合わせマージンを考慮すると、ほぼ全面で重畳している図2(b)に示した構造が望ましい。なぜなら、電極が重畳することにより、重畳した電極の端部では電界集中を生じやすく、より大きな電界が発生するからである。従って、本発明を実施するためには非常に有効である。またこの時、重畳している一組の電極のうち、下層に配置されている電極(図中では第3の電極3)幅が、その上層に配置されている電極(図中では第1の電極1)の幅より広い構造が望ましい。電極が重畳し、かつ重畳した下層の電極幅を広くすることによりこれら電極端部で有効に強電界を発生させることができるというものである。

【0048】

さらに図2(a)や図2(b)に示したように電極が重畳している場合には、少なくとも下層に配置されている電極がITOなどの透明導電膜であることが望ましい。上述したように重畳した電極の端部では強電界により液晶分子は高速に駆動される。そのために、他の領域に比べて電圧印加開始後、最初に光が透過する。下層電極が透明電極である場合には、このような領域の光を利用できるために、画素全体の応答時間がより短縮できる。特に応答速度が遅いといわれる中間調表示での応答時間の短縮が期待できる。

【0049】

なお、電極が重畳している場合には、電極間隔dL は、それら電極間に介在する絶縁膜9の膜厚にほぼ等しい。

【0050】

この強度の異なる電界を形成するには、通常の表示に必要な電界の他に、この電界と同じ方向の成分を持つ別の電界を形成すれば良いが、より有効に電界形成し高速化を実現するためには上述の(式1)で示したように、少なくとも図1(a)で示した第1の電極1と第3の電極3との間に生じる電界4の強度が第1の電極1と第2の電極2との間に生じる電界5の強度より大きくすることが望ましい。

【0051】

なお、各電極が配置される層として、図1(a)では第1の電極1が、第2の電極2及び第3の電極3と異なる層に配置されているが、本発明による高速応答化の効果を得るためには、電極が重畳する場合を除いて、これらすべての電極が同層に配置されていてもよい。

【0052】

以上により、強電界の効果を考慮して液晶分子の高速応答化を実現するための構造及び駆動方法を説明したが、一方でこの強電界は高速応答化には非常に有効であるが、液晶表示性能を著しく劣化させる要因の一つである残像現象を発生させるという副作用を有することがわかった。特に図2(a)及び(b)に示したような電極が重畳している構造においてはその副作用は顕著に現れる。

【0053】

上述したように本発明者らの検討から、部分的に発生する非常に大きな電界により液晶分子が液晶層中の平均的な液晶分子の回転角度よりも数倍大きく回転している場合には、液晶分子の回転で生じる回転トルクにより、配向膜表面の塑性変形が主原因と考えられる残像を生じることがわかった。さらに、この残像現象は大きな回転トルクが保持される時間、すなわち強電界が保持される時間と大きく相関があり、その保持時間が長いほど悪化することがわかった。従って、液晶分子に強電界が印加されても、その保持時間を短縮することで残像を抑制することができることを見出した。

【0054】

そこで、本発明ではこれらのことに着目し、まず1フレーム周期内の初期段階(t0<t<t1)には強電界を発生させ、液晶分子を高速に応答させる。その後、例えば図1(b)に示したように、第3の電極電位V3 を第1の電極電位V1 との差が小さくなるように変化させることにより、1フレーム周期内で時間tがt1<t<t2を満たす領域(途中段階)では強電界成分をほぼなくし、第1の電極1と第2の電極2により生じる均一な横電界5と第3の電極3と第2の電極2により生じる均一な横電界6により液晶を駆動する。このように構成することにより、強電界は1フレーム期間中の初期段階である一時的(t0<t<t1)にしか印加されないために残像現象を生じることがなくなる。

【0055】

以上のような電極構造及び1フレーム周期内の各電極の電位変化を有する構成により、高速応答化と残像抑制を両立できる液晶表示装置を得ることができる。さらに本構成では、電極間隔を例えば液晶層の厚み以下に狭めることにより電界強度を大きくし液晶分子を駆動しているために、オーバードライブ駆動のようにドライバ耐圧による制限がなく、全階調に対して高速応答化を実現できる。

【0056】

以下、本発明を具体的に実施するための電極及び配線構造と、各電極及び配線へ供給される信号波形について実施例で説明する。なお、本実施例で示した画素構造は、画素内2分割であり、また、第3の電極が共通電極もしくは画素電極と重畳した構造であるが、本発明は特にこれら画素構造に限定されるものではない。また、各電極及び配線に供給される信号波形についても、実施例で示した信号波形に限定されるものではない。

【0057】

(実施例1)

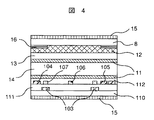

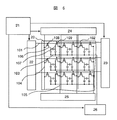

本実施例の構成を図3,図4,図5,図6,図7を用いて説明する。図3は画素部の電極構造を説明するための図である。図4は本実施例の液晶表示パネルにおける画素部断面図である。図5は図3における各電極及び配線に供給される信号波形を示す図である。図6はこれらの画素構成を有する液晶表示装置全体構成を説明する図である。尚、本明細書では、前述した図1や図4に示した一対の基板及び液晶層、一対の基板に配置した電極等を含めて液晶表示パネルということにし、この液晶表示パネルと光源等を組合せたシステム構成を液晶表示装置ということにする。

【0058】

本実施例における液晶表示パネルは、表示部が対角14.1 インチサイズであり、一対の基板は共に透明なガラス基板であり、厚みは0.7mm である。まず、ガラス基板110上に走査配線101,102及び共通電極103を形成する。次に第1の絶縁膜111が窒化シリコンSiNxを用いて形成され、その上に信号配線104,105,画素電極106,第3の電極107が形成されている。電極材料としてはクロムモリブデン(CrMo)を用いている。信号配線104,105や走査配線101,102の材料には電気抵抗の低いものであれば特に問題はなく、アルミニウムや銅,銀もしくはこららの合金等が考えられる。さらに、これら電極上に第2の絶縁膜112が窒化シリコン(SiNx)を用いて形成されている。なお、マトリクス状に形成された第1の走査配線101と第1の信号配線104の交点付近に、能動素子として機能するアモルファスシリコンを用いて作製される第1のTFT108が配置され、第2の走査配線102と第2の信号配線105の交点付近に、能動素子として機能するアモルファスシリコンを用いて作製される第2のTFT109が配置され、これらマトリクス状に形成される各配線に囲まれた領域に対応して画素を形成している。なお、本実施例では能動素子としてアモルファスシリコンを用いたが、ポリシリコンにより形成されたTFTでもよい。ポリシリコンTFTではアモルファスシリコンに比べ移動度が2桁ほど大きいために、以下2つの利点を有する。第1の利点は、アモルファスシリコンTFTに比べチャネル領域の幅を小さくできることからTFTサイズを小さくできることである。本実施例のように1画素内に2つの能動素子を形成する場合には、能動素子のサイズが開口率に大きく寄与するために、小サイズのポリシリコンTFTが有効である。第2の利点は、高速でスイッチングできることである。後述するように、本発明を実施するためには電極構造によっては1フレーム周期内で2回もしくは複数回走査する必要がある。このような場合には高速でスイッチングでき、短い時間で書きこみが可能なポリシリコンTFTが有効である。

【0059】

本電極構造では、図3に示したように一つの画素を駆動するために、2つのTFT,2本の走査配線,2本の信号配線を有している。すなわち、表示部を構成する各画素において、一つの画素内に2つの薄膜トランジスタ(TFT)が形成され、画素電極106が、信号を供給するための第1の信号配線104に、第1のTFT108を介して接続され、この第1のTFT108は第1の走査配線101からの走査信号により走査される。

【0060】

一方、強電界成分を発生させるための第3の電極107が、信号を供給するための第2の信号配線105に第2のTFT109を介して接続され、この第2のTFT109は第2の走査配線102からの走査信号により走査される。ここで、共通電極103は走査配線101,102と同層に形成され、この共通電極103の上に第3の電極107が第1の絶縁膜111を介して重畳している。

【0061】

一方、TFTを形成したガラス基板110に対向するガラス基板8はストライプ状の3色RGBカラーフィルタ12とブラックマトリクス16を兼ね備えた構成である。カラーフィルタ12とブラックマトリクス16上には平坦化するためのオーバーコート樹脂13を形成する。なお、オーバーコート樹脂としてはエポキシ樹脂などを用いる。

【0062】

このようにして作製される各ガラス基板表面に、液晶分子を配向させるためのポリイミド配向膜11を、膜厚100nmで形成する。一般にポリイミド膜は、その前駆体であるポリアミック酸を基板表面に印刷機などで塗布し、これらを高温で焼成することにより形成される。ここで形成されたポリイミド配向膜11の表面をラビング処理することにより配向処理を施す。ラビング方向は画素電極106の長手方向から15°傾いた方向である。

【0063】

本実施例においては、画素内に配置された電極(画素電極,共通電極,第3の電極)は櫛歯状に形成されているが、図7に示すように電極延長方向に対して角度θを有するくの字型に形成されていてもよい。くの字型に形成されることにより、電圧が印加された場合に液晶分子の回転方向が異なる領域を生じ、これにより色付きを抑制することができる。ただし、くの字型電極の場合には液晶分子の初期配向方向として、例えばポジ型液晶の場合には液晶分子の長軸が画素の長手方向と一致するように配向処理する必要がある。

【0064】

次に、これら一対の基板のうち、一方の基板の表示領域周縁部に熱硬化型のシール材を塗布し、もう一方の対向基板を重ね合わせる。なお、シール材は、後に液晶素子内に液晶を注入するための封入口が形成されるように塗布される。加熱しながら加圧し、両基板を接着固定する。基板間には直径4マイクロメートルの高分子ビーズが分散され、基板間の間隔を保持できるようになっている。その後、封入口から真空封入法により液晶を液晶表示素子内に注入し、封入口を紫外線硬化樹脂などで封止する。なお、ここでは液晶材料として分子構造内にシアノ基を有するシアノ系液晶(誘電率異方性が正)を使用する。

【0065】

組合せた基板の両面に偏光板15をノーマリークローズ特性(低電圧で黒表示、高電圧で白表示)となるようにクロスニコル配置で貼りつける。

【0066】

また図6に示すように、各配線は基板の端部まで延在配置され、第1の信号配線104,第2の信号配線105,第1の走査配線101,第2の走査配線102,共通電極103はそれぞれに対応して第1の信号電極駆動回路24,第2の信号電極駆動回路25,第1の走査電極駆動回路22,第2の走査電極駆動回路23,共通電極駆動回路26に接続される。また、各駆動回路は表示制御装置21により制御されている。なお、破線で囲まれた表示画素部20には一つの画素に対応する本電極構造に相当する等価回路を示している。

【0067】

その後、図8で示したシールドケース32,拡散板33,導光板34,反射板35,光源であるバックライト36,下側ケース37,インバータ回路38を組合せることにより液晶表示装置39を組み立てた。

【0068】

このようにして得られる液晶表示装置において、図5に示したような信号波形を各配線及び電極に印加することによって、本発明の効果を得ることができる。以下、各電極及び配線へ印加する信号波形について説明する。

【0069】

図5(a)は第1の走査配線101に供給される信号波形VG1、(b)は第1の信号配線104に供給される信号波形VD1、(c)は第2の走査配線102に供給される信号波形VG2、(d)は第2の信号配線105に供給される信号波形VD2、(e)は共通電極103に印加される信号波形VC 、(f)は画素内に配置した各電極(画素電極106,共通電極103,第3の電極107に印加される信号波形(画素電極VS ,共通電極VC ,第3の電極VA )を示す。

【0070】

まず第1の走査配線101からの走査信号によりt=t0において第1のTFTがオン状態となり、画素電極106には第1の信号配線104からの電圧が印加される。一方、第2の信号配線105には第1の信号配線104と位相の異なる信号を供給し、かつt=t1 において第2のTFTがオン状態になるよう駆動し、第2の信号配線105からの電圧が第3の電極107に印加される。また、共通電極103の電位VC は第1の信号波形VD1と同期をとり、かつその位相が逆になるよう駆動する。このような駆動においては、1フレーム周期内の初期状態(t0<t<t1)では、画素電極106と共通電極103との間に生じる均一な横電界に加えて、第3の電極107と共通電極103の間に生じる電位差VA−VC (図中矢印)により強電界を生じる。第3の電極107近傍の液晶分子はこの強電界により高速で駆動され、また、共通電極103と画素電極106の間の液晶分子は均一な横電界で駆動されるのに加え、強電界により駆動される液晶分子に引きずられるために全体として従来のIPSに比べ高速応答化が可能である。その後、フレーム周期内の後期(t1<t<t2)においては、第3の電極107の電位VA は共通電極103の電位VC とほぼ同程度になるため、初期のような強電界は発生せず、液晶分子は画素電極106と共通電極103との間に発生する均一な横電界によってのみ駆動される。

【0071】

次に、ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。応答速度は、ホトダイオードを組合せたオシロスコープを用いて評価した。

【0072】

まず、画面上には全面黒色パターンを表示し、その後、最大輝度に相当する白色パターンを表示する。このときの輝度変化をオシロスコープにて読み取り、変化前の輝度B0 から変化後の輝度Bfin への変化量を100%とし、そのうちの90%の変化が終了した時点をもって応答時間とする。本実施例の液晶表示装置において、同一の液晶材料を用いた場合に従来IPSに比べ応答時間が短縮されたことを確認した。

【0073】

次に残像評価について説明する。残像を定量的に評価するためホトダイオードを組合せたオシロスコープを用いて評価した。画面上に最大輝度でウィンドパターンを30分間表示し、その後、残像が最も目立つ中間調表示、ここでは輝度が最大輝度の10%となるように表示画面全面を切り替え、ウィンドの残像部分と周辺中間調部分での輝度Bにおける輝度変動分の大きさΔB/B10% を残像強度として評価した。液晶表示装置の表示特性として残像現象が問題のないレベルは残像強度が2%以下とされており、本実施例で得られた液晶表示装置においては2%以下を達成している。また、この実施例では、後述する実施例2の構造のように第1の電極106と第3の電極107を重畳させる構造ではないため、第1の電極を第3の電極と異なる層に配置するためのスルーホールの形成の必要がない。

【0074】

尚、本発明は本実施例で示した画素内2分割の構造に限られるわけでなく、例えば画素内4分割の構造、あるいはそれ以上の分割数を有する画素構造でもよい。特に精細度の低い液晶表示装置などでは、1画素当たりのピッチが広いために2分割構造では電極間隔が広くなり駆動電圧が上昇してしまう。従って、適当な電極間隔を得るために、精細度に応じて画素の分割数を変える必要がある。

【0075】

図9に画素内4分割の構造を示す。この構造については、第3の電極107は共通電極103に重畳している。特に本図では以下の問題を考慮して第3の電極107を画素中央部の共通電極103に重畳させている。

【0076】

画素を設計する上で、重要な課題の一つは、信号配線104,105から画素内電極(例えば画素電極となる第1の電極106,第3の電極107)へのノイズを低減することである。この信号配線104,105からのノイズにより特に画素電極の電位が変動し、輝度を変動させるからである。従って、図9では第3の電極107は、1画素内に信号配線104,105方向に伸びた3本の第2の電極103(共通電極)のうち中央に配置された第2の電極にのみ重畳させて配置して信号配線104,105からのノイズを受けないようにしている。つまり、3本の第2の電極103の両端の2本の第2の電極で画素内電極をノイズからシールドし、中央の第2の電極と第3の電極により強電界を発生させているということである。

【0077】

このような画素構造においても、1フレーム期間内の初期段階では画素内中央部の共通電極と第3の電極107によって強電界を発生させ、本発明の効果を十分に得ることが可能である。

【0078】

尚、画素を2分割以上の構造にする場合であっても、図9と同様に複数本配置した第2の電極の両端の電極には第3の電極を重畳させないように配置し、両端以外の第2の電極に第3の電極を重畳させる構造とすることで、画素分割数に関わらず同様に適用でき、同様の効果を奏する。

【0079】

(実施例2)

本発明における別の実施例の構成について、図10,図11を用いて説明する。図10は画素部の電極構造を説明するための図である。図11は図10のように配置された各電極及び配線に供給される信号波形について説明する図である。

【0080】

本実施例における液晶表示パネルの構成と、実施例1の液晶表示素子との構成の違いは、第3の電極107が画素電極106と重畳している点である。この構成に伴い、画素電極106は第1の信号配線104が配置されている層より上層に配置する必要があり、図9に示すように画素電極106はスルーホール113を介してさらに上層に配置され、第3の電極107と重畳している。また、第3の電極107が画素電極106に重畳していることから、各電極及び配線に供給される信号波形も実施例1と異なる。その他、電極構造以外の縦構造(配向膜形成,カラーフィルタ形成など)や、画素の等価回路的構成については実施例1と同様である。

【0081】

本実施例での各電極及び配線へ供給される信号波形について図11に示す。以下、各電極及び配線へ印加する信号波形について説明する。

【0082】

図11(a)は第1の走査配線101に供給される信号波形VG1、(b)は第1の信号配線104に供給される信号波形VD1、(c)は第2の走査配線105に供給される信号波形VG2、(d)は第2の信号配線105に供給される信号波形VD2、(e)は共通電極103に印加される信号波形VC 、(f)は画素内の電極(画素電極106,共通電極103,第3の電極107)に印加される信号波形(画素電極VS ,共通電極VC ,第3の電極VA )を示す。

【0083】

まず第1の走査配線101からの走査信号によりt=t0 において第1のTFTがオン状態となり、画素電極106には第1の信号配線104からの電圧が印加される。一方、第2の信号配線105には第1の信号配線104と位相の異なる信号を供給し、かつt=t1 において第2のTFTがオン状態になるよう駆動し、第2の信号配線105からの電圧が第3の電極107に印加される。また、共通電極103の電位VC は一定である。このような駆動においては、1フレーム周期内の初期段階(t0<t<t1)では、画素電極106と共通電極103との間に生じる均一な横電界に加えて、第3の電極107と画素電極106の間に生じる電位差VS−VA(図中矢印)により強電界を生じる。第3の電極107近傍の液晶分子はこの強電界により高速で駆動され、また、共通電極103と画素電極106の間の液晶分子は均一な横電界で駆動されるのに加え、強電界により駆動される液晶分子に引きずられるために全体として従来のIPSに比べ高速応答化が可能である。その後、フレーム周期内の途中段階(t1<t<t2)においては、第3の電極107の電位VA は画素電極106の電位VA とほぼ同程度になるため、初期のような強電界は発生せず、液晶分子は画素電極106と共通電極103との間に発生する均一な横電界によってのみ駆動される。

【0084】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、同一の液晶材料を用いた場合に従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0085】

本実施例においても、実施例1と同様に画素内2分割の構造に限らず、4分割あるいはそれ以上の分割数を有する画素構造でもよい。

【0086】

図12に画素内4分割の構造を示す。ここで、第3の電極107は画素電極106に重畳した構造である。このような画素構造においても、1フレーム期間内の初期段階では画素電極106と第3の電極107によって強電界を発生させ、本発明の効果を十分に得ることが可能である。この実施例2の4分割構造の場合には、実施例1の4分割構造の場合と比較して、2組の第1の電極及び第3の電極が重畳しているので、より低電圧駆動で有効に強電界を発生させることができる。

【0087】

また、本画素構造においても信号配線104,105に沿って共通電極103となる幅の広い第2の電極を配置することにより信号配線から画素電極へのノイズを遮蔽することができ、実施例1で述べたような課題を解消できる。

【0088】

(実施例3)

本発明における別の実施例の構成について、図13,図14,図15を用いて説明する。図13は画素部の電極構造を説明するための図である。図14は各電極及び配線に供給される信号波形示す図である。図15はこれらの画素構成を有する液晶表示パネルの全体構成を説明する図である。

【0089】

本実施例における液晶表示パネルの構成と、実施例1の液晶表示パネルの構成との差異は、一つの画素内に配置された2つのTFTを1つの走査配線により駆動する点である。実施例1に比べて走査配線を一つに減らすことにより第2の走査配線駆動ドライバが不要となるという効果がある。

【0090】

本電極構造では、図13に示したように一つの画素を駆動するために、2つのTFT,1本の走査配線,2本の信号配線を有する。すなわち、表示部を構成する画素において、一つの画素の内に2つの薄膜トランジスタ(TFT)が形成され、画素電極106が、信号を供給するための第1の信号配線104に、第1のTFT108を介して接続され、一方、強電界成分を発生させるために必要な第3の電極107が、信号を供給するための第2の信号配線105に第2のTFT109を介して接続され、かつ第1のTFT108及び第2のTFT109が共に一つの第1の走査配線101からの走査信号により走査される。ここで、共通電極103は走査配線101と同層に形成され、この共通電極103の上に第3の電極107が絶縁膜111を介して重畳している。

【0091】

また、図15に示すように、各配線は基板の端部まで延在配置され、第1の信号配線104,第2の信号配線105,第1の走査配線101,共通電極103はそれぞれに対応して第1の信号電極駆動回路24,第2の信号電極駆動回路25,第1の走査電極駆動回路22,共通電極駆動回路26に接続される。また、各駆動回路は表示制御装置21により制御されている。なお、破線で囲まれた表示画素部20には一つの画素に対応する本電極構造に相当する等価回路を示している。

【0092】

このようにして得られる液晶表示装置において、図14に示したような信号波形を各配線及び電極に印加することによって、本発明の効果を得ることができる。

【0093】

図14(a)は走査配線101に供給される信号波形VG1、(b)は第1の信号配線104に供給される信号波形VD1、(c)は第2の信号配線105に供給される信号波形VD2、(d)は共通電極103に印加される信号波形VC 、(e)は画素内の電極(画素電極106,共通電極103,第3の電極107)に印加される信号波形(画素電極VS ,共通電極VC ,第3の電極VA )を示す。ここで特徴的な点は、走査配線101が1フレーム周期内に2回走査される点である。

【0094】

第1の信号配線104と第2の信号配線105には位相の異なる信号が供給され、走査配線101は1フレーム周期内に2回走査される。t=t0 及びt=t1 において、走査配線101のからの走査信号により第1のTFT108と第2のTFT109が同時にオン状態となり、画素電極106には第1の信号配線104からの電圧が、一方、第3の電極107には第2の信号配線105からの電圧が印加される。また、共通電極103の電位VC は第1の信号波形VD1と同期をとり、かつその位相が逆になるよう駆動する。このような駆動においては、1フレーム周期内の初期状態(t0<t<t1)では、画素電極106と共通電極103との間に生じる均一な横電界に加えて、第3の電極107と共通電極103の間に生じる電位差VA−VC(図中矢印)により強電界を生じる。第3の電極107近傍の液晶分子はこの強電界により高速で駆動され、また、共通電極103と画素電極106の間の液晶分子は均一な横電界で駆動されるのに加え、強電界により駆動される液晶分子に引きずられるために全体として従来のIPSに比べ高速応答化が可能である。その後、フレーム周期内の後期(t1<t<t2)においては、第3の電極107の電位VA は共通電極103の電位VC とほぼ同程度になるため、初期のような強電界は発生せず、液晶分子は画素電極106と共通電極103との間に発生する均一な横電界によってのみ駆動される。

【0095】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、同一の液晶材料を用いた場合に従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0096】

尚、画素内4分割以上の構造についても、実施例1と同様に本実施例においても適用できる

(実施例4)

本発明における別の実施例の構成について、図16,図17を用いて説明する。図16は画素部の電極構造を説明するための図である。図17は各電極及び配線に供給される信号波形を説明する図である。

【0097】

本実施例における液晶表示パネルの構成と、実施例3の液晶表示パネルの構成との差異は、本実施例では第3の電極107が画素電極106に重畳している点である。この構成の違いに伴い、画素電極106は第1の信号配線104が配置されている層より上層に配置される必要があり、図16に示すように画素電極106はスルーホール113を介してさらに上層に配置され、第3の電極107と重畳している。また、第3の電極107が画素電極106に重畳していることから、各電極及び配線に供給される信号波形も実施例3と異なる。また、画素の等価回路的構成については実施例3と同様である。

【0098】

本実施例での各電極及び配線へ供給される信号波形について図17に示した。以下、各電極及び配線へ印加する信号波形について説明する。

【0099】

図17(a)は走査配線101に供給される信号波形VG1、(b)は第1の信号配線104に供給される信号波形VD1、(c)は第2の信号配線105に供給される信号波形VD2、(d)は共通電極103に印加される信号波形VC 、(e)は画素内の電極(画素電極106,共通電極103,第3の電極107)に印加される信号波形(画素電極VS ,共通電極VC ,第3の電極VA )を示す。ここで特徴的な点は、走査配線101が1フレーム周期内に2回走査される点である。

【0100】

第1の信号配線104と第2の信号配線105には位相の異なる信号が供給され、走査配線101は1フレーム周期内に2回走査される。t=t0 及びt=t1 において、走査配線101からの走査信号により第1のTFT108と第2のTFT109が同時にオン状態となり、画素電極106には第1の信号配線104からの電圧が、一方、第3の電極107には第2の信号配線105からの電圧が印加される。また、共通電極103の電位VC は一定である。このような駆動においては、1フレーム周期内の初期状態(t0<t<t1)では、画素電極106と共通電極103との間に生じる均一な横電界に加えて、第3の電極107と画素電極106の間に生じる電位差VS−VA(図中矢印)により強電界を生じる。第3の電極107近傍の液晶分子はこの強電界により高速で駆動され、また、共通電極103と画素電極106の間の液晶分子は均一な横電界で駆動されるのに加え、強電界により駆動される液晶分子に引きずられるために全体として従来のIPSに比べ高速応答化が可能である。その後、フレーム周期内の後期(t1<t<t2)においては、第3の電極107の電位VA は画素電極106の電位VS とほぼ同程度になるため、初期のような強電界は発生せず、液晶分子は画素電極106と共通電極103との間に発生する均一な横電界によってのみ駆動される。

【0101】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、同一の液晶材料を用いた場合に従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0102】

尚、画素内4分割以上の構造についても、実施例1,3と同様に本実施例においても適用できる

(実施例5)

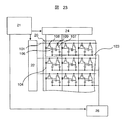

本発明における別の実施例の構成について、図18,図19,図20を用いて説明する。図18は画素部の電極構造を説明するための図である。図19は各電極及び配線に供給される信号波形を示す図である。図20はこれらの画素構成を有する液晶表示パネルの全体構成を説明する図である。

【0103】

本実施例における液晶表示パネルの構成と、実施例2の液晶表示パネルの構成との差異は、本実施例の構成は一つの画素内に配置された画素電極106と第3の電極107に印加される電圧が、同一の信号配線104から供給される点である。信号配線を一つ減らすことにより、実施例2と比較して第2の信号配線駆動ドライバが不要となる。さらに、この構成は実施例2と比較して開口率の点でも有利である。

【0104】

本電極構造では、図18に示したように一つの画素を駆動するために、2つのTFT,2本の走査配線,1本の信号配線を有する。すなわち、表示部を構成する各画素において、一つの画素内に2つの薄膜トランジスタ(TFT)が形成され、画素電極106と第3の電極107がそれぞれ第1のTFT108と第2のTFT109を介して、共に一つの第1の信号配線104に接続され、かつ第1のTFT108及び第2のTFT109はそれぞれ第1の走査配線101及び第2の走査配線102からの走査信号により走査される。ここで、画素電極106はスルーホールを介して最上層に形成され、第3の電極107と絶縁膜112を介して重畳している。

【0105】

また、図20に示すように、各配線は基板端部まで延在配置され、第1の信号配線104,第1の走査配線101,第2の走査配線102,共通電極103はそれぞれに対応して、第1の信号電極駆動回路24,第1の走査電極駆動回路22,第2の走査電極駆動回路23,共通電極駆動回路26に接続される。また、各駆動回路は表示制御装置21により制御されている。なお、破線で囲まれた表示画素部20には一つの画素に対応する本電極構造に相当する等価回路を示している。

【0106】

ここで得られる液晶表示装置において、図19に示したような信号波形を各配線及び電極に印加することによって、本発明の効果を得ることができる。

【0107】

図19(a)は第1の走査配線101に供給される信号波形VG1、(b)は第2の走査配線102に供給される信号波形VG2、(c)は信号配線104に供給される信号波形VD1、(d)は共通電極103に印加される信号波形VC 、(e)は画素内の電極(画素電極106,共通電極103,第3の電極107)に印加される信号波形(画素電極VS ,共通電極VC ,第3の電極VA )を示す。

【0108】

まず第1の走査配線101からの走査信号によりt=t0 において第1のTFTがオン状態となり、画素電極106には信号配線104からの電圧が印加される。一方、第2の走査配線102からの走査信号によりt=t1 において第2のTFTがオン状態となり、第3の電極107には信号配線からの電圧が印加される。また、共通電極103の電位は一定である。このような駆動においては、1フレーム周期内の初期状態(t0<t<t1)では、画素電極106と共通電極103との間に生じる均一な横電界に加えて、第3の電極107と画素電極106の間に生じる電位差VS−VA(図中矢印)により強電界を生じる。第3の電極107近傍の液晶分子はこの強電界により高速で駆動され、また、共通電極103と画素電極106の間の液晶分子は均一な横電界で駆動されるのに加え、強電界により駆動される液晶分子に引きずられるために全体として従来のIPSに比べ高速応答化が可能である。その後、フレーム周期内の後期(t1<t<t2)においては、第3の電極107の電位VA は画素電極106の電位VS とほぼ同程度になるため、初期のような強電界は発生せず、液晶分子は画素電極106と共通電極103との間に発生する均一な横電界によってのみ駆動される。

【0109】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、同一の液晶材料を用いた場合に従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0110】

尚、画素内4分割以上の構造についても、実施例2と同様に本実施例においても適用できる

(実施例6)

本発明における別の実施例の構成について、図21,図22,図23を用いて説明する。図21は画素部の電極構造を説明するための図である。図22は各電極及び配線に供給される信号波形を示す図である。図23はこれらの画素構成を有する液晶表示パネルの全体構成を説明する図である。

【0111】

本実施例における液晶表示パネルの構成と、実施例5の液晶表示パネルの構成との差異は、本実施例の構成では一つの画素内に配置された2つのTFTを同一の走査配線からの走査信号により駆動する点である。走査配線を一つ減らすことにより、実施例5と比較して第2の走査配線駆動ドライバが不要となるという効果がある。また、実施例5と比較して開口率の点でも有利である。

【0112】

本電極構造では、図21に示したように一つの画素を駆動するために、2つのTFT,1本の走査配線,1本の信号配線を有する。すなわち、表示部を構成する各画素において、一つの画素内に2つの薄膜トランジスタ(TFT)が形成され、画素電極106と第3の電極107がそれぞれ第1のTFT108と第2のTFT109を介して、共に一つの第1の信号配線104に接続され、かつ第1のTFT108及び第2のTFT109は共に一つの第1の走査配線101からの走査信号により走査される。ここで、画素電極106はスルーホールを介して最上層に形成され、第3の電極107と絶縁膜112を介して重畳している。

【0113】

また、図23に示すように、各配線は基板端部まで延在配置され、第1の信号配線104,第1の走査配線101,共通電極103はそれぞれに対応して、第1の信号電極駆動回路24,第1の走査電極駆動回路22,共通電極駆動回路26に接続される。また、各駆動回路は表示制御装置21により制御されている。なお、破線で囲まれた表示画素部20には一つの画素に対応する本電極構造に相当する等価回路を示している。

【0114】

ここで得られる液晶表示装置において、図22に示したような信号波形を各配線及び電極に印加することによって、本発明の効果を得ることができる。

【0115】

図22(a)は第1の走査配線101に供給される信号波形VG1、(b)は第1の信号配線104に供給される信号波形VD1、(c)は共通電極103に印加される信号波形VC 、(d)は画素内の電極(画素電極106,共通電極103,第3の電極107)に印加される信号波形(画素電極VS ,共通電極VC ,第3の電極VA )を示す。本実施例で特に特徴的な点は、1フレーム周期内で選択期間が2回となるように走査信号を供給し、かつ、これら走査信号で駆動される2つのTFTの閾値電圧特性が異なる点である。

【0116】

信号配線に供給される信号波形に対して、図22に示すように走査信号には1フレーム周期内に2回走査し、かつ2回目の走査電圧(VGH2)が1回目の走査電圧(VGH1)より大きな値とする。このとき、画素内に配置された2つのTFTは閾値電圧が異なるものであり、画素電極に接続された第1のTFTはVGH1 以上でオン状態になる特性を有し、第3の電極に接続された第2のTFTはVGH2 以上でのみオン状態となる特性を有する。

【0117】

TFTの閾値電圧は特に、TFTを構成するゲート絶縁膜などにより異なる。図24にアモルファスシリコンにより作成された逆スタガ型のTFTの断面図を示した。TFTのスイッチング特性(閾値電圧や立ち上がり時間)はTFTを構成する絶縁膜の材料や膜厚などで決まり、特に閾値電圧は走査配線41の直上に形成されるゲート絶縁膜42の誘電率や膜厚もしくは層構成に大きく影響される。例えば、第1のTFT108を構成するゲート絶縁膜としてSiNを用い、第2のTFT109を構成するゲート絶縁膜にはSiNに加えSiO2 を積層した構成とする。この場合、第2のTFT109は第1のTFT108に比べ閾値電圧は上昇し、本実施例に適した、閾値特性の異なるTFTを作製することができる。

【0118】

このような構成では、t=t0 において走査電圧VGH1 を印加することにより、第1のTFT108のみがオン状態になり、信号配線104からの信号電圧が画素電極106に印加される。次にt=t1 において走査電圧VGH2 を印加することにより、第1のTFT108と第2のTFT109が同時にオン状態となり、信号配線104からの信号電圧が画素電極106と第3の電極107に印加される。また、共通電極103の電位は一定である。

【0119】

このような駆動においては、1フレーム周期内の初期段階(t0<t<t1)では、画素電極106と共通電極103との間に生じる均一な横電界に加えて、第3の電極107と画素電極106の間に生じる電位差VS−VA(図中矢印)により強電界を生じる。第3の電極107近傍の液晶分子はこの強電界により高速で駆動され、また、共通電極103と画素電極106の間の液晶分子は均一な横電界で駆動されるのに加え、強電界により駆動される液晶分子に引きずられるために全体として従来のIPSに比べ高速応答化が可能である。その後、フレーム周期内の途中段階(t1<t<t2)においては、第3の電極107の電位は画素電極106の電位とほぼ同程度になるため、初期のような強電界は発生せず、液晶分子は画素電極と共通電極との間に発生する均一な横電界によってのみ駆動される。

【0120】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、同一の液晶材料を用いた場合に従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0121】

尚、画素内4分割以上の構造についても、実施例2,5と同様に本実施例においても適用できる。

【0122】

尚、閾値電圧の異なるTFTを作製するためには、例えばゲート絶縁膜の膜厚を変えたり、又はゲート絶縁膜を多層にし各層の材料の組合せをTFTにより変える(例えば誘電率などを変える)ことが考えられる。

【0123】

(実施例7)

本発明における別の実施例の構成について、図25,図26を用いて説明する。図25は画素部の電極構造を説明するための図である。図26は各電極及び配線に供給される信号波形を説明する図である。

【0124】

本実施例における液晶表示パネルの構成と、実施例4の液晶表示パネルの構成との差異は、本実施例の構成は、画素内の共通電極を、画素の長手方向に隣接する画素を駆動するための走査配線を用いて代用している点である。

【0125】

液晶表示装置においては、今後低消費電力化の要請から高開口率が要求されている。開口率を向上させることによりバックライトの利用効率を向上させ、低消費電力化を図ることが可能である。通常のIPS液晶表示装置では液晶分子を駆動させるための電極として、画素内には画素電極と共通電極の2種類の電極しか配置されない。それに対して、本発明ではこれら電極に加えて第3の電極を配置することから、開口率の低下が懸念される。これを改善するために電極材料としてITOなどの透明導電膜を用いると同時に電極構造からの対策が必要となる。そこで、本実施例では、共通電極を画素の長手方向に隣接する画素を駆動するための走査配線に接続して構成することにより、実施例4で画素内に配置されている共通電極を別途形成する必要が無く開口率の向上が見込める。

【0126】

図26に本実施例における各電極及び配線に供給される信号波形を示した。共通電極として、隣接する画素の走査配線の信号を利用すること以外は実施例4と同様である。

【0127】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0128】

尚、画素内4分割以上の構造についても、実施例1,3,4と同様に本実施例においても適用できる

(実施例8)

本発明における別の実施例の構成について図27,図28,図29を用いて説明する。図27は画素部の電極構造を説明するための図である。図28は各電極及び配線に供給される信号波形を示す図である。図29はこれらの画素構成を有する液晶表示パネルの全体構成を説明する図である。

【0129】

本実施例では画素電極は、画素内に一つだけ配置されたTFTを介して信号配線に接続され、このTFTは走査配線101からの信号により制御される。また共通電極103及び第3の電極107にはそれぞれ専用の駆動用回路が直接接続され、第3の電極107はスルーホール113を介して共通電極103と重畳するように配置されている。

【0130】

図28に本実施例における各電極及び配線に供給される信号波形を示した。このような駆動においては、1フレーム周期内の初期状態(t0<t<t1)では、画素電極106と共通電極103との間に生じる均一な横電界に加えて、第3の電極107と共通電極103の間に生じる電位差VA−VC(図中矢印)による強電界を生じる。第3の電極107近傍の液晶分子はこの強電界により高速で駆動され、また、共通電極103と画素電極106の間の液晶分子は均一な横電界で駆動されるのに加え、強電界により駆動される液晶分子に引きずられるために全体として従来のIPSに比べ高速応答化が可能である。その後、フレーム周期内の後期(t1<t<t2)においては、第3の電極107の電位VA は共通電極103の電位VC とほぼ同程度になるため、初期のような強電界は発生せず、液晶分子は画素電極106と共通電極103との間に発生する均一な横電界によってのみ駆動される。このように、第2の電極は共通配線に接続され、第3の電極は所定の電位を印加することができる配線に接続されている。また、図29のように、信号配線104に交差するように配置され、能動素子108に接続された走査線を有し、信号線、及び走査線に囲まれた領域に対応して画素20を構成し、この画素を複数配置して表示領域を形成している。さらに、表示領域の外側に、信号線に接続された信号駆動回路24と、走査線に接続された走査駆動回路22と、共通配線に接続された共通電極駆動回路26と、所定の電位を印加することができる配線に接続された第3電極駆動回路27を有して液晶表示パネルが構成されている。さらには、信号駆動回路24,走査駆動回路22,共通電極駆動回路26、及び第3電極駆動回路27に接続された表示制御回路21を有するというものである。

【0131】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、同一の液晶材料を用いた場合に従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0132】

尚、画素内4分割以上の構造についても、他の実施例と同様に本実施例においても適用できる

(実施例9)

本発明における別の実施例の構成について図30を用いて説明する。図30は画素部の電極構造を説明するための図である。

【0133】

本実施例における液晶表示パネルの構成と、実施例6の液晶表示パネルの構成との差異は、画素内の共通電極を、他の電極や配線よりも液晶層に近い側に配置し、絶縁膜を介して信号配線上に重畳させている点である。このとき、共通電極と信号配線が重畳していることから、これら電極間には容量が発生する。この容量は大きいほど駆動の負担になるため、これら容量をできるだけ小さくする目的でこれら電極間には例えば有機膜などの容量の小さい絶縁膜(低容量有機絶縁膜115)が形成される。

【0134】

実施例7で記したように、今後、液晶表示装置には開口率の向上が要求され、本実施例は共通電極を重畳することにより開口率を向上している。第3の電極形成による開口率の低下を抑制するための一つの手段である。また、共通電極をこのように重畳させることにより、重畳領域の液晶には電圧が印加されず、液晶分子の回転による光透過はない。従って、本電極構造では対向基板上に形成される遮光用ブラックマトリクスにおいて、信号配線延在方向に形成されるブラックマトリクスが不要なり、このような対向基板との組合せによりさらに開口率を向上できる。

【0135】

ここで得られる液晶表示装置において、実施例6と同様の信号波形を各配線及び電極に印加することによって、本発明の効果を得ることができる。

【0136】

ここで得られる液晶表示装置を用いて、応答速度及び残像に関して評価した。本実施例の液晶表示装置において、従来IPSに比べ応答時間が短縮されたことを確認した。また、本実施例で得られた液晶表示装置においては残像強度2%以下を達成している。

【0137】

尚、画素内4分割以上の構造についても、実施例2,5,6と同様に本実施例においても適用できる

(実施例10)

本発明における別の実施例の構成について図31を用いて説明する。図31は画素部の電極構造を説明するための図である。本実施例の構成は、実施例9の構成でさらに共通電極を走査配線上にも重畳させたというものである。このような構成では、共通電極を重畳させることにより開口率の向上が図れると同時に、実施例9で記したように重畳部では液晶に電圧が印加されず、液晶分子の駆動による光透過がないことから、対向基板に形成されるべき走査配線延在方向及び信号配線延在方向の遮光用ブラックマトリクスが不要になる。従って、このような信号配線方向及び走査配線方向のブラックマトリクスが形成されていない対向基板と組合せることにより更なる開口率の向上が期待できる。

【0138】

(実施例11)

本発明における別の実施例の構成について説明する。本実施例と、実施例1との差異は、使用する液晶材料である。本実施例では液晶材料として分子構造内にフッ素原子を有するフッ素系液晶を用いる。フッ素系液晶ではシアノ系液晶に比べて誘電率異方性が小さく粘度も低い。

【0139】

本発明では第1の電極と第3の電極の端部で一時的に強電界を発生させて液晶を駆動させることから、従来のIPSに比べ低誘電率の液晶材料を用いることが容易である。一般に誘電率異方性が小さな液晶材料はその粘度も低いために、同程度の電界強度が印加された場合、高速応答が期待できる。上述したように、フッ素系液晶ではシアノ系液晶に比べて誘電率異方性が小さく、粘度も低いため、シアノ系液晶材料を用いた場合に比べ高速応答化が期待できる。さらに、このようなフッ素系液晶では誘電率が低いことから、イオン性不純物などの取り込みも少なく、これら不純物による保持率低下などの表示性能の劣化を引き起こすこともない。

【0140】

よって、本発明により誘電率の低い液晶を用いることが可能となる。誘電率の低い液晶は一般に粘度も低く、高速応答に適している。また誘電率が低い材料では不純物イオンなどを抱き込みにくく、イオンなどに起因する表示むらを生じないと考えられる。

【0141】

(実施例12)

本発明における別の実施例の構成について説明する。本実施例と、実施例5とは、配向処理法が異なる。実施例5ではラビングにより配向処理を施したが、本実施例では光配向による配向処理を施した。

【0142】

特に、第3の電極と共通電極が重畳しているために、電極端部で大きな段差を生じる。このような電極段差は配向膜を布でこするラビング工程時において、電極端部でラビング布の毛が所望の方向にこすれず液晶分子の初期配向方向のずれを生じる。これは光漏れなどの原因となり、コントラスト低下などの表示不良を生じる。しかし、光を照射することにより液晶分子の初期配向方向を制御する光配向膜を用いる手段では、このような段差部での配向不良を生じないことが期待でき、コントラスト低下などの表示品質の劣化を抑制できる。

【0143】

これらの各実施例の本発明によれば、高速応答化を実現でき、かつ残像現象を抑制した高品質な液晶表示パネル、及び液晶表示装置を得ることができる。

【0144】

【発明の効果】

本発明によれば、高速応答に適した液晶表示パネル、及び液晶表示装置を提供できる。

【図面の簡単な説明】

【図1】本発明の概念を説明するための電極構造及び各電極の信号波形を示した図である。

【図2】本発明を実施するための電極構造の概略図である。

【図3】実施例1での液晶表示パネルにおける画素部の電極構造である。

【図4】実施例1での液晶表示パネルにおける画素部断面図である。

【図5】実施例1での液晶表示パネルにおける各電極及び配線に供給される信号波形を示す図である。

【図6】実施例1及び実施例2での液晶表示パネルを駆動する全体構成図である。

【図7】電極形状を説明するための図である。

【図8】液晶表示装置の分解斜視図である。

【図9】実施例1での他の画素分割構造を示す図である。

【図10】実施例2での液晶表示パネルにおける画素部の電極構造である。

【図11】実施例2での液晶表示パネルにおける各電極及び配線に供給される信号波形を示す図である。

【図12】実施例2での他の画素分割構造を示す図である。

【図13】実施例3での液晶表示パネルにおける画素部の電極構造である。

【図14】実施例3での液晶表示パネルにおける各電極及び配線に供給される信号波形を示す図である。

【図15】実施例3及び実施例4での液晶表示パネルを駆動する全体構成図である。

【図16】実施例4での液晶表示パネルにおける画素部の電極構造である。

【図17】実施例4での液晶表示パネルにおける各電極に供給される信号波形を示す図である。

【図18】実施例5での液晶表示パネルにおける画素部の電極構造である。

【図19】実施例5での液晶表示パネルにおける各電極に供給される信号波形を示す図である。

【図20】実施例5での液晶表示パネルを駆動する全体構成図である。

【図21】実施例6での液晶表示パネルにおける画素部の電極構造である。

【図22】実施例6での液晶表示パネルにおける各電極に供給される信号波形を示す図である。

【図23】実施例6での液晶表示パネルを駆動する全体構成図である。

【図24】アモルファスシリコンにより作製されたTFTの断面図である。

【図25】実施例7での液晶表示パネルにおける画素部の電極構造である。

【図26】実施例7での液晶表示パネルにおける各電極に供給される信号波形を示す図である。

【図27】実施例8での液晶表示パネルにおける画素部の電極構造である。

【図28】実施例8での液晶表示パネルにおける各電極に供給される信号波形を示す図である。

【図29】実施例8での液晶表示パネルを駆動する全体構成図である。

【図30】実施例9での液晶表示パネルにおける画素部の電極構造である。

【図31】実施例10での液晶表示パネルにおける画素部の電極構造である。

【図32】従来IPS方式の画素部電極構造を説明するための図である。

【図33】従来IPS方式の画素部断面図である。

【図34】従来IPS方式の液晶表示装置を駆動する全体システムを示す図である。

【符号の説明】

1…第1の電極、2…第2の電極、3,107…第3の電極、4…第1の電極と第3の電極間に生じる電界、5…第1の電極と第2の電極間に生じる電界(横電界)、6…第2の電極と第3の電極間に生じる電界、7,110…ガラス基板1、8…ガラス基板2、9,111…第1の絶縁膜、10,112…第2の絶縁膜、11…配向膜、12…カラーフィルタ、13…オーバーコート膜(カラーフィルタ保護膜)、14…液晶層、15…偏光板、20…表示画素部、21…表示制御装置、22…第1の走査電極駆動回路、23…第2の走査電極駆動回路、

24…第1の信号電極駆動回路、25…第2の信号電極駆動回路、26…共通電極駆動回路、27…第3の電極駆動回路、31…液晶表示素子(液晶表示パネル)、32…シールドケース、33…拡散板、34…導光板、35…反射板、36…バックライト、37…下側ケース、38…インバータ回路基板、39…液晶表示装置、40…ガラス基板、41…走査配線(ゲート配線)、42…ゲート絶縁膜、43…アモルファスシリコン、44…信号配線(ドレイン配線)、45…n+ アモルファスシリコン、46…画素電極(ソース電極)、47…絶縁膜、101…第1の走査配線、102…第2の走査配線、103…共通電極、104…第1の信号配線、105…第2の信号配線、106…画素電極(ソース電極)、108…第1のTFT、109…第2のTFT、113…スルーホール、114…前段の走査配線、115…低容量有機絶縁膜。

Claims (54)

- 一対の基板と、

該一対の基板間に配置した液晶層と、

前記一対の基板の一方の基板上に形成された、複数の信号配線と、前記複数の信号配線と交差して配置された複数の走査配線と、前記複数の信号配線と前記複数の走査配線との交点付近に配置された複数の能動素子と、

前記複数の信号配線と前記複数の走査配線のそれぞれによって囲まれた領域からなる画素と、を有する液晶表示パネルにおいて、

前記画素内に配置され、ある方向に伸びた第1の電極,第2の電極、及び第3の電極を有し、

前記第1の電極と前記第2の電極と前記第3の電極の各間で生じる少なくとも2つの電位差が、前記複数の走査配線それぞれにおける1フレーム期間内の初期段階と途中段階で異なり、前記1フレーム期間内の初期段階では強電界を形成し、途中段階では前記初期段階の電界よりも弱い電界を形成するように、前記第1の電極,第2の電極、または前記第3の電極に与える少なくとも一つの電位を変え、前記第1の電極と前記第2の電極と前記第3の電極の各間で生じる電界によって前記液晶層内の液晶分子の配向方向を制御することにより、表示を制御するように構成した液晶表示パネル。 - 前記第3の電極は、前記第1の電極と前記第2の電極間の前記第1の電極により近い位置に配置された請求項1の液晶表示パネル。

- 前記第1の電極または前記第2の電極の一方の電極が第1の能動素子を介して第1の信号配線に接続され、

前記第1の電極または前記第2の電極のうち、前記第1の能動素子に接続されていない他方の電極が共通配線に接続され、

前記第3の電極は、第2の能動素子を介して第2の信号配線に接続されている請求項1または2に記載の液晶表示パネル。 - 前記第1の信号配線に交差するように配置され、前記第1の能動素子に接続された第1の走査配線を有し、

前記第2の信号配線に交差するように配置され、前記第2の能動素子に接続された第2の走査配線を有し、

前記第1の信号配線,前記第1の走査配線,前記第2の信号配線、及び前記第2の走査配線に囲まれた領域に対応して画素を構成し、該画素を複数配置して表示領域を形成した請求項3の液晶表示パネル。 - 前記表示領域の外側に、

前記第1の信号配線に接続された第1の信号駆動回路と、

前記第2の信号配線に接続された第2の信号駆動回路と、

前記第1の走査配線に接続された第1の走査駆動回路と、

前記第2の走査配線に接続された第2の走査駆動回路と、

前記共通配線に接続された共通配線駆動回路を有する請求項4の液晶表示パネル。 - 前記表示領域の外側に、

前記第1の信号駆動回路,前記第2の信号駆動回路,前記第1の走査駆動回路,前記第2の走査駆動回路、及び前記共通配線駆動回路に接続された表示制御回路を有する請求項5の液晶表示パネル。 - 前記第1の信号配線、及び前記第2の信号配線に交差するように配置され、前記第1の能動素子及び前記第2の能動素子に接続された走査配線を有し、

前記第1の信号配線,前記走査配線、及び前記第2の信号配線に囲まれた領域に対応して画素を構成し、該画素を複数配置して表示領域を形成した請求項3の液晶表示パネル。 - 前記画素に対応するそれぞれの走査配線は、1フレーム期間内に2回走査されることを特徴とする請求項7の液晶表示パネル。

- 前記表示領域の外側に、

前記第1の信号配線に接続された第1の信号駆動回路と、

前記第2の信号配線に接続された第2の信号駆動回路と、

前記走査配線に接続された走査駆動回路と、

前記共通配線に接続された共通配線駆動回路を有する請求項8の液晶表示パネル。 - 前記表示領域の外側に、

前記第1の信号駆動回路,前記第2の信号駆動回路,前記走査駆動回路、及び前記共通配線駆動回路に接続された表示制御回路を有する請求項9の液晶表示パネル。 - 前記第1の電極または前記第2の電極の一方の電極が第1の能動素子を介して、及び前記第3の電極が第2の能動素子を介して信号配線に接続され、

前記第1の電極または前記第2の電極のうち、前記第1の能動素子に接続されていない他方の電極が共通配線に接続されている請求項1または2に記載の液晶表示パネル。 - 前記信号配線に交差するように配置され、前記第1の能動素子及び前記第2の能動素子に接続された走査配線を有し、

前記信号配線,前記走査配線に囲まれた領域に対応して画素を構成し、該画素を複数配置して表示領域を形成した請求項11の液晶表示パネル。 - 前記画素に対応するそれぞれの走査配線は、1フレーム期間内に2回走査されることを特徴とする請求項12の液晶表示パネル。

- 前記2回の走査は、異なる走査電圧値で行うことを特徴とする請求項13の液晶表示パネル。

- 前記第1の能動素子および前記第2の能動素子は、異なる閾値特性を有することを特徴とする請求項13の液晶表示パネル。

- 前記表示領域の外側に、

前記信号配線に接続された信号駆動回路と、

前記走査配線に接続された走査駆動回路と、

前記共通配線に接続された共通配線駆動回路を有する請求項12〜15のいずれか一項に液晶表示パネル。 - 前記表示領域の外側に、

前記信号駆動回路、及び前記走査駆動回路に接続された表示制御回路を有する請求項16の液晶表示パネル。 - 前記信号配線に交差するように配置され、前記第1の能動素子に接続された第1の走査配線と、

前記信号配線に交差するように配置され、前記第2の能動素子に接続された第2の走査配線を有し、

前記信号配線,前記第1の走査配線、及び前記第2の走査配線に囲まれた領域に対応して画素を構成し、該画素を複数配置して表示領域を形成した請求項11の液晶表示パネル。 - 前記表示領域の外側に、

前記信号配線に接続された信号駆動回路と、

前記第1の走査配線に接続された第1の走査駆動回路と、

前記第2の走査配線に接続された第2の走査駆動回路と、

前記共通配線に接続された共通配線駆動回路を有する請求項18の液晶表示パネル。 - 前記表示領域の外側に、

前記信号駆動回路,前記第1の走査駆動回路,前記第2の走査駆動回路、及び前記共通配線駆動回路に接続された表示制御回路を有する請求項19の液晶表示パネル。 - 前記第1の電極または前記第2の電極の一方の電極が第1の能動素子を介して第1の信号配線に接続され、

前記第3の電極は、第2の能動素子を介して第2の信号配線に接続され、

前記第1の信号配線及び第2の信号配線に交差して、前記第1の能動素子及び前記第2の能動素子に接続された走査配線と、

前記第1の信号配線,前記走査配線、及び前記第2の信号配線に囲まれた領域に対応して画素を構成し、該画素を複数配置して表示領域を形成し

前記第1の電極または前記第2の電極のうち、前記第1の能動素子に接続されていない他方の電極が、前記第1の能動素子及び前記第2の能動素子が接続された走査配線に隣接する走査配線に接続された請求項1または2に記載の液晶表示パネル。 - 前記画素に対応するそれぞれの走査配線は、1フレーム期間内に2回走査されることを特徴とする請求項21の液晶表示パネル。

- 前記表示領域の外側に、

前記第1の信号配線に接続された第1の信号駆動回路と、

前記第2の信号配線に接続された第2の信号駆動回路と、

前記走査配線及び共通配線に接続された走査駆動回路とを有する請求項22の液晶表示パネル。 - 前記表示領域の外側に、

前記第1の信号駆動回路,前記第2の信号駆動回路、及び前記走査駆動回路に接続された表示制御回路を有する請求項23の液晶表示パネル。 - 前記第1の電極または前記第2の電極の一方の電極が能動素子を介して信号配線に接続され、

前記第1の電極または前記第2の電極のうち、前記能動素子に接続されていない他方の電極が共通配線に接続され、

前記第3の電極は、所定の電位を印加することができる配線に接続されている請求項1または2に記載の液晶表示パネル。 - 前記信号配線に交差するように配置され、前記能動素子に接続された走査配線を有し、

前記信号配線、及び前記走査配線に囲まれた領域に対応して画素を構成し、該画素を複数配置して表示領域を形成した請求項25の液晶表示パネル。 - 前記表示領域の外側に、

前記信号配線に接続された信号駆動回路と、

前記走査配線に接続された走査駆動回路と、

前記共通配線に接続された共通配線駆動回路と、

前記所定の電位を印加することができる配線に接続された第3電極駆動回路を有する請求項26の液晶表示パネル。 - 前記表示領域の外側に、

前記信号駆動回路,前記走査駆動回路,前記共通配線駆動回路、及び前記第3電極駆動回路に接続された表示制御回路を有する請求項27の液晶表示パネル。 - 前記第1の電極と前記第3の電極は絶縁膜を介して異層に配置されていることを特徴とする請求項1〜28のいずれか一項に記載の液晶表示パネル。

- 前記第1の電極と前記第3の電極は、前記絶縁膜を介して少なくとも一部が重畳されて配置されていることを特徴とする請求項29の液晶表示パネル。

- 前記第1の電極と前記第3の電極のうち、下層に配置された電極は透明導電膜で構成されていることを特徴とする請求項29の液晶表示パネル。

- 1フレーム期間内の前記初期段階と途中段階の切り替えは、1フレーム期間の半分以下の時間内に行うことを特徴とする請求項1〜31のいずれか一項に記載の液晶表示パネル。

- 前記電位差ΔV1 と、前記距離dL と、前記ΔV2 と、前記距離dH とが、1フレーム期間内の初期時には(式1)を満足し、かつ、1フレーム期間内の半分以下の時間内に、(式2)を満足するように駆動することを特徴とする請求項33の液晶表示パネル。

- 一対の基板と、該一対の基板間に配置された液晶層を有する液晶表示パネルにおいて、

前記一対の基板の一方の基板上には、

複数の第1の信号配線と、複数の第2の信号配線と、前記複数の第1の信号配線及び前記複数の第2の信号配線に交差するように配置した複数の第1の走査配線と、前記複数の第1の信号配線及び前記複数の第2の信号配線に交差するように配置した複数の第2の走査配線とを配置し、前記複数の第1の信号配線及び前記複数の第1の走査配線のそれぞれの交点付近に対応して配置した第1の能動素子と、前記複数の第2の信号配線及び前記複数の第2の走査配線のそれぞれの交点付近に対応して配置した第2の能動素子と、前記第1の能動素子に接続されある方向に伸びた第1の電極と、該第1の電極と同じ方向に伸びた第2の電極と、前記第2の能動素子に接続され前記第1の電極と前記第2の電極間の前記第1の電極により近い位置に前記第1の電極と同じ方向に伸びて配置された第3の電極とを有し、

1フレーム期間の始めは、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが異なるように各電極に電位を与え、1フレーム期間の途中で、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが実質的に同一になるように各電極に電位を与え、前記1フレーム期間内の始めでは強電界を形成し、前記1フレーム期間の途中では前記1フレーム期間内の始めの電界よりも弱い電界を形成するように構成した液晶表示パネル。 - 一対の基板と、該一対の基板間に配置された液晶層を有する液晶表示パネルにおいて、

前記一対の基板の一方の基板上には、

複数の第1の信号配線と、複数の第2の信号配線と、前記複数の第1の信号配線及び前記複数の第2の信号配線に交差するように配置した複数の走査配線とを配置し、前記複数の第1の信号配線及び前記複数の走査配線のそれぞれの交点付近に対応して配置した第1の能動素子と、前記複数の第2の信号配線及び前記複数の走査配線のそれぞれの交点付近に対応して配置した第2の能動素子と、前記第1の能動素子に接続されある方向に伸びた第1の電極と、該第1の電極と同じ方向に伸びた第2の電極と、前記第2の能動素子に接続され前記第1の電極と前記第2の電極間の前記第1の電極により近い位置に前記第1の電極と同じ方向に伸びて配置された第3の電極とを有し、

1フレーム期間の始めは、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが異なるように各電極に電位を与え、1フレーム期間の途中で、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが実質的に同一になるように各電極に電位を与え、前記1フレーム期間内の始めでは強電界を形成し、前記1フレーム期間の途中では前記1フレーム期間内の始めの電界よりも弱い電界を形成するように構成した液晶表示パネル。 - 前記第1の電極と前記第3の電極は、絶縁膜を介して少なくとも一部が重畳して配置されていることを特徴とする請求項35または36の液晶表示パネル。

- 前記第2の電極は、前記複数の走査線と同じ方向に伸びた共通配線に接続されていることを特徴とする請求項36の液晶表示パネル。

- 前記第2の電極は、前記第1の能動素子及び前記第2の能動素子が接続された走査配線とは別の隣接する走査配線に接続されていることを特徴とする請求項36の液晶表示パネル。

- 一対の基板と、該一対の基板間に配置された液晶層を有する液晶表示パネルにおいて、

前記一対の基板の一方の基板上には、

複数の信号配線と、該複数の信号配線に交差するように配置した複数の第1の走査配線と、前記複数の信号配線に交差するように配置した複数の第2の走査配線とを配置し、前記複数の信号配線及び前記複数の第1の走査配線のそれぞれの交点付近に対応して配置した第1の能動素子と、前記複数の信号配線及び前記複数の第2の走査配線のそれぞれの交点付近に対応して配置した第2の能動素子と、前記第1の能動素子に接続されある方向に伸びた第1の電極と、該第1の電極と同じ方向に伸びた第2の電極と、前記第2の能動素子に接続され前記第1の電極と前記第2の電極間の前記第1の電極により近い位置に前記第1の電極と同じ方向に伸びて配置された第3の電極とを有し、

1フレーム期間の始めは、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが異なるように各電極に電位を与え、1フレーム期間の途中で、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが実質的に同一になるように各電極に電位を与え、前記1フレーム期間内の始めでは強電界を形成し、前記1フレーム期間の途中では前記1フレーム期間内の始めの電界よりも弱い電界を形成するように構成した液晶表示パネル。 - 一対の基板と、該一対の基板間に配置された液晶層を有する液晶表示パネルにおいて、

前記一対の基板の一方の基板上には、

複数の信号配線と、該複数の信号線に交差するように配置した複数の走査配線とを配置し、前記複数の信号配線及び前記複数のそれぞれの交点付近に対応して配置した第1の能動素子及び該第1の能動素子とは閾値電圧特性が異なる第2の能動素子と、前記第1の能動素子に接続されある方向に伸びた第1の電極と、該第1の電極と同じ方向に伸びた第2の電極と、前記第2の能動素子に接続され前記第1の電極と前記第2の電極間の前記第1の電極により近い位置に前記第1の電極と同じ方向に伸びて配置された第3の電極とを有し、

1フレーム期間の始めは、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが異なるように各電極に電位を与え、1フレーム期間の途中で、前記第1の電極と前記第2の電極間の電位差と、前記第2の電極と前記第3の電極間の電位差とが実質的に同一になるように各電極に電位を与え、前記1フレーム期間内の始めでは強電界を形成し、前記1フレーム期間の途中では前記1フレーム期間内の始めの電界よりも弱い電界を形成するように構成した液晶表示パネル。 - 前記第1の電極と前記第3の電極は、絶縁膜を介して少なくとも一部が重畳して配置されていることを特徴とする請求項40または41の液晶表示パネル。

- 少なくとも一方が透明な一対の基板と、前記一対の基板に挟持された液晶層とを有し、

前記一対の基板の一方の基板は、複数の信号配線と、前記複数の信号配線に交差するように配置した複数の走査配線と、前記複数の信号配線及び前記複数のそれぞれの交点付近に対応して配置した複数の能動素子と、前記複数の信号配線と前記複数の走査配線のそれぞれによって囲まれた領域からなる画素と、を有し、

前記画素内に、第1の電極及び第2の電極並びに能動素子を有し、前記第1の電極と前記第2の電極との間に電圧を印加して、前記第1の電極と前記第2の電極間に生じる電界により、前記液晶層の液晶分子の配向方向を制御して表示を行う液晶表示パネルにおいて、

前記第1の電極と前記第2の電極の間に、前記第1の電極若しくは前記第2の電極のどちらかに近づけるように第3の電極を配置し、前記第1の電極と前記第2の電極のうち、前記第3の電極との距離が近い側に配置された電極と、前記第3の電極の電位差ΔV1 が、1フレーム期間内の初期時に比べ1フレーム期間内の途中時では弱い電界が形成されるように駆動し、前記第1の電極と前記第2の電極と前記第3の電極の各間で生じる電界によって前記液晶層内の液晶分子の配向方向を制御して表示を行うように構成し、

前記電位差ΔV 1 と、前記第1の電極と前記第2の電極のうち前記第3の電極に近い方の電極と前記第3の電極との距離d L と、前記第1の電極と前記第2の電極のうち前記第3の電極との距離が遠い側に配置された電極と第3の電極との電位差ΔV 2 と、該遠い側に配置した電極と前記第3の電極との距離d H とが、1フレーム期間内の初期時には(式1)を満足し、かつ、1フレーム期間内の途中時に(式2)を満足するように駆動することを特徴とする液晶表示パネル。

- 前記電位差ΔV1 と、前記距離dL と、前記ΔV2 と、前記距離dH とが、1フレーム期間内の初期時には(式1)を満足し、かつ、1フレーム期間内の半分以下の時間内に、(式2)を満足するように駆動することを特徴とする請求項43の液晶表示パネル。

- 前記第1の電極と前記第2の電極のうち、前記第3の電極との距離が近い側に配置された電極と、前記第3の電極とが画素表示領域内で少なくとも一部分が絶縁膜を介して重畳していることを特徴とする請求項43または44に記載の液晶表示パネル。

- 前記重畳している2つの電極のうち、前記液晶層に近い側に配置された電極の幅が、前記液晶層から遠い側に配置された電極の幅よりも狭いことを特徴とする請求項45の液晶表示パネル。

- 前記第1の電極,第2の電極及び前記第3の電極が、くの字型に形成されていることを特徴とする請求項43〜46のいずれか一項に記載の液晶表示パネル。

- 前記一対の基板の一方の基板が透明基板である請求項1の液晶表示パネル。

- 前記第1の電極,第2の電極、及び第3の電極は、独立して電位が与えられる請求項48の液晶表示パネル。

- 前記第3の電極は、前記第1の電極と前記第2の電極間の前記第1の電極により近い位置に配置され、

前記第1の電極と前記第3の電極の電位差と、前記第2の電極と前記第3の電極の電位差が、1フレーム期間内の初期段階と途中段階で異なっている請求項49の液晶表示パネル。 - 一対の基板と、該一対の基板間に配置した液晶層と、前記一対の基板の一方の基板上に配置された、複数の信号配線と、前記複数の信号配線と交差して配置された複数の走査配線と、前記複数の信号配線と前記複数の走査配線との交点付近に配置された複数の能動素子と、前記複数の信号配線と前記複数の走査配線のそれぞれによって囲まれた領域からなる画素と、前記画素内に配置され、ある方向に伸びた第1の電極,第2の電極、及び第3の電極を有し、前記第1の電極と前記第2の電極と前記第3の電極の各間で生じる少なくとも2つの電位差が、前記複数の走査配線それぞれにおける1フレーム期間内の初期段階と途中段階で異なり、前記1フレーム期間内の初期段階では強電界を形成し、途中段階では前記初期段階の電界よりも弱い電界を形成するように、前記第1の電極,第2の電極、または前記第3の電極に与える少なくとも1つの電位を変え、前記第1の電極と前記第2の電極と前記第3の電極の各間で生じる電界によって前記液晶層内の液晶分子の配向方向を制御することにより、表示を制御するように構成した液晶表示パネルと、

光源と、を有する液晶表示装置。 - 前記光源を制御するインバータ回路を有する請求項51の液晶表示装置。

- 一対の基板と、該一対の基板間に配置した液晶層と、前記一対の基板の一方の基板上に配置された、複数の信号配線と、前記複数の信号配線と交差して配置された複数の走査配線と、前記複数の信号配線と前記複数の走査配線との交点付近に配置された複数の能動素子と、前記複数の信号配線と前記複数の走査配線のそれぞれによって囲まれた領域からなる画素と、前記画素内に配置され、ある方向に伸びた第1の電極,第2の電極、及び第3の電極を有し、前記第1の電極と前記第2の電極と前記第3の電極の各間で生じる少なくとも2つの電位差が、前記複数の走査配線それぞれにおける1フレーム期間内の初期段階と途中段階で異なり、前記1フレーム期間内の初期段階では強電界を形成し、途中段階では前記初期段階の電界よりも弱い電界を形成するように、前記第1の電極,第2の電極、または前記第3の電極に与える少なくとも1つの電位を変え、前記第1の電極と前記第2の電極と前記第3の電極の各間で生じる電界によって前記液晶層内の液晶分子の配向方向を制御することにより、表示を制御するように構成した液晶表示パネルと、

光源と、

該光源を制御するインバータ回路と、

チューナーとを有する液晶テレビ。 - 前記第3の電極は、前記第1の電極と前記第2の電極間の前記第1の電極により近い位置に配置され、

前記第1の電極,第2の電極、及び第3の電極間のそれぞれの電位差について、2つの電位差の関係が、1フレーム期間内の初期段階と途中段階で異なっている請求項53の液晶テレビ。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001284356A JP3879463B2 (ja) | 2001-09-19 | 2001-09-19 | 液晶表示パネル,液晶表示装置、及び液晶テレビ |

| US10/101,172 US7027023B2 (en) | 2001-09-19 | 2002-03-20 | Liquid crystal display panel, liquid crystal display device, and liquid crystal television |

| TW091105911A TWI250361B (en) | 2001-09-19 | 2002-03-26 | Liquid crystal display panel, liquid crystal display apparatus and liquid crystal television |

| KR1020020048452A KR100842503B1 (ko) | 2001-09-19 | 2002-08-16 | 액정 표시 패널, 액정 표시 장치 및 액정 텔레비전 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001284356A JP3879463B2 (ja) | 2001-09-19 | 2001-09-19 | 液晶表示パネル,液晶表示装置、及び液晶テレビ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003091014A JP2003091014A (ja) | 2003-03-28 |

| JP2003091014A5 JP2003091014A5 (ja) | 2005-02-24 |

| JP3879463B2 true JP3879463B2 (ja) | 2007-02-14 |

Family

ID=19107692

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001284356A Expired - Fee Related JP3879463B2 (ja) | 2001-09-19 | 2001-09-19 | 液晶表示パネル,液晶表示装置、及び液晶テレビ |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7027023B2 (ja) |

| JP (1) | JP3879463B2 (ja) |

| KR (1) | KR100842503B1 (ja) |

| TW (1) | TWI250361B (ja) |

Families Citing this family (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW548860B (en) * | 2001-06-20 | 2003-08-21 | Semiconductor Energy Lab | Light emitting device and method of manufacturing the same |

| US7768589B2 (en) | 2003-12-18 | 2010-08-03 | Sharp Kabushiki Kaisha | Display device |

| US20050140634A1 (en) * | 2003-12-26 | 2005-06-30 | Nec Corporation | Liquid crystal display device, and method and circuit for driving liquid crystal display device |

| KR101010433B1 (ko) * | 2003-12-26 | 2011-01-21 | 엘지디스플레이 주식회사 | 횡전계 방식 액정표시장치의 구동방법 |

| EP1825691A1 (en) | 2004-12-06 | 2007-08-29 | Koninklijke Philips Electronics N.V. | A stereoscopic display apparatus |

| CN100446079C (zh) | 2004-12-15 | 2008-12-24 | 日本电气株式会社 | 液晶显示装置、其驱动方法及其驱动电路 |

| JP4449784B2 (ja) * | 2005-02-28 | 2010-04-14 | エプソンイメージングデバイス株式会社 | 電気光学装置、駆動方法および電子機器 |

| KR20060112155A (ko) * | 2005-04-26 | 2006-10-31 | 삼성전자주식회사 | 표시 패널과, 이를 구비한 표시 장치 및 이의 구동 방법 |

| WO2006126373A1 (ja) * | 2005-05-24 | 2006-11-30 | Sharp Kabushiki Kaisha | 液晶表示装置及びその駆動方法 |

| KR101261611B1 (ko) * | 2005-09-15 | 2013-05-06 | 삼성디스플레이 주식회사 | 액정표시장치 |

| EP3229066A1 (en) | 2005-12-05 | 2017-10-11 | Semiconductor Energy Laboratory Co., Ltd. | Transflective liquid crystal display with a horizontal electric field configuration |

| TWI329216B (en) * | 2006-01-02 | 2010-08-21 | Chunghwa Picture Tubes Ltd | Pixel structure and liquid crystal display panel |

| JP4466596B2 (ja) * | 2006-03-29 | 2010-05-26 | カシオ計算機株式会社 | 配向転移方法 |

| JP2007279634A (ja) * | 2006-04-12 | 2007-10-25 | Nec Lcd Technologies Ltd | 横電界方式の液晶表示装置 |

| KR101241137B1 (ko) * | 2006-04-27 | 2013-03-08 | 엘지디스플레이 주식회사 | 횡전계방식 액정표시장치 및 그 구동방법 |

| KR101252854B1 (ko) * | 2006-06-29 | 2013-04-09 | 엘지디스플레이 주식회사 | 액정 패널, 데이터 드라이버, 이를 구비한 액정표시장치 및그 구동 방법 |

| KR101264693B1 (ko) * | 2006-06-30 | 2013-05-16 | 엘지디스플레이 주식회사 | 횡전계방식 액정표시장치 및 그 구동방법 |

| JP4605110B2 (ja) * | 2006-07-11 | 2011-01-05 | セイコーエプソン株式会社 | 液晶装置、及びそれを備えた画像表示装置 |

| JP5426823B2 (ja) * | 2007-11-06 | 2014-02-26 | エルジー ディスプレイ カンパニー リミテッド | 液晶表示装置 |

| KR20100034874A (ko) * | 2008-09-25 | 2010-04-02 | 삼성전자주식회사 | 평탄화된 기판을 포함하는 표시장치 및 이의 제조방법 |

| KR101641538B1 (ko) * | 2008-12-24 | 2016-07-22 | 삼성디스플레이 주식회사 | 표시 패널 |

| US9159283B2 (en) * | 2011-07-18 | 2015-10-13 | Innolux Corporation | Switch circuit, pixel element and display panel for using in refreshing memory in pixel |

| JP2015111173A (ja) * | 2012-03-27 | 2015-06-18 | シャープ株式会社 | 液晶駆動方法及び液晶表示装置 |

| FR2989483B1 (fr) * | 2012-04-11 | 2014-05-09 | Commissariat Energie Atomique | Dispositif d'interface utilisateur a electrodes transparentes |

| KR101602091B1 (ko) * | 2012-05-10 | 2016-03-09 | 샤프 가부시키가이샤 | 액정 구동 방법 및 액정 표시 장치 |

| CN104321691B (zh) * | 2012-05-23 | 2016-10-26 | 夏普株式会社 | 液晶驱动方法和液晶显示装置 |

| KR101975930B1 (ko) * | 2012-07-04 | 2019-05-07 | 엘지디스플레이 주식회사 | 듀얼모드 액정표시장치의 구동방법 |

| JP2015166752A (ja) * | 2012-07-05 | 2015-09-24 | シャープ株式会社 | 液晶表示装置および液晶表示装置の駆動方法 |

| KR102011985B1 (ko) | 2012-07-23 | 2019-08-20 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| CN102789100B (zh) * | 2012-07-27 | 2015-01-21 | 京东方科技集团股份有限公司 | 阵列基板、液晶显示面板和液晶显示器 |

| FR2995419B1 (fr) | 2012-09-12 | 2015-12-11 | Commissariat Energie Atomique | Systeme d'interface utilisateur sans contact |

| FR2996933B1 (fr) | 2012-10-15 | 2016-01-01 | Isorg | Appareil portable a ecran d'affichage et dispositif d'interface utilisateur |

| CN102937765B (zh) * | 2012-10-22 | 2015-02-04 | 京东方科技集团股份有限公司 | 像素单元、阵列基板、液晶显示面板、装置及驱动方法 |

| TWI514364B (zh) | 2014-03-28 | 2015-12-21 | Au Optronics Corp | 液晶顯示面板之液晶畫素電路及其驅動方法 |

| US20180330683A1 (en) * | 2017-05-15 | 2018-11-15 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Pixel driving electrode, array substrate thereof and display panel |

| US10520763B2 (en) * | 2017-06-06 | 2019-12-31 | Apple Inc. | Vcom drift improvements by new design and compensation techniques |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5648793A (en) * | 1992-01-08 | 1997-07-15 | Industrial Technology Research Institute | Driving system for active matrix liquid crystal display |

| JP3764504B2 (ja) * | 1995-02-28 | 2006-04-12 | ソニー株式会社 | 液晶表示装置 |

| JP3110648B2 (ja) * | 1995-03-22 | 2000-11-20 | シャープ株式会社 | 表示装置の駆動方法 |

| US5959599A (en) * | 1995-11-07 | 1999-09-28 | Semiconductor Energy Laboratory Co., Ltd. | Active matrix type liquid-crystal display unit and method of driving the same |

| US5847687A (en) * | 1996-03-26 | 1998-12-08 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of active matrix display device |

| US6549258B1 (en) * | 1997-09-04 | 2003-04-15 | Lg. Philips Lcd Co., Ltd. | Hybrid switching mode liquid crystal display device |

| JP2976948B2 (ja) * | 1997-10-06 | 1999-11-10 | 日本電気株式会社 | 液晶表示装置、その製造方法およびその駆動方法 |

| JP3361049B2 (ja) * | 1998-03-20 | 2003-01-07 | 株式会社東芝 | 液晶表示装置 |

| US6927825B1 (en) * | 1999-05-14 | 2005-08-09 | Sanyo Electric Co., Ltd. | Liquid crystal display using liquid crystal with bend alignment and driving method thereof |

| KR100322969B1 (ko) * | 1999-12-22 | 2002-02-01 | 주식회사 현대 디스플레이 테크놀로지 | 인-플레인 스위칭 모드 액정표시장치 및 그의 제조방법 |

| KR100736114B1 (ko) * | 2000-05-23 | 2007-07-06 | 엘지.필립스 엘시디 주식회사 | 횡전계 방식의 액정표시장치 및 그 제조방법 |

-

2001

- 2001-09-19 JP JP2001284356A patent/JP3879463B2/ja not_active Expired - Fee Related

-

2002

- 2002-03-20 US US10/101,172 patent/US7027023B2/en not_active Expired - Fee Related

- 2002-03-26 TW TW091105911A patent/TWI250361B/zh not_active IP Right Cessation

- 2002-08-16 KR KR1020020048452A patent/KR100842503B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR20030025169A (ko) | 2003-03-28 |

| US20030052847A1 (en) | 2003-03-20 |

| JP2003091014A (ja) | 2003-03-28 |

| TWI250361B (en) | 2006-03-01 |

| KR100842503B1 (ko) | 2008-07-01 |

| US7027023B2 (en) | 2006-04-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3879463B2 (ja) | 液晶表示パネル,液晶表示装置、及び液晶テレビ | |

| JP4051001B2 (ja) | 液晶表示装置 | |

| US7057698B2 (en) | Liquid crystal display panel of horizontal electric field applying type including plurality of pixels divided into at least four sub-pixels | |

| US8736779B2 (en) | Active matrix substrate, liquid crystal display panel, liquid crystal display device, method for manufacturing active matrix substrate, method for manufacturing liquid crystal display panel, and method for driving liquid crystal display panel | |

| JP4667587B2 (ja) | 液晶表示装置 | |

| JP5093714B2 (ja) | 液晶表示装置 | |

| JP3847590B2 (ja) | 液晶表示装置 | |

| JP2002162643A (ja) | 共通電極基板及びそれを備えた液晶表示装置 | |

| US9116568B2 (en) | Liquid crystal display device | |

| JP3264270B2 (ja) | 液晶表示装置 | |

| JP4287514B2 (ja) | 複合電界方式の液晶表示素子 | |

| WO2011040080A1 (ja) | 液晶表示装置 | |

| JP4628802B2 (ja) | 液晶表示装置 | |

| US7623190B2 (en) | LCD device having common line extension and gate line recess of equal areas | |

| WO2010131552A1 (ja) | 液晶表示装置 | |

| JP2017037135A (ja) | 液晶表示装置 | |

| KR100430376B1 (ko) | 액정디스플레이 | |

| JP4087306B2 (ja) | 液晶表示装置 | |

| US20090201453A1 (en) | Liquid crystal display panel and method of manufacturing the same | |

| JP4213356B2 (ja) | 液晶表示装置 | |

| WO2011024966A1 (ja) | 液晶表示装置 | |

| JP4551230B2 (ja) | 液晶表示装置の製造方法 | |

| JP2002214613A (ja) | 液晶表示装置 | |

| KR100640215B1 (ko) | 횡전계방식 액정표시장치 | |

| WO2010131510A1 (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040319 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040319 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060322 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20060419 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060725 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060925 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061017 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061030 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101117 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| S631 | Written request for registration of reclamation of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313631 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313121 Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121117 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121117 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131117 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |