JP3853473B2 - サーマルヘッド駆動装置 - Google Patents

サーマルヘッド駆動装置 Download PDFInfo

- Publication number

- JP3853473B2 JP3853473B2 JP19027297A JP19027297A JP3853473B2 JP 3853473 B2 JP3853473 B2 JP 3853473B2 JP 19027297 A JP19027297 A JP 19027297A JP 19027297 A JP19027297 A JP 19027297A JP 3853473 B2 JP3853473 B2 JP 3853473B2

- Authority

- JP

- Japan

- Prior art keywords

- resistance

- thermal head

- resistance value

- voltage

- heating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Electronic Switches (AREA)

- Measurement Of Resistance Or Impedance (AREA)

Description

【発明の属する技術分野】

本発明は、サーマルヘッド駆動装置に関し、詳細には、熱転写記録方式若しくは感熱記録方式を用いたプリンタ、ファクシミリ、複写機等に使用し得るサーマルヘッド駆動装置に関する。

【0002】

【従来の技術】

サーマルヘッドは、発熱抵抗素子を等間隔でライン上に形成し、発熱抵抗素子により発生するジュール熱を用いて記録を行うものである。サーマルヘッドによる記録は、感熱記録方式と熱転写方式に大別されるが、構造が簡単で、保守性・操作性に優れ、騒音がなく、また、安価で信頼性が高いといった多くの特長をもっている。そして、記録もモノクロからカラーまでできるため、用途が拡大してきており、このため、ファクシミリ、券売機、パソコン、ビデオ、電子黒板、OA関連機器の記録、各種のプリンタなどに広く使用されている。

【0003】

例えば、このサーマルヘッドを使用して、昇華プリンタ等の階調記録が可能なプリンタでは、サーマルヘッドの発熱抵抗素子のサーマルヘッド内での抵抗値のばらつきは印字エネルギーの差となって現れ、印字画像に濃度ムラが発生してしまう。このため、各発熱抵抗素子の抵抗値を基に印字データを演算し、均一なエネルギーで印字するためには抵抗値の補正が必要である。また、発熱抵抗素子は、経時的に抵抗値が変化する事が知られており、プリンタ電源投入時などに全発熱抵抗素子の抵抗値を測定し、この測定した抵抗値を用いて抵抗値の補正演算などを行うことが望ましい。

【0004】

つぎに、従来提案されている発熱抵抗素子の抵抗値のばらつきの補正方法を、具体例を挙げて説明する。例えば、特開昭60−244564号公報に記載されたサーマルプリンタが公知である。図10は、上記特開昭60−244564号公報に記載されたサーマルプリンタの構成を示すブロック図である。

【0005】

かかるサーマルプリンタは、図10に示す如く、サーマルヘッド200と、非印字用抵抗体201の抵抗値を測定する抵抗測定回路204と、印字用発熱抵抗体202に印加する電圧を発生する電圧発生回路205と、抵抗値測定回路204の抵抗値に基づいて、電圧発生回路205の出力電圧を制御する電圧制御回路206と、印字用発熱抵抗体202を選択的に駆動するための駆動パルス発生回路207と、サーマルヘッド200の印字用発熱抵抗体202および非印字用抵抗体201と外部回路とを着脱自在に接続するコネクタ203と、を備えている。

【0006】

上記の如く構成されるサーマルプリンタでは、サーマルヘッド200をサーマルプリンタに取り付けることにより、非印字用抵抗体201の両端には、コネクタ203を介して、抵抗測定回路204が接続され、印字用発熱抵抗体202の共通電極にはコネクタ203を介して電圧発生回路205の出力端子が接続され、印字用発熱抵抗体202の個別電極には、コネクタ203を介して駆動回路が接続されることになる。

【0007】

そして、非印字用抵抗体201の抵抗値が抵抗測定回路204で自動的に測定され、該抵抗測定回路204の測定値に基づいて、電圧制御回路206は電圧発生回路205の出力電圧を印字濃度に応じて予め設定されている最適値になるように制御している。すなわち、上記サーマルプリンタは、非印字用抵抗体201をサーマルヘッド200に付加し、この非印字用抵抗体201の抵抗値を測定し、印字用発熱抵抗体202の平均抵抗を推定するものである。

【0008】

しかるに、上記特開昭60−244564号公報に開示されたサーマルプリンタは、サーマルヘッドに非印字用抵抗体を設け、この非印字用抵抗体の抵抗値を測定して、印字用発熱素子の平均抵抗値を推定する構成であるので、専用のサーマルヘッドが必要となるとともに、抵抗値の測定精度が悪いという問題がある。

【0009】

また、特開昭60−244565号公報に記載れたサーマルプリンタが公知である。図11は、上記特開昭60−244565号公報に記載されたサーマルプリンタの構成を示すブロック図である。

【0010】

かかるサーマルプリンタは、図11に示す如く、サーマルヘッド301と、発熱抵抗体302の発熱抵抗を測定する抵抗測定回路304と、発熱抵抗体302に印加する電圧を発生する電圧発生回路305と、抵抗値測定回路304の抵抗値に基づいて、電圧発生回路305の出力電圧を制御する電圧制御回路306と、発熱抵抗体302を選択的に駆動するための駆動パルス発生回路307と、サーマルヘッド301の発熱抵抗体302と外部回路とを着脱自在に接続するコネクタ303と、検出用抵抗308とを備えている。

【0011】

上記の如く構成されるサーマルプリンタでは、サーマルヘッド301をサーマルサプリンタに取り付けることにより、発熱抵抗体302の共通電極にはコネクタ303および検出用抵抗308を介して電圧発生回路305の出力端子が接続されるとと共に、抵抗測定回路304および電圧制御回路306が接続され、発熱抵抗体302の個別電極にはコネクタ303を介して駆動回路が接続されることとなる。

【0012】

そして、電源投時に駆動パルス発生回路307から全ての発熱抵抗体302を同時に駆動するための駆動パルスを送出すると共に、検出用抵抗308の両端の電圧を抵抗測定回路304で測定することによって発熱抵抗体302群の抵抗値を求め、該抵抗測定回路304の測定値に基づいて、電圧制御回路306が電圧発生回路305の出力電圧を印字濃度に応じて予め定めた最適値になるように設定する。すなわち、上記サーマルプリンタは、サーマルヘッド電源経路に検出用抵抗308を挿入し、この検出用抵抗308の両端の電圧をA/D変換してサーマルヘッド301の発熱抵抗素子の抵抗を測定するものである。

【0013】

しかるに、特開昭60−244565は、サーマルヘッドを全素子がONとなるように駆動し、サーマルヘッドの印字電源ラインに挿入した抵抗の両端の電圧を検出して平均抵抗値を求める構成であるので、個々の発熱素子の抵抗値が解からないため、2値画像程度用にしか使えないという問題がある。

【0014】

これを解決する方法として、例えば、特開昭61−228970公報で開示されたサーマルヘッド駆動装置が公知である。図12は、上記特開昭60−244565号公報に記載されたサーマルプリンタの構成を示すブロック図である。

【0015】

かかるサーマルヘッド駆動装置は、図12に示す如く、サーマルヘッド上に形成された発熱抵抗体401と、発熱抵抗体401の各単位発熱抵抗体の電気抵抗値を測定する電気抵抗測定部(付図示)と、この電気抵抗に応じた印字パルスの印加時間を求めてこれに対応する印字制御データをメモリ404に格納するデータ処理部(不図示)と、各単位発熱体に対して印字制御データに対応する制御パルスを供給する印字制御部(不図示)と、を備えている。

【0016】

すなわち、かかるサーマルヘッド駆動装置は、サーマルヘッドに1画素のみがONとなるデータを転送し、印字を順次行うことで、印字用電源ラインに挿入した抵抗の両端に発生する電圧をA/D変換し、メモリに記憶していく事で、全発熱素子の抵抗値を各々測定するものである。

【0017】

【発明が解決しようとする課題】

しかしながら、特開昭61−228970公報で開示されたサーマルヘッド駆動装置では、以下の如き問題がある。この問題を、図13および図14を参照しつつ説明する。

【0018】

図13は、特開昭61−228970の1素子測定時の等価回路を示している。図13において、電源電圧をVH 、被測定素子(発熱抵抗体401)の抵抗値をRX 、抵抗測定用抵抗の抵抗値をR、A/D変換器の入力電圧をVR とすると、A/D変換器の入力電圧VR は、下式(1)により導出される。

【0019】

VR =(VH ・R)/(R+RX )・・・(1)

【0020】

図14は、図13の被測定素子の抵抗値RX とA/D変換器の入力電圧VR との関係を示す特性図である。図14に示す如く、被測定素子の抵抗値RX に対するA/D変換器の入力電圧VR は、抵抗測定用抵抗の抵抗値Rの影響により線形とはならず、被測定素子の抵抗値の測定に誤差が生じ、測定精度が悪いという問題がある。

【0021】

上記課題に鑑み、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能なサーマルヘッド駆動装置を提供することにある。

【0022】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各々の抵抗値を精度良く測定可能で、かつ、印字モードと抵抗値測定モードとを実行可能なサーマルヘッド駆動装置を提供することにある。

【0023】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、印字モードと抵抗値測定モードとで電源供給源を容易に切り替え可能なサーマルヘッド駆動装置を提供することにある。

【0024】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、印字モードと抵抗値測定モードとで電源供給源を切り替える場合に、抵抗測定回路を破損させないサーマルヘッド駆動装置を提供することにある。

【0025】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、簡単な構成で、抵抗測定回路を実現可能なサーマルヘッド駆動装置を提供することにある。

【0026】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、抵抗値測定回路を構成するA/D変換器に適正レベルの電圧を入力可能なサーマルヘッド駆動装置を提供することにある。

【0027】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、抵抗値測定回路を構成する増幅回路のゲインとオフセットを容易に調整可能なサーマルヘッド駆動装置を提供することにある。

【0028】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、高速な抵抗値測定が可能なサーマルヘッド駆動装置を提供することにある。

【0029】

また、本発明の目的は、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、発熱抵抗素子の抵抗値がばらついても濃度ムラのない高画質の印字が可能なサーマルヘッド駆動装置を提供することにある。

【0030】

【課題を解決するための手段】

上記課題を解決するために、本発明に係るサーマルヘッド駆動装置は、サーマルヘッドを構成する複数の発熱抵抗素子を駆動して印字を行うサーマルヘッド駆動装置において、前記複数の発熱抵抗素子の抵抗値を測定するために、当該複数の発熱抵抗素子が接続される電源ラインに定電流を供給する定電流発生手段と、前記複数の発熱抵抗素子の各抵抗値を測定する抵抗値測定手段と、を備えたものである。

【0031】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、複数の発熱抵抗素子の抵抗値を測定するために、複数の発熱抵抗素子が接続される電源ラインに定電流発生手段により定電流を供給して、複数の発熱抵抗素子の各抵抗値を測定することとしたので、抵抗測定用抵抗が不要となるため、この抵抗測定用抵抗による誤差がなくなり、精度良く複数の発熱抵抗素子の各抵抗値を測定することが可能となる。

【0032】

また、本発明に係るサーマルヘッド駆動装置は、サーマルヘッドを構成する複数の発熱抵抗素子を駆動して印字を行うサーマルヘッド駆動装置において、通常の印字を行う印字モードと、前記複数の発熱抵抗素子の抵抗値を測定する抵抗値測定モードとを有し、前記複数の発熱抵抗素子の抵抗値を測定するために、当該複数の発熱抵抗素子が接続される電源ラインに定電流を供給する定電流発生手段と、前記複数の発熱抵抗素子の各抵抗値を測定する抵抗値測定手段と、を備えたものである。

【0033】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、印字モードと印刷モードを有し、複数の発熱抵抗素子の抵抗値を測定するために、複数の発熱抵抗素子が接続される電源ラインに定電流発生手段により定電流を供給して、複数の発熱抵抗素子の各抵抗値を測定することとしたので、印字モードと抵抗値測定モードとを実行可能となり、また、抵抗測定用抵抗が不要となるため、この抵抗測定用抵抗による誤差がなくなり、精度良く複数の発熱抵抗素子の各抵抗値を測定することが可能となる。

【0034】

また、本発明に係るサーマルヘッド駆動装置は、前記印字モードの場合には、印字用電圧供給手段の出力を前記電源ラインに接続する一方、前記抵抗値測定モードの場合には、前記定電流発生手段の出力を当該電源ラインに接続する電源切換手段を備えたものである。

【0035】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、電源切換手段により、印字モードの場合には、印字用電圧供給手段の出力を電源ラインに接続する一方、抵抗値測定モードの場合には、定電流発生手段の出力を電源ラインに接続する構成であるので、請求項2に係るサーマルヘッド駆動装置の発明の効果に加えて、印字モードと抵抗値測定モードにおいて、電源ラインに接続する電源を容易に切換ることが可能となる。

【0036】

また、本発明に係るサーマルヘッド駆動装置は、前記電源切換手段は、前記電源ラインに前記印字用電圧供給手段が接続されている場合には、前記抵抗測定手段を、当該印字用電圧供給手段から電気的に切断する機構を備えたものである。

【0037】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、電源切換手段は、抵抗値測定手段を、印字用電圧供給手段から電気的に切断することとしたので、抵抗値測定手段に高電圧が印加されて、抵抗値測定手段が破壊されるのを防止することが可能となる。

【0038】

また、本発明に係るサーマルヘッド駆動装置は、前記電源切換手段は、抵抗値測定モードが設定された場合には、前記電源ラインの電荷の放電を行った後に、当該電源ラインに定電流発生手段の出力を接続するものである。

【0039】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、電源切換手段は、抵抗値測定モードが設定された場合には、電源ラインの電荷の放電を行った後に、電源ラインに定電流発生手段の出力を接続することとしたので、電源ラインの電荷により抵抗値測定手段が破壊されるのを防止することが可能となる。

【0040】

また、本発明に係るサーマルヘッド駆動装置は、前記抵抗値測定手段は、前記定電流発生手段の出力が供給される前記電源ラインに接続された複数の発熱抵抗素子を1素子毎に、順次ONさせることにより各発熱抵抗素子の両端にそれぞれ生じる電圧を夫々増幅して出力する増幅手段と、前記増幅手段の各出力をA/D変換して得られる各電圧データを出力するA/D変換手段と、前記A/D変換手段から出力される各電圧データに基づいて、前記複数の発熱抵抗素子の各抵抗値を算出する抵抗値算出手段と、を備えたものである。

【0041】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、抵抗値測定手段を、定電流発生手段の出力が供給される電源ラインに接続された複数の発熱抵抗素子を1素子毎に、順次ONさせることにより各発熱抵抗素子にそれぞれ生じる電圧を夫々増幅して出力する増幅手段と、増幅手段の各出力をA/D変換して得られる各電圧データを出力するA/D変換手段と、A/D変換手段から出力される各電圧データに基づいて、複数の発熱抵抗素子の各抵抗値を算出する抵抗値算出手段と、電圧データに基づいて、複数の発熱抵抗素子の各々の抵抗値を算出する抵抗値算出手段と、を備えた構成としたので、簡単な回路構成で抵抗値測定手段を実現することが可能となる。

【0042】

また、本発明に係るサーマルヘッド駆動装置は、前記増幅手段は、入力される前記被測定電圧を、前記A/D変換手段の適正入力範囲内のレベルに増幅するために、DCオフセットを可変に設定できるDCオフセットレベル可変手段と、ゲインを可変に設定できるゲイン可変手段とを備えたものである。

【0043】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、増幅手段に入力される被測定電圧をA/D変換手段の適正入力範囲内のレベルに増幅するために、増幅手段を、DCオフセットを可変に設定できるDCオフセットレベル可変手段と、ゲインを可変に設定できるゲイン可変手段とで構成したので、A/D変換手段に適正レベルの電圧を入力可能となり、A/D変換誤差を低減することが可能となる。

【0044】

また、本発明に係るサーマルヘッド駆動装置は、前記DCオフセットレベル可変手段は、前記発熱抵抗素子の下限抵抗値に略等しい基準抵抗を前記増幅手段の入力端子と接地間に接続した場合に、出力が前記A/D変換手段の略入力下限電圧になるようにDCオフセット値を調整するDCオフセット調整手段を備え、前記ゲイン可変手段は、前記発熱抵抗素子の上限抵抗値に略等しい基準抵抗を前記増幅手段の入力端子と接地間に接続した場合に、出力が前記A/D変換手段の略入力上限電圧になるようにゲインを調整するゲイン調整手段を備えたものである。

【0045】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、DCオフセットレベル調整手段が、発熱抵抗素子の下限抵抗値に略等しい基準抵抗を前記増幅手段の入力端子と接地間に接続した場合に、出力がA/D変換手段の略入力下限電圧になるようにDCオフセット値を調整する一方、ゲイン調整手段が、発熱抵抗素子の上限抵抗値に略等しい基準抵抗を増幅手段の入力端子と接地間に接続した場合に、出力がA/D変換手段の略入力上限電圧になるようにゲインを調整することとしたので、増幅手段のゲインとDCオフセット電圧を簡単に精度良く調整することが可能となる。

【0046】

また、本発明に係るサーマルヘッド駆動装置は、前記定電流発生手段の出力は、抵抗素子の一端に接続され、抵抗値測定時以外のときには、前記抵抗素子の他端をグランドに接続させるスイッチ機構を有するスイッチ手段を備えたものである。

【0047】

すなわち、本発明に係るサーマルヘッド駆動装置は、定電流発生手段の出力を抵抗素子の一端に接続し、抵抗値測定時以外のときには、抵抗素子の他端をグランドに接続させるスイッチ機構を有するスイッチ手段を備えているので、本発明に係るサーマルヘッド駆動装置の効果に加えて、抵抗測定時以外のときには、定電流発生手段の出力は抵抗素子を介してグランドに落ちることになり、抵抗値測定手段に規定範囲外の電圧が入力されるのを防止することができると共に、抵抗の非測定状態から測定状態への電圧変化量を少なくし、高速な抵抗値測定が可能となる。

【0048】

また、本発明に係るサーマルヘッド駆動装置は、前記抵抗素子は、前記複数の発熱抵抗素子の略平均抵抗値を有するものである。

【0049】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、抵抗素子の抵抗値を複数の発熱抵抗素子の略平均抵抗値としたので、より高速な抵抗測定が可能となる。

【0050】

また、本発明に係るサーマルヘッド駆動装置は、前記抵抗値測定手段により測定された前記複数の発熱抵抗素子の各抵抗値に基づいて、前記サーマルヘッドの印字制御を行う印字制御手段を備えたものである。

【0051】

すなわち、本発明に係るサーマルヘッド駆動装置によれば、測定された複数の発熱抵抗素子の各抵抗値に基づいて、サーマルヘッドの印字制御を行うこととしたので、発熱抵抗素子の抵抗値がばらついても濃度ムラのない高画質の印字が可能となる。

【0052】

【発明の実施の形態】

以下に添付図面を参照して、本発明に係るサーマルヘッド駆動装置の好適な実施の形態を詳細に説明する。

【0053】

図1は、本発明に係るサーマルヘッド駆動装置を適用した熱記録装置の回路構成を示すブロック図である。

【0054】

図1において、1は熱記録装置を示しており、この熱記録装置1は、ホストコンピュータから送出される印字データを格納するスレーブ共有メモリ2と、スレーブCPU6が実行する制御プログラム(例えば、印字モード実行プログラムや抵抗測定モード実行プログラム等)を格納したROM3と、スレーブCPU6のワークメモリとして使用され各種データを格納するRAM4と、I/O5と、ROM3に格納された制御プログラムに基づいて装置内の各部の制御を司るスレーブCPU6と、D/A変換器7と、アンプAMP15からの出力をA/D変換するA/D変換器8と、を備えている。

【0055】

さらに、サーマルヘッド17を駆動するヘッドドライブ回路9と、スレーブ共有メモリ2から1ライン毎に転送される印字データを一時的に格納するデュアルポートRAM10と、ヘッドドライブ回路9(2値化部96)でレベル変換された印字データを格納する出力RAM11と、印字モードにおいてサーマルヘッド17に駆動電圧を供給するヘッド印字用電源12と、抵抗値測定モードにおいてサーマルヘッド17の発熱抵抗素子RX1〜RXnの抵抗値を測定するための定電流ICONSTをサーマルヘッド17の電源ライン(VHライン)に供給する定電流源13と、を備えている。

【0056】

さらに、動作モードに応じてヘッド印字用電源12と定電流源13との出力を択一的に切り替えてサーマルヘッド9に出力するヘッド電源切換回路14と、A/D変換器8に入力される電圧のレベルを調整するアンプAMP15と、A/D変換器8への入力を切り替えるアナログセレクタ16と、記録紙に熱定着を行うサーマルヘッド17とを備えている。

【0057】

上記構成の熱記録装置は、通常の印字を行う印字モードとサーマルヘッド17の発熱抵抗素子RX1〜RXnの抵抗値を測定する抵抗値測定モードとを備えており、上記スレーブCPU6は、これら印字モードおよび抵抗値測定モードを実行し、各動作モードの設定は、スレーブCPU6がヘッドドライブ回路9のモード設定レジスタ91にアクセスすることにより行われる。

【0058】

また、スレーブCPU6、A/D変換器8、およびアンプAMP15等は、抵抗測定回路を構成する。この抵抗測定回路は、抵抗値測定モードにおいて、サーマルヘッド17の発熱抵抗素子Rxの抵抗値を測定する。

【0059】

図2は、図1に示した定電流源13の具体的回路構成を示す図である。定電流源13は、図2に示す如く、ツェナーダイオードD1と、分圧抵抗RA、分圧抵抗RBと、アンプOP1と、およびトランジスタT1等を備えている。図2に示す如く、分圧抵抗RAと分圧抵抗RBは互いに直列接続されており、この直列回路には、ツェナーダイオードD1が並列接続されている。そして、この並列回路の一端は定電源(+VDD)に接続され、他端は抵抗R2を介して接地されている。

【0060】

また、アンプOP1の正相入力端子(+)は、分圧抵抗RAと分圧抵抗RBの分圧点に接続され、逆相入力端子(−)は、抵抗R1を介して定電源(+VDD)に接続されるとともに、トランジスタT1のドレインに接続され、アンプOP1の出力は、トランジスタT1のゲートに接続されている。そして、トランジスタT1のゲートは、アンプOP1の出力に接続され、そのドレインは、アンプの逆相入力端子(−)に接続されるとともに、抵抗R1を介して、定電源(+VDD)に接続され、そのソースはヘッド電源切換回路14に接続されている。

【0061】

上記構成の定電流源13においては、定電源から供給される電圧+VDDが、分圧抵抗RAと分圧抵抗RBとにより分圧されて、アンプOP1の正相入力端子(+)に供給され、また、電圧+VDDは、抵抗R1を介して、アンプOP1の逆相入力端子(−)に供給される。アンプOP1は、入力電圧を作動増幅した出力をトランジスタT1のゲートに供給して、トランジスタT1をスイッチングする。トランジスタT1は、アンプOP1の出力でスイッチングされて、定電源から抵抗R1を介して入力される電圧+VDDを増幅して得られる定電流ICONST を、ソースからヘッド電源切換回路14に出力する。

【0062】

すなわち、定電流源13においては、定電流ICONSTの大きさは、分圧抵抗RA と分圧抵抗RBにより決定される。従って、分圧抵抗RAと分圧抵抗RBの抵抗値を設定することにより、定電流ICONST の大きさを任意に設定することができる。

【0063】

図3は、図1のアンプAMP15の具体的回路構成を示す図である。アンプAMP15は、図3に示す如く、アンプAMP15のDCオフセット量を設定するDCオフセット可変部151と、定電流源13から供給される定電流ICONSTにより生じるサーマルヘッド17の発熱抵抗体VXの両端間の電圧を増幅してアナログセレクタ16に出力する増幅部152とから成る。アンプAMP15は、DCオフセット可変部151と増幅部152とにより、A/D変換器8に入力される発熱抵抗体VXの両端間の電圧VXのレベルをA/D変換器8の適正入力電圧範囲となるように調整している。

【0064】

上記DCオフセット可変部151は、アンプOP2や可変抵抗(DCオフセット調整ボリューム)VR1等からなり、可変抵抗VR1,分圧抵抗R4、および分圧抵抗R5からなる直列回路の一端は、抵抗R3を介して定電源+VCCに接続され、その他端は接地されている。この直列回路と抵抗R3間には、一端が接地されたツェナーダイオードD2が接続されている。

【0065】

そして、アンプOP2の正相入力端子(+)には、可変抵抗VR1が接続され、アンプOP2の出力はその逆相入力端子(−)に帰還されるとともに、抵抗R6を介して、増幅部152のアンプOP3の逆相入力端子(−)に接続されている。また、可変抵抗VR1とアンプOP2間には一端が接地されたコンデンサC1が接続され、アンプOP2と抵抗R6間には一端が接地されたコンデンサC2が接続されている。

【0066】

増幅部152は、アンプOP3や可変抵抗(ゲイン調整用ボリューム)VR2等からなり、アンプOP3の正相入力端子(+)には定電流源13からの出力が入力され、その逆相入力端子(−)は、DCオフセット可変部151のアンプOP2の出力に抵抗R6を介して接続される。アンプOP3の出力は、抵抗R8および可変抵抗VR2を介してアンプOP3の逆相入力端子(−)に帰還される一方、アナログセレクタ14を経てA/D変換器8に接続される。

【0067】

上記構成のアンプAMP15においては、先ず、DCオフセット可変部151において、定電源から供給される電圧+VCCが、可変抵抗VR1,分圧抵抗R4、および分圧抵抗R5からなる直列回路により分圧されて、アンプOP2の正相入力端子(+)に供給され、増幅された後、抵抗R6を介して、DCオフセット電圧としてアンプOP3の逆相入力端子(−)に出力される。増幅部152では、アンプOP3の正相入力端子(+)に入力される定電流源13から入力される電圧と逆相入力端子(−)に入力される電圧とを、抵抗R2と可変抵抗VR2で決定されるゲインで作動増幅して、アナログセレクタ16を介してA/D変換器8に出力する。

【0068】

すなわち、アンプAMP15では、DCオフセット電圧は、可変抵抗VR1により調整され、ゲインはVR2で調整される。従って、可変抵抗VR1を調整することによりDCオフセット電圧を所望値に設定し、可変抵抗VR2を調整することによりゲインを設定できる。

【0069】

つぎに、上記アンプAMP15のゲインとDCオフセット電圧の調整方法について説明する。前述のように、アンプAMP15を具備することにより、A/D変換器8のA/D変換誤差を小さくできるが、より好ましくは、ゲインとDCオフセット電圧を正確に調整する必要がある。

【0070】

ここで、サーマルヘッド17の発熱抵抗素子Rxの製造バラツキの下限値をRLow,上限値をRHigh、A/D変換器8の適正下限入力電圧をVLOW,上限入力電圧をVHIGHとする。

【0071】

先ず、増幅部152の入力INとグランド間に、RLowと略等しい基準抵抗を接続し、DCオフセット調整ボリューム(可変抵抗)VR1を、出力電圧OUTがVLOWとなるように調整する。つぎに、入力INとグランド間にRHighを接続し、ゲイン調整ボリューム(可変抵抗)VR2を、出力電圧OUTがVHIGHとなるように調整する。以上の操作を数回繰り返すことにより、ゲインとDCオフセット電圧は完全に調整され、入力INにRLowを接続した場合には出力電圧OUTがVLOW、入力INにRHighを接続した場合には出力電圧OUTがVHIGHとなる。これにより、サーマルヘッド17の発熱抵抗素子Rxで生じる電圧VXは、理想的な電圧範囲でA/D変換器8に入力され、高精度な抵抗値測定が可能となる。

【0072】

図4は、図1のサーマルヘッド17の詳細な回路構成例を示している。サーマルヘッド17は、図4に示す如く、ライン状に配置され、一端がVH ライン(電源ライン)に並列に接続され他端がスイッチング回路TR1〜TRnにそれぞれ接続された複数の発熱抵抗素子RX1〜RXnと、ヘッドドライブ回路9から入力されるシリアルの印字データDATAをパラレルのデータに変換するシフトレジスタ171と、シフトレジスタ171から出力されるパラレルのデータをヘッドドライブ回路9のタイミングコントローラ93(図5参照)から供給されるラッチパルス*LATCH(*はLOWアクティブを示す。以下、同様である)に基づいてラッチするラッチ回路172と、前記ラッチ回路172の出力線とストローブジェネレータ92(図5参照)から供給される発熱抵抗素子RX1〜RXnを駆動するためのストローブパルス*STB(*はLOWアクティブを示す。以下、同様である)の供給線とに接続され、ラッチ回路172のラッチ信号*LATCHとストローブパルス*STBとの論理積信号を出力するアンドゲートAND1〜ANDnと、アンドゲートAND1〜ANDnからの出力により開閉制御されて発熱抵抗素子RX1〜RXnに記録電流を流すスイッチング回路TR1〜TR2と、を備えている。

【0073】

また、上記VHラインには、一端が接地されたノイズ防止用コンデンサC(パスコン)が接続されている。なお、これらスイッチング回路TR1〜TRn、シフトレジスタ171、ラッチ回路172、およびアンドゲート173は、IC化されている。

【0074】

図5は、図1に示した熱記録装置の一部構成を示しており、特に、ヘッドドライブ回路9,ヘッド電圧切換回路14,およびアナログセレクタ16の詳細な構成並びにその周辺の構成を示すものである。

【0075】

上記ヘッドドライブ回路9は、図5に示す如く、動作モード(印刷モード、抵抗測定モード)やストローブ幅(DUTY)等の設定レジスタを備えたモード設定レジスタ91と、モード設定レジスタで設定されたストローブ幅(DUTY)のストローブパルス*STB(*はLOWアクティブを示す。以下、同様である)を発生してサーマルヘッド17に供給するストローブジェネレータ92と、内部システムクロック,ヘッドドライブ回路9内の各種タイミング信号,およびサーマルヘッド17を駆動するタイミング信号(クロックCKやラッチパルス*LATCH)を生成するタイミングコントローラ93と、デュアルポートRAM10のリード制御を行うデュアルポートRAMI/F94と、デュアルポートRAMI/F94の出力先を動作モードに応じて切り替えるSW95と、デュアルポートRAMI/F94から出力される階調データ(例えば、8bitのデータ)をサーマルヘッド17で印字可能な2値データに変換する2値化回路96と、2値化された印字データを出力RAM11にライトする出力RAMI/F97と、奇数画素と偶数画素を交互に印字するための印字データを出力するO−E(ODD−EVEN)フィルタ98と、動作モードに応じてサーマルヘッド17への印字データの出力を択一的に切り替えるSW99とから構成されている。

【0076】

ヘッド電圧切換回路14は、図5に示す如く、例えば、リレーRY1とリレーRY2とからなり、リレーRY1は、スレーブCPU6の制御により、ヘッド印字用電源14の+端子側に接続されたメーク接点(a1接点)側とリレーRY2を介して抵抗値測定回路に接続されるブレーク接点(b1接点)側との接続を切り替える。また、リレーRY2は、スレーブCPU6の制御により、抵抗値測定回路に接続されたメーク接点(a2接点)側と一端が接地された抵抗RSに接続されたブレーク接点(b2接点)側との接続を切り替える。この抵抗RSは、サーマルヘッド17のVH ラインに実装されているノイズ防止用コンデンサCに蓄積された電荷を放電するために設けられている。

【0077】

上記構成のヘッド電圧切換回路14においては、印字時には、リレーRY1をON(a1側に接続)とし、ヘッド印字用電源10の出力がサーマルヘッド17のVHライン(電源ライン)に印加される。リレーRY1がONしている場合は、抵抗値測定回路が接続されることはなく、ヘッド印字用電源12の高電圧が微少電圧用の抵抗値測定回路に入力されないため、抵抗値測定回路が破壊されるのを防止できる。

【0078】

非印字時のスタンバイ状態には、リレーRY1とリレーRY2が共にOFF(b1,b2側に接続)となっており、サーマルヘッド17のVHライン(電源ライン)と接地間に接続されたノイズ防止用コンデンサCの電荷は、抵抗RSから放電されるため、サーマルヘッド17の発熱抵抗素子RXに付着したナトリウムイオン等によるグランドへの不要放電による素子破壊を防止することができる。

【0079】

また、抵抗値測定時には、スレーブCPU6は、I/Oポート5を介して、先ずリレーRY1をOFFし、所定時間経過後、リレーRY2をONとする。これにより、定電流源13から定電流ICONSTがサーマルヘッド17のVH ラインに供給される。リレーRY1をOFFし、所定時間経過後、リレーRY2をONしているため、サーマルヘッド17のVHラインに実装されているノイズ防止用コンデンサC(図7参照)に蓄積された電荷を抵抗RSにより放電し、このコンデンサCに蓄積された電荷により抵抗値測定回路が破壊されるのを防止できる。また、抵抗値測定を行う場合は、リレーRY2をONしているため、抵抗RSはVHラインから切り離されることになり、抵抗RSは抵抗値測定には影響を与えない。

【0080】

アナログセレクタ16は、図5に示す如く、例えば、アナログスイッチSW1とアナログスイッチSW2からなり、アナログスイッチSW1は、スレーブCPU6の制御により、AMP15に接続されたX1側と、サーマルヘッド17のTHRに接続されたY1側との接続を切り替える。また、アナログスイッチSW2は、スレーブCPU6の制御により、無接続のX2側と、オープンコレクタTTL18を介してストローブジェネレータ92のストローブパルス*STB供給線に接続されるY2側との接続を切り替える。

【0081】

このY2側にはオープンコレクタTTL18がワイアードORで接続されている。このオープンコレクタTTL18は、ストローブジェネレータ92から出力されるストローブパルス*STBがアクティブでない時にONされる。また、このY2側とヘッド電圧切換回路14のリレーRY2のa2側間には、抵抗素子RTYPが接続されている。また、このa2側と抵抗素子RTYPの接続は、定電流源13とAMP15間の接続に交差している。かかる抵抗素子RTYPは、定電流源13の出力がアンプAMP15に入力されるのを防止するためのものである。

【0082】

上記構成のアナログセレクタ16においては、抵抗値測定時には、スレーブCPU6は、I/Oポート5を介して、アナログスイッチSW1をX1側に切り替えると共に、アナログスイッチSW2をX2側に切り替える。これにより、アンプAMP15の出力がSW1を経てA/D変換器8に入力され、抵抗値測定が行われる。また、アナログスイッチSW2は、X2側に接続されているため、抵抗素子RTYPは抵抗値測定には何ら影響を与えない。

【0083】

一方、サーマルヘッド17に搭載されたサーミスタと抵抗RTとで発生した電圧でサーマルヘッド17の温度を測定する場合には、スレーブCPU6は、I/Oポート5を介して、アナログスイッチSW1をY1側に切り替え、また、アナログスイッチSW2をY2側に切り替える。これにより、サーマルヘッド17のTHR出力は、アナログスイッチSW1とアンプを経てA/D変換器8に入力されることになる。また、アナログスイッチSW2は、Y2側へ接続されているため、定電流源13の出力は、抵抗素子RTYPを通じてGNDに落ちることになり、アンプAMP15には、定電流源13の出力を開放した高電圧が印加されることはない。

【0084】

上記図1〜図5の構成において、定電流源13は定電流発生手段を、抵抗測定回路は抵抗値測定手段を、ヘッド印字用電源12は印字用電源供給手段を、ヘッド電源切換回路14は電源切換手段を、アンプAMP15は増幅手段を、A/D変換器8はA/D変換手段を、スレーブCPU6は抵抗値算出手段および印字制御手段を、DCオフセット可変部151はDCオフセットレベル可変手段を、増幅部152はゲイン可変手段を、DCオフセット調整ボリュームVR1はDCオフセット調整手段を、ゲイン調整用ボリュームVR2はゲイン調整手段を、アナログセレクタ16はスイッチ手段を、それぞれ実現している。

【0085】

つぎに、上記熱記録装置の動作を説明する。上記図1〜図5の如く構成される熱記録装置1は、前述の如く、印刷モードと抵抗測定モードを有しており、以下、抵抗測定モード、印字モードの順に説明する。

【0086】

(抵抗測定モードの動作)

この抵抗測定モードは、サーマルヘッド17の全発熱抵抗素子RX1〜RXnの各抵抗値を測定するモードであり、定電流源13に接続されたサーマルヘッド17の発熱抵抗素子RX1〜RXnを1画素(1素子)ずつ順次ONし、発熱抵抗素子RXに生じる電圧VX(VH ラインとグランド間の電圧)をスレーブCPU6がA/D変換器8にA/D変換させ、このA/D変換された電圧データに基づいて発熱抵抗素子RXの抵抗値を算出する。この抵抗測定モードは、スレーブCPU6によりシステムの電源投入時等に実行される。

【0087】

図6は、抵抗値測定モードにおいて、発熱抵抗素子RX1(1素子)のみをONさせる場合のサーマルヘッド17およびその関連部(定電流源13,A/D変換器8)を模式的に示した図である。

【0088】

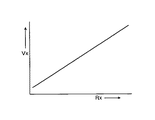

図7は、発熱抵抗素子RXの両端間に生じる電圧VXと、発熱抵抗素子RXとの関係を示す特性図である。

【0089】

図8は、抵抗値測定モードの動作を示すタイミングチャートであり、特に、オープンコレクタTTL18(図5参照)を作動させた場合のタイミングチャートを示している。

【0090】

図9は、抵抗値測定モードの動作を示すタイミングチャートであり、特に、オープンプンコレクタTTL18(図5参照)を作動させない場合のタイミングチャートを示している。

【0091】

図8および図9において、(A)は、ヘッドドライブ回路9から出力されるデータDATAの波形を示しており、(B)は、タイミングコントローラ93から出力されるクロックCLKの波形を示しており、(C)は、タイミングコントローラ93から出力されるラッチパルス*LATCHの波形を示しており、(D)は、ストローブジェネレータ92から出力されるストローブパルス*STBの波形を示しており、(E)は、A/D変換器8の動作を示す波形を示しており、(F)は、VH ラインとグランド間の電圧VXの波形を示している。

【0092】

以下、上記図6〜図9を参照して、抵抗値測定モードの動作を説明する。スレーブCPU6は、電源投入後、所定の初期化終了後、ROM3に格納された抵抗値測定プログラムを実行する。先ず、スレーブCPU6は、ヘッドドライブ回路9のモード設定レジスタ91に対して、抵抗値測定モードの設定を行う。つぎに、スレーブCPU6は、I/Oポート5を介して、ヘッド電源切換回路14のリレーRY1をOFFしてb1側に接続するとともに、リレーRY2をONしてa2側に接続するとともに、アナログセレクタ16のアナログスイッチSW1およびSW2をX1、X2側にそれぞれ接続する。これにより、定電流源13の定電流ICONSTが、リレーRY1およびリレーRY2を経てサーマルヘッド17のVHラインに供給されることになる。

【0093】

つぎに、スレーブCPU6は、デュアルポートバッファRAM10にサーマルヘッド9の発熱抵抗素子Rxのうち最初の1素子Rx 1のみをONさせる1ライン分のデータDATA"100・・・00"を書き込み、タイミングコントローラ93に対してスタート指示を出す。

【0094】

これに応じて、ヘッドドライブ回路9では、デュアルポートRAMI/F94によりデュアルポートバッファRAM10から発熱抵抗素子RX1〜RXnの最初の1素子(RX1)のみをONさせる1ライン分の図8(A)の如きデータDATAを読み出すとともに、データスイッチSW95およびデータスイッチSW99をX側に接続して、印字モードで使用される2値化部96,出力RAMI/F97,およびO−Eフィルタ98をスルーして、サーマルヘッド17のシフトレジスタ171へ転送する。これと同時に、タイミングコントローラ19は、1ライン分の図8(B)の如きクロックCLKをサーマルヘッド17のシフトレジスタ171に転送する。

【0095】

続いて、タイミングコントローラ93は、図8(C)の如きラッチパルス*LATCHを、サーマルヘッド17のラッチ回路172に出力してラッチ回路172に転送データをラッチさせる。その後、ストローブジェネレータ92は、図7(D)に示す如く、ストローブパルス*STBを「LOW」にしてアクティブにするとともに、タイミングコントローラ93は、スレーブCPU6に対して割込信号LSYNCをアサートする。これに応じて、スレーブCPU6は、A/Dコンバータ8を起動する。

【0096】

かくして、図6に示す構成のサーマルヘッド171では、先ず、シフトレジスタ92が、転送される図8(B)の如きクロックCLKのタイミングで、転送される1ライン分の図8(A)の如きデータDATAを取り込んで、ラッチ回路172に順次出力する。

【0097】

この場合、図6に示す如く、シフトレジスタ92には、発熱抵抗素子RX1〜RXnの最初の1素子(Rx1)のみをONさせるデータ"100・・・000"が取り込まれることになる。ラッチ回路172は、図8(C)の如きラッチパルス*LATCHにより起動され、シフトレジスタから供給されるデータを取り込んで、アンドゲートAND1〜ANDnに順次出力する。この場合、図6に示す如く、発熱抵抗素子RX1〜RXnの最初の1素子(RX1)のみをONさせるデータがラッチされることになる。

【0098】

アンドゲートAND1〜ANDnでは、ラッチ回路172から供給されるデータと図8(D)の如きストローブ信号*STBがインバータにより反転された信号との論理積が演算され、得られる論理積信号が、スイッチング回路TR1〜TRnのベースに出力される。これにより、スイッチング回路TR1のみが動作して、トランジスタのコレクタに接続された発熱抵抗素子Tx1がONする。

【0099】

続いて、定電流源13から出力される定電流ICONST により、発熱抵抗素子TX1に生じる電圧VX1、すなわち、サーマルヘッド17のVHラインとGND間に生じる図8(F)の如き電圧VX1が、アンプAMP15、アナログスイッチSW16およびバッファを介してA/D変換器8に入力し、A/D変換器8は入力する電圧VX1を図8(E)に示すタイミングで、A/D変換して得られる電圧データをスレーブCPU6に出力する。スレーブCPU6は、入力される電圧データからR−Iの抵抗値を算出する。

【0100】

なお、スレーブCPU6は、抵抗値測定時でないときには、SW2をY2側に接続するとともに、ストローブパルス*STBがアクティブでない場合にオープンコレクタTTL18をONすることにより、高速な抵抗値測定を実現している。これについては、詳細は後述する。

【0101】

最初の1素子のA/D変換が終了したら、スレーブCPU6は、A/Dコンバータ8から入力される電圧データをRAM4に格納し、最初の素子の抵抗値測定を終了する。この動作をONさせる発熱抵抗素子を1素子ずつ順次移動して測定を全発熱抵抗素子の回数nだけ繰り返すことにより、サーマルヘッド17の全発熱抵抗素子RX1〜RXnの個々の電圧データをRAM4に格納する。

【0102】

ところで、アナログスイッチSW1がX2側に接続されている場合、すなわち、抵抗値測定時には、抵抗素子RTYPは開放状態であるが、サーマルヘッド17へのデータ転送時など、ストローブパルスSTBがアクティブでない時には、定電流源13の出力は、開放状態となり、開放電圧まで上昇してしまう。

【0103】

さらに、図6に示すように、サーマルヘッド17の電源ラインVHにはノイズ防止用コンデンサC(パスコン)が通常実装されているため、何も対策しないで抵抗測定を行うと、図9(F)に示す如く、一度定電流源の開放電圧まで跳ね上がった電圧はノイズ防止用コンデンサCに蓄積された電荷の放電により、ストローブパルス*STBをアクティブにしてもすぐにVX とはならず、だらだらと下降した後、VXに落ち着く。

【0104】

従って、スレーブCPU6は、ストローブパルス*STBをアクティブしてから一定時間ウエイトした後、A/D変換器8を起動しなければないため、高速な抵抗値測定が行えず、サーマルヘッド17の全発熱抵抗素子の抵抗値測定を行うのに非常に時間がかかってしまう。

【0105】

そこで、本実施の形態では、前述の抵抗値測定時以外の時、定電流源13の出力を抵抗素子RTYPを通じてGNDに落とすアナログスイッチSW2にワイアッドORでオープンコレクタTTL18を接続し、このオープンコレクタTTL18をストローブパルス*STBがアクティブでない時にはONするように構成することにより、図8(F)に示すように、ストローブパルス*STBがアクティブでない時も定電流源13の開放電圧まで跳ね上がる事がなくなり、これによってVx に安定するまでの時間が短くて済むため、高速な測定が可能となる。

【0106】

前述の抵抗素子RTYPの抵抗値をサーマルヘッド17の発熱抵抗素子RXの製造ばらつきの平均値とする事により、前述の効果をより大きくすることができ、より高速な抵抗値測定が可能となる。

【0107】

つぎに、上記抵抗値測定モードにおける抵抗測定方法を具体的に説明する。上記図7において、例えば、発熱抵抗素子RXの抵抗値RXVは、ドライブトランジスタT1のコレクタ−エミッタ間の飽和電圧をVCEとした場合、下式(2)の如く表すことができる。

【0108】

RXV=(VX −VCE)/(ICONST ) ・・(2)

【0109】

上記式(2)においては、ICONSTとVCEは一定となるため、抵抗値の測定精度は高くなる。また、スレーブCPU6は、電圧データの代わりに、上記式(2)で算出した抵抗値RXVを、RAM4に格納することにしても良い。

【0110】

つぎに、上記測定した抵抗値に基づいて、印字モードでの印字条件を決定する方法を具体的に説明する。

【0111】

実際の印字時の印字エネルギーEは、ヘッド印字電圧をVH、階調画像データをD、1階調当たりのストローブパルス幅をτとすると、データDを8ビット(0〜255)とした場合、下式(3)の如く表すことができる。

【0112】

E=(VH 2/RXV)・(D・255)・τ ・・・(3)

【0113】

スレーブCPU6は、上記式(3)の条件で、印字モードでサーマルヘッドを印字制御する事により、発熱抵抗素子RXの抵抗値RXVがばらついても、均一でムラのない画像を印字することができる。

【0114】

(印字モードの動作)

スレーブCPU6は、ROM6に格納された印字モード実行プログラムに基づいて、印字モードを実行する。先ず、スレーブCPU6は、ヘッドドライブ回路9に、印刷モードでスタート指示を出す。これにより、サーマルヘッドドライブ回路9は、フリーラン動作を開始する。続いて、スレーブCPU6は、デュアルポートRAM10に1ライン分の例えば8bitの階調データを書き込む。

【0115】

そして、デュアルポートRAMI/F94は、デュアルポートRAM10に書き込まれた1ライン分の階調データを読み出す。読み出された1ライン分の階調データは、SW95を介して、2値化回路96に出力される。2値化回路96は、階調データをサーマルヘッド17で印字可能な2値の256レベルデータに変換し、出力RAMI/F97は、この2値の256レベルデータを出力RAM11に書き込む。

【0116】

続いて、O−Eフィルタ98は、出力RAMI/F97により出力RAM11から読み出された第1レベルの2値データを、先ず、奇数画素有効、偶数画素を非印字データとして、サーマルヘッド17に転送する。この場合、タイミングコントローラ93は、転送クロックCLKを、同時にサーマルヘッド17のシフトレジスタ172に転送する。

【0117】

タイミングコントローラ93は、データ転送と転送クロックCLKの転送が完了すると、ラッチパルス*LATCHをサーマルヘッド17に転送し、続いて、タイミングコントローラ92が、サーマルヘッド17にラッチパルス*LATCHを送信する。これにより、サーマルヘッド17では奇数画素の印字が行われる。

【0118】

つぎに、出力RAMI/F97は、出力RAM11から同じ2値データを読み出し、奇数画素を非印字データ、偶数画素を有効としてサーマルヘッド17のシフトレジスタ173に転送する。タイミングコントローラ93は、同様に、転送クロックCLKを、同時にサーマルヘッド17のシフトレジスタ171に転送する。そして、タイミングコントローラ93は、データ転送と転送クロックCLKの転送が完了すると、続いて、サーマルヘッド17のラッチ回路172にラッチパルス*LATCHを送信する。これにより、サーマルヘッド17では偶数画素の印字が行われる。

【0119】

以上の処理を、第1レベルから第256レベルまで行い、1ラインの印字を終了すると、タイミングコントローラ93は、スレーブCPU6に対して、割り込み信号/LSYNCをアサートし、次ラインのデータ転送を要求する。

【0120】

以上説明したように、本実施の形態においては、サーマルヘッド17を構成する複数の発熱抵抗素子RX1〜RXnの抵抗値を測定するために、これら発熱抵抗素子RX1〜RXnが接続される電源ライン(VH ライン)に、定電流源13により定電流ICONSTを供給して、発熱抵抗素子RX1〜RXnの各抵抗値を測定することとしたので、抵抗測定用抵抗が不要となるため、この抵抗測定用抵抗による誤差がなくなり、精度良く複数の発熱抵抗素子の各抵抗値を測定することが可能となる。

【0121】

また、本実施の形態では、熱記録装置1は、印字モードと抵抗測定モードとを有しており、印字モードにおいては、スレーブCPU6は、1ライン周期の間に1ライン分の多値データをデュアルポートRAM10に書き込み、2値化部96でサーマルヘッド17で印字可能な2値データに変換し、出力RAM11,出力RAMI/F97、およびO−Eフィルタ98を介して、この2値化データをサーマルヘッド17に転送する構成である。

【0122】

他方、抵抗測定モードにおいては、スレーブCPU6は、1ライン周期の間に1ライン分の多値データをデュアルポートRAM10に書き込み、ヘッドドライブ回路9では、出力RAM11,出力RAMI/F97、およびO−Eフィルタ98をスルーしてこの多値データをサーマルヘッド17に転送する構成である。

【0123】

従って、印字モードと抵抗モードとでサーマルヘッド回路9の一部を共有して使用することができ、モード毎に、別々の回路を使用する場合に比して、回路規模を小さくできる。また、上記した如く、印字モードにおいては、スレーブCPU6が、デュアルポートRAM10に1ライン分の多値データを書き込むと、ヘッドドライブ回路9が、この多値データを2値レベルデータに変換して、階調数回、この2値レベルデータをサーマルヘッド17に転送する構成であるので、高速かつ高品質な階調印字を行う事が可能となる。

【0124】

また、本実施の形態においては、ヘッド電源切換回路15が、印字モードの場合には、ヘッド印字用電源14の出力をサーマルヘッド17の電源ライン(VHライン)に接続する一方、抵抗値測定モードの場合には、定電流源13の出力をサーマルヘッド17の電源ラインに接続する構成であるので、モードに応じて、電源ラインに接続する電源を容易に切換ることが可能となる。

【0125】

また、上記ヘッド電源切換回路15では、リレーRY1のメーク接点(a1接点)側にヘッド印刷用電源12が接続され、ブレーク接点(b1接点)側に抵抗値測定回路(アンプAMP15,A/D変換器8等)が接続される構成であるので、リレーRY1がON(a1側に接続)している場合には、抵抗値測定回路が接続されないため、ヘッド印字用電源12の高電圧が微少電圧用の抵抗値測定回路に入力されず抵抗値測定回路が破壊されるのを防止できる。

【0126】

また、上記ヘッド電源切換回路15は、抵抗値測定を行う場合に、スレーブCPU6の指示により、先ず、リレーRY1をOFF(b1側に接続)し、所定時間経過後、リレーRY2をON(a2側に接続)する構成であるので、サーマルヘッド17の電源ライン(VHライン)に実装されているノイズ防止用コンデンサCに蓄積された電荷を抵抗RSを介してグランドに放電でき、このノイズ防止用コンデンサCに蓄積された電荷により抵抗値測定回路が破壊されるのを防止できる。

【0127】

また、本実施の形態では、抵抗測定回路を、アンプAMP15、A/D変換器8、およびスレーブCPU6等で構築しているので、簡単な回路構成で抵抗値測定回路を実現することが可能となる。

【0128】

また、上記アンプAMP15を、DCオフセット電圧を可変に設定できるDCオフセット可変部151と、ゲインを可変に設定できる増幅部152とで構成したので、A/D変換器8に入力される電圧を、A/D変換器8の適正入力範囲内のレベルに増幅することができ、A/D変換器8に適正レベルの電圧が入力されA/D変換誤差を低減することが可能となる。

【0129】

付言すると、抵抗値測定時の発熱抵抗素子RX1〜RXnのストレスを少なくするため、できるだけ微少電流で抵抗を測定するのが望ましいが、微少電流では、発熱抵抗素子RX1〜RXnで発生する電圧が小さくなり、一般に、A/D変換誤差が大きくなる。本実施の形態では、アンプAMP15を上記構成としたので、微少電流で抵抗を測定する場合にも、A/D変換誤差を低減することが可能である。

【0130】

また、上記アンプAMP15のDCオフセット値を調整する場合に、発熱抵抗素子Rーの下限抵抗値に略等しい基準抵抗を、増幅部152の入力INと接地間に接続し、DCオフセット調整ボリュームVR1を調整して、出力がA/D変換器8の略入力下限電圧になるようにDCオフセット値を調整する構成である。

【0131】

また、上記AMP15のゲインを調整する場合に、発熱抵抗素子Rーの上限抵抗値に略等しい基準抵抗を増幅部152の入力端子INと接地間に接続し、ゲイン調整用ボリュームVR2を調整して、出力がA/D変換器8の略入力上限電圧になるようにゲインを調整する構成である。従って、AMP15のゲインとDCオフセット電圧を簡単に精度良く調整することが可能となる。

【0132】

また、本実施の形態では、定電流源13の出力を抵抗素子TTYPの一端に接続し、この抵抗素子TTYPの他端を、アナログセレクタ16のアナログSW2のY2側に接続し、また、このY2側に、ストローブジェネレータ92のストローブパルス*STB供給線に接続されたオープンコレクタTTL18をワイアードORで接続した構成において、抵抗値測定時以外の時、このアナログSW2をY2側に接続して、定電流源13の出力を抵抗素子RTYP を通じてGNDに落とすと共に、ストローブパルス*STBがアクティブでない場合には、オープンコレクタTTL16をONすることとした。

【0133】

これにより、抵抗値測定時以外のときには、定電流源13の出力は抵抗素子RTYPを介してグランドに落ちることになり、抵抗値測定回路に規定範囲外の電圧が入力されるのを防止することができると共に、抵抗の非測定状態から測定状態への電圧変化量を少なくすることができ、高速な抵抗値測定が可能となる。

【0134】

また、上記抵抗素子RTYP の抵抗値を発熱抵抗素子RX1〜RXnの略平均抵抗値としたので、より高速な抵抗測定が可能となる。

【0135】

また、本実施の形態においては、スレーブCPU6は、測定された複数の発熱抵抗素子RX1〜RXnの各抵抗値に基づいて、サーマルヘッドの印字制御を行うこととしたので、発熱抵抗素子RX1〜RXnの抵抗値がばらついても濃度ムラのない高画質の印字が可能となる。

【0136】

なお、上記した実施の形態では、本発明に係るサーマルヘッド駆動装置を熱記録装置に適用した場合を説明したが、本発明はこれに限られるものではなく、感熱記録装置等にも適用可能であることは勿論である。

【0137】

また、上記したタイミングチャートは、本発明に係るサーマルヘッド駆動装置を実現するための一例にすぎず、本発明に係るサーマルヘッド駆動装置を実現可能なタイミングであれば如何なるタイミングとしても良い。

【0138】

また、本発明は、上記実施の形態のみに限定されるものではなく、発明の要旨を変更しない範囲で適宜変形して実施可能である。

【0139】

【発明の効果】

以上説明したように、本発明によれば、複数の発熱抵抗素子の抵抗値を測定するために、複数の発熱抵抗素子が接続される電源ラインに定電流発生手段により定電流を供給して、複数の発熱抵抗素子の各抵抗値を測定することとしたので、抵抗測定用抵抗が不要となるため、この抵抗測定用抵抗による誤差がなくなり、精度良く複数の発熱抵抗素子の各抵抗値を測定することが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能なサーマルヘッド駆動装置を提供することが可能となる。

【0140】

また、本発明によれば、印字モードと印刷モードを有し、複数の発熱抵抗素子の抵抗値を測定するために、複数の発熱抵抗素子が接続される電源ラインに定電流発生手段により定電流を供給して、複数の発熱抵抗素子の各抵抗値を測定することとしたので、印字モードと抵抗値測定モードとを実行可能となり、また、抵抗測定用抵抗が不要となるため、この抵抗測定用抵抗による誤差がなくなり、精度良く複数の発熱抵抗素子の各抵抗値を測定することが可能となる。この結果、サーマルヘッドを構成する複数の発熱抵抗素子の各々の抵抗値を精度良く測定可能で、かつ、印字モードと抵抗値測定モードとを実行可能なサーマルヘッド駆動装置を提供することが可能となる。

【0141】

また、本発明によれば、電源切換手段により、印字モードの場合には、印字用電圧供給手段の出力を電源ラインに接続する一方、抵抗値測定モードの場合には、定電流発生手段の出力を電源ラインに接続する構成であるので、印字モードと抵抗値測定モードにおいて、電源ラインに接続する電源を容易に切換ることが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、印字モードと抵抗値測定モードとで電源供給源を容易に切り替え可能なサーマルヘッド駆動装置を提供することが可能となる。

【0142】

また、本発明によれば、電源切換手段は、印字モードにおいては、抵抗値測定手段を、印字用電圧供給手段から電気的に切断することとしたので、抵抗値測定手段に高電圧が印加されて、抵抗値測定手段が破壊されるのを防止することが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、印字モードと抵抗値測定モードとで電源供給源を切り替えた場合に抵抗値測定精度を悪化させないサーマルヘッド駆動装置を提供することが可能となる。

【0143】

また、本発明によれば、電源切換手段は、抵抗値測定モードが設定された場合には、電源ラインの電荷の放電を行った後に、電源ラインに定電流発生手段の出力を接続することとしたので、電源ラインの電荷による抵抗値測定精度の悪化を防止することが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、印字モードと抵抗値測定モードとで電源供給源を切り替えた場合に抵抗値測定精度を悪化させないサーマルヘッド駆動装置を提供することが可能となる。

【0144】

また、本発明によれば、抵抗値測定手段を、定電流発生手段の出力が供給される電源ラインに接続された複数の発熱抵抗素子を1素子毎に、順次ONさせることにより各発熱抵抗素子にそれぞれ生じる電圧を夫々増幅して出力する増幅手段と、増幅手段の各出力をA/D変換して得られる各電圧データを出力するA/D変換手段と、A/D変換手段から出力される各電圧データに基づいて、複数の発熱抵抗素子の各抵抗値を算出する抵抗値算出手段と、電圧データに基づいて、複数の発熱抵抗素子の各々の抵抗値を算出する抵抗値算出手段と、を備えた構成としたので、簡単な回路構成で抵抗値測定手段を実現することが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、簡単な構成で、抵抗測定回路を実現可能なサーマルヘッド駆動装置を提供することが可能となる。

【0145】

また、本発明によれば、増幅手段に入力される被測定電圧をA/D変換手段の適正入力範囲内のレベルに増幅するために、増幅手段を、DCオフセットを可変に設定できるDCオフセットレベル可変手段と、ゲインを可変に設定できるゲイン可変手段とで構成したので、請求項6に係るサーマルヘッド駆動装置の効果に加えて、A/D変換手段に適正レベルの電圧を入力可能となり、A/D変換誤差を低減することが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、抵抗値測定手段を構成するA/D変換手段に適正レベルの電圧を入力可能なサーマルヘッド駆動装置を提供することが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、抵抗値測定回路を構成するA/D変換器に適正レベルの電圧を入力可能なサーマルヘッド駆動装置を提供することにある。

【0146】

また、本発明によれば、DCオフセットレベル調整手段が、発熱抵抗素子の下限抵抗値に略等しい基準抵抗を前記増幅手段の入力端子と接地間に接続した場合に、出力がA/D変換手段の略入力下限電圧になるようにDCオフセット値を調整する一方、ゲイン調整手段が、発熱抵抗素子の上限抵抗値に略等しい基準抵抗を増幅手段の入力端子と接地間に接続した場合に、出力がA/D変換手段の略入力上限電圧になるようにゲインを調整することとしたので、請求項7に係るサーマルヘッド駆動装置の効果に加えて、増幅手段のゲインとDCオフセット電圧を簡単に精度良く調整することが可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、抵抗値測定回路を構成する増幅回路のゲインとオフセットを容易に調整可能なサーマルヘッド駆動装置を提供することが可能となる。

【0147】

また、本発明によれば、定電流発生手段の出力を抵抗素子の一端に接続し、抵抗値測定時以外のときには、抵抗素子の他端をグランドに接続させるスイッチ機構を有するスイッチ手段を備えているので、抵抗測定時以外のときには、定電流発生手段の出力は抵抗素子を介してグランドに落ちることになり、抵抗値測定手段に規定範囲外の電圧が入力されるのを防止することができると共に、抵抗の非測定状態から測定状態への電圧変化量を少なくし、高速な抵抗値測定が可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、高速な抵抗値測定が可能なサーマルヘッド駆動装置を提供することが可能となる。

【0148】

また、本発明によれば、抵抗素子の抵抗値を複数の発熱抵抗素子の略平均抵抗値としたので、より高速な抵抗測定が可能となる。その結果、サーマルヘッドを構成する複数の発熱抵抗素子の各抵抗値を精度良く測定可能で、かつ、高速な抵抗値測定が可能なサーマルヘッド駆動装置を提供することが可能となる。

【0149】

また、本発明によれば、測定された複数の発熱抵抗素子の各抵抗値に基づいて、サーマルヘッドの印字制御を行うこととしたので、発熱抵抗素子の抵抗値がばらついても濃度ムラのない高画質の印字が可能となる。

【図面の簡単な説明】

【図1】 本発明に係るサーマルヘッド駆動装置を適用した熱記録装置の回路構成を示すブロック図である。

【図2】 図1に示した定電流源の具体的回路構成を示すブロック図である。

【図3】 図1に示したアンプの具体的回路構成を示すブロック図である。

【図4】 図1に示したサーマルヘッドの具体的な構成を示すブロック図である。

【図5】 図1に示した熱記録装置の一部構成を示す図である。

【図6】 抵抗値測定モードにおいて、発熱抵抗素子RX 1(1素子)のみをONさせる場合のサーマルヘッドおよびその関連部を模式的に示した図である。

【図7】 発熱抵抗素子RX の両端間に生じる電圧VX と、発熱抵抗素子RX との関係を示す特性図である。

【図8】 抵抗値測定モードの動作を示すタイミングチャートであり、特に、オープンコレクタTTL18を作動させた場合のタイミングチャートである。

【図9】 抵抗値測定モードの動作を示すタイミングチャートであり、特に、オープンプンコレクタTTL18を作動させない場合のタイミングチャートである。

【図10】 従来におけるサーマルプリンタの構成を示すブロック図である。

【図11】 従来におけるサーマルプリンタの構成を示すブロック図である。

【図12】 従来におけるサーマルヘッド駆動装置の構成を示すブロック図である。

【図13】 図12に示したサーマルヘッド駆動装置の1素子測定時の等価回路を示す説明図である。

【図14】 図13に示した被測定素子の抵抗値RXとA/D変換器の入力電圧VRとの関係を示す特性図である。

【符号の簡単な説明】

1 熱記録装置

2 スレーブ共有メモリ

3 ROM

4 RAM

5 I/O

6 スレーブCPU

7 D/A変換器

8 アナログ変換器

9 ヘッドドライブ回路

10 デュアルポートRAM

11 出力RAM

12 ヘッド印字用電源

13 定電流源

14 ヘッド電源切換回路

15 アンプAMP

16 アナログセレクタ

17 サーマルヘッド

18 オープンコレクタTTL

91 モード設定レジスタ

92 ストローブジェネレータ

93 タイミングコントローラ

94 デュアルポートRAMI/F

95 SW

96 2値化部

97 出力RAMI/F

98 O−Eフィルタ

99 SW

171 シフトレジスタ

172 ラッチ回路

Claims (4)

- サーマルヘッドを構成する複数の発熱抵抗素子を駆動して印字を行うサーマルヘッド駆動装置において、

通常の印字を行う印字モードと、前記複数の発熱抵抗素子の抵抗値を測定する抵抗値測定モードとを有し、

前記複数の発熱抵抗素子の抵抗値を測定するために、当該複数の発熱抵抗素子が接続される電源ラインに定電流を供給する定電流発生手段と、

前記複数の発熱抵抗素子の各抵抗値を測定する抵抗値測定手段と、

前記印字モードの場合には、印字用電圧供給手段の出力を前記電源ラインに接続する一方、前記抵抗値測定モードの場合には、前記定電流発生手段の出力を当該電源ラインに接続する電源切換手段と、

を備え、

前記電源切換手段は、前記抵抗値測定モードが設定された場合には、前記電源ラインの電荷の放電を行った後に、当該電源ラインに前記定電流発生手段の出力を接続することを特徴とするサーマルヘッド駆動装置。 - 前記定電流発生手段の出力は、抵抗素子の一端に接続され、

前記抵抗値測定手段は、

抵抗値測定時以外のときには、前記抵抗素子の他端をグランドに接続させるスイッチ機構を有するスイッチ手段を備えたことを特徴とする請求項1に記載のサーマルヘッド駆動装置。 - 前記抵抗素子は、前記複数の発熱抵抗素子の略平均抵抗値を有することを特徴とする請求項2に記載のサーマルヘッド駆動装置。

- 前記抵抗値測定手段により測定された前記複数の発熱抵抗素子の各抵抗値に基づいて、前記サーマルヘッドの印字制御を行う印字制御手段を備えたことを特徴とする請求項1〜3のいずれか一つに記載のサーマルヘッド駆動装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP19027297A JP3853473B2 (ja) | 1997-07-15 | 1997-07-15 | サーマルヘッド駆動装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP19027297A JP3853473B2 (ja) | 1997-07-15 | 1997-07-15 | サーマルヘッド駆動装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1134380A JPH1134380A (ja) | 1999-02-09 |

| JP3853473B2 true JP3853473B2 (ja) | 2006-12-06 |

Family

ID=16255401

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP19027297A Expired - Lifetime JP3853473B2 (ja) | 1997-07-15 | 1997-07-15 | サーマルヘッド駆動装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3853473B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002137429A (ja) * | 2000-11-02 | 2002-05-14 | Canon Ntc Inc | サーマルヘッドの発熱素子の抵抗値測定装置及び破損判定装置 |

| JP4183226B2 (ja) * | 2001-11-15 | 2008-11-19 | キヤノン株式会社 | 記録ヘッド用基板、記録ヘッド、記録装置、および記録ヘッド用基板の検査方法 |

| CN100427957C (zh) * | 2006-11-28 | 2008-10-22 | 南京师范大学 | 开关电源emi噪声源内阻抗测定装置及测定方法 |

| JP2012000954A (ja) * | 2010-06-21 | 2012-01-05 | Canon Inc | デバイス |

| CN113815315B (zh) * | 2020-11-26 | 2022-10-04 | 山东华菱电子股份有限公司 | 热敏打印头的恒流加热控制方法及热敏打印头 |

-

1997

- 1997-07-15 JP JP19027297A patent/JP3853473B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH1134380A (ja) | 1999-02-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3590702B2 (ja) | サーマルヘッドの抵抗データ測定方法及び装置並びにこれを備えたサーマルプリンタ | |

| US6469725B1 (en) | Thermal printhead | |

| JPH08169133A (ja) | サーマルヘッド装置 | |

| JPH05502633A (ja) | 感熱式プリンタの寄生抵抗補正装置 | |

| JP3520090B2 (ja) | サーマルプリンタのための加熱制御 | |

| JP3853473B2 (ja) | サーマルヘッド駆動装置 | |

| JPS63317359A (ja) | 多階調熱転写記録装置 | |

| US9186905B2 (en) | Thick film print head structure and control circuit | |

| JP6204718B2 (ja) | 素子基板、記録ヘッド及び記録装置 | |

| JP3439445B2 (ja) | サーマルヘッド温度測定用電圧検出回路およびこのサーマルヘッド温度測定用電圧検出回路を備えたプリンタ | |

| JPH06198944A (ja) | 動作パラメータの変動を補償するための改良されたサーマルプリンタシステムおよびその方法 | |

| JP4046816B2 (ja) | サーマルヘッド駆動装置 | |

| JPH10129026A (ja) | 素子駆動用集積回路 | |

| JP2001180030A (ja) | サーマルヘッド及びサーマルプリンタ | |

| JP2721150B2 (ja) | 感熱記録装置 | |

| JP2662123B2 (ja) | 記録ヘッド駆動装置 | |

| JPH07266599A (ja) | 熱転写プリント装置および該熱転写プリント装置の電圧降下を補償する方法 | |

| JP4385459B2 (ja) | サーマルヘッドの制御装置及びその制御方法 | |

| JP3673264B2 (ja) | サーマルヘッド制御装置 | |

| JP3876683B2 (ja) | プリンタおよびプリンタの予熱制御方法 | |

| KR100212322B1 (ko) | 잉크젯 프린터의 헤드 온도 조절 장치 | |

| JP2681004B2 (ja) | サーマルヘッド制御回路 | |

| JP2003154697A (ja) | プリンタおよびプリンタの予熱制御方法 | |

| JP2019171708A (ja) | サーマルプリンタおよび印刷制御方法 | |

| JPH0890821A (ja) | サーマルプリンタの駆動制御装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040713 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060511 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060516 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060714 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060808 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060906 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100915 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100915 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110915 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120915 Year of fee payment: 6 |