JP3849842B2 - はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法 - Google Patents

はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法 Download PDFInfo

- Publication number

- JP3849842B2 JP3849842B2 JP2000218046A JP2000218046A JP3849842B2 JP 3849842 B2 JP3849842 B2 JP 3849842B2 JP 2000218046 A JP2000218046 A JP 2000218046A JP 2000218046 A JP2000218046 A JP 2000218046A JP 3849842 B2 JP3849842 B2 JP 3849842B2

- Authority

- JP

- Japan

- Prior art keywords

- flux

- soldering

- electronic circuit

- solder

- solder paste

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

Landscapes

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

- Wire Bonding (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法に関する。

【0002】

【従来の技術】

例えば、部品搭載基板に対する部品のはんだ付けに当たっては、周知のように、フラックスが用いられる。フラックスの主な機能は、部品搭載基板に設けられた金属導体及び部品のはんだ付け用金属の表面の酸化皮膜を除去し、はんだの濡れ性を向上させることにある。フラックスとしては、ロジンを主成分とするものが最もよく知られている。ロジンには、アビエチン酸、レボビマル酸等のカルボン酸が含まれており、カルボキシル基の働きにより、はんだ付けされる金属表面の酸化膜を除去する。

【0003】

フラックスには、通常、上述したロジンの外、印刷性の向上及び仮止め強度を得る目的で、溶剤、可塑剤またはチキソ剤等の各種の添加物が配合される。例えば、特開平11−121915号公報は、粘性を、アルコール添加によって調整するタイプのフラックスを開示している。

【0004】

更に、別のフラックスとして、ミル規格で規定されているRMA(ハロゲンフリー)系フラックスも知られている。このフラックスの場合、リフロー後、フラックス等の洗浄工程が省略される。

【0005】

上述したフラックスは、はんだ付け後は、はんだ付けされた部品の接着に関与せず、はんだ接合は、はんだ金属の溶融接合によって達成される。従って、はんだ付けされる金属間の接合強度は、はんだ接合面積に依存する。

【0006】

ところが、各種電子機器において、高密度実装が進むにつれ、部品が小型化され、部品の配置間隔が狭ピッチ化され、これに伴い、はんだ接合面積の狭小化が急速に進展しつつあり、現段階でも、既に、十分なはんだ付け強度を確保することが困難になっている。しかも、実装の高密度化、部品の小型化及び部品の配置間隔の狭ピッチ化は、更に進展する傾向にあり、はんだ接合面積のみによってはんだ接合強度を確保する従来手段では、この技術動向に対応することが、ますます困難になる傾向にある。

【0007】

一般に、はんだ接合強度を確保する手段として、はんだのフィレット部を形成し、部品の端子と部品搭載基板上の導体(ランドまたははんだバンプ)とのはんだ接合面積を拡大する手段が採られている。ところが、高密度実装においては、フィレット部の接合面積も小さくなってしまうため、フィレット部による接合強度の増大手段も採りにくい。

【0008】

また、例えば、各種の電子回路モジュールでは、両面実装タイプの部品搭載基板を用い、部品搭載基板の一面上に高温はんだを用いて部品をはんだ付け(通炉)した後、他面に部品を搭載し、再び通炉する。従って、部品搭載基板の他面側における部品のはんだ付けに当たっては、一面側の高温はんだよりも低い融点を持つ低温はんだを用いてはんだ付けする必要がある。従来、はんだの融点はPbの含有量によって調整するのが一般的であった。

【0009】

ところが、地球環境保全の立場から、Pbを含有しないはんだ(Pbフリーはんだ)が要求され、そのようなはんだ組成の開発が盛んに行われている。しかし、Pbフリーはんだで、従来の高温はんだに匹敵する高温融点のはんだ組成は、現在のところ、実用化されていない。理由として、Pbフリーはんだ自体の融点が220℃前後と、共晶はんだに比較し、約40℃も上昇するため、Pb以外の代替組成が見つからないからである。このため、両面実装タイプの部品搭載基板において、両面側で用いられるはんだの融点差を十分にとることができず、部品を部品搭載基板上に実装する際、部品が浮動し、または脱落する等の不具合が生じる。

【0010】

更に、半導体チップを用いた電子回路モジュールにおいては、半導体チップをチップ搭載基板にはんだ付けした後、封止剤を接合界面に流し込み、半導体チップと、チップ搭載基板とを封止剤で接着固定する作業が付加される。

【0011】

ところが、封止剤注入時にフラックスの残渣が残っていると、フラックスのために、封止剤が半導体チップと基板との間の界面に十分に到達せず、接着力が発揮できない。そこで、封止剤を注入する前、フラックスを洗浄する工程が付加される。フラックスの洗浄は、通常、揮発性有機溶剤を用い、数回に分けて行なわれる。ところが、環境保全等の目的から、揮発性有機溶剤の使用が規制されており、フラックスの洗浄工程は、コストおよび環境保全の両面から、負担の大きい工程となっている。

【0012】

更に、上述のようにして得られた電子回路モジュールをマザー基板に搭載して、電子回路装置を構成する場合、チップ搭載基板にセラミックを用い、マザー基板に有機樹脂基板を用いた組み合わせにおいては、搭載後の熱衝撃試験などにおいて、セラミック基板及び有機樹脂基板の熱膨張率の違いから、はんだ接合部に収縮応力が集中し、クラックが入り易く、接合寿命が短いとされている。よってはんだ接合強度向上を図るため、封止剤の注入を行ないたいが、マザー基板全体を、フラックス洗浄工程及び封止剤注入工程に付することは、かなりのコストアップを招くため、実際には行われていない。

【0013】

【発明が解決しようとする課題】

本発明の課題は、実装の高密度化、部品の小型化及び部品の配置間隔の狭ピッチ化等に対しても、十分な接合強度をもって対応し得るはんだ付け用フラックス及びはんだペースト及びはんだ付け方法を提供することである。

【0014】

本発明のもう一つの課題は、両面実装タイプの部品搭載基板において、両面側で用いられるはんだの融点差を十分にとらなくとも、部品の浮動または脱落等の不具合を確実に阻止し得るはんだ付け用フラックス及びはんだペースト及びはんだ付け方法を提供することである。

【0015】

本発明の更にもう一つの課題は、フラックス洗浄工程を必要とせず、製造コストの安価な電子部品装置、電子回路モジュール及び電子回路装置を提供することである。

【0016】

本発明の更にもう一つの課題は、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子部品装置、電子回路モジュール及び電子回路装置を提供することである。

【0017】

【課題を解決するための手段】

上述した課題を解決するため、本発明に係るはんだ付け用フラックスは、接着性樹脂と硬化剤とを含有する。

【0018】

本発明に係るフラックスは、接着性樹脂と、硬化剤とを含有するから、はんだ付け後に、接着性樹脂を、部品搭載基板と部品を固定する接着剤として機能させることができる。このため、衝撃や熱ストレスに対し、部品の剥離、脱落を防ぎ、はんだ接合の信頼性を向上させることができる。この点、はんだ付け後に、接着機能を持たない従来のロジン系フラックスと著しく異なる。

【0019】

しかも、本発明に係るフラックスを使用することにより、フィレット部がなくても、十分な固着強度を確保できる。このため、部品搭載基板上に形成される部品接続用導体(ランド)に、フィレット部を生じさせるための領域を設ける必要がなくなるので、実装密度を向上させることが可能となる。

【0020】

本発明に係るフラックスにおいて、接着性樹脂としては、多数の樹脂材料から、温度に応じて、高い接着力を示す樹脂を選択し、これを接着性樹脂として用いることができる。従って、両面実装タイプの部品搭載基板の1面目に本発明に係るフラックスを用いて、部品をはんだ付けした後、部品搭載基板の2面目に通常の共晶はんだを用い、リフロー炉を通炉した場合でも、1面目に搭載された部品がシフティング、マンハッタン現象(部品立ち現象)または脱落等の不具合を起こすことはない。勿論、1面目及び2面目の両はんだ付け処理において、本発明に係るフラックスを用いることができる。

【0021】

本発明に係るフラックスは液状またはペーストの形態を採ることができる。このようなフラックスは、印刷、ディスペンサー塗布、スプレー、はけ塗り等の手段によって、部品搭載基板等に容易に塗布できる。

【0022】

本発明に係るフラックスにおいて、好ましい接着性樹脂は、熱硬化性樹脂である。熱硬化性樹脂の具体例としては、エポキシ樹脂、フェノール樹脂、ポリイミド樹脂、シリコン樹脂または変性樹脂またはアクリル樹脂から選択された少なくとも1種を挙げることができる。例示された樹脂材料の種類及び配合量は、接着温度帯及び目標とする皮膜硬度等に応じて選択することができる。

【0023】

硬化剤は、接着性樹脂を硬化させるものであればよい。好ましくは、カルボン酸を含む。カルボン酸を含む硬化剤は、熱硬化性樹脂に対する硬化作用のみならず、はんだ付けされる金属表面の酸化膜を除去するフラックス作用も兼ね備える。

【0024】

本発明に係るフラックスは、溶剤、可塑剤及びチキソ剤等を含んでいてもよい。溶剤は、接着性樹脂の硬化温度及び硬化速度を調整すると共に、塗布形態に応じて粘度を調整するために加えられる。可塑剤及びチキソ剤も、塗布形態に応じて、粘度を調整するために加えられる。溶剤、可塑剤及びチキソ剤等は、その使用目的に合うように、配合量が選択される。

【0025】

本発明に係るフラックスは、接着性樹脂、還元作用をもたらす有機酸、カルボン酸、溶剤または硬化剤を封入したマイクロカプセルの形態であってもよい。

【0026】

更に、本発明に係るフラックスは、はんだ粉末と混合して、はんだペーストを構成するために用いることもできる。はんだ粉末は、Sn、Cu、Ag、Sb、Pb、In、Zn及びBiから選択することができる。Pbフリーのはんだペーストを得る場合には、はんだ粉末はPb以外のはんだ粉末で構成する。

【0027】

本発明は、更に、上述したフラックスを用いた電子部品装置、電子回路モジュール及び電子回路装置を開示する。まず、本発明に係る電子部品装置は、少なくとも1つの電子部品と、部品搭載基板と、はんだ付け用フラックスとを含む。前記電子部品は、部品搭載基板の上にはんだ付けされている。前記はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有し、前記電子部品と前記部品搭載基板との間に介在し、両者を接着している。

【0028】

前記電子部品と前記部品搭載基板との間に介在するはんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能する。このはんだ付け用フラックスは洗浄する必要がなく、そのまま接着はんだ付け用フラックスとして用いることができる。従って、フラックス洗浄工程を必要とせず、製造コストの安価な電子部品装置を得ることができる。しかも、はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子部品装置を得ることができる。

【0029】

次に、本発明に係る電子回路モジュールは、半導体チップと、チップ搭載基板と、はんだ付け用フラックスとを含む。前記半導体チップは、少なくとも1つの半導体素子を含み、チップ搭載基板の上にはんだ付けされている。前記はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有し、前記半導体チップと前記チップ搭載基板との間に介在し、両者を接着している。

【0030】

前記半導体チップと前記チップ搭載基板との間に介在するはんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能する。このはんだ付け用フラックスは洗浄する必要がなく、そのまま接着はんだ付け用フラックスとして用いることができる。従って、フラックス洗浄工程を必要とせず、製造コストの安価な電子回路モジュールを得ることができる。しかも、はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子回路モジュールを得ることができる。

【0031】

更に、本発明に係る電子回路装置は、電子回路モジュールと、マザー基板と、はんだ付け用フラックスとを含む。前記電子回路装置は、前記マザー基板上にはんだ付けされている。前記はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有し、前記半導体チップと前記マザー基板との間に介在し、両者を接着している。このはんだ付け用フラックスは洗浄する必要がなく、そのまま接着はんだ付け用フラックスとして用いることができる。従って、フラックス洗浄工程を必要としないから、製造コストの安価な電子回路装置を得ることができる。しかも、はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子回路装置を得ることができる。

【0032】

本発明は、更に、上述したフラックス及びはんだペーストを用いたはんだ付け方法についても開示する。

【0033】

【発明の実施の形態】

<フラックス、電子部品装置>

実施例1

熱硬化性樹脂としてビスフェノールAを用い、硬化剤にはカルボン酸の無水物を使用した。熱硬化性樹脂及び硬化剤の配合比は重量比で1:1とした。また、粘性を確保するために、少量の溶剤及びチクソ剤を配合した。

【0034】

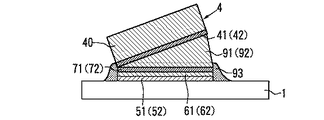

上記組成にて調製したフラックス3を、予め、はんだバンプ21、22を施した部品搭載基板1(図1(a)参照)の上に塗布(図1(b)参照)した。次に、図1(c)に示すように、長さ1mm、幅0.5mmのチップ状の電子部品4を搭載した。電子部品4は、基体40の相対する両端に端部電極41、42を有し、端部電極41、42がはんだバンプ21、22上に位置するようにして、部品搭載基板1上に配置した。電子部品4を搭載した部品搭載基板1を、リフロー炉に通炉し、電子部品4の基体40の両端に設けられた端部電極41、42をはんだバンプ21、22にはんだ接合した。これにより、本発明に係る電子部品装置が得られる。フラックス3は、電子部品4と部品搭載基板1との間に生じる間隔に充填され、接着性はんだ付け用フラックスとして機能する。得られた電子部品装置について、図2に示すように、電子部品4を横方向F1に押し、部品横押し強度を測定した。

【0035】

比較例1

比較のために、従来のロジン系フラックスを用い、図1に従って部品を搭載し、はんだ付け処理を行い、次に、図2に示した試験方法に従い、部品横押し強度を測定した。

【0036】

図3は横押し強度試験結果を示している。図3に示すように、従来のロジンフラックスを用いた比較例1の横押し強度平均値は800g程度であったが、本発明に係るフラックスを使用した実施例1では、平均値1600g程度の横押し強度を得ることができた。

【0037】

電子部品4と部品搭載基板1との間に生じる間隔に充填されているフラックスは、接着性樹脂と、硬化剤とを含有しており、接着性接着剤として機能する。このフラックス(はんだ付け用フラックス)3は洗浄する必要がなく、そのまま接着はんだ付け用フラックスとして用いることができる。従って、フラックス洗浄工程を必要としない製造コストの安価な電子部品装置を得ることができる。しかも、フラックス3で構成されるはんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着性はんだ付け用フラックスとして機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子部品装置を得ることができる。

【0038】

実施例2

実施例1で調製したフラックスと、はんだ粉末とを混合し、はんだぺーストを調製した。はんだ粉末に対するフラックスの配合量は10wt%とした。このはんだペーストを用いて、チップ部品を部品搭載基板上にはんだ付けした。図4(a)〜(c)は部品搭載基板の詳細と、部品搭載基板に対するチップ部品のはんだ付け工程を示す部分断面図である。部品搭載基板1は、Cu膜51(52)、Ni膜61(62)及びAu膜71(72)を順次に積層して形成した2つのランドを有する。

【0039】

上述した部品搭載基板1のランドの上に、本発明に係るはんだペースト81(82)を塗布した(図4(a)参照)。はんだペースト81(82)の塗布に当たっては、厚み100μmのメタルマスクを用いて印刷した。メタルマスクの開口寸法は0.5mm×0.3mmとし、電子部品4の搭載されるランド寸法と同寸法とした。

【0040】

そして、はんだペースト81(82)の上に、長さ1mm、幅0.5mmの電子部品4を搭載(図4(b)参照)し、リフロー炉に通炉することにより、電子部品4を部品搭載基板1上にはんだ付けした(図4(c)参照)。これにより、本発明に係る電子部品装置が得られる。

【0041】

この後、図2に示した方法に従って横押し強度を測定した。図4(c)において、参照符号3は、はんだペースト81(82)に含まれていた本発明に係るフラックスを示し、端部電極41、42の外側でフィレット状になる。

【0042】

比較例2

比較のため、従来のロジン系フラックスを含むはんだペーストを用い、チップ部品を部品搭載基板にはんだ付けした。はんだ粉末に対するロジン系フラックスの配合量は10wt%とした。

【0043】

図5(a)〜(c)は部品搭載基板の詳細と、部品搭載基板に対するチップ部品のはんだ付け工程を示す部分断面図である。図示するように、部品搭載基板1は、Cu膜51(52)、Ni膜61(62)及びAu膜71(72)を順次に積層した2つのランドを有する。この部品搭載基板1のランドの上に、ロジン系フラックスを含有するはんだペースト91(92)を塗布した(図5(a)参照)。

【0044】

そして、ロジン系フラックスを含有するはんだペースト91(92)の上に、長さ1mm、幅0.5mmの電子部品4を搭載(図5(b)参照)し、リフロー炉に通炉することにより、電子部品4を部品搭載基板1上にはんだ付けした(図5(c)参照)。この後、図2に示した方法に従って、部品横押し強度を測定した。

【0045】

図6は実施例2及び比較例2の部品横押し強度試験の結果を示す図である。図示するように、比較例2の横押し強度の平均値は600g程度であったが、実施例2では平均値1500g程度の強度を得ることができた。

【0046】

実施例3

実施例1で調製したフラックスと、はんだ粉末とを混合し、はんだぺ一ストを調製した。はんだ粉末に対するフラックスの配合量は、20〜45wt%まで増やした。

【0047】

このはんだぺ一ストを用い、図7に従って、電子部品4を部品搭載基板1に搭載し、はんだ付けした。図7を参照して具体的に述べると、部品搭載基板1は、Cu膜51(52)、Ni膜61(62)及びAu膜71(72)を順次に積層して形成した2つのランドを有する(図7(a)参照)。

【0048】

上述した部品搭載基板1のランドの上に、本発明に係るはんだペースト81(82)を塗布した(図7(a)参照)。はんだペースト81(82)の塗布に当たっては、厚み100μmのメタルマスクを用いて印刷した。メタルマスクの開口寸法は0.5mm×0.3mmとし、電子部品4の搭載されるランド寸法と同寸法とした。

【0049】

そして、はんだペースト81(82)の上に、長さ1mm、幅0.5mmの電子部品4を搭載(図7(b)参照)し、リフロー炉に通炉することにより、電子部品4を部品搭載基板1上にはんだ付けした(図7(c)参照)。これにより、本発明に係る電子部品装置が得られる。

【0050】

はんだ付け後の外観は、図8に示す通りである。図8は図7(c)の8ー8線に沿った断面図である。実施例3では、意図的にフラックス含有量を増やしたはんだぺ一ストを用いたものであるが、実質、はんだ量が少なくて済み、電子部品4は、図8に示すように、傾斜することなく、正常な状態ではんだ付けされた。図7(c)及び図10において、参照符号3は、はんだペースト81(82)に含まれていた本発明に係るフラックスを示し、端部電極41、42の外側でフィレット状になる。

【0051】

また、本発明に係るフラックスを含有するはんだペーストを用いたことにより、はんだ付け後の電子部品4の周辺を、フラックスが覆い、部品横押し強度の向上も認められた。このように、はんだぺ一スト中のフラックス含有率を故意に向上させることにより、はんだ厚みを、はんだぺ一ストによって制御も可能となる。特に、フラックスの含有量が35wt%以上の領域で、斜めはんだ付けを回避し、かつ、従来品と同等以上の接合強度を得ることができた。

【0052】

比較例3

比較のために、従来のロジン系フラックス含有のはんだペーストを用い、図9に従って、電子部品4を部品搭載基板1に搭載し、はんだ付けした。図9を参照して具体的に述べると、部品搭載基板1は、Cu膜51(52)、Ni膜61(62)及びAu膜71(72)を順次に積層して形成した2つのランドを有する(図9(a)参照)。

【0053】

上述した部品搭載基板1のランドの上に、ロジン系フラックス含有のはんだペースト91(92)を塗布した(図9(a)参照)。はんだペースト91(92)の塗布に当たっては、厚み100μmのメタルマスクを用いて印刷した。メタルマスクの開口寸法は0.5mm×0.3mmとし、電子部品4の搭載されるランド寸法と同寸法とした。

【0054】

そして、はんだペースト91(92)の上に、長さ1mm、幅0.5mmの電子部品4を搭載(図9(b)参照)し、リフロー炉に通炉することにより、電子部品4を部品搭載基板1上にはんだ付けした(図9(c)参照)。

【0055】

リフローはんだ付け後の外観は、図10に示す通りである。図10は図9(c)の10ー10線に沿った部分断面図である。図10に示すように、従来のロジン系フラックス含有はんだぺ一ストではんだ付けしたものは、はんだ量が多すぎ、電子部品4が斜めにはんだ付けされた。図9(c)及び図10において、参照符号93は、はんだペースト91(92)に含まれていたロジン系フラックスを示す。

【0056】

実施例4

フラックスの配合組成について検討した。接着性樹脂として、液状エポキシ樹脂を用い、硬化剤としてアビエチン酸(カルボン酸)を用いた。液状エポキシ樹脂に対し、アビエチン酸を、表1に示す重量比で配合した。このフラックスを基板上に塗布し、230℃のリフロー炉に通炉し、樹脂硬化膜について検証した。

【0057】

表1に示すように、液状エポキシ樹脂1wt%に対し、アビエチン酸1wt%の配合比のとき、硬い硬化膜となり、最も良好な結果が得られる。その他の配合比では、硬化しなかったり、ゲル状になったり、あるいは弾性硬化膜になったりするので、適当でない。リフロー温度に対しては、エポキシ樹脂の配合比、或いは、エポキシ樹脂の分子量、官能基数を変え、硬化剤(カルボン酸)の種類を検討すれば、任意の温度で、所望の硬化膜(接着性)を得ることができる。

【0058】

実施例5

実施例4で調製したフラックスと、はんだ粉末とを混合し、はんだペーストを調製した。はんだ粉末としては、Sn(96.5)Ag(3.5)を用いた。フラックスの含有量は25wt%とした。これを実施例5とする。

【0059】

図11は実施例5のはんだペーストを用いてチップ部品をはんだ付けした場合、及び、従来のロジン系はんだペーストを用いてチップ部品をはんだ付けした場合について、リフロー温度と部品横押し強度との関係を示す図である。図において、曲線L1は実施例5のはんだペーストを用いた場合の特性、曲線L2は従来のロジン系はんだペーストを用いた場合の特性である。

【0060】

図11に示すように、フラックスを含有するはんだぺ一ストは、220〜260℃のリフロー温度範囲において、従来のロジン系はんだペーストよりも高い接合強度を示す。特に、リフロー温度230℃以上で高い接合強度を確保することができた。

【0061】

実施例6

実施例5に示したはんだペーストを用いて、チップ部品を部品搭載基板にはんだ付けし、本発明に係る電子部品装置を得た。この後、部品搭載基板とチップ部品の端子極の接合性について観察したところ、フラックスを含有するはんだペーストは、ロジン系はんだペーストと同様の接合性を有していた。因に、従来の導電性接着剤や異方性導電ぺ一ストを上記フラックスと同様に評価した場合、部品搭載基板と部品の端子との接合は得られなかった。

【0062】

上記実施例では、部品搭載基板1の一面に電子部品4を搭載する例を示したが、部品搭載基板1の両面に電子部品4を搭載することができる。この場合、部品搭載基板1の一面上に、本発明に係るはんだペーストによるはんだ付け処理を実行した後、部品搭載基板1の他面上で、本発明に係るはんだペーストとは異なるはんだ、例えば、従来のロジン系はんだペーストを用いて、電子部品4をはんだ付けすることができる。これとは異なって、部品搭載基板1の両面側において、本発明に係るはんだペーストを用いて、電子部品4をはんだ付けすることもできる。何れの場合も、電子部品4がシフティング、マンハッタン現象(部品立ち現象)または脱落等の不具合を起こすことはない。

【0063】

<電子回路モジュール>

本発明に係る電子回路モジュールは、既に述べた電子部品装置との対比において、電子部品が、半導体チップに置き換わる点、及び、部品搭載基板がチップ搭載基板に置き換わる点を除けば、本質的に異なる点はない。換言すれば、本発明に係る電子回路モジュールの基本構成は、実質的に、電子部品装置に開示されている。用いられる半導体チップには、特に限定はない。半導体チップには、一般には、半導体素子(図示しない)または受動回路素子が含まれる。チップサイズパッケージ(CSP)と称される電子回路モジュールも、当然用いることができる。

【0064】

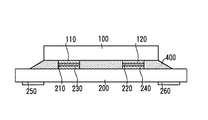

図12は本発明に係る電子回路モジュールの正面部分断面図である。図示された電子回路モジュールは、半導体チップ100と、チップ搭載基板200と、はんだ付け用フラックス400とを含む。図示された半導体チップ100は、下面等の適当な位置に、適当数の端子電極110、120が形成してあって、この端子電極110、120を、はんだ210、220によって、チップ搭載基板200の上のランド230、240に接合してある。

【0065】

チップ搭載基板200は、セラミック基板、有機樹脂基板またはそれらの組み合わせによって構成することができる。チップ搭載基板200の内部には、一般に、単層または複数層の導体パターン、及び、厚み方向に設けられたビヤホール等が形成されている。導体パターンは、単に、回路引き回しのために備えられる他、キャパシタまたはインダクタ等を構成するために備えられることもある。

【0066】

はんだ付け用フラックス400は、接着性樹脂と、硬化剤とを含有し、半導体チップ100と、チップ搭載基板200との間に介在し、両者を接着している。はんだ付け用フラックス400は接着剤として機能する。

【0067】

図示実施例において、はんだ付け用フラックス400は、半導体チップ100とチップ搭載基板200との間の隙間を、ほぼ埋めるように充填されている。

【0068】

既に述べたように、はんだ付け用フラックス400は洗浄する必要がなく、そのまま接着剤として用いることができる。従って、フラックス洗浄工程を必要とせず、製造コストの安価な電子回路モジュールを得ることができる。しかも、はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子回路モジュールを得ることができる。

【0069】

図13は図12に示したCSP(チップサイズパッケ−ジ)等の電子回路モジュールのはんだ付け方法を説明する図である。このはんだ付け方法は、図1に示したはんだ付け方法を、電子回路モジュールのはんだ付けに適用したものに相当する。既に述べたように、接着性樹脂と、硬化剤とを含有するフラックス400を、予め、はんだバンプ210、220を形成したチップ搭載基板200の上に塗布する。はんだバンプ210、220はチップ搭載基板200の表面に設けられたランド230、240の上に形成されている。フラックス400の詳細は、既に述べた通りである。

【0070】

そして、このチップ搭載基板200の上に半導体チップ100を搭載する。半導体チップ100は、端子電極110、120がはんだバンプ210、220上に位置するようにして、チップ搭載基板200上に配置する。その後、半導体チップ100を搭載したチップ搭載基板200を、リフロー炉に通炉し、半導体チップ100の基体40の両端に設けられた端子電極110、120をはんだバンプ210、220にはんだ接合する。これにより、図12に示した電子回路モジュールが得られる。

【0071】

図14は本発明に係る電子回路モジュールの別の例を示す正面部分断面図である。図において、図12に図示された構成部分と同一の構成部分には、同一の参照符号を付してある。図示実施例において、はんだ付け用フラックス400は、半導体チップ100とチップ搭載基板200との間に介在し、はんだバンプ210、220の周りで、両者を接着している。

【0072】

この場合も、はんだ付け用フラックス400は洗浄する必要がなく、そのまま接着剤として用いることができる。従って、フラックス洗浄工程を必要とせず、製造コストの安価な電子回路モジュールを得ることができる。しかも、はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子回路モジュールを得ることができる。

【0073】

図15は図14に示した電子回路モジュールのはんだ付け方法を説明する図である。このはんだ付け方法は、図4〜8に示したはんだ付け方法を、電子回路モジュールのはんだ付けに適用したものに相当する。既に述べた組成のはんだ粉末含有フラックス410、420を、予め、チップ搭載基板200の表面に設けられたランド230、240の上に塗布する。

【0074】

そして、このチップ搭載基板200の上に半導体チップ100を搭載する。半導体チップ100は、端子電極110、120がはんだ粉末含有フラックス410、420上に位置するようにして、チップ搭載基板200上に配置する。半導体チップ100を搭載したチップ搭載基板200を、リフロー炉に通炉し、半導体チップ100の両端に設けられた端子電極110、120をはんだ粉末含有フラックス410、420に含まれるはんだ成分によりはんだ接合する。

【0075】

接合状態では、はんだ粉末含有フラックス410、420に含まれる接着性樹脂及び硬化剤が、半導体チップ100とチップ搭載基板200との間に介在し、はんだバンプ210、220の周りで、両者を接着する。これにより、図14に示した電子回路モジュールが得られる。図15において、はんだ粉末含有フラックス410、420の量を増加させることにより、図12に図示したように、はんだ付け用フラックス400が、半導体チップ100とチップ搭載基板200との間の隙間を、ほぼ埋めるように充填した構造を実現することもできる。

【0076】

次に具体的な実施例及び比較例を挙げて説明する。

【0077】

実施例7

まず、次の組成になる熱硬化性フラックス入りのはんだぺ一ストを調製した。

【0078】

フラックス:ビスフエノールA樹脂/無水フタル酸を質量比1対1で混合し、溶剤を10質量%添加したもの

はんだ粉末:Sn−3.5Ag

上記はんだ粉末に対し、上記フラックスを、10質量%の割合で添加した。はんだ粉末の組成はリフロー温度に応じて選択できるもので、他の組成系でもよい。また、フラックスの配合量も任意に選択できる。

【0079】

上述した熱硬化性フラックス入りのはんだぺ一ストを、スクリーン印刷法により、有機系チップ搭載基板上に塗布した。スクリーン印刷に当たっては、メタルマスタ厚み100μmのスクリーンを用いた。

【0080】

次に、予め、はんだバンプが形成されている半導体チップを有機系チップ搭載基板上に載せ、リフロー炉に通炉した。リフロー温度は、最高温度240℃とし、220℃以上の通炉時間を30秒とした。

【0081】

比較例7

比較のため、封止剤を用いた従来品、および、封止剤を用いない従来品を用意した。

【0082】

<試験>

実施例7に係る電子回路モジュール、及び、2種の従来電子回路モジュールを熱衝撃試験に付した。熱衝撃試験は、(一55℃)を0.5時間保持し、次に(+125℃)を0.5時間保持し、これを1サイクルとし、2000サイクルまで行った。その後に、はんだ接続部分における直流抵抗(RDC)を測定した。

【0083】

図16はRDC測定結果を示すグラフである。図16において、横軸に熱衝撃サイクル(サイクル)を採り、縦軸にRDC(Ω)を採ってある。特性L11は封止剤を用いない従来品の特性、特性L12は封止剤を用いた従来品の特性、特性L13は本発明に係る実施例7の特性である。

【0084】

図16において、封止剤を用いなかった従来品は、特性L11で示されているように、1500サイクルを越えると、RDCが急激に増大しており、RDCが劣化している。これに対して、本発明に係る実施例7は、特性L13で示されるように、2000サイクルを経過してもRDCの劣化は見られなかった。これは、封止剤を用いた従来品の特性L12と同等の特性である。

【0085】

<電子回路装置>

本発明係る電子回路装置は、既に述べた電子部品装置との対比において、電子部品が、電子回路モジュールに置き換わる点、及び、部品搭載基板がマザー基板に置き換わる点を除けば、本質的に異なる点はない。換言すれば、本発明に係る電子回路装置の基本構成は、実質的に、電子部品装置に開示されている。

【0086】

図17は本発明に係る電子回路装置の正面部分断面図である。図示された電子回路装置は、電子回路モジュール300と、マザー基板500と、はんだ付け用フラックス600とを含む。

【0087】

電子回路モジュール300は、従来タイプの電子回路モジュールを用いることもできるが、好ましくは、図12、14に示した構造のものを用いる。電子回路モジュール300は、下面等の適当な位置に、適当数の端子電極250、260が形成してあって、この端子電極250、260を、はんだバンプ510、520によって、マザー基板500の上のランド530、540に接合してある。

【0088】

マザー基板200は、セラミック基板、有機樹脂基板またはそれらの組み合わせによって構成することができる。マザー基板500の内部には、単層または複数層の導体パターン、及び、厚み方向に設けられたビヤホール等が形成されることがある。導体パターンは、単に、回路引き回しのために備えられる他、キャパシタまたはインダクタ等を構成するために備えられることもある。

【0089】

はんだ付け用フラックス600は、接着性樹脂と、硬化剤とを含有し、電子回路モジュール300と、マザー基板500との間に介在し、両者を接着している。はんだ付け用フラックス600は、接着剤として機能する。図示実施例において、はんだ付け用フラックス600は、電子回路モジュール300とマザー基板500との間の隙間を、ほぼ埋めるように充填されている。

【0090】

はんだ付け用フラックス600は洗浄する必要がなく、そのまま接着剤として用いることができる。従って、フラックス洗浄工程を必要とせず、製造コストの安価な電子回路装置を得ることができる。しかも、はんだ付け用フラックスは、接着性樹脂と、硬化剤とを含有しており、接着剤として機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子回路装置を得ることができる。

【0091】

図18は図17に示した電子回路装置のはんだ付け方法を説明する図である。このはんだ付け方法は、図1に示したはんだ付け方法を、電子回路装置のはんだ付けに適用したものに相当する。既に述べたように、接着性樹脂と、硬化剤とを含有するフラックス600を、予め、はんだバンプ510、520を形成したマザー基板500の上に塗布する。フラックス600ははんだ粉末を含有しない。

【0092】

はんだバンプ510、520はマザー基板500の表面に設けられたランド530、540の上に形成されている。そして、このマザー基板500の上に電子回路モジュール300を搭載する。電子回路モジュール300は、端子電極250、260がはんだバンプ510、520上に位置するようにして、マザー基板500上に配置する。電子回路モジュール300を搭載したマザー基板500を、リフロー炉に通炉し、電子回路モジュール300の端子電極250、260をはんだバンプ510、520にはんだ接合する。これにより、図17に示した電子回路装置が得られる。

【0093】

図19は本発明に係る電子回路装置の別の例を示す正面部分断面図である。図において、図17に図示された構成部分と同一の構成部分には、同一の参照符号を付してある。図示実施例において、はんだ付け用フラックス600は、電子回路モジュール300とマザー基板500との間に介在し、はんだバンプ510、520の周りで、両者を接着している。

【0094】

この場合も、はんだ付け用フラックス600は洗浄する必要がなく、そのまま接着剤として用いることができる。従って、フラックス洗浄工程を必要とせず、製造コストの安価な電子回路装置を得ることができる。しかも、はんだ付け用フラックス600は、はんだ粉末を含む他、接着性樹脂と、硬化剤とを含有しており、接着剤として機能するから、はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子回路装置を得ることができる。

【0095】

図20は図19に示した電子回路装置のはんだ付け方法を説明する図である。このはんだ付け方法は、図4〜8に示したはんだ付け方法を、電子回路装置のはんだ付けに適用したものに相当する。既に述べた組成にて調製したはんだ粉末含有フラックス610、620を、予め、マザー基板500の表面に設けられたランド530、540の上に塗布する。そして、このマザー基板500の上に電子回路モジュール300を搭載する。電子回路モジュール300は、端子電極250、260がはんだ粉末含有フラックス610、620上に位置するようにして、マザー基板500上に配置する。

【0096】

次に、電子回路モジュール300を搭載したマザー基板500を、リフロー炉に通炉し、電子回路モジュール300に設けられた端子電極250、260をはんだ粉末含有フラックス610、620に含まれるはんだ成分によりはんだ接合する。はんだ粉末含有フラックス610、620に含まれる接着性樹脂及び硬化剤が、電子回路モジュール300とマザー基板500との間に介在し、はんだバンプ510、520の周りで、両者を接着する。これにより、図19に示した電子回路装置が得られる。図20において、はんだ粉末含有フラックス610、620の量を増加させることにより、図17に図示したように、はんだ付け用フラックス600が、電子回路モジュール300とマザー基板500との間の隙間を、ほぼ埋めるように充填した構造を実現することもできる。

【0097】

次に具体的な実施例を挙げて説明する。

【0098】

実施例8

まず、次の組成になる熱硬化性フラックス入りのはんだぺ一ストを調製した。

【0099】

フラックス:ビスフエノールA樹脂/無水フタル酸を質量比1対1で混合し、溶剤を10質量%添加したもの

はんだ粉末:Sn−3.5Ag

上記はんだ粉末に対し、上記フラックスを、10質量%の割合で添加した。はんだ粉末の組成はリフロー温度に応じて選択できるもので、他の組成系でもよい。また、フラックスの配合量も任意に選択できる。

【0100】

マザー基板としては、有機系マザー基板を用いた。電子回路モジュールは、有機系のチップ搭載基板を用い、その上に半導体チップを搭載したものを用いた。有機系チップ搭載基板の下面に備えられた端子電極の表面には、有機系マザー基板とはんだ付けが可能なように、Auめっき処理を施した。

【0101】

上述した熱硬化性フラックス入りのはんだぺ一ストを、スクリーン印刷法により、有機系チップ搭載基板上に塗布した。スクリーン印刷に当たっては、メタルマスタ厚み100μmのスクリーンを用いた。

【0102】

次に、電子回路モジュールを、有機系マザー基板上に載せ、リフロー炉に通炉した。リフロー温度は、最高温度240℃とし、220℃以上の通炉時間を30秒とした。

【0103】

実施例9

電子回路モジュールのチップ搭載基板を、セラミック基板とした他は、実施例8と同様にして、電子回路装置を製造した。

【0104】

比較例8

電子回路モジュールのチップ搭載基板を有機系材料によって構成し、この電子回路モジュールを、従来のフラックスを用いて、有機系マザー基板にはんだ付けした。有機系チップ搭載基板の下面に備えられた端子電極の表面には、有機系マザー基板とはんだ付けが可能なように、Auめっき処理を施した。

【0105】

比較例9

電子回路モジュールのチップ搭載基板をセラミック材料によって構成し、この電子回路モジュールを、従来のフラックスを用いて、有機系マザー基板にはんだ付けした。セラミック系チップ搭載基板の下面に備えられた端子電極の表面には、有機系マザー基板とはんだ付けが可能なように、Auめっき処理を施した。

【0106】

<試験>

実施例8、9に係る電子回路モジュール、及び、比較例8、9に係る従来電子回路モジュールを熱衝撃試験に付した。熱衝撃試験は、(一55℃)を0.5時間保持し、次に(+125℃)を0.5時間保持し、これを1サイクルとし、2000サイクルまで行った。その後に、はんだ接続部分における直流抵抗(RDC)を測定した。

【0107】

図21はRDC測定結果を示すグラフである。図21において、横軸に熱衝撃サイクル(サイクル)を採り、縦軸にRDC(Ω)を採ってある。特性L21は比較例9の特性、特性L22は実施例8、9及び比較例8の特性である。

【0108】

図21において、電子回路モジュールのチップ搭載基板がセラミック材料でなり、マザー基板が有機材料でなる比較例9は、特性L21で示されているように、1000サイクルを越えると、RDCが急激に増大し、RDCが劣化する。これに対して、本発明に係る実施例8、9は、特性L22で示されるように、2000サイクルを経過してもRDCの劣化は見られなかった。特に、実施例9の特性L22と、比較例9の特性L21との対比から明らかなように、電子回路モジュールのチップ搭載基板を、セラミック基板とし、マザー基板を有機樹脂基板とした場合、従来は著しいRDCの劣化を招いていた(特性L21参照)が、本発明によれば、このような基板の組み合わせにおいても、RDCの劣化を阻止できる(特性L22参照)という優れた効果が得られる。

【0109】

上述したように、本発明では、フラックスに含まれる接着性樹脂を利用して、電子部品を部品搭載基板に接着する。この後、電子部品と部品搭載基板とが接着された状態で、はんだ付けの状態を検査する検査工程に付される。はんだ付け不良の場合、部品搭載基板から電子部品を取り外し、その電子部品を、再度、部品搭載基板にはんだ付けしたい。もし、部品搭載基板から電子部品を取り外すことができないならば、電子部品及び部品搭載基板は、廃棄することになり、コストの増大または歩留まりの低下を招く。そこで、本発明のフラックス及びはんだペーストは、はんだ付けの後で部品搭載基板から電子部品を取り外すことのできるものであることが好ましい。

【0110】

また、最近、地球環境保全の立場から、Pbを含有しないはんだ(Pbフリーはんだ)が導入されつつあり、様々な組成のはんだ成分が利用されるようになっている。はんだ成分は、その組成により、融点が異なるので、利用するはんだ成分の組成に応じて、様々な値のリフロー温度を設定しなければならない。このため、設定される任意のリフロー温度に応じて接着性樹脂を硬化できる技術が必要である。

【0111】

ここでは、電子部品を、部品搭載基板にはんだ付けする場合を例にとって説明したが、半導体チップをチップ搭載基板にはんだ付けする場合、及び、電子回路モジュールをマザー基板にはんだ付けする場合も同様である。

【0112】

次に、上述した問題点を解決するフラックス及びはんだペーストの構成を開示する。まず、フラックスにおいて、硬化剤は、少なくとも2種のカルボン酸を含み、これらのカルボン酸は、互いに異なる融点を有する。融点の低いカルボン酸は、リフロー温度で硬化剤として機能する。また、融点の高いカルボン酸は、リフロー温度より高いリペア温度で接着性樹脂の粘度を低下させる。

【0113】

フラックスの温度を、リペア温度前後に上昇させると、融点の高いカルボン酸も溶融し、接着性樹脂の粘度が低下するので、部品搭載基板から電子部品を取り外すことができる。従って、接着機能を保持しながら、従来のロジンフラックスと同様に電子部品をリペアすることができる。このような組成の接着性フラックスは、電子回路モジュール等の高価な大型パッケージ品をはんだ付けする場合、特に有益である。

【0114】

しかも、互いに融点の異なるカルボン酸を混合することにより、接着性樹脂の熱硬化温度を変えることができる。従って、任意のリフロー温度で接着性樹脂を硬化できるようになり、利用するはんだ成分の融点に合わせてリフロー温度を変更できるようになる。

【0115】

更に、混合するカルボン酸の組み合わせまたは混合比を変更することによっても、接着性樹脂の熱硬化温度を変えることができ、同様な作用及び効果が得られる。

【0116】

次に、はんだペーストは、上述の構成のフラックスと、はんだ粉末とを含む。従って、このはんだペーストも、上述の構成のフラックスと同様な作用及び効果を得られる。

【0117】

上述した作用及び効果を、実験を参照して具体的に説明する。まず、リペア性に優れたフラックス及びはんだペーストを得るため、次のような実験1を行った。

【0118】

実験1:複数種のカルボン酸の組み合わせによるリペア性の獲得

熱硬化性樹脂としてビスフェノールAを用いた。硬化剤としては、2種類のカルボン酸、具体的には、アジピン酸とピメリット酸とを用いた。アジピン酸及びピメリット酸はカルボン酸の範疇に含まれる。アジピン酸とピメリット酸とは、融点が互いに異なる。具体的には、アジピン酸の融点は153℃、ピメリット酸の融点は279℃である。ビスフェノールAとアジピン酸とピメリット酸とを、下記の表2に示す配合比(質量%)で配合し、サンプル1〜4のフラックスを調製した。サンプル1〜4のフラックスは、アジピン酸の含有率をa(質量%)とし、ピメリット酸の含有率をb(質量%)としたとき、

a:b=(50:50)〜(95:5)(但しa+b=100)

の範囲で変化させてある。また、ビスフェノールAとアジピン酸とを、下記の表2に示す配合比(質量%)で配合し、サンプル5のフラックスを調製した。

【0119】

次に、調製した各サンプル1〜5のフラックスに、はんだ粉末を混合し、はんだペーストを調製した。はんだ粉末としてはSn−3.5Agを用いた。はんだ粉末の組成はリフロー温度に応じて選択できるもので、他の組成系でもよい。また、はんだ粉末に対するフラックスの配合量は25質量%とした。フラックスの配合量も任意に選択できる。

【0120】

上記組成において製作したはんだぺ一ストを用いて、マザー基板上に電子回路モジュールをはんだ付けした。図22〜図25は、マザー基板に対する電子回路モジュールのはんだ付け工程を示す正面部分断面図である。図において、図19に図示された構成部分と同一の構成部分には、同一の参照符号を付してある。

【0121】

図22に示すように、マザー基板500の表面には、ランド530、540が設けられている。マザー基板500は、セラミック基板、有機樹脂基板またはそれらの組み合わせによって構成することができる。図示のマザー基板500は、有機樹脂基板でなる。

【0122】

図23に示すように、マザー基板500のランド530、540の上に、実施例10のはんだペースト610、620を塗布した。はんだペースト610、620の塗布に当たっては、メタルマスクを用いて印刷した。

【0123】

そして、図24に示すように、マザー基板500の上に電子回路モジュール300を搭載した。図示の電子回路モジュール300は、図12に図示された電子回路モジュールと同様な構成である。電子回路モジュール300は、LGA構造品と称されるCSP(チップサイズパッケージ)の電子回路モジュールである。電子回路モジュール300のチップ搭載基板200はセラミック基板でなる。図24に示すように、電子回路モジュール300は、端子電極250、260がはんだペースト610、620上に位置するようにして、マザー基板500上に配置した。

【0124】

次に、電子回路モジュール300を搭載したマザー基板500を、リフロー炉に通炉し、電子回路モジュール300に設けられた端子電極250、260をはんだペースト610、620に含まれるはんだ成分によりはんだ接合した。はんだペースト610、620に含まれる接着性樹脂及び硬化剤が、電子回路モジュール300とマザー基板500との間に介在し、はんだバンプ510、520の周りで、両者を接着する。これにより、図25に示すように、本発明に係る電子回路装置が得られる。図25において、参照符号600は、はんだペースト610(620)に含まれていた実施例10のフラックスを示し、端子電極250、260の外側でフィレット状になる。

【0125】

上述したように、フラックス600は、接着性樹脂と、硬化剤とを含んでいる。硬化剤は、アジピン酸と、ピメリット酸とを含み、アジピン酸と、ピメリット酸は、互いに異なる融点を有する。融点の低いアジピン酸は、リフロー温度で硬化剤として機能する。融点の高いピメリット酸は、リフロー温度より高いリペア温度で接着性樹脂の粘度を低下させる。

【0126】

以下、具体的に、サンプル1〜5のフラックスについて述べる。サンプル5のフラックスを用いた場合、リフロー炉に通炉することにより、フラックスに含まれるアジピン酸が溶融し、はんだが溶融した。この結果、マザー基板のランドと、電子回路モジュールの端子電極とが接合された。

【0127】

サンプル1、2のフラックスを用いた場合、リフロー炉に通炉しても、フラックスに含まれるピメリット酸の硬化が進行し、はんだが溶融しなかった。このため、マザー基板のランドと電子回路モジュールの端子電極とが接合されなかった。

【0128】

サンプル3、4のフラックスを用いた場合、リフロー炉に通炉することにより、フラックス600に含まれるアジピン酸が溶融し、はんだが溶融した。この結果、マザー基板500のランド530、540と、電子回路モジュール300の端子電極250、260とが接合された。

【0129】

図26、図27は、マザー基板から電子回路モジュールを取り外す工程を示す正面部分断面図である。図26に示すようにフラックス600に熱風を吹き込み、フラックス600の温度を、リペア温度前後に上昇させると、融点の高いピメリット酸が溶融し、接着性樹脂の粘度が低下する。このため、図27に示すように、マザー基板500から電子回路モジュール300を取り外すことができる。

【0130】

従って、接着機能を保持しながら、従来のロジンフラックスと同様に電子回路モジュール300をリペアすることができる。かような組成の接着性フラックスは、大型パッケージ等の高価な電子回路モジュール300をはんだ付けする場合、特に有効である。また、この接着性フラックスのリペア工法は、従来はんだ付けのリペア工法と同じ作業レベルで実行できる。

【0131】

以下、具体的に述べる。サンプル1〜5のフラックスのうち、リフロー実装できたサンプル3〜5のフラックスに対してリペア実験を行った。リペア実験では、電子回路モジュール300のチップ搭載基板200と、マザー基板500との接合部に300℃前後の熱風を吹き込んだ。

【0132】

サンプル5のフラックスは、電子回路モジュールのチップ搭載基板と、マザー基板とを接着しており、一度軟化したが、熱風により再び硬化した。このため、マザー基板から電子回路モジュールを引き剥がすことはできなかった。

【0133】

サンプル3、4のフラックス600を用いた場合、電子回路モジュール300のチップ搭載基板200と、マザー基板500との接合部に熱風を吹き込むと、フラックス600に含まれるピメリット酸が再溶融し、マザー基板500から電子回路モジュール300を引き剥がすことができた。

【0134】

よって、はんだ付けされた電子回路モジュール300をリペアするためには、接着性樹脂硬化用のアジピン酸の他に、リペア温度付近に融点を有するピメリット酸を混合しておけばよい。リペア温度で、そのピメリット酸を溶融させると、接着性樹脂の粘度が低下する。このため、マザー基板500上にはんだ付けされた電子回路モジュール300を、マザー基板500から取り外し、リペアすることができる。

【0135】

上述した実験1の結果によれば、好ましくは、接着性樹脂硬化用のアジピン酸に、リペア用のピメリット酸を15質量%〜5質量%添加すればよい。言い換えれば、アジピン酸の含有率a(質量%)と、ピメリット酸の含有率b(質量%)とについて、

a:b=(85:15)〜(95:5)(但しa+b=100)

を満たせばよい。

【0136】

実験1で調製したフラックスは、はんだ粉末と混合され、混合により得られたはんだペーストを用いてはんだ付けを行っている。これと異なり、はんだバンプを施した基板上に実験1のフラックスを塗布してはんだ付けを行っても、同様な作用及び効果が得られる。

【0137】

本発明に係る電子部品装置は、既に述べた電子回路装置との対比において、電子回路モジュールが、電子部品に置き換わる点、及び、マザー基板が部品搭載基板に置き換わる点を除けば、本質的に異なる点はない。換言すれば、本発明に係る電子部品装置の基本構成は、実質的に、電子回路装置に開示されている。

【0138】

同様に、本発明に係る電子回路モジュールは、既に述べた電子回路装置との対比において、電子回路モジュールが、半導体チップに置き換わる点、及び、マザー基板がチップ搭載基板に置き換わる点を除けば、本質的に異なる点はない。換言すれば、本発明に係る電子回路モジュールの基本構成は、実質的に、電子回路装置に開示されている。

【0139】

次に、リフロー温度を変更するため、次のような実験2〜5を行った。まず、実験2では、硬化剤として一種のカルボン酸のみを配合してフラックスを調製し、フラックスの熱硬化物性を調べた。

【0140】

実験2:一種のカルボン酸のみを配合したフラックスの熱硬化物性

熱硬化性樹脂としてビスフェノールAを用いた。硬化剤としては、下記の表3に示すように、アジピン酸、マレイン酸、コハク酸またはピメリット酸の1つを用いた。熱硬化性樹脂と、上述の硬化剤とを質量比1:1の割合で配合し、フラックスを調製した。そして、調製したフラックスを2g、Cu板上に塗布し、240℃のリフロー炉に通炉し、皮膜の挙動を比較した。

【0141】

表3に示すように、サンプル11、12のフラックスでは、皮膜が、ゲル化したり、常温で硬化したりするので適当でない。これらに対し、サンプル13、14のフラックスでは、皮膜がリフロー通炉により硬化し、良好な結果が得られた。

【0142】

サンプル11〜14のフラックスにおいて、硬化の進み具合を比較する。硬化剤の融点が高いと熱硬化が進み、アジピン酸を硬化剤としたフラックス(サンプル11)の硬化が最も遅い。硬化剤としてアジピン酸とコハク酸を混合した場合、コハク酸の配合比を増やすにつれ、より硬い硬化皮膜が得られる。

【0143】

上述の実験2を踏まえ、アジピン酸とコハク酸とを混合してリフロー温度の変更を試みた。

【0144】

実験3:複数種のカルボン酸の混合によるリフロー温度の変更

熱硬化性樹脂としてビスフェノールAを用いた。硬化剤としては、2種類のカルボン酸、具体的には、アジピン酸とコハク酸とを用いた。アジピン酸及びコハク酸はカルボン酸の範疇に含まれる。アジピン酸とコハク酸とは、融点が互いに異なる。具体的には、アジピン酸の融点は153℃、コハク酸の融点は188℃である。ビスフェノールAとアジピン酸とコハク酸とを、質量比1:0.5:0.5の割合で配合し、フラックスを調製した。

【0145】

次に、調製したフラックスと、はんだ粉末とを混合し、はんだペーストを調製した。はんだ粉末としてはSn−3.5Agを用い、はんだ粉末に対するフラックスの配合量は15質量%とした。以下、このはんだペーストを、サンプル22のはんだペーストと呼ぶ。はんだ粉末の組成はリフロー温度に応じて選択できるもので、他の組成系でもよい。フラックスの配合量も任意に選択できる。

【0146】

また、ビスフェノールAとアジピン酸とを、質量比1:1の割合で配合し、フラックスを調製した。そして、調製したフラックスと、はんだ粉末とを混合し、はんだペーストを調製した。サンプル22のはんだペーストと同様に、はんだ粉末としてはSn−3.5Agを用い、はんだ粉末に対するフラックスの配合量は15質量%とした。以下、このはんだペーストを、サンプル21のはんだペーストと呼ぶ。

【0147】

図28は、サンプル21、22のはんだペーストを用いてコンデンサをはんだ付けした場合について、リフロー温度と部品横押し強度との関係を示す図である。試験用のコンデンサとして、1005サイズのSTD端子コンデンサと、1005サイズのCSB端子コンデンサとの2種類を用いた。STD端子コンデンサとは、コンデンサ素体の両側面に端子を形成したコンデンサである。CSB端子コンデンサとは、コンデンサ素体の底面の両端に端子を形成したコンデンサである。

【0148】

図28において、特性L31はSTD端子コンデンサにサンプル21のはんだペーストを用いた場合の特性、特性L32はSTD端子コンデンサにサンプル22のはんだペーストを用いた場合の特性、特性L41はCSB端子コンデンサにサンプル21のはんだペーストを用いた場合の特性、特性L42はCSB端子コンデンサにサンプル22のはんだペーストを用いた場合の特性である。部品横押し強度は、前述の図2に示した方法に従って測定した。

【0149】

図28に示すように、STD端子コンデンサをはんだ付けする場合、サンプル22のはんだペースト(特性L32参照)は、サンプル21のはんだペースト(特性L31参照)よりも低いリフロ−温度で同程度の部品横押し強度を得られた。

【0150】

また、CSB端子コンデンサをはんだ付けする場合、サンプル22のはんだペースト(特性L42参照)は、サンプル21のはんだペースト(特性L41参照)よりも低いリフロ−温度で同程度の部品横押し強度を得られた。例えば、部品横押し強度として0.9kg必要であると仮定すると、サンプル21のはんだペースト(特性L41参照)の場合、224〜230℃のリフロ−温度を必要とするが、サンプル22のはんだペースト(特性L42参照)の場合、217〜221℃のリフロ−温度で済む。

【0151】

以上述べたように、互いに融点の異なるカルボン酸(アジピン酸とコハク酸)を混合することにより、接着性樹脂(ビスフェノールA)の熱硬化温度を変えることができる。従って、任意のリフロー温度で接着性樹脂(ビスフェノールA)を硬化できるようになり、利用するはんだ成分の融点に合わせてリフロー温度を変更できるようになる。リフロ−温度は一定の値に固定せずに済むようになる。

【0152】

更に、混合するカルボン酸の組み合わせ(アジピン酸及びコハク酸)を変更することによっても、接着性樹脂(ビスフェノールA)の熱硬化温度を変えることができ、同様な作用及び効果が得られる。例えば、アジピン酸とコハク酸との組み合わせを、アジピン酸とピメリット酸との組み合わせに変更すると、接着性樹脂(ビスフェノールA)の熱硬化温度が変わる。

【0153】

次に、混合するカルボン酸(アジピン酸とコハク酸)の混合比を調整して、リフロー温度の変更を試みた。

【0154】

実験4:カルボン酸の混合比の調整によるリフロー温度の変更

熱硬化性樹脂としてビスフェノールAを用いた。硬化剤としては、アジピン酸とコハク酸とを用いた。ビスフェノールAとアジピン酸とコハク酸とを、下記の表4に示す配合比(質量%)で配合し、フラックスを調製した。これらのフラックスは、アジピン酸の含有率をa(質量%)とし、コハク酸の含有率をc(質量%)としたとき、

a:c=(100:0)〜(0:100)(但しa+c=100)

の範囲で変化させてある。

【0155】

次に、調製した各フラックスにはんだ粉末を混合し、サンプル50〜55のはんだペーストを調製した。はんだ粉末としては、共晶はんだ(Sn63−Pb37)の粉末を用いた。はんだ粉末に対するフラックスの配合量は15質量%とした。はんだ粉末の組成はリフロー温度に応じて選択できるもので、他の組成系でもよい。フラックスの配合量も任意に選択できる。

【0156】

表4に示すように、サンプル50のはんだペーストは、はんだ付けにおいて端子を良好に接続できた。しかし、サンプル50のはんだペーストは、硬化剤としてアジピン酸しか含んでいないので、接着性樹脂(ビスフェノールA)の熱硬化温度を変えることができず、リフロー温度を変更できない。

【0157】

また、サンプル55のはんだペーストは、はんだが溶融する前にフラックスが硬化してしまい、端子を接合できなかった。

【0158】

これに対し、サンプル51〜54のはんだペーストは、それぞれ、はんだ付けにおいて端子を良好に接続できた。

【0159】

図32は、サンプル50〜54のはんだペーストを用いてコンデンサをはんだ付けした場合について、リフロー温度と部品横押し強度との関係を示す図である。試験用のコンデンサとしては、1005サイズのSTD端子コンデンサを用いた。図29において、特性L50〜L54は、それぞれ、サンプル50〜54のはんだペーストを用いた場合の特性である。

【0160】

コハク酸の配合率を増大させることにより、低いリフロー温度でも、必要な部品横押し強度を確保することができる。例えば、部品横押し強度として1.4kg必要であると仮定すると、サンプル52のはんだペースト(特性L52参照)は、230℃のリフロ−温度を必要とする。これに対し、サンプル53のはんだペースト(特性L53参照)は、上述のサンプル52よりもコハク酸の配合率を増大させてあるので、210℃のリフロ−温度で済む。

【0161】

以上述べたように、混合するカルボン酸(アジピン酸とコハク酸)の混合比を変更することにより、接着性樹脂(ビスフェノールA)の熱硬化温度を変えることができる。従って、任意のリフロー温度で接着性樹脂(ビスフェノールA)を硬化できるようになり、利用するはんだ成分の融点に合わせてリフロー温度を変更できるようになる。リフロ−温度は一定の値に固定せずに済むようになる。

【0162】

上述した実験4の結果によれば、はんだ成分として共晶はんだ(Sn63−Pb37)を用いる場合、硬化剤としてアジピン酸及びコハク酸を配合するとき、アジピン酸の含有率a(質量%)と、コハク酸の含有率c(質量%)とについて、

a:c=(95:5)〜(25:75)(但しa+c=100)

を満たすのが好ましい。

【0163】

実験4では、はんだ成分として共晶はんだ(Sn63−Pb37)を用いている。共晶はんだ(Sn63−Pb37)の融点は183℃である。

【0164】

かような実験4と異なり、はんだ成分としてSn−3.5Agはんだを用いた実験(以下実験5と称する)を説明する。Sn−3.5Agはんだの融点は217℃であり、共晶はんだ(Sn63−Pb37)の融点183℃よりもかなり高い。

【0165】

実験5:フラックスと組み合わせられるはんだ成分の変更

ビスフェノールAとアジピン酸とコハク酸とを、下記の表5に示す配合比(質量%)で配合し、フラックスを調製した。これらのフラックスは、アジピン酸の含有率をa(質量%)とし、コハク酸の含有率をc(質量%)としたとき、

a:c=(100:0)〜(0:100)(但しa+c=100)

の範囲で変化させてある。

【0166】

次に、調製した各フラックスにはんだ粉末を混合し、サンプル70〜75のはんだペーストを調製した。はんだ粉末としては、Sn−3.5Agはんだ粉末を用いた。はんだ粉末に対するフラックスの配合量は15質量%とした。

【0167】

表5に示すように、サンプル72〜75のはんだペーストは、それぞれ、はんだが溶融する前にフラックスが硬化してしまい、端子を接合できなかった。

【0168】

また、サンプル70、71のはんだペーストは、それぞれ、はんだ付けにおいて端子を良好に接続できた。

【0169】

上述した実験5の結果によれば、はんだ成分としてSn−3.5Agはんだを用いる場合、硬化剤としてアジピン酸及びコハク酸を配合するとき、アジピン酸の含有率a(質量%)と、コハク酸の含有率c(質量%)とについて、

a:c=(100:0)〜(95:5)(但しa+c=100)

を満たすのが好ましい。

【0170】

上述した実験3〜5では、フラックスを、はんだ粉末に混合し、混合により得られたはんだペーストを用いてはんだ付けを行っている。これと異なり、はんだバンプを施した基板上にフラックスを塗布してはんだ付けを行っても、同様な作用及び効果が得られる。

【0171】

実験3〜5で調製したはんだペーストを利用しても、図25に図示された電子回路装置と同様な電子回路装置を構成できることは自明である。勿論、実験3〜5のはんだペーストを利用して電子部品装置及び電子回路モジュールを構成することもできる。

【0172】

また、硬化剤として、互いに熱硬化速度の異なるカルボン酸を混合すると、接着性樹脂の熱硬化速度を変えることができる。従って、利用するはんだ成分に合わせてリフロー時間またはリフロー温度を変更できるようになる。例えば、アジピン酸とコハク酸の場合、コハク酸の熱硬化に必要な熱量は、アジピン酸の熱硬化に必要な熱量よりも少ないので、コハク酸の熱硬化速度は、アジピン酸の熱硬化速度よりも速い。従って、硬化剤としてアジピン酸とコハク酸とを混合すると、接着性樹脂(ビスフェノールA)の熱硬化速度を変更でき、リフロー時間またはリフロー温度を変更できる。他のカルボン酸の組み合わせ、例えば、アジピン酸とピメリット酸の場合も同様である。

【0173】

更に、混合するカルボン酸の組み合わせまたは混合比を変更することによっても、接着性樹脂の熱硬化速度を変えることができ、同様な作用及び効果が得られる。

【0174】

図示は省略するが、本発明に係るはんだペーストを用いる場合、本発明に係るフラックスを封止剤として用い、電子部品と部品搭載基板、半導体チップとチップ搭載基板及び電子回路モジュールとマザー基板とを、フラックスでなる封止剤によって接合することもできる。また、本発明に係るフラックスを用いた部品搭載基板において、本フラックスの上層部に一般的な封止剤を形成することもできる。

【0175】

【発明の効果】

以上述べたように、本発明によれば、次のような効果が得られる。

(a)実装の高密度化、部品の小型化及び部品の配置間隔の狭ピッチ化等に対しても、十分な接合強度をもって対応し得るはんだ付け用フラックス及びはんだペースト及びはんだ付け方法を提供することができる。

(b)両面実装タイプの部品搭載基板において、部品の浮動または脱落等の不具合を確実に阻止し得るはんだ付け用フラックス及びはんだペースト及びはんだ付け方法を提供することができる。

(c)フラックス洗浄工程を必要とせず、製造コストの安価な電子部品装置、電子回路モジュール及び電子回路装置を提供することができる。

(d)はんだ接合寿命を、従来よりも著しく長期化させた高信頼度の電子部品装置、電子回路モジュール及び電子回路装置を提供することができる。

【図面の簡単な説明】

【図1】本発明に係るフラックスを用いたチップ部品のはんだ付け方法を示す部分断面図である。

【図2】部品搭載基板にはんだ付けされたチップ部品の横押し強度試験方法を示す部分断面図である。

【図3】図2に示した部品横押し強度試験による結果を示す図である。

【図4】本発明に係るフラックスを含有するはんだペーストを用いた場合について、部品搭載基板の詳細と、部品搭載基板に対するチップ部品のはんだ付け工程を示す部分断面図である。

【図5】従来のロジン系フラックスを含有するはんだペーストを用いた場合について、部品搭載基板の詳細と、部品搭載基板に対するチップ部品のはんだ付け工程を示す部分断面図である。

【図6】図4に示す本発明に係るはんだ付け方法と、図5に示す従来のはんだ付け方法とについて、部品横押し強度試験の結果を示す図である。

【図7】本発明に係るフラックスを含有するはんだペーストを用いたはんだ付け方法を示す部分断面図である。

【図8】図7に示した本発明に係るはんだ付け方法によって、チップ部品を部品搭載基板上にはんだ付けした場合の外観を示す図であって、図7の8ー8線に沿った部分断面図である。

【図9】従来のロジン系フラックス含有のはんだペーストを用いたはんだ付け方法を示す部分断面図である。

【図10】図9に示した従来のはんだ付け方法によって、チップ部品を部品搭載基板上にはんだ付けした場合の外観を示す図であって、図9の10ー10線に沿った部分断面図である。

【図11】本発明に係るはんだペーストを用いてチップ部品をはんだ付けした場合と、従来のロジン系フラックス含有はんだペーストを用いてチップ部品をはんだ付けした場合のリフロー温度と部品横押し強度との関係を示す図である。

【図12】本発明に係る電子回路モジュールの正面部分断面図である。

【図13】図12に示した電子回路モジュールのはんだ付け方法を説明する図である。

【図14】本発明に係る電子回路モジュールの別の例を示す正面部分断面図である。

【図15】図14に示した電子回路モジュールのはんだ付け方法を説明する図である。

【図16】RDC測定結果を示すグラフである。

【図17】本発明に係る電子回路装置の正面部分断面図である。

【図18】図17に示した電子回路装置のはんだ付け方法を説明する図である。

【図19】本発明に係る電子回路装置の別の例を示す正面部分断面図である。

【図20】図19に示した電子回路装置のはんだ付け方法を説明する図である。

【図21】RDC測定結果を示すグラフである。

【図22】マザー基板に対する電子回路モジュールのはんだ付け工程を示す正面部分断面図である。

【図23】図22に示した工程の次の工程を示す正面部分断面図である。

【図24】図23に示した工程の次の工程を示す正面部分断面図である。

【図25】図24に示した工程の次の工程を示す正面部分断面図である。

【図26】マザー基板から電子回路モジュールを取り外す工程を示す正面部分断面図である。

【図27】図26に示した工程の次の工程を示す正面部分断面図である。

【図28】サンプル21、22のはんだペーストを用いてコンデンサをはんだ付けした場合について、リフロー温度と部品横押し強度との関係を示す図である。

【図29】サンプル50〜54のはんだペーストを用いてコンデンサをはんだ付けした場合について、リフロー温度と部品横押し強度との関係を示す図である。

【符号の説明】

1 部品搭載基板

21、22 はんだバンプ

3 フラックス

4 チップ部品

81、82 はんだペースト

Claims (25)

- 接着性樹脂と、硬化剤とを含有するはんだ付け用フラックスであって、

前記接着性樹脂は、熱硬化性樹脂を含み、

前記硬化剤は、少なくとも2種のカルボン酸を含み、

前記少なくとも2種のカルボン酸のうち、1種はアジピン酸であり、

前記少なくとも2種のカルボン酸は、互いに異なる融点を有する、

はんだ付け用フラックス。 - 請求項1に記載されたはんだ付け用フラックスであって、

前記少なくとも2種のカルボン酸のうち、1種はアジピン酸であり、

他の1種はコハク酸又は、ピメリット酸から選択される、

はんだ付け用フラックス。 - 接着性樹脂と、硬化剤とを含有するはんだ付け用フラックスであって、

前記硬化剤は、少なくとも2種のカルボン酸を含み、

前記少なくとも2種のカルボン酸は、互いに異なる融点を有し、

前記少なくとも2種のカルボン酸のうち、1種はアジピン酸であり、他の1種はコハク酸又は、ピメリット酸から選択される、

はんだ付け用フラックス。 - 接着性樹脂と、硬化剤とを含有するはんだ付け用フラックスであって、

前記硬化剤は、少なくとも2種のカルボン酸を含み、

前記少なくとも2種のカルボン酸は、互いに異なる融点を有し、

前記2種のカルボン酸の少なくとも1種は、リフロー温度より低い融点をもち、他の1種は、前記リフロー温度より高い融点をもつ、

はんだ付け用フラックス。 - 接着性樹脂と、硬化剤とを含有するはんだ付け用フラックスであって、

前記硬化剤は、少なくとも2種のカルボン酸を含み、

前記少なくとも2種のカルボン酸は、互いに異なる融点を有し、

前記2種のカルボン酸の少なくとも1種は、リフロー温度で前記接着性樹脂を硬化させ、他の1種のカルボン酸は、前記リフロー温度より高い温度で前記接着性樹脂の粘度を低下させる、

はんだ付け用フラックス。 - 請求項1乃至5に記載されたフラックスであって、液状またはペースト状であるフラックス。

- 請求項3乃至6の何れかに記載されたフラックスであって、前記接着性樹脂は、熱硬化性樹脂を含む

フラックス。 - 請求項1、2、7の何れかに記載されたフラックスであって、

前記熱硬化性樹脂はリフロー温度において硬化を始め、リフロー温度より高い温度において粘度が低下する、

フラックス。 - 請求項1、2、7、8に記載されたフラックスであって、

前記熱硬化性樹脂は、エポキシ樹脂、フェノール樹脂、ポリイミド樹脂、シリコン樹脂、変性樹脂またはアクリル樹脂から選択された少なくとも1種を含む、

フラックス。 - 請求項2乃至3に記載されたフラックスであって、

前記アジピン酸の含有率をa(質量%)とし、前記ピメリット酸の含有率をb(質量%)としたとき、

a:b=(85:15)〜(95:5)

を満たす、

フラックス。 - 請求項2乃至3に記載されたフラックスであって、

前記アジピン酸の含有率をa(質量%)とし、前記コハク酸の含有率をc(質量%)としたとき、

a:c=(95:5)〜(25:75)

を満たす、

フラックス。 - はんだ粉末と、フラックスとを含むはんだペーストであって、

前記フラックスは、請求項1乃至11の何れかに記載されたものでなり、

前記はんだ粉末は、前記フラックスと混合されている、

はんだペースト。 - 請求項12に記載されたはんだペーストであって、

前記はんだ粉末は、Sn、Cu、Ag、Sb、Pb、In、ZnまたはBiから選択された少なくとも1種を含む、

はんだペースト。 - 少なくとも1つの電子部品と、部品搭載基板と、はんだ付け用フラックスとを含む電子部品装置であって、

前記電子部品は、前記部品搭載基板の上にはんだ付けされており、

前記はんだ付け用フラックスは、請求項1乃至11の何れかに記載されたフラックスでなり、前記電子部品と前記部品搭載基板との間に介在し、両者を接着している、

電子部品装置。 - 半導体チップと、チップ搭載基板と、はんだ付け用フラックスとを含む電子回路モジュールであって、

前記半導体チップは、少なくとも1つの半導体素子を含み、前記チップ搭載基板の上にはんだ付けされており、

前記はんだ付け用フラックスは、請求項1乃至11の何れかに記載されたものでなり、前記半導体チップと前記チップ搭載基板との間に介在し、両者を接着している、

電子回路モジュール。 - 請求項15に記載された電子回路モジュールであって、

少なくとも一面上にはんだ付けされ、

前記はんだ付けは、はんだ付け用フラックス、又ははんだペーストから選択されるものを用い、

前記はんだ付け用フラックスは請求項1乃至11に記載のものであり、

前記はんだペーストは請求項12又は13に記載のものである、

両面実装電子回路モジュール。 - 電子回路モジュールと、マザー基板と、はんだ付け用フラックスとを含む電子回路装置であって、

前記電子回路モジュールは、前記マザー基板上にはんだ付けされており、

前記はんだ付け用フラックスは、請求項1乃至11の何れかに記載されたものでなり、前記電子回路モジュールと前記マザー基板との間に介在し、両者を接着している、

電子回路装置。 - 請求項17に記載された電子回路装置であって、前記電子回路モジュールは、請求項15又は16に記載されたものでなる、

電子回路装置。 - 請求項1乃至11の何れかに記載されたフラックスを用いてはんだ付けする方法。

- 請求項12または13に記載されたはんだペーストを用いてはんだ付けする方法。

- フラックスによって部品搭載基板に接合された電子部品を、前記部品搭載基板から取り外すリペア方法であって、

前記フラックスは請求項1、3、4、5で記載されたものより選択されるものであり、

前記フラックスの温度をリペア温度に上昇させ、

次に、前記電子部品を取り外す、

工程を含むリペア方法。 - はんだペーストによって部品搭載基板に接合された電子部品を、前記部品搭載基板から取り外すリペア方法であって、

前記はんだペーストは請求項12又は13で記載されたものより選択されるものであり、

はんだペーストの温度をリペア温度に上昇させ、

次に、前記電子部品を取り外す、

工程を含むリペア方法。 - 請求項19又は20に記載された方法であって、

基板の上に電子部品、電子回路モジュールまたは半導体チップをはんだ付けする、

はんだ付け方法。 - 請求項23に記載された方法であって、

前記基板の一面上に、前記はんだペーストによるはんだ付け処理を実行し、

次に、前記基板の他面上で、前記はんだペーストとは異なるはんだを用いて、電子部品をはんだ付けする工程を含む、

はんだ付け方法。 - はんだ付け方法であって、

基板の一面に請求項12または13に記載されたはんだペーストを用いてはんだ付けし、前記はんだペーストに含まれる前記接着性樹脂によって部品搭載基板と部品を固定し、

更に、前記基板の他面上で、前記はんだペーストとは異なるはんだを用いてはんだ付けする方法。

Priority Applications (10)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000218046A JP3849842B2 (ja) | 1999-10-05 | 2000-07-18 | はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法 |

| TW089120637A TW527253B (en) | 1999-10-05 | 2000-10-04 | Soldering flux, soldering paste and soldering process |

| PCT/JP2000/006957 WO2001024968A1 (fr) | 1999-10-05 | 2000-10-05 | Flux de soudure, pate de soudure et procede de soudage |

| US10/089,067 US6915944B1 (en) | 1999-10-05 | 2000-10-05 | Soldering flux, solder paste and method of soldering |

| EP06076345A EP1762329B1 (en) | 1999-10-05 | 2000-10-05 | Soldering flux, soldering paste and method of soldering |

| DE60033552T DE60033552T2 (de) | 1999-10-05 | 2000-10-05 | Lötmittel, lötpaste und lötverfahren |

| DE60040311T DE60040311D1 (de) | 1999-10-05 | 2000-10-05 | Lötmittel, Lötpaste und Lötverfahren |

| AT06076345T ATE408475T1 (de) | 1999-10-05 | 2000-10-05 | Lötmittel, lötpaste und lötverfahren |

| EP00964695A EP1231016B1 (en) | 1999-10-05 | 2000-10-05 | Soldering flux, solder paste and method of soldering |

| AT00964695T ATE354451T1 (de) | 1999-10-05 | 2000-10-05 | Lötmittel, lötpaste und lötverfahren |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP11-284859 | 1999-10-05 | ||

| JP28485999 | 1999-10-05 | ||

| JP2000218046A JP3849842B2 (ja) | 1999-10-05 | 2000-07-18 | はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001170797A JP2001170797A (ja) | 2001-06-26 |

| JP2001170797A5 JP2001170797A5 (ja) | 2005-12-15 |

| JP3849842B2 true JP3849842B2 (ja) | 2006-11-22 |

Family

ID=26555632

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000218046A Expired - Lifetime JP3849842B2 (ja) | 1999-10-05 | 2000-07-18 | はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3849842B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10319888A1 (de) | 2003-04-25 | 2004-11-25 | Siemens Ag | Lotmaterial auf SnAgCu-Basis |

| JP2005072173A (ja) * | 2003-08-22 | 2005-03-17 | Senju Metal Ind Co Ltd | 電子部品およびソルダペースト |

| EP1914035B1 (en) | 2005-08-11 | 2014-08-06 | Senju Metal Industry Co., Ltd. | Lead free solder paste and application thereof |

| JP4535050B2 (ja) * | 2005-09-27 | 2010-09-01 | パナソニック電工株式会社 | 熱硬化性樹脂組成物及びその製造方法 |

| EP2052805B1 (en) * | 2006-08-04 | 2016-09-28 | Panasonic Intellectual Property Management Co., Ltd. | Bonding material, bonded portion and circuit board |

| JP5411503B2 (ja) * | 2006-08-28 | 2014-02-12 | パナソニック株式会社 | 熱硬化性樹脂組成物及びその製造方法並びに回路基板 |

| JP5052857B2 (ja) * | 2006-10-13 | 2012-10-17 | 株式会社フジクラ | 導電性組成物およびこれを用いた導電体、導電回路の形成方法 |

| JP5468199B2 (ja) * | 2006-11-22 | 2014-04-09 | 日立化成株式会社 | 導電性接着剤組成物、電子部品搭載基板及び半導体装置 |

| WO2009044801A1 (ja) | 2007-10-03 | 2009-04-09 | Hitachi Chemical Company, Ltd. | 接着剤組成物及びそれを用いた電子部品搭載基板並びに半導体装置 |

| JP5373464B2 (ja) * | 2008-04-23 | 2013-12-18 | パナソニック株式会社 | 導電性ペーストおよびこれを用いた実装構造体 |

| JP5464463B2 (ja) * | 2008-09-25 | 2014-04-09 | パナソニック株式会社 | 熱硬化性樹脂組成物及び回路基板 |

| US20100101845A1 (en) * | 2008-10-27 | 2010-04-29 | Arata Kishi | Electronic Device and Manufacturing Method for Electronic Device |

| CN102576766A (zh) * | 2009-10-15 | 2012-07-11 | 日立化成工业株式会社 | 导电性粘接剂、太阳能电池及其制造方法、以及太阳能电池模块 |

| CN103328596A (zh) * | 2011-01-27 | 2013-09-25 | 日立化成株式会社 | 导电性粘接剂组合物、连接体及太阳能电池模块 |

| JP5952849B2 (ja) | 2014-03-25 | 2016-07-13 | 岡村製油株式会社 | フラックス及びソルダペースト |

| KR102329367B1 (ko) * | 2018-06-22 | 2021-11-22 | 인듐 코포레이션 | 접착제 물질의 활용을 통한 vippo 납땜 접합부의 포스트 리플로우 상호연결부 고장의 방지 |

-

2000

- 2000-07-18 JP JP2000218046A patent/JP3849842B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001170797A (ja) | 2001-06-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3849842B2 (ja) | はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法 | |

| US6574859B2 (en) | Interconnection process for module assembly and rework | |

| US7145236B2 (en) | Semiconductor device having solder bumps reliably reflow solderable | |

| JP2008510620A (ja) | 半田組成物および半田接合方法ならびに半田接合構造 | |

| JP3454509B2 (ja) | 導電性材料の使用方法 | |

| US6915944B1 (en) | Soldering flux, solder paste and method of soldering | |

| JP5093766B2 (ja) | 導電性ボール等搭載半導体パッケージ基板の製造方法 | |

| JP2008510621A (ja) | 半田組成物及び半田接合方法並びに半田接合構造 | |

| WO2010050185A1 (ja) | 半導体の実装構造体およびその製造方法 | |

| KR20060126677A (ko) | 납땜용 플럭스 및 납땜 방법 | |

| JP4356581B2 (ja) | 電子部品実装方法 | |

| KR20120102803A (ko) | 납프리 땜납 접속 구조체 및 땜납 볼 | |

| US10756039B2 (en) | Fluxes effective in suppressing non-wet-open at BGA assembly | |

| JP2001170798A (ja) | はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール、電子回路装置、及び、はんだ付け方法 | |

| JP2015220396A (ja) | はんだバンプの形成方法及びはんだボール固定用はんだペースト | |

| JP4134976B2 (ja) | 半田接合方法 | |

| KR20150111403A (ko) | 전자부품을 접합하기 위한 무연납땜용 플럭스 및 페이스트, 이를 이용하여 납땜하는 방법 | |

| JP5579996B2 (ja) | はんだ接合方法 | |

| JP2006152312A (ja) | 封止材料、はんだ付け用フラックス、はんだぺースト、電子部品装置、電子回路モジュール及び電子回路装置 | |

| JP3812800B2 (ja) | 封止材料、はんだ付け用フラックス、はんだぺ一スト、電子部品装置、電子回路モジュール及び電子回路装置 | |

| JPH11320176A (ja) | はんだペースト | |

| JP4312996B2 (ja) | はんだペーストおよび半導体装置の製造方法 | |

| JP4259431B2 (ja) | 半田ペーストおよび半田接合方法 | |

| KR20100067702A (ko) | 접착층이 형성된 솔더볼 및 제조방법 | |

| JP2001313459A (ja) | 電子部品装置、電子回路モジュール、電子回路装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051031 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051031 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20051031 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20051208 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051214 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060329 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060404 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060823 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060823 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3849842 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100908 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110908 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120908 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130908 Year of fee payment: 7 |

|

| EXPY | Cancellation because of completion of term |