JP3846748B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP3846748B2 JP3846748B2 JP18761396A JP18761396A JP3846748B2 JP 3846748 B2 JP3846748 B2 JP 3846748B2 JP 18761396 A JP18761396 A JP 18761396A JP 18761396 A JP18761396 A JP 18761396A JP 3846748 B2 JP3846748 B2 JP 3846748B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- output

- signal

- output node

- state

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

- G11C11/417—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction for memory cells of the field-effect type

- G11C11/419—Read-write [R-W] circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1051—Data output circuits, e.g. read-out amplifiers, data output buffers, data output registers, data output level conversion circuits

Description

【0001】

【発明の属する技術分野】

本発明は半導体記憶装置に関し、特にセンスイネーブル時間を最適化した半導体記憶装置に関する。

【0002】

【従来の技術】

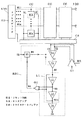

図14に従来の半導体記憶装置の一例として、1ビットのデータの入出力を行うSRAM(staticRAM)90の構成を示す。

図14に示すように、ビット線BLおよびバーBL間に複数のメモリセルMC1〜MCnが接続されてメモリセルカラムCCが構成されている。メモリセルMC1〜MCnには、アドレスデコーダから延在するワード線WL1〜WLnがそれぞれ接続されている。このようなメモリセルカラムCCが並列して複数配置され、それぞれのメモリセルカラムCCから延在するビット線BLおよびバーBLはカラムセレクタCSに接続されている。

【0003】

カラムセレクタCSからは入出力線IOおよびバーIOが延在し、読み出しブロックRBのセンスアンプSAの正入力および負入力に接続されている。また、入出力線IOおよびバーIOは書き込みドライバWDの出力および反転出力にも接続されている。

【0004】

センスアンプSAの出力ノードN1はトライステートバッファTBの入力に接続されている。ここで、センスアンプSAおよびトライステートバッファTBにはセンスイネーブル信号SEが与えられる構成となっており、センスイネーブル信号SEに応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0005】

トライステートバッファTBの出力ノードN2は、データ保持手段Lを構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0006】

また、書き込みドライバWDは、ライトイネーブル信号WEが与えられる構成となっており、ライトイネーブル信号WEに応じて活性あるいは非活性状態となり、活性状態の場合にデータ入力ポートDIより入力されたデータを、入出力線IOおよびバーIOに相補的に出力する。

【0007】

次に、SRAM90の書き込み、読み出し動作の概略について説明する。データ入力ポートDIより入力されたデータは、書き込み時に活性状態となる書き込みドライバWDによって増幅され、入出力線IOおよびバーIOに相補的に出力される。このとき、アドレス入力ポートADより入力された書き込みアドレス信号は、アドレスデコーダADDによりデコードされ、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択し、そのワード線に接続されたメモリセルにデータを書き込む。

【0008】

一方、所望のメモリセルからデータを読み出す場合、アドレス入力ポートADから当該所望のメモリセルを指定する読み出しアドレス信号を入力し、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択する。所望のメモリセルが選択されると、その中に書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力される。このとき、読み出しブロックRB内のセンスアンプSAおよびトライステートバッファTBはセンスイネーブル信号SEで活性状態となっており、出力ノードN2から読み出しデータが増幅されて出力される。

【0009】

以下、図15に示すタイミングチャートを参照しつつ読み出しブロックRBの動作について説明する。

図15に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図15においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0010】

ここで、センスアンプSAおよびトライステートバッファTBはセンスイネーブル信号SEを“H”状態にすることで活性状態となるように構成されている。従って、センスイネーブル信号SEが“H”状態の期間(すなわちセンスアンプSAおよびトライステートバッファTBが活性状態の期間)は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0011】

データ保持手段Lに到達した読み出しデータは、インバータI1で反転増幅され出力ノードN3に出力される。なお、インバータI1では伝搬の遅延が生じるため、出力ノードN3における読み出しデータの出力タイミングは出力ノードN2よりもさらにずれている。

【0012】

そして、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅されて出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0013】

一方、センスイネーブル信号SEが“L”状態の期間(すなわちセンスアンプSAおよびトライステートバッファTBが非活性状態の期間)は、センスアンプSAの出力ノードN1は高インピーダンス状態(“HiZ”状態)となる。

【0014】

ここで、トライステートバッファTBの出力ノードN2にはインバータI2の出力が与えられる構成となっているので、出力ノードN2が“HiZ”状態になることはなく、また、出力ノードN3の読み出しデータはセンスイネーブル信号SEが“L”状態となっても、所定の期間は直前のデータを維持する、すなわちラッチする。

【0015】

そして、センスイネーブル信号SEのサイクル1が終了しサイクル2が始まる、すなわち再びセンスイネーブル信号SEが“H”になると、サイクル1とサイクル2とでは入出力線IOおよびバーIOに出力される読み出しデータが異なるので、データ保持手段Lにラッチされたデータ、すなわち出力ノードN3が所定時間経過後に、“L”状態から“H”状態に反転する。ここで、センスイネーブル信号SEのサイクル1が終了しサイクル2が始まった時点(センスイネーブル信号SEの立ち上がり半値点)から、出力ノードN3が“L”状態から“H”状態に反転した時点(出力ノードN3の立ち上がり半値点)までをラッチ反転時間と呼称する。

【0016】

なお、センスイネーブル信号SEのサイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータが同じなので、サイクル2が終了しサイクル3が始まる、すなわち再びセンスイネーブル信号SEが“H”になってもデータ保持手段Lにラッチされたデータは変化しない。

【0017】

【発明が解決しようとする課題】

SRAM90を一例として説明した従来の半導体記憶装置は以上のように構成されているので、センスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられている。センスイネーブル信号SEが“H”状態の期間は、いわゆるセンス時間ということになるが、前に読み出したデータ(データ保持手段Lにラッチされたデータ)と、現在読み出されているデータが同じ場合(例えば図15に示すサイクル2とサイクル3の場合)においては、両データが同じであることが確認されればそれ以上のセンス時間は不要である。

【0018】

また、前に読み出したデータ(データ保持手段Lにラッチされたデータ)と、現在読み出されているデータが異なる場合(例えば図15に示すサイクル1とサイクル2の場合)において、センス時間は、短い場合は、出力ノードN2が変化するまでの時間、長くてもデータ保持手段Lにラッチされたデータ、すなわち出力ノードN3が反転するまでの所定時間、すなわちラッチ反転時間だけで十分である。

【0019】

しかしながら、従来の半導体記憶装置では図15に示すように、センス時間はラッチ反転時間が経過した後にまで及び、センスする必要がなくなってもセンスイネーブル信号SEが“H”状態の期間が続くことになる。

【0020】

このように、センス時間がラッチ反転時間だけでなくセンス不要時間を含んでいたのは、出力ノードN2が変化するまでの時間や、ラッチ反転時間は素子(トランジスタなど)の電圧特性や温度特性などによってばらつきが生じるため、設計時にラッチ反転時間を正確に求めることが困難であり、センス時間が短すぎてラッチが完了しないといった不具合を防止するためセンス時間にマージンを設定する必要があったためである。

【0021】

一方、センスアンプSAは、メモリセルから読み出された微小なビット線電位や入出力線電位を増幅する差動アンプであり、活性状態(すなわちセンス状態)では常にDC電流が流れ続けるカレントミラー回路などを有した構成となっている。従って、センス不要時間においてもDC電流が流れ続けるので、不要な電力を消費するといった問題があった。

【0022】

本発明は上記のような問題点を解消するためになされたもので、センスイネーブル時間を最適化して不要な電力消費を低減した半導体記憶装置を提供する。

【0023】

【課題を解決するための手段】

本発明に係る請求項1記載の半導体記憶装置は、メモリセルに保持されたデータを読み出すデータ読み出し手段を備える半導体記憶装置であって、前記データ読み出し手段が、周期的に与えられる読み出し制御信号に応答して前記データを増幅して出力するセンス増幅手段と、前記センス増幅手段の出力を受け、前記データを一時的に保持した後、外部出力端子に出力するデータ保持手段と、前記読み出し制御信号の第1のサイクルで前記センス増幅手段から出力され、前記データ保持手段に保持された保持データと、前記読み出し制御信号の第2のサイクルで前記センス増幅手段から出力され、前記データ保持手段に保持される前の保持前データとを比較して、その比較結果を出力するデータ比較手段と、前記データ比較手段に接続され、前記比較結果に応じて前記読み出し制御信号を変更する信号変更手段とを備え、前記読み出し制御信号は、前記センス増幅手段を活性状態にして前記データを増幅して出力させる活性化信号と、前記センス増幅手段を非活性状態にする非活性化信号とで1のサイクルを構成し、前記信号変更手段は、前記比較結果が所定の結果を呈する場合には、前記活性化信号を、強制的に前記非活性化信号に転化させる。

【0024】

本発明に係る請求項2記載の半導体記憶装置は、前記所定の結果が、前記保持前データと前記保持データとが異なる結果であって、前記データ比較手段は、一方の入力を前記保持データを検出することが可能なノードに接続され、他方の入力を前記保持前データを検出することが可能なノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の比較結果信号を出力する組み合わせ論理回路を有している。

【0025】

本発明に係る請求項3記載の半導体記憶装置は、前記データ保持手段が、直列に接続された少なくとも1の第1および第2の信号反転手段を有し、前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、前記保持データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の出力ノードであって、前記保持前データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の入力ノードである。

【0026】

本発明に係る請求項4記載の半導体記憶装置は、前記組み合わせ論理回路がEXNOR回路である。

【0027】

本発明に係る請求項5記載の半導体記憶装置は、前記所定の結果が、前記保持前データと前記保持データとが同一の結果であって、前記データ比較手段は、一方の入力を前記保持データを検出することが可能なノードに接続され、他方の入力を前記保持前データを検出することが可能なノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の信号を出力する第1の組み合わせ論理回路と、前記第1の組み合わせ論理回路の出力と、前記活性化信号が与えられるタイミングに対応して与えられるパルス状のタイミング信号とを受け、前記保持前データと前記保持データとが同一の場合にのみ、前記タイミング信号に対応したパルス状の比較結果信号を出力する第2の組み合わせ論理回路とを有している。

【0028】

本発明に係る請求項6記載の半導体記憶装置は、前記データ読み出し手段が、前記センス増幅手段の出力部と前記データ保持手段の入力部との間に介挿され、前記データを所定の期間遅延させて出力する遅延手段を備え、前記データ比較手段は、前記センス増幅手段の出力と前記遅延手段の出力とを受け、前記読み出し制御信号のうち、前記活性化信号が与えられている期間は、前記センス増幅手段の出力を出力し、前記非活性化信号が与えられている期間は、前記遅延手段の出力を出力する切り替え手段と、前記読み出し制御信号を受け、前記活性化信号が与えられるタイミングに対応して前記タイミング信号を生成するパルス生成手段とを有し、前記データ保持手段は、直列に接続された少なくとも1の第1および第2の信号反転手段を有し、前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、前記保持データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、前記保持前データを検出することが可能なノードは、前記切り替え手段の出力ノードである。

【0029】

本発明に係る請求項7記載の半導体記憶装置は、前記第1の組み合わせ論理回路がEXNOR回路であり、前記第2の組み合わせ論理回路がAND回路である。

【0030】

本発明に係る請求項8記載の半導体記憶装置は、前記所定の結果が、前記保持前データと前記保持データとが異なる第1の結果と、前記保持前データと前記保持データとが同一である第2の結果とを含み、前記データ比較手段は、一方の入力を前記保持データを検出することが可能な第1のノードに接続され、他方の入力を前記保持前データを検出することが可能な第2のノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の第1の比較結果信号を出力する第1の組み合わせ論理回路と、一方の入力を前記保持データを検出することが可能な第3のノードに接続され、他方の入力を前記保持前データを検出することが可能な第4のノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の信号を出力する第2の組み合わせ論理回路と、前記第2の組み合わせ論理回路の出力と、前記活性化信号が与えられるタイミングに対応して与えられるパルス状のタイミング信号とを受け、前記保持前データと前記保持データとが同一の場合にのみ、前記タイミング信号に対応したパルス状の第2の比較結果信号を出力する第3の組み合わせ論理回路と、前記第1の組み合わせ論理回の出力と、前記第3の組み合わせ論理回路の出力とを受け、前記保持前データと前記保持データとが異なる場合には前記第1の比較結果信号を、前記保持前データと前記保持データとが同一の場合には前記第2の比較結果信号を出力する第4の組み合わせ論理回路とを有している。

【0031】

本発明に係る請求項9記載の半導体記憶装置は、前記データ読み出し手段が、前記センス増幅手段の出力部と前記データ保持手段の入力部との間に介挿され、前記データを所定の期間遅延させて出力する遅延手段を備え、前記データ比較手段は、前記センス増幅手段の出力と前記遅延手段の出力とを受け、前記読み出し制御信号のうち、前記活性化信号が与えられている期間は、前記センス増幅手段の出力を出力し、前記非活性化信号が与えられている期間は、前記遅延手段の出力を出力する切り替え手段と、前記読み出し制御信号を受け、前記活性化信号が与えられるタイミングに対応して前記タイミング信号を生成するパルス生成手段とを有し、前記データ保持手段は、直列に接続された少なくとも1の第1および第2の信号反転手段を有し、前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、前記保持データを検出することが可能な第1のノードは、前記少なくとも1の第1の信号反転手段の出力ノードであり、前記保持前データを検出することが可能な第2のノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、前記保持データを検出することが可能な第3のノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、前記保持前データを検出することが可能な第4のノードは、前記切り替え手段の出力ノードである。

【0032】

本発明に係る請求項10記載の半導体記憶装置は、前記第1の組み合わせ論理回路はEXNOR回路であり、前記第2の組み合わせ論理回路はEXNOR回路であり、前記第3の組み合わせ論理回路はAND回路であり、前記第4の組み合わせ論理回路はOR回路である。

【0033】

【発明の実施の形態】

<A.実施の形態1>

<A−1.装置構成>

本発明に係る半導体記憶装置の実施の形態1として、1ビットのデータの入出力を行うSRAM100の構成および動作について図1〜図6を用いて説明する。

【0034】

<A−1−1.全体構成>

図1はSRAM100の全体構成を示す図である。図1に示すように、ビット線BLおよびバーBL間に複数のメモリセルMC1〜MCnが接続されてメモリセルカラムCCが構成されている。メモリセルMC1〜MCnには、アドレスデコーダから延在するワード線WL1〜WLnがそれぞれ接続されている。このようなメモリセルカラムCCが並列して複数配置され、それぞれのメモリセルカラムCCから延在するビット線BLおよびバーBLはカラムセレクタCSに接続されている。

【0035】

カラムセレクタCSからは入出力線IOおよびバーIOが延在し、読み出しブロックRB1のセンスアンプSAの正入力および負入力に接続されている。また、入出力線IOおよびバーIOは書き込みドライバWDの出力および反転出力にも接続されている。

【0036】

センスアンプSAの出力ノードN1はトライステートバッファ(遅延手段)TBの入力に接続されている。そして、トライステートバッファTBの出力ノードN2は、データ保持手段L1を構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力ノードN11にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0037】

また、出力ノードN2およびN3はEXNOR回路G1の入力に接続され、EXNOR回路G1の出力ノードN4はリセット回路RSに接続されている。ここで、EXNOR回路G1は、後に説明する理由からデータ比較手段と言うことができ、リセット回路RSは、後に説明する理由から信号変更手段と言うことができる。

【0038】

リセット回路RSにはセンスイネーブル信号SE(読み出し制御信号)が入力され、その出力ノードN5はセンスアンプSAおよびトライステートバッファTBに接続される構成となっており、センスアンプSAおよびトライステートバッファTBは出力ノードN5から与えられる信号に応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0039】

また、書き込みドライバWDは、ライトイネーブル信号WEが与えられる構成となっており、ライトイネーブル信号WEに応じて活性あるいは非活性状態となり、活性状態の場合にデータ入力ポートDIより入力されたデータを、入出力線IOおよびバーIOに相補的に出力する。

【0040】

<A−1−2.センスアンプの構成>

図2にセンスアンプSAの構成を示す。図2に示すようにセンスアンプSAはPMOSトランジスタQ1およびQ2と、NMOSトランジスタQ3〜Q5によって構成されるカレントミラー回路を有している。

【0041】

PMOSトランジスタQ1とNMOSトランジスタQ3、およびPMOSトランジスタQ2とNMOSトランジスタQ4が直列に接続され、PMOSトランジスタQ1およびQ2のソース電極は電源電位VDDに接続され、NMOSトランジスタQ3およびQ4のソース電極は、NMOSトランジスタQ5のドレイン電極に共通に接続されている。なお、NMOSトランジスタQ5のソース電極は接地電位GNDに接続されている。

【0042】

ここで、PMOSトランジスタQ1およびQ2のゲート電極は、共通してNMOSトランジスタQ3のドレイン電極に接続され、PMOSトランジスタQ2とNMOSトランジスタQ4の接続ノードがセンスアンプSAの出力ノードN1となっている。また、NMOSトランジスタQ3およびQ4のゲート電極には、それぞれ入出力線IOおよびバーIOが接続され、NMOSトランジスタQ5のゲート電極にはリセット回路RSの出力ノードN5が接続される構成となっている。

【0043】

このような構成のセンスアンプSAにおいては、出力ノードN5が“L”状態にあるときは、出力ノードN1は高インピーダンス状態(“HiZ”状態)となる。

【0044】

<A−1−3.トライステートバッファの構成>

図3にトライステートバッファTBの構成を示す。図3に示すようにトライステートバッファTBは、電源電位VDDと接地電位GNDの間に順に直列に接続されたPMOSトランジスタQ11、Q12、NMOSトランジスタQ13、Q14と、入力側がNMOSトランジスタQ14のゲート電極に接続され、出力側がPMOSトランジスタQ11のゲート電極に接続されたインバータI10とで構成される前段回路と、電源電位VDDと接地電位GNDの間に順に直列に接続されたPMOSトランジスタQ15、Q16、NMOSトランジスタQ17、Q18と、入力側がNMOSトランジスタQ18のゲート電極に接続され、出力側がPMOSトランジスタQ15のゲート電極に接続されたインバータI11とで構成される後段回路とを有している。

【0045】

前段回路において、PMOSトランジスタQ12およびNMOSトランジスタQ13のゲート電極は、共通してセンスアンプSAの出力ノードN1に接続され、NMOSトランジスタQ14のゲート電極にはリセット回路RSの出力ノードN5が接続される構成となっている。

【0046】

後段回路において、PMOSトランジスタQ16およびNMOSトランジスタQ17のゲート電極は、共通してPMOSトランジスタQ12およびNMOSトランジスタQ13の接続ノードに接続され、PMOSトランジスタQ16およびNMOSトランジスタQ17の接続ノードがトライステートバッファTBの出力ノードN2となっている。また、NMOSトランジスタQ18のゲート電極にはリセット回路RSの出力ノードN5が接続される構成となっている。

【0047】

このような構成のトライステートバッファTBにおいては、出力ノードN5が“L”状態にあるときは、出力ノードN2は高インピーダンス状態(“HiZ”状態)となるが、先に説明したようにトライステートバッファTBの出力ノードN2にはインバータI2の出力が与えられる構成となっているので、出力ノードN2が“HiZ”状態になることはない。

【0048】

<A−1−4.リセット回路の構成>

図4にリセット回路RSの構成を示す。図4に示すようにリセット回路RSはEXNOR回路G11およびG12、反転入力EXOR回路G13、NOR回路G14とを備えている。

【0049】

EXNOR回路G11および反転入力EXOR回路G13のそれぞれの一方の入力にはセンスイネーブル信号SEが与えられ、EXNOR回路G12およびNOR回路G14のそれぞれの一方の入力にはEXNOR回路G1の出力ノードN4が接続される構成となっている。また、EXNOR回路G11の出力はEXNOR回路G12の他方の入力に接続され、EXNOR回路G12の出力は反転入力EXOR回路G13の他方の入力に接続され、反転入力EXOR回路G13の出力はNOR回路G14およびEXNOR回路G11の他方の入力に接続されている。そしてNOR回路G14の出力がリセット回路RSの出力ノードN5となっている。

【0050】

図5にリセット回路RSの単独動作を示す。図5に示すように、出力ノードN4が“L”状態にあるときはセンスイネーブル信号SEはそのまま通過し、出力ノードN4が“H”状態になったときは出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しく、センスイネーブル信号SEは非活性(ディスエーブル)状態になるに等しい。

【0051】

また、出力ノードN4が“H”状態になるタイミングで出力ノードN5は“L”状態になるが、一旦“L”状態になる(リセットされると)と、次にセンスイネーブル信号SEが“H”になる(すなわちセットされる)まで“L”状態を維持する。このように、リセット回路RSはセンスイネーブル信号SEを実質的に変更するので信号変更手段と言うことができる。

【0052】

<A−2.装置動作>

次に、SRAM100の書き込み、読み出し動作の概略について説明する。データ入力ポートDIより入力されたデータは、書き込み時に活性状態となる書き込みドライバWDによって増幅され、入出力線IOおよびバーIOに相補的に出力される。このとき、アドレス入力ポートADより入力された書き込みアドレス信号は、アドレスデコーダADDによりデコードされ、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択し、そのワード線に接続されたメモリセルにデータを書き込む。

【0053】

一方、所望のメモリセルからデータを読み出す場合、アドレス入力ポートADから当該所望のメモリセルを指定する読み出しアドレス信号を入力し、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択する。所望のメモリセルが選択されると、その中に書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力される。以後の動作は読み出しブロックRB1内のEXNOR回路G1およびリセット回路RSの動作と密接に関連するので、図6に示すタイミングチャートを参照しつつ説明する。

【0054】

図6に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図6においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0055】

ここで、図6に示すように、サイクル1の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。センスアンプSAおよびトライステートバッファTBは、図2および図3を用いて説明したようにリセット回路RSの出力ノードN5を“H”状態にすることで活性状態となるように構成されている。従って、出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0056】

なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0057】

データ保持手段L1においては、サイクル1になっても暫くの間は直前の状態を維持しており、出力ノードN2は“L”状態、出力ノードN3は“H”状態なのでEXNOR回路G1の出力ノードN4は“L”状態である。

【0058】

そして、サイクル1で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“H”状態になる)と、出力ノードN3は“H”状態にあるので、EXNOR回路G1の出力ノード4は“H”状態となり、図4を用いて説明したようにリセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0059】

ここで、EXNOR回路G1はデータ保持手段L1にラッチされたデータの変化を検出し、その結果をリセット回路RSに出力するので、データ比較手段と言うことができる。

【0060】

なお、先に説明したように、リセット回路RSは出力ノードN4が“H”状態になるタイミングで出力ノードN5を“L”状態にする回路であり、一旦“L”状態になる(リセットされると)と、次にセンスイネーブル信号SEが“H”になる(すなわちセットされる)まで“L”状態を維持する。

【0061】

また、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。先に説明したように、出力ノードN11は出力ノードN2に接続されているので、出力ノードN5が“L”状態になって、センスアンプSAおよびトライステートバッファTBが非活性状態になっても、出力ノードN2は“H”状態を維持する。

【0062】

次に、サイクル1からサイクル2に変わると、入出力線IOおよびバーIOに出力される読み出しデータが変わる。サイクル2の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、リセット回路RSの出力ノードN5からセンスイネーブル信号SEがそのまま出力される。出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0063】

データ保持手段L1においては、サイクル2になっても暫くの間は直前の状態を維持しており、出力ノードN2は“H”状態、出力ノードN3は“L”状態なのでEXNOR回路G1の出力ノードN4は“L”状態である。

【0064】

そして、サイクル2で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“L”状態になる)と、出力ノードN3は“L”状態にあるので、EXNOR回路G1の出力ノードN4は“H”状態となる。従って、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0065】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0066】

次に、サイクル2からサイクル3に変わっても、入出力線IOおよびバーIOに出力される読み出しデータは変化しない。サイクル3の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、リセット回路RSの出力ノードN5からセンスイネーブル信号SEがそのまま出力される。出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0067】

読み出しデータが変化しないので、出力ノードN2は“L”状態、出力ノードN3は“H”状態を維持し、EXNOR回路G1の出力ノードN4は“L”状態を維持する。従って、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることはない。

【0069】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0070】

<A−3.特徴的作用効果>

以上説明したように、入出力線IOおよびバーIOに出力される読み出しデータが、その前後で変化するサイクル1およびサイクル2においては、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることにより、センスイネーブル時間を最適化でき、保持データと現在読み出しているデータが異なっている場合にセンスアンプSAが活性状態にある期間を短縮し、センスアンプSAで消費される電力を低減することができる。

【0071】

なお、図6に示すサイクル1およびサイクル2において、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。ここで、当該センス時間はトライステートバッファの出力ノードN2が完全に変化するまでの時間をカバーしているので十分な長さを有していると言える。

【0072】

また、図6に示すサイクル3においても、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。この場合は、センスイネーブル信号SEが“H”状態の期間と同じであるのでセンスアンプSAで消費される電力を低減することはできないが、入出力線IOおよびバーIOに出力される読み出しデータが、その前後で変化する場合が多い装置、例えば画像処理装置などに本実施の形態を適用すると、構成が比較的簡単で、消費電力の低減効果を十分に得ることができる。

【0073】

<A−4.変形例>

ここで、図6に示すサイクル1およびサイクル2において、EXNOR回路G1の出力ノードN4が“H”状態にある期間を、データ変化検出期間と呼称することができる。

【0074】

このデータ変化検出期間は、出力ノードN2が変化してから出力ノードN3が変化するまでの期間によって規定される。従って、出力ノードN2が変化してから出力ノードN3が変化するまでの期間が長くなるように、増幅手段(ドライバやバッファ等)や論理反転手段(インバータ等)を出力ノードN2、N3、N11、およびデータ出力ポートDOに付加することで、このデータ変化検出期間を長くすることができる。

【0075】

データ変化検出期間を長くすることによる利点は、出力ノードN4を確実に“H”状態にできることにある。すなわち、出力ノードN2が変化してから出力ノードN3が変化するまでの期間が短いと、EXNOR回路G1を構成する半導体素子(トランジスタ等)の動作が変化に追いつけず、出力ノードN4を確実に“H”状態にできないからである。

【0076】

なお、データ変化検出期間を1ナノ秒(nsec)程度とするには、インバータを使用する場合には5〜10個のインバータを、例えばインバータI1に付加すれば良い。

【0077】

この場合、データ保持手段L1におけるデータの変化を検出するためには、データの取り出しノードは出力ノードN2とN3だけに限らず、データ保持手段L1の入力からデータ出力ポートDOまでの間であれば、何れの出力ノードから取り出しても良い。

【0078】

<B.実施の形態2>

<B−1.装置構成>

本発明に係る半導体記憶装置の実施の形態2として、1ビットのデータの入出力を行うSRAM200の構成および動作について図7〜図11を用いて説明する。

【0079】

<B−1−1.読み出しブロックの構成>

図7にSRAM200の読み出しブロックRB2の構成を示す。なお、読み出しブロックRB2に、入出力線IOおよびバーIOを介してカラムセレクタCSやメモリセルカラムCC等が接続され、入出力線IOおよびバーIOに書き込みドライバWDが接続される構成については、図1に示したSRAM100と同様であるので、簡略化のため図示は省略する。また、図1と同一の構成については同一の符号を付し、重複する説明は省略する。

【0080】

図7において、センスアンプSAの出力ノードN1はトライステートバッファTBの入力に接続されている。そして、トライステートバッファTBの出力ノードN2は、データ保持手段L2を構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力ノードN11にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0081】

また、出力ノードN1およびN2はセレクタSL(切り替え手段)に接続され、セレクタSLの出力ノードN6はEXNOR回路G2の一方の入力に接続されている。そして、EXNOR回路G2の他方の入力には出力ノードN2が接続され、EXNOR回路G2の出力ノードN8はAND回路G3の一方の入力に接続されている。

【0082】

AND回路G3の出力ノードN9はリセット回路RSに接続されている。リセット回路RSにはセンスイネーブル信号SEが入力され、その出力ノードN5はセンスアンプSAおよびトライステートバッファTBに接続される構成となっており、センスアンプSAおよびトライステートバッファTBは出力ノードN5から与えられる信号に応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0083】

また、センスイネーブル信号SEは、セレクタSLおよびパルス生成手段PGにも与えられ、パルス生成手段PGの出力ノードN7はAND回路G3の他方の入力に接続されている。

【0084】

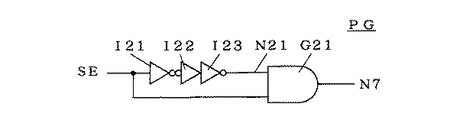

<B−1−2.パルス生成手段の構成>

図8にパルス生成手段PGの構成を示す。図8に示すようにパルス生成手段PGは、直列に接続されたインバータI21〜I23とAND回路G21とを有している。そして、センスイネーブル信号SEがAND回路G21の一方の入力、およびインバータI21の入力に与えられる構成となっている。また、インバータI23の出力ノードN21はAND回路G21の他方の入力に接続され、AND回路G21の出力が出力ノードN7となっている。

【0085】

図9にパルス生成手段PGの単独動作を示す。図9に示すように、センスイネーブル信号SEが“H”状態になると、インバータI21〜I23で発生する所定の遅延時間が経過した後、インバータI23の出力ノードN21が“L”状態となる。AND回路G21は、センスイネーブル信号SEおよび出力ノードN21における信号変化のタイミングの時間差に相当する期間だけ“H”状態となる。すなわちパルス信号を出力ノードN7に与える。

【0086】

<B−1−3.セレクタの構成>

図10にセレクタSLの構成を示す。図10に示すようにセレクタSLはトランスミッションゲートTG1およびTG2と、インバータI31とを備えている。

【0087】

トランスミッションゲートTG1およびTG2の入力端子には、それぞれ出力ノードN1およびN2が接続され、トランスミッションゲートTG1およびTG2の出力端子が共通して出力ノードN6となっている。そして、トランスミッションゲートTG1のNMOSトランジスタ側のゲート電極およびトランスミッションゲートTG2のPMOSトランジスタ側のゲート電極にはセンスイネーブル信号SEが与えられ、トランスミッションゲートTG1のPMOSトランジスタ側のゲート電極およびトランスミッションゲートTG2のNMOSトランジスタ側のゲート電極には、インバータI31を介してセンスイネーブル信号SEの反転信号が与えられる構成となっている。

【0088】

このような構成のセレクタSLにおいては、センスイネーブル信号SEが“H”状態の場合は出力ノードN1のデータを出力ノードN6に与え、センスイネーブル信号SEが“L”状態の場合は出力ノードN2のデータを出力ノードN6に与えることになる。

【0089】

<B−2.装置動作>

SRAM200の書き込み、読み出し動作の概略については、SRAM100と同様であるので重複する説明は省略する。なお、所望のメモリセルに書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力された後の動作は、データ比較手段であるEXNOR回路G2、AND回路G3、セレクタSL、パルス生成手段PG、およびリセット回路RSの動作と密接に関連するので、図11に示すタイミングチャートを参照しつつ説明する。

【0090】

図11に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図11においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0091】

ここで、図11に示すように、サイクル1の直前においてはEXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”である。従って、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。センスアンプSAおよびトライステートバッファTBは、図2および図3を用いて説明したようにリセット回路RSの出力ノードN5を“H”状態にすることで活性状態となるように構成されている。従って、出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0092】

なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0093】

データ保持手段L2においては、サイクル1になっても暫くの間は直前の状態を維持しており、出力ノードN2は“L”状態、出力ノードN3は“H”状態である。そして、サイクル1で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“H”状態になった)時点では、トライステートバッファTBの出力ノードN2はLである。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0094】

やがて、出力ノードN2が“H”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0095】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられる。従ってAND回路G3の出力ノードN9は“L”状態のままであり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力することになる。

【0096】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0097】

次に、サイクル1からサイクル2に変わると、入出力線IOおよびバーIOに出力される読み出しデータが変わる。サイクル2の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”状態である。従って、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0098】

データ保持手段L2においては、サイクル2になっても暫くの間は直前の状態を維持しており、出力ノードN2は“H”状態、出力ノードN3は“L”状態である。そして、サイクル2で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“H”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0099】

やがて、出力ノードN2が“L”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0100】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられる。従ってAND回路G3の出力ノードN9は“L”状態のままであり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力することになる。

【0101】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0102】

次に、サイクル2からサイクル3に変わっても、入出力線IOおよびバーIOに出力される読み出しデータは変化しない。サイクル3の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”である。従って、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0103】

しかし、サイクル3においては、出力ノードN2は“L”状態、出力ノードN3は“H”状態であり、サイクル3で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“L”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“H”状態のままである。

【0104】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられるが、EXNOR回路G2の出力ノードN8が“H”状態であるので、当該パルス信号に対応してAND回路G3の出力ノードN9が“H”状態となり、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0105】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0106】

<B−3.特徴的作用効果>

以上説明したように、入出力線IOおよびバーIOに出力される読み出しデータが、その前のサイクルと変わらないサイクル3においては、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることにより、センスイネーブル時間を最適化してセンスアンプSAが活性状態にある期間を短縮するので、保持データと現在読み出しているデータが同一の場合にセンスアンプSAで消費される電力を低減することができる。

【0107】

なお、図11に示すサイクル3において、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。ここで、当該センス時間は出力ノードN1およびN2において、データの変化がないことを確認するだけの長さがあれば良いので、トライステートバッファの出力ノードN2が完全に変化するまでの時間をカバーする必要があった実施の形態1におけるセンス時間よりもさらに短縮されている。

【0108】

また、図11に示すサイクル1およびサイクル2においても、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。この場合は、センスイネーブル信号SEが“H”状態の期間と同じであるのでセンスアンプSAで消費される電力を低減することはできないが、入出力線IOおよびバーIOに出力される読み出しデータが、その前のサイクルと変わらない場合が多い装置、例えば読み出しが多いインストラクションメモリなどに本実施の形態を適用すると、消費電力の低減効果が大きな装置を得ることができる。

【0109】

<B−4.変形例>

ここで、図11に示すサイクル1およびサイクル2において、EXNOR回路G2の出力ノードN8が“L”状態にある期間を、データ変化検出期間と呼称することができる。

【0110】

このデータ変化検出期間は、出力ノードN1が変化してから出力ノードN2が変化するまでの期間によって規定される。従って、出力ノードN1が変化してから出力ノードN2が変化するまでの期間が長くなるように、増幅手段(ドライバやバッファ等)や論理反転手段(インバータ等)を出力ノードN2、N3、N11、およびデータ出力ポートDOに付加することで、このデータ変化検出期間を長くすることができる。

【0111】

データ変化検出期間を長くすることによる利点は、出力ノードN8を確実に“L”状態にできることにある。すなわち、出力ノードN1が変化してから出力ノードN2が変化するまでの期間が短いと、EXNOR回路G2を構成する半導体素子(トランジスタ等)の動作が変化に追いつけず、出力ノードN8を確実に“L”状態にできないからである。

【0112】

この場合、データの変化を検出するためのデータの取り出しノードは、出力ノードN1およびN2に限られず、センスアンプSAの出力からデータ保持手段L2の入力での間であれば、何れの出力ノードから取り出しても良い。

【0113】

また、図7においては、パルス生成手段PGを用いて、センスイネーブル信号SEに基づいて出力ノードN7のパルス信号を生成しているが、当該信号はセンスイネーブル信号SEとは別個に、外部から供給するようにしても良い。この場合、専用の外部クロック信号などを使用する。

【0114】

<C.実施の形態3>

<C−1.装置構成>

本発明に係る半導体記憶装置の実施の形態3として、1ビットのデータの入出力を行うSRAM300の構成および動作について図12および図13を用いて説明する。

【0115】

<C−1−1.読み出しブロックの構成>

図12にSRAM300の読み出しブロックRB3の構成を示す。なお、読み出しブロックRB3に、入出力線IOおよびバーIOを介してカラムセレクタCSやメモリセルカラムCC等が接続され、入出力線IOおよびバーIOに書き込みドライバWDが接続される構成については、図1に示したSRAM100と同様であるので、簡略化のため図示は省略する。また、図1と同一の構成については同一の符号を付し、重複する説明は省略する。

【0116】

図12において、センスアンプSAの出力ノードN1はトライステートバッファTBの入力に接続されている。そして、トライステートバッファTBの出力ノードN2は、データ保持手段L3を構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力ノードN11にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0117】

また、出力ノードN1およびN2はセレクタSLに接続され、セレクタSLの出力ノードN6はEXNOR回路G2の一方の入力に接続されている。そして、EXNOR回路G2の他方の入力には出力ノードN2が接続され、EXNOR回路G2の出力ノードN8はAND回路G3の一方の入力に接続されている。

【0118】

AND回路G3の出力ノードN9はOR回路G4の一方の入力に接続され、OR回路G4の出力ノードN10はリセット回路RSに接続されている。

【0119】

リセット回路RSにはセンスイネーブル信号SEが入力され、その出力ノードN5はセンスアンプSAおよびトライステートバッファTBに接続される構成となっており、センスアンプSAおよびトライステートバッファTBは出力ノードN5から与えられる信号に応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0120】

また、センスイネーブル信号SEは、セレクタSLおよびパルス生成手段PGにも与えられ、パルス生成手段PGの出力ノードN7はAND回路G3の他方の入力に接続されている。

【0121】

また、出力ノードN2およびN3はEXNOR回路G1の入力に接続され、EXNOR回路G1の出力ノードN4はOR回路G4の他方の入力に接続されている。

【0122】

<C−2.装置動作>

SRAM300の書き込み、読み出し動作の概略については、SRAM100およびSRAM200と同様であるので重複する説明は省略する。なお、所望のメモリセルに書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力された後の動作は、データ比較手段であるEXNOR回路G1およびG2、AND回路G3、OR回路G4、セレクタSL、パルス生成手段PG、およびリセット回路RSの動作と密接に関連するので、図13に示すタイミングチャートを参照しつつ説明する。

【0123】

図13に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図13においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0124】

ここで、図13に示すように、サイクル1の直前においてはEXNOR回路G1の出力ノードN4は“L”状態である。また、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”状態である。従って、OR回路G4の出力ノードN10は“L”状態となり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0125】

センスアンプSAおよびトライステートバッファTBは、図2および図3を用いて説明したようにリセット回路RSの出力ノードN5を“H”状態にすることで活性状態となるように構成されている。従って、出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0126】

なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0127】

データ保持手段L3においては、サイクル1になっても暫くの間は直前の状態を維持しており、出力ノードN2は“L”状態、出力ノードN3は“H”状態である。

【0128】

そして、サイクル1で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“H”状態になる)と、出力ノードN3は“H”状態にあるので、EXNOR回路G1の出力ノードN4は“H”状態となる。

【0129】

また、サイクル1で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“H”状態になった)時点では、出力ノードN2はLである。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0130】

やがて、出力ノードN2が“H”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0131】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられ、AND回路G3の出力ノードN9は“L”状態のままである。従って、OR回路G4の出力ノードN10は、出力ノードN4の変化に合わせて“H”状態となり、出力ノードN4が“L”状態となると出力ノードN10も“L”状態となる。

【0132】

出力ノードN10が“H”状態になると、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0133】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0134】

次に、サイクル1からサイクル2に変わると、入出力線IOおよびバーIOに出力される読み出しデータが変わる。サイクル2の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”状態である。また、EXNOR回路G1の出力ノードN4は“L”状態である。従って、OR回路G4の出力ノードN10は“L”状態であり、リセット回路RSの出力ノードN5からセンスイネーブル信号SEがそのまま出力される。出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0135】

データ保持手段L3においては、サイクル2になっても暫くの間は直前の状態を維持しており、出力ノードN2は“H”状態、出力ノードN3は“L”状態なのでEXNOR回路G1の出力ノードN4は“L”状態である。

【0136】

そして、サイクル2で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“L”状態になる)と、出力ノードN3は“L”状態にあるので、EXNOR回路G1の出力ノードN4は“H”状態となる。

【0137】

また、サイクル2で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“H”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0138】

やがて、出力ノードN2が“L”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0139】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられ、AND回路G3の出力ノードN9は“L”状態のままである。従って、OR回路G4の出力ノードN10は、出力ノードN4の変化に合わせて“H”状態となり、出力ノードN4が“L”状態となると出力ノードN10も“L”状態となる。

【0140】

出力ノードN10が“H”状態になると、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0141】

次に、サイクル2からサイクル3に変わっても、入出力線IOおよびバーIOに出力される読み出しデータは変化しない。サイクル3の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”である。また、サイクル3の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、OR回路G4の出力ノードN10は“L”であり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0142】

しかし、サイクル3においては、出力ノードN2は“L”状態、出力ノードN3は“H”状態であり、サイクル3で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“L”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“H”状態のままである。

【0143】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられるが、EXNOR回路G2の出力ノードN8が“H”状態であるので、当該パルス信号に対応してAND回路G3の出力ノードN9が“H”状態となる。

【0144】

一方、読み出しデータが変化しないので、出力ノードN2は“L”状態、出力ノードN3は“H”状態を維持し、EXNOR回路G1の出力ノードN4は“L”状態を維持する。従ってOR回路G4の出力ノードN10は“H”状態となり、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0145】

<C−3.特徴的作用効果>

以上説明したように、入出力線IOおよびバーIOに出力される読み出しデータが、その前後で変化するサイクル1およびサイクル2において、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態とし、また、入出力線IOおよびバーIOに出力される読み出しデータが、その前のサイクルと変わらないサイクル3において、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることにより、センスイネーブル時間を最適化してセンスアンプSAが活性状態にある期間を短縮するので、保持データと現在読み出しているデータが異なっている場合でも同一の場合でも、センスアンプSAで消費される電力を大幅に低減することができる。

【0146】

<C−4.変形例>

ここで、データ変化検出期間である、EXNOR回路G1の出力ノードN4が“H”状態にある期間、およびEXNOR回路G2の出力ノードN8が“L”状態にある期間を調整して、出力ノードN4を確実に“H”状態に、出力ノードN8を確実に“L”状態にするために、増幅手段(ドライバやバッファ等)や論理反転手段(インバータ等)を出力ノードN2、N3、N11、およびデータ出力ポートDOに付加しても良いことは実施の形態1および実施の形態2と同様である。

【0147】

【発明の効果】

本発明に係る請求項1記載の半導体記憶装置によれば、データ比較手段により、データ保持手段に保持された保持データと、データ保持手段に保持される前の保持前データとを比較し、その比較結果が所定の結果を呈する場合には、信号変更手段により、読み出し制御信号のうち、センス増幅手段を活性化させる活性化信号を、強制的に非活性化信号に転化させるので、センス増幅手段が活性状態にある期間を短縮し、センス増幅手段で消費される電力を低減して、低消費電力の半導体記憶装置を得ることができる。

【0148】

本発明に係る請求項2記載の半導体記憶装置によれば、保持データと保持前データとが異なる結果の場合、組み合わせ論理回路からパルス状の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させるので、保持データと保持前データとが異なる場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが異なる場合には、センス増幅手段が活性状態にある期間を短縮し、センス増幅手段で消費される電力を低減して、低消費電力の半導体記憶装置を得ることができる。

【0149】

本発明に係る請求項3記載の半導体記憶装置によれば、データ保持手段の少なくとも1の第1の信号反転手段の出力ノードから保持データを検出し、少なくとも1の第1の信号反転手段の入力ノードから保持前データを検出することにより、保持データと保持前データとの間に少なくとも1の第1の信号反転手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。

【0150】

本発明に係る請求項4記載の半導体記憶装置によれば、組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の比較結果信号を信号変更手段に与えることができる。

【0151】

本発明に係る請求項5記載の半導体記憶装置によれば、第1の組み合わせ論理回路から、保持前データと保持データとが異なる場合にのみパルス状の信号を出力し、第2の組み合わせ論理回路において、当該パルス状の信号とタイミング信号とを比較し、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合にのみ、第2の組み合わせ論理回路からタイミング信号に対応したパルス状の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させるので、保持データと保持前データとが同一の場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが同一の場合には、センス増幅手段が活性状態にある期間を短縮し、センス増幅手段で消費される電力を低減して、低消費電力の半導体記憶装置を得ることができる。

【0152】

本発明に係る請求項6記載の半導体記憶装置によれば、少なくとも1の第1の信号反転手段の入力ノードから保持データを検出し、切り替え手段の出力ノードから保持前データを検出することにより、保持データと保持前データとの間に遅延手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。また、活性化信号が与えられるタイミングに対応してタイミング信号を生成するパルス生成手段を備えるので、外部からタイミング信号を与えることが不要になる。

【0153】

本発明に係る請求項7記載の半導体記憶装置によれば、第1の組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の信号を出力することができ、第2の組み合わせ論理回路をAND回路とすることで、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合には、タイミング信号に対応したパルス状の比較結果信号を信号変更手段に与えることができる。

【0154】

本発明に係る請求項8記載の半導体記憶装置によれば、保持データと保持前データとが異なる結果の場合、第1の組み合わせ論理回路からパルス状の第1の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させ、第2の組み合わせ論理回路から、保持前データと保持データとが異なる場合にのみパルス状の信号を出力し、第3の組み合わせ論理回路において、当該パルス状の信号とタイミング信号とを比較し、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合にのみ、第3の組み合わせ論理回路からタイミング信号に対応したパルス状の第2の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させるので、保持データと保持前データとが異なる場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが異なる場合に、センス増幅手段が活性状態にある期間を短縮するとともに、保持データと保持前データとが同一の場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが同一の場合にも、センス増幅手段が活性状態にある期間を短縮するので、センス増幅手段で消費される電力を大幅に低減して、低消費電力の半導体記憶装置を得ることができる。

【0155】

本発明に係る請求項9記載の半導体記憶装置によれば、データ保持手段の少なくとも1の第1の信号反転手段の出力ノードから保持データを検出し、少なくとも1の第1の信号反転手段の入力ノードから保持前データを検出することにより、保持データと保持前データとの間に少なくとも1の第1の信号反転手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。また、少なくとも1の第1の信号反転手段の入力ノードから保持データを検出し、切り替え手段の出力ノードから保持前データを検出することにより、保持データと保持前データとの間に遅延手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。また、活性化信号が与えられるタイミングに対応してタイミング信号を生成するパルス生成手段を備えるので、外部からタイミング信号を与えることが不要になる。

【0156】

本発明に係る請求項10記載の半導体記憶装置によれば、第1の組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の第1の比較結果信号を出力することができ、第2の組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の信号を出力することができ、第3の組み合わせ論理回路をAND回路とすることで、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合には、タイミング信号に対応したパルス状の第2の比較結果信号を出力することができ、第4の組み合わせ論理回路をOR回路とすることで、保持前データと保持データとが異なる場合には第1の比較結果信号を、保持前データと保持データとが同一の場合には第2の比較結果信号を信号変更手段に与えることができる。

【図面の簡単な説明】

【図1】 本発明に係る半導体記憶装置の実施の形態1の構成を示す図である。

【図2】 センスアンプの構成を示す図である。

【図3】 トライステートバッファの構成を示す図である。

【図4】 リセット回路の構成を示す図である。

【図5】 リセット回路の動作を説明するタイミングチャートである。

【図6】 本発明に係る半導体記憶装置の実施の形態1の動作を説明するタイミングチャートである。

【図7】 本発明に係る半導体記憶装置の実施の形態2の構成を示す図である。

【図8】 パルス生成手段の構成を示す図である。

【図9】 パルス生成手段の動作を説明するタイミングチャートである。

【図10】 セレクタの構成を示す図である。

【図11】 本発明に係る半導体記憶装置の実施の形態2の動作を説明するタイミングチャートである。

【図12】 本発明に係る半導体記憶装置の実施の形態3の構成を示す図である。

【図13】 本発明に係る半導体記憶装置の実施の形態3の動作を説明するタイミングチャートである。

【図14】 従来の半導体記憶装置の構成を示す図である。

【図15】 従来の半導体記憶装置の動作を説明するタイミングチャートである。

【符号の説明】

RS リセット回路、SA センスアンプ、TB トライステートバッファ、SL セレクタ、PG パルス生成手段。

【発明の属する技術分野】

本発明は半導体記憶装置に関し、特にセンスイネーブル時間を最適化した半導体記憶装置に関する。

【0002】

【従来の技術】

図14に従来の半導体記憶装置の一例として、1ビットのデータの入出力を行うSRAM(staticRAM)90の構成を示す。

図14に示すように、ビット線BLおよびバーBL間に複数のメモリセルMC1〜MCnが接続されてメモリセルカラムCCが構成されている。メモリセルMC1〜MCnには、アドレスデコーダから延在するワード線WL1〜WLnがそれぞれ接続されている。このようなメモリセルカラムCCが並列して複数配置され、それぞれのメモリセルカラムCCから延在するビット線BLおよびバーBLはカラムセレクタCSに接続されている。

【0003】

カラムセレクタCSからは入出力線IOおよびバーIOが延在し、読み出しブロックRBのセンスアンプSAの正入力および負入力に接続されている。また、入出力線IOおよびバーIOは書き込みドライバWDの出力および反転出力にも接続されている。

【0004】

センスアンプSAの出力ノードN1はトライステートバッファTBの入力に接続されている。ここで、センスアンプSAおよびトライステートバッファTBにはセンスイネーブル信号SEが与えられる構成となっており、センスイネーブル信号SEに応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0005】

トライステートバッファTBの出力ノードN2は、データ保持手段Lを構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0006】

また、書き込みドライバWDは、ライトイネーブル信号WEが与えられる構成となっており、ライトイネーブル信号WEに応じて活性あるいは非活性状態となり、活性状態の場合にデータ入力ポートDIより入力されたデータを、入出力線IOおよびバーIOに相補的に出力する。

【0007】

次に、SRAM90の書き込み、読み出し動作の概略について説明する。データ入力ポートDIより入力されたデータは、書き込み時に活性状態となる書き込みドライバWDによって増幅され、入出力線IOおよびバーIOに相補的に出力される。このとき、アドレス入力ポートADより入力された書き込みアドレス信号は、アドレスデコーダADDによりデコードされ、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択し、そのワード線に接続されたメモリセルにデータを書き込む。

【0008】

一方、所望のメモリセルからデータを読み出す場合、アドレス入力ポートADから当該所望のメモリセルを指定する読み出しアドレス信号を入力し、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択する。所望のメモリセルが選択されると、その中に書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力される。このとき、読み出しブロックRB内のセンスアンプSAおよびトライステートバッファTBはセンスイネーブル信号SEで活性状態となっており、出力ノードN2から読み出しデータが増幅されて出力される。

【0009】

以下、図15に示すタイミングチャートを参照しつつ読み出しブロックRBの動作について説明する。

図15に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図15においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0010】

ここで、センスアンプSAおよびトライステートバッファTBはセンスイネーブル信号SEを“H”状態にすることで活性状態となるように構成されている。従って、センスイネーブル信号SEが“H”状態の期間(すなわちセンスアンプSAおよびトライステートバッファTBが活性状態の期間)は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0011】

データ保持手段Lに到達した読み出しデータは、インバータI1で反転増幅され出力ノードN3に出力される。なお、インバータI1では伝搬の遅延が生じるため、出力ノードN3における読み出しデータの出力タイミングは出力ノードN2よりもさらにずれている。

【0012】

そして、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅されて出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0013】

一方、センスイネーブル信号SEが“L”状態の期間(すなわちセンスアンプSAおよびトライステートバッファTBが非活性状態の期間)は、センスアンプSAの出力ノードN1は高インピーダンス状態(“HiZ”状態)となる。

【0014】

ここで、トライステートバッファTBの出力ノードN2にはインバータI2の出力が与えられる構成となっているので、出力ノードN2が“HiZ”状態になることはなく、また、出力ノードN3の読み出しデータはセンスイネーブル信号SEが“L”状態となっても、所定の期間は直前のデータを維持する、すなわちラッチする。

【0015】

そして、センスイネーブル信号SEのサイクル1が終了しサイクル2が始まる、すなわち再びセンスイネーブル信号SEが“H”になると、サイクル1とサイクル2とでは入出力線IOおよびバーIOに出力される読み出しデータが異なるので、データ保持手段Lにラッチされたデータ、すなわち出力ノードN3が所定時間経過後に、“L”状態から“H”状態に反転する。ここで、センスイネーブル信号SEのサイクル1が終了しサイクル2が始まった時点(センスイネーブル信号SEの立ち上がり半値点)から、出力ノードN3が“L”状態から“H”状態に反転した時点(出力ノードN3の立ち上がり半値点)までをラッチ反転時間と呼称する。

【0016】

なお、センスイネーブル信号SEのサイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータが同じなので、サイクル2が終了しサイクル3が始まる、すなわち再びセンスイネーブル信号SEが“H”になってもデータ保持手段Lにラッチされたデータは変化しない。

【0017】

【発明が解決しようとする課題】

SRAM90を一例として説明した従来の半導体記憶装置は以上のように構成されているので、センスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられている。センスイネーブル信号SEが“H”状態の期間は、いわゆるセンス時間ということになるが、前に読み出したデータ(データ保持手段Lにラッチされたデータ)と、現在読み出されているデータが同じ場合(例えば図15に示すサイクル2とサイクル3の場合)においては、両データが同じであることが確認されればそれ以上のセンス時間は不要である。

【0018】

また、前に読み出したデータ(データ保持手段Lにラッチされたデータ)と、現在読み出されているデータが異なる場合(例えば図15に示すサイクル1とサイクル2の場合)において、センス時間は、短い場合は、出力ノードN2が変化するまでの時間、長くてもデータ保持手段Lにラッチされたデータ、すなわち出力ノードN3が反転するまでの所定時間、すなわちラッチ反転時間だけで十分である。

【0019】

しかしながら、従来の半導体記憶装置では図15に示すように、センス時間はラッチ反転時間が経過した後にまで及び、センスする必要がなくなってもセンスイネーブル信号SEが“H”状態の期間が続くことになる。

【0020】

このように、センス時間がラッチ反転時間だけでなくセンス不要時間を含んでいたのは、出力ノードN2が変化するまでの時間や、ラッチ反転時間は素子(トランジスタなど)の電圧特性や温度特性などによってばらつきが生じるため、設計時にラッチ反転時間を正確に求めることが困難であり、センス時間が短すぎてラッチが完了しないといった不具合を防止するためセンス時間にマージンを設定する必要があったためである。

【0021】

一方、センスアンプSAは、メモリセルから読み出された微小なビット線電位や入出力線電位を増幅する差動アンプであり、活性状態(すなわちセンス状態)では常にDC電流が流れ続けるカレントミラー回路などを有した構成となっている。従って、センス不要時間においてもDC電流が流れ続けるので、不要な電力を消費するといった問題があった。

【0022】

本発明は上記のような問題点を解消するためになされたもので、センスイネーブル時間を最適化して不要な電力消費を低減した半導体記憶装置を提供する。

【0023】

【課題を解決するための手段】

本発明に係る請求項1記載の半導体記憶装置は、メモリセルに保持されたデータを読み出すデータ読み出し手段を備える半導体記憶装置であって、前記データ読み出し手段が、周期的に与えられる読み出し制御信号に応答して前記データを増幅して出力するセンス増幅手段と、前記センス増幅手段の出力を受け、前記データを一時的に保持した後、外部出力端子に出力するデータ保持手段と、前記読み出し制御信号の第1のサイクルで前記センス増幅手段から出力され、前記データ保持手段に保持された保持データと、前記読み出し制御信号の第2のサイクルで前記センス増幅手段から出力され、前記データ保持手段に保持される前の保持前データとを比較して、その比較結果を出力するデータ比較手段と、前記データ比較手段に接続され、前記比較結果に応じて前記読み出し制御信号を変更する信号変更手段とを備え、前記読み出し制御信号は、前記センス増幅手段を活性状態にして前記データを増幅して出力させる活性化信号と、前記センス増幅手段を非活性状態にする非活性化信号とで1のサイクルを構成し、前記信号変更手段は、前記比較結果が所定の結果を呈する場合には、前記活性化信号を、強制的に前記非活性化信号に転化させる。

【0024】

本発明に係る請求項2記載の半導体記憶装置は、前記所定の結果が、前記保持前データと前記保持データとが異なる結果であって、前記データ比較手段は、一方の入力を前記保持データを検出することが可能なノードに接続され、他方の入力を前記保持前データを検出することが可能なノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の比較結果信号を出力する組み合わせ論理回路を有している。

【0025】

本発明に係る請求項3記載の半導体記憶装置は、前記データ保持手段が、直列に接続された少なくとも1の第1および第2の信号反転手段を有し、前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、前記保持データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の出力ノードであって、前記保持前データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の入力ノードである。

【0026】

本発明に係る請求項4記載の半導体記憶装置は、前記組み合わせ論理回路がEXNOR回路である。

【0027】

本発明に係る請求項5記載の半導体記憶装置は、前記所定の結果が、前記保持前データと前記保持データとが同一の結果であって、前記データ比較手段は、一方の入力を前記保持データを検出することが可能なノードに接続され、他方の入力を前記保持前データを検出することが可能なノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の信号を出力する第1の組み合わせ論理回路と、前記第1の組み合わせ論理回路の出力と、前記活性化信号が与えられるタイミングに対応して与えられるパルス状のタイミング信号とを受け、前記保持前データと前記保持データとが同一の場合にのみ、前記タイミング信号に対応したパルス状の比較結果信号を出力する第2の組み合わせ論理回路とを有している。

【0028】

本発明に係る請求項6記載の半導体記憶装置は、前記データ読み出し手段が、前記センス増幅手段の出力部と前記データ保持手段の入力部との間に介挿され、前記データを所定の期間遅延させて出力する遅延手段を備え、前記データ比較手段は、前記センス増幅手段の出力と前記遅延手段の出力とを受け、前記読み出し制御信号のうち、前記活性化信号が与えられている期間は、前記センス増幅手段の出力を出力し、前記非活性化信号が与えられている期間は、前記遅延手段の出力を出力する切り替え手段と、前記読み出し制御信号を受け、前記活性化信号が与えられるタイミングに対応して前記タイミング信号を生成するパルス生成手段とを有し、前記データ保持手段は、直列に接続された少なくとも1の第1および第2の信号反転手段を有し、前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、前記保持データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、前記保持前データを検出することが可能なノードは、前記切り替え手段の出力ノードである。

【0029】

本発明に係る請求項7記載の半導体記憶装置は、前記第1の組み合わせ論理回路がEXNOR回路であり、前記第2の組み合わせ論理回路がAND回路である。

【0030】

本発明に係る請求項8記載の半導体記憶装置は、前記所定の結果が、前記保持前データと前記保持データとが異なる第1の結果と、前記保持前データと前記保持データとが同一である第2の結果とを含み、前記データ比較手段は、一方の入力を前記保持データを検出することが可能な第1のノードに接続され、他方の入力を前記保持前データを検出することが可能な第2のノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の第1の比較結果信号を出力する第1の組み合わせ論理回路と、一方の入力を前記保持データを検出することが可能な第3のノードに接続され、他方の入力を前記保持前データを検出することが可能な第4のノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の信号を出力する第2の組み合わせ論理回路と、前記第2の組み合わせ論理回路の出力と、前記活性化信号が与えられるタイミングに対応して与えられるパルス状のタイミング信号とを受け、前記保持前データと前記保持データとが同一の場合にのみ、前記タイミング信号に対応したパルス状の第2の比較結果信号を出力する第3の組み合わせ論理回路と、前記第1の組み合わせ論理回の出力と、前記第3の組み合わせ論理回路の出力とを受け、前記保持前データと前記保持データとが異なる場合には前記第1の比較結果信号を、前記保持前データと前記保持データとが同一の場合には前記第2の比較結果信号を出力する第4の組み合わせ論理回路とを有している。

【0031】

本発明に係る請求項9記載の半導体記憶装置は、前記データ読み出し手段が、前記センス増幅手段の出力部と前記データ保持手段の入力部との間に介挿され、前記データを所定の期間遅延させて出力する遅延手段を備え、前記データ比較手段は、前記センス増幅手段の出力と前記遅延手段の出力とを受け、前記読み出し制御信号のうち、前記活性化信号が与えられている期間は、前記センス増幅手段の出力を出力し、前記非活性化信号が与えられている期間は、前記遅延手段の出力を出力する切り替え手段と、前記読み出し制御信号を受け、前記活性化信号が与えられるタイミングに対応して前記タイミング信号を生成するパルス生成手段とを有し、前記データ保持手段は、直列に接続された少なくとも1の第1および第2の信号反転手段を有し、前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、前記保持データを検出することが可能な第1のノードは、前記少なくとも1の第1の信号反転手段の出力ノードであり、前記保持前データを検出することが可能な第2のノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、前記保持データを検出することが可能な第3のノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、前記保持前データを検出することが可能な第4のノードは、前記切り替え手段の出力ノードである。

【0032】

本発明に係る請求項10記載の半導体記憶装置は、前記第1の組み合わせ論理回路はEXNOR回路であり、前記第2の組み合わせ論理回路はEXNOR回路であり、前記第3の組み合わせ論理回路はAND回路であり、前記第4の組み合わせ論理回路はOR回路である。

【0033】

【発明の実施の形態】

<A.実施の形態1>

<A−1.装置構成>

本発明に係る半導体記憶装置の実施の形態1として、1ビットのデータの入出力を行うSRAM100の構成および動作について図1〜図6を用いて説明する。

【0034】

<A−1−1.全体構成>

図1はSRAM100の全体構成を示す図である。図1に示すように、ビット線BLおよびバーBL間に複数のメモリセルMC1〜MCnが接続されてメモリセルカラムCCが構成されている。メモリセルMC1〜MCnには、アドレスデコーダから延在するワード線WL1〜WLnがそれぞれ接続されている。このようなメモリセルカラムCCが並列して複数配置され、それぞれのメモリセルカラムCCから延在するビット線BLおよびバーBLはカラムセレクタCSに接続されている。

【0035】

カラムセレクタCSからは入出力線IOおよびバーIOが延在し、読み出しブロックRB1のセンスアンプSAの正入力および負入力に接続されている。また、入出力線IOおよびバーIOは書き込みドライバWDの出力および反転出力にも接続されている。

【0036】

センスアンプSAの出力ノードN1はトライステートバッファ(遅延手段)TBの入力に接続されている。そして、トライステートバッファTBの出力ノードN2は、データ保持手段L1を構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力ノードN11にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0037】

また、出力ノードN2およびN3はEXNOR回路G1の入力に接続され、EXNOR回路G1の出力ノードN4はリセット回路RSに接続されている。ここで、EXNOR回路G1は、後に説明する理由からデータ比較手段と言うことができ、リセット回路RSは、後に説明する理由から信号変更手段と言うことができる。

【0038】

リセット回路RSにはセンスイネーブル信号SE(読み出し制御信号)が入力され、その出力ノードN5はセンスアンプSAおよびトライステートバッファTBに接続される構成となっており、センスアンプSAおよびトライステートバッファTBは出力ノードN5から与えられる信号に応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0039】

また、書き込みドライバWDは、ライトイネーブル信号WEが与えられる構成となっており、ライトイネーブル信号WEに応じて活性あるいは非活性状態となり、活性状態の場合にデータ入力ポートDIより入力されたデータを、入出力線IOおよびバーIOに相補的に出力する。

【0040】

<A−1−2.センスアンプの構成>

図2にセンスアンプSAの構成を示す。図2に示すようにセンスアンプSAはPMOSトランジスタQ1およびQ2と、NMOSトランジスタQ3〜Q5によって構成されるカレントミラー回路を有している。

【0041】

PMOSトランジスタQ1とNMOSトランジスタQ3、およびPMOSトランジスタQ2とNMOSトランジスタQ4が直列に接続され、PMOSトランジスタQ1およびQ2のソース電極は電源電位VDDに接続され、NMOSトランジスタQ3およびQ4のソース電極は、NMOSトランジスタQ5のドレイン電極に共通に接続されている。なお、NMOSトランジスタQ5のソース電極は接地電位GNDに接続されている。

【0042】

ここで、PMOSトランジスタQ1およびQ2のゲート電極は、共通してNMOSトランジスタQ3のドレイン電極に接続され、PMOSトランジスタQ2とNMOSトランジスタQ4の接続ノードがセンスアンプSAの出力ノードN1となっている。また、NMOSトランジスタQ3およびQ4のゲート電極には、それぞれ入出力線IOおよびバーIOが接続され、NMOSトランジスタQ5のゲート電極にはリセット回路RSの出力ノードN5が接続される構成となっている。

【0043】

このような構成のセンスアンプSAにおいては、出力ノードN5が“L”状態にあるときは、出力ノードN1は高インピーダンス状態(“HiZ”状態)となる。

【0044】

<A−1−3.トライステートバッファの構成>

図3にトライステートバッファTBの構成を示す。図3に示すようにトライステートバッファTBは、電源電位VDDと接地電位GNDの間に順に直列に接続されたPMOSトランジスタQ11、Q12、NMOSトランジスタQ13、Q14と、入力側がNMOSトランジスタQ14のゲート電極に接続され、出力側がPMOSトランジスタQ11のゲート電極に接続されたインバータI10とで構成される前段回路と、電源電位VDDと接地電位GNDの間に順に直列に接続されたPMOSトランジスタQ15、Q16、NMOSトランジスタQ17、Q18と、入力側がNMOSトランジスタQ18のゲート電極に接続され、出力側がPMOSトランジスタQ15のゲート電極に接続されたインバータI11とで構成される後段回路とを有している。

【0045】

前段回路において、PMOSトランジスタQ12およびNMOSトランジスタQ13のゲート電極は、共通してセンスアンプSAの出力ノードN1に接続され、NMOSトランジスタQ14のゲート電極にはリセット回路RSの出力ノードN5が接続される構成となっている。

【0046】

後段回路において、PMOSトランジスタQ16およびNMOSトランジスタQ17のゲート電極は、共通してPMOSトランジスタQ12およびNMOSトランジスタQ13の接続ノードに接続され、PMOSトランジスタQ16およびNMOSトランジスタQ17の接続ノードがトライステートバッファTBの出力ノードN2となっている。また、NMOSトランジスタQ18のゲート電極にはリセット回路RSの出力ノードN5が接続される構成となっている。

【0047】

このような構成のトライステートバッファTBにおいては、出力ノードN5が“L”状態にあるときは、出力ノードN2は高インピーダンス状態(“HiZ”状態)となるが、先に説明したようにトライステートバッファTBの出力ノードN2にはインバータI2の出力が与えられる構成となっているので、出力ノードN2が“HiZ”状態になることはない。

【0048】

<A−1−4.リセット回路の構成>

図4にリセット回路RSの構成を示す。図4に示すようにリセット回路RSはEXNOR回路G11およびG12、反転入力EXOR回路G13、NOR回路G14とを備えている。

【0049】

EXNOR回路G11および反転入力EXOR回路G13のそれぞれの一方の入力にはセンスイネーブル信号SEが与えられ、EXNOR回路G12およびNOR回路G14のそれぞれの一方の入力にはEXNOR回路G1の出力ノードN4が接続される構成となっている。また、EXNOR回路G11の出力はEXNOR回路G12の他方の入力に接続され、EXNOR回路G12の出力は反転入力EXOR回路G13の他方の入力に接続され、反転入力EXOR回路G13の出力はNOR回路G14およびEXNOR回路G11の他方の入力に接続されている。そしてNOR回路G14の出力がリセット回路RSの出力ノードN5となっている。

【0050】

図5にリセット回路RSの単独動作を示す。図5に示すように、出力ノードN4が“L”状態にあるときはセンスイネーブル信号SEはそのまま通過し、出力ノードN4が“H”状態になったときは出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しく、センスイネーブル信号SEは非活性(ディスエーブル)状態になるに等しい。

【0051】

また、出力ノードN4が“H”状態になるタイミングで出力ノードN5は“L”状態になるが、一旦“L”状態になる(リセットされると)と、次にセンスイネーブル信号SEが“H”になる(すなわちセットされる)まで“L”状態を維持する。このように、リセット回路RSはセンスイネーブル信号SEを実質的に変更するので信号変更手段と言うことができる。

【0052】

<A−2.装置動作>

次に、SRAM100の書き込み、読み出し動作の概略について説明する。データ入力ポートDIより入力されたデータは、書き込み時に活性状態となる書き込みドライバWDによって増幅され、入出力線IOおよびバーIOに相補的に出力される。このとき、アドレス入力ポートADより入力された書き込みアドレス信号は、アドレスデコーダADDによりデコードされ、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択し、そのワード線に接続されたメモリセルにデータを書き込む。

【0053】

一方、所望のメモリセルからデータを読み出す場合、アドレス入力ポートADから当該所望のメモリセルを指定する読み出しアドレス信号を入力し、複数のメモリセルカラムCCのうちの何れか、およびその中のワード線WL1〜WLnの何れかを選択する。所望のメモリセルが選択されると、その中に書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力される。以後の動作は読み出しブロックRB1内のEXNOR回路G1およびリセット回路RSの動作と密接に関連するので、図6に示すタイミングチャートを参照しつつ説明する。

【0054】

図6に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図6においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0055】

ここで、図6に示すように、サイクル1の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。センスアンプSAおよびトライステートバッファTBは、図2および図3を用いて説明したようにリセット回路RSの出力ノードN5を“H”状態にすることで活性状態となるように構成されている。従って、出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0056】

なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0057】

データ保持手段L1においては、サイクル1になっても暫くの間は直前の状態を維持しており、出力ノードN2は“L”状態、出力ノードN3は“H”状態なのでEXNOR回路G1の出力ノードN4は“L”状態である。

【0058】

そして、サイクル1で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“H”状態になる)と、出力ノードN3は“H”状態にあるので、EXNOR回路G1の出力ノード4は“H”状態となり、図4を用いて説明したようにリセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0059】

ここで、EXNOR回路G1はデータ保持手段L1にラッチされたデータの変化を検出し、その結果をリセット回路RSに出力するので、データ比較手段と言うことができる。

【0060】

なお、先に説明したように、リセット回路RSは出力ノードN4が“H”状態になるタイミングで出力ノードN5を“L”状態にする回路であり、一旦“L”状態になる(リセットされると)と、次にセンスイネーブル信号SEが“H”になる(すなわちセットされる)まで“L”状態を維持する。

【0061】

また、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。先に説明したように、出力ノードN11は出力ノードN2に接続されているので、出力ノードN5が“L”状態になって、センスアンプSAおよびトライステートバッファTBが非活性状態になっても、出力ノードN2は“H”状態を維持する。

【0062】

次に、サイクル1からサイクル2に変わると、入出力線IOおよびバーIOに出力される読み出しデータが変わる。サイクル2の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、リセット回路RSの出力ノードN5からセンスイネーブル信号SEがそのまま出力される。出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0063】

データ保持手段L1においては、サイクル2になっても暫くの間は直前の状態を維持しており、出力ノードN2は“H”状態、出力ノードN3は“L”状態なのでEXNOR回路G1の出力ノードN4は“L”状態である。

【0064】

そして、サイクル2で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“L”状態になる)と、出力ノードN3は“L”状態にあるので、EXNOR回路G1の出力ノードN4は“H”状態となる。従って、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0065】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0066】

次に、サイクル2からサイクル3に変わっても、入出力線IOおよびバーIOに出力される読み出しデータは変化しない。サイクル3の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、リセット回路RSの出力ノードN5からセンスイネーブル信号SEがそのまま出力される。出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0067】

読み出しデータが変化しないので、出力ノードN2は“L”状態、出力ノードN3は“H”状態を維持し、EXNOR回路G1の出力ノードN4は“L”状態を維持する。従って、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることはない。

【0069】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0070】

<A−3.特徴的作用効果>

以上説明したように、入出力線IOおよびバーIOに出力される読み出しデータが、その前後で変化するサイクル1およびサイクル2においては、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることにより、センスイネーブル時間を最適化でき、保持データと現在読み出しているデータが異なっている場合にセンスアンプSAが活性状態にある期間を短縮し、センスアンプSAで消費される電力を低減することができる。

【0071】

なお、図6に示すサイクル1およびサイクル2において、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。ここで、当該センス時間はトライステートバッファの出力ノードN2が完全に変化するまでの時間をカバーしているので十分な長さを有していると言える。

【0072】

また、図6に示すサイクル3においても、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。この場合は、センスイネーブル信号SEが“H”状態の期間と同じであるのでセンスアンプSAで消費される電力を低減することはできないが、入出力線IOおよびバーIOに出力される読み出しデータが、その前後で変化する場合が多い装置、例えば画像処理装置などに本実施の形態を適用すると、構成が比較的簡単で、消費電力の低減効果を十分に得ることができる。

【0073】

<A−4.変形例>

ここで、図6に示すサイクル1およびサイクル2において、EXNOR回路G1の出力ノードN4が“H”状態にある期間を、データ変化検出期間と呼称することができる。

【0074】

このデータ変化検出期間は、出力ノードN2が変化してから出力ノードN3が変化するまでの期間によって規定される。従って、出力ノードN2が変化してから出力ノードN3が変化するまでの期間が長くなるように、増幅手段(ドライバやバッファ等)や論理反転手段(インバータ等)を出力ノードN2、N3、N11、およびデータ出力ポートDOに付加することで、このデータ変化検出期間を長くすることができる。

【0075】

データ変化検出期間を長くすることによる利点は、出力ノードN4を確実に“H”状態にできることにある。すなわち、出力ノードN2が変化してから出力ノードN3が変化するまでの期間が短いと、EXNOR回路G1を構成する半導体素子(トランジスタ等)の動作が変化に追いつけず、出力ノードN4を確実に“H”状態にできないからである。

【0076】

なお、データ変化検出期間を1ナノ秒(nsec)程度とするには、インバータを使用する場合には5〜10個のインバータを、例えばインバータI1に付加すれば良い。

【0077】

この場合、データ保持手段L1におけるデータの変化を検出するためには、データの取り出しノードは出力ノードN2とN3だけに限らず、データ保持手段L1の入力からデータ出力ポートDOまでの間であれば、何れの出力ノードから取り出しても良い。

【0078】

<B.実施の形態2>

<B−1.装置構成>

本発明に係る半導体記憶装置の実施の形態2として、1ビットのデータの入出力を行うSRAM200の構成および動作について図7〜図11を用いて説明する。

【0079】

<B−1−1.読み出しブロックの構成>

図7にSRAM200の読み出しブロックRB2の構成を示す。なお、読み出しブロックRB2に、入出力線IOおよびバーIOを介してカラムセレクタCSやメモリセルカラムCC等が接続され、入出力線IOおよびバーIOに書き込みドライバWDが接続される構成については、図1に示したSRAM100と同様であるので、簡略化のため図示は省略する。また、図1と同一の構成については同一の符号を付し、重複する説明は省略する。

【0080】

図7において、センスアンプSAの出力ノードN1はトライステートバッファTBの入力に接続されている。そして、トライステートバッファTBの出力ノードN2は、データ保持手段L2を構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力ノードN11にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0081】

また、出力ノードN1およびN2はセレクタSL(切り替え手段)に接続され、セレクタSLの出力ノードN6はEXNOR回路G2の一方の入力に接続されている。そして、EXNOR回路G2の他方の入力には出力ノードN2が接続され、EXNOR回路G2の出力ノードN8はAND回路G3の一方の入力に接続されている。

【0082】

AND回路G3の出力ノードN9はリセット回路RSに接続されている。リセット回路RSにはセンスイネーブル信号SEが入力され、その出力ノードN5はセンスアンプSAおよびトライステートバッファTBに接続される構成となっており、センスアンプSAおよびトライステートバッファTBは出力ノードN5から与えられる信号に応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0083】

また、センスイネーブル信号SEは、セレクタSLおよびパルス生成手段PGにも与えられ、パルス生成手段PGの出力ノードN7はAND回路G3の他方の入力に接続されている。

【0084】

<B−1−2.パルス生成手段の構成>

図8にパルス生成手段PGの構成を示す。図8に示すようにパルス生成手段PGは、直列に接続されたインバータI21〜I23とAND回路G21とを有している。そして、センスイネーブル信号SEがAND回路G21の一方の入力、およびインバータI21の入力に与えられる構成となっている。また、インバータI23の出力ノードN21はAND回路G21の他方の入力に接続され、AND回路G21の出力が出力ノードN7となっている。

【0085】

図9にパルス生成手段PGの単独動作を示す。図9に示すように、センスイネーブル信号SEが“H”状態になると、インバータI21〜I23で発生する所定の遅延時間が経過した後、インバータI23の出力ノードN21が“L”状態となる。AND回路G21は、センスイネーブル信号SEおよび出力ノードN21における信号変化のタイミングの時間差に相当する期間だけ“H”状態となる。すなわちパルス信号を出力ノードN7に与える。

【0086】

<B−1−3.セレクタの構成>

図10にセレクタSLの構成を示す。図10に示すようにセレクタSLはトランスミッションゲートTG1およびTG2と、インバータI31とを備えている。

【0087】

トランスミッションゲートTG1およびTG2の入力端子には、それぞれ出力ノードN1およびN2が接続され、トランスミッションゲートTG1およびTG2の出力端子が共通して出力ノードN6となっている。そして、トランスミッションゲートTG1のNMOSトランジスタ側のゲート電極およびトランスミッションゲートTG2のPMOSトランジスタ側のゲート電極にはセンスイネーブル信号SEが与えられ、トランスミッションゲートTG1のPMOSトランジスタ側のゲート電極およびトランスミッションゲートTG2のNMOSトランジスタ側のゲート電極には、インバータI31を介してセンスイネーブル信号SEの反転信号が与えられる構成となっている。

【0088】

このような構成のセレクタSLにおいては、センスイネーブル信号SEが“H”状態の場合は出力ノードN1のデータを出力ノードN6に与え、センスイネーブル信号SEが“L”状態の場合は出力ノードN2のデータを出力ノードN6に与えることになる。

【0089】

<B−2.装置動作>

SRAM200の書き込み、読み出し動作の概略については、SRAM100と同様であるので重複する説明は省略する。なお、所望のメモリセルに書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力された後の動作は、データ比較手段であるEXNOR回路G2、AND回路G3、セレクタSL、パルス生成手段PG、およびリセット回路RSの動作と密接に関連するので、図11に示すタイミングチャートを参照しつつ説明する。

【0090】

図11に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図11においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0091】

ここで、図11に示すように、サイクル1の直前においてはEXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”である。従って、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。センスアンプSAおよびトライステートバッファTBは、図2および図3を用いて説明したようにリセット回路RSの出力ノードN5を“H”状態にすることで活性状態となるように構成されている。従って、出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0092】

なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0093】

データ保持手段L2においては、サイクル1になっても暫くの間は直前の状態を維持しており、出力ノードN2は“L”状態、出力ノードN3は“H”状態である。そして、サイクル1で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“H”状態になった)時点では、トライステートバッファTBの出力ノードN2はLである。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0094】

やがて、出力ノードN2が“H”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0095】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられる。従ってAND回路G3の出力ノードN9は“L”状態のままであり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力することになる。

【0096】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0097】

次に、サイクル1からサイクル2に変わると、入出力線IOおよびバーIOに出力される読み出しデータが変わる。サイクル2の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”状態である。従って、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0098】

データ保持手段L2においては、サイクル2になっても暫くの間は直前の状態を維持しており、出力ノードN2は“H”状態、出力ノードN3は“L”状態である。そして、サイクル2で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“H”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0099】

やがて、出力ノードN2が“L”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0100】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられる。従ってAND回路G3の出力ノードN9は“L”状態のままであり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力することになる。

【0101】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0102】

次に、サイクル2からサイクル3に変わっても、入出力線IOおよびバーIOに出力される読み出しデータは変化しない。サイクル3の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”である。従って、図4を用いて説明したようにリセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0103】

しかし、サイクル3においては、出力ノードN2は“L”状態、出力ノードN3は“H”状態であり、サイクル3で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“L”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“H”状態のままである。

【0104】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられるが、EXNOR回路G2の出力ノードN8が“H”状態であるので、当該パルス信号に対応してAND回路G3の出力ノードN9が“H”状態となり、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0105】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0106】

<B−3.特徴的作用効果>

以上説明したように、入出力線IOおよびバーIOに出力される読み出しデータが、その前のサイクルと変わらないサイクル3においては、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることにより、センスイネーブル時間を最適化してセンスアンプSAが活性状態にある期間を短縮するので、保持データと現在読み出しているデータが同一の場合にセンスアンプSAで消費される電力を低減することができる。

【0107】

なお、図11に示すサイクル3において、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。ここで、当該センス時間は出力ノードN1およびN2において、データの変化がないことを確認するだけの長さがあれば良いので、トライステートバッファの出力ノードN2が完全に変化するまでの時間をカバーする必要があった実施の形態1におけるセンス時間よりもさらに短縮されている。

【0108】

また、図11に示すサイクル1およびサイクル2においても、リセット回路RSの出力ノードN5が“H”状態にある期間、すなわち出力ノードN5の立ち上がり半値点から立ち下がり半値点までをセンス時間と呼称する。この場合は、センスイネーブル信号SEが“H”状態の期間と同じであるのでセンスアンプSAで消費される電力を低減することはできないが、入出力線IOおよびバーIOに出力される読み出しデータが、その前のサイクルと変わらない場合が多い装置、例えば読み出しが多いインストラクションメモリなどに本実施の形態を適用すると、消費電力の低減効果が大きな装置を得ることができる。

【0109】

<B−4.変形例>

ここで、図11に示すサイクル1およびサイクル2において、EXNOR回路G2の出力ノードN8が“L”状態にある期間を、データ変化検出期間と呼称することができる。

【0110】

このデータ変化検出期間は、出力ノードN1が変化してから出力ノードN2が変化するまでの期間によって規定される。従って、出力ノードN1が変化してから出力ノードN2が変化するまでの期間が長くなるように、増幅手段(ドライバやバッファ等)や論理反転手段(インバータ等)を出力ノードN2、N3、N11、およびデータ出力ポートDOに付加することで、このデータ変化検出期間を長くすることができる。

【0111】

データ変化検出期間を長くすることによる利点は、出力ノードN8を確実に“L”状態にできることにある。すなわち、出力ノードN1が変化してから出力ノードN2が変化するまでの期間が短いと、EXNOR回路G2を構成する半導体素子(トランジスタ等)の動作が変化に追いつけず、出力ノードN8を確実に“L”状態にできないからである。

【0112】

この場合、データの変化を検出するためのデータの取り出しノードは、出力ノードN1およびN2に限られず、センスアンプSAの出力からデータ保持手段L2の入力での間であれば、何れの出力ノードから取り出しても良い。

【0113】

また、図7においては、パルス生成手段PGを用いて、センスイネーブル信号SEに基づいて出力ノードN7のパルス信号を生成しているが、当該信号はセンスイネーブル信号SEとは別個に、外部から供給するようにしても良い。この場合、専用の外部クロック信号などを使用する。

【0114】

<C.実施の形態3>

<C−1.装置構成>

本発明に係る半導体記憶装置の実施の形態3として、1ビットのデータの入出力を行うSRAM300の構成および動作について図12および図13を用いて説明する。

【0115】

<C−1−1.読み出しブロックの構成>

図12にSRAM300の読み出しブロックRB3の構成を示す。なお、読み出しブロックRB3に、入出力線IOおよびバーIOを介してカラムセレクタCSやメモリセルカラムCC等が接続され、入出力線IOおよびバーIOに書き込みドライバWDが接続される構成については、図1に示したSRAM100と同様であるので、簡略化のため図示は省略する。また、図1と同一の構成については同一の符号を付し、重複する説明は省略する。

【0116】

図12において、センスアンプSAの出力ノードN1はトライステートバッファTBの入力に接続されている。そして、トライステートバッファTBの出力ノードN2は、データ保持手段L3を構成するインバータI1の入力に接続され、インバータI1の出力ノードN3はインバータI2の入力に接続されている。ここで、トライステートバッファTBの出力ノードN2はインバータI2の出力ノードN11にも接続されてループ経路を構成し、出力ノードN11は出力バッファOBの入力に接続され、出力バッファOBの出力は、データ出力ポートDOに接続されている。

【0117】

また、出力ノードN1およびN2はセレクタSLに接続され、セレクタSLの出力ノードN6はEXNOR回路G2の一方の入力に接続されている。そして、EXNOR回路G2の他方の入力には出力ノードN2が接続され、EXNOR回路G2の出力ノードN8はAND回路G3の一方の入力に接続されている。

【0118】

AND回路G3の出力ノードN9はOR回路G4の一方の入力に接続され、OR回路G4の出力ノードN10はリセット回路RSに接続されている。

【0119】

リセット回路RSにはセンスイネーブル信号SEが入力され、その出力ノードN5はセンスアンプSAおよびトライステートバッファTBに接続される構成となっており、センスアンプSAおよびトライステートバッファTBは出力ノードN5から与えられる信号に応じて活性あるいは非活性状態となり、活性状態の場合にビット線BLおよびバーBLに読み出される信号の電位差を増幅して出力ノードN2から出力する。

【0120】

また、センスイネーブル信号SEは、セレクタSLおよびパルス生成手段PGにも与えられ、パルス生成手段PGの出力ノードN7はAND回路G3の他方の入力に接続されている。

【0121】

また、出力ノードN2およびN3はEXNOR回路G1の入力に接続され、EXNOR回路G1の出力ノードN4はOR回路G4の他方の入力に接続されている。

【0122】

<C−2.装置動作>

SRAM300の書き込み、読み出し動作の概略については、SRAM100およびSRAM200と同様であるので重複する説明は省略する。なお、所望のメモリセルに書き込まれたデータがビット線BLおよびバーBLを介して入出力線IOおよびバーIOに出力された後の動作は、データ比較手段であるEXNOR回路G1およびG2、AND回路G3、OR回路G4、セレクタSL、パルス生成手段PG、およびリセット回路RSの動作と密接に関連するので、図13に示すタイミングチャートを参照しつつ説明する。

【0123】

図13に示すようにセンスイネーブル信号SEは“H”状態と“L”状態が交互に規則的に与えられ、“H”状態と“L”状態の1組で1サイクルを構成している。そして、図13においてはセンスイネーブル信号SEのサイクル1とサイクル2とでは、入出力線IOおよびバーIOに出力される読み出しデータは異なり、サイクル2とサイクル3とでは入出力線IOおよびバーIOに出力される読み出しデータは同じである。

【0124】

ここで、図13に示すように、サイクル1の直前においてはEXNOR回路G1の出力ノードN4は“L”状態である。また、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”状態である。従って、OR回路G4の出力ノードN10は“L”状態となり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0125】

センスアンプSAおよびトライステートバッファTBは、図2および図3を用いて説明したようにリセット回路RSの出力ノードN5を“H”状態にすることで活性状態となるように構成されている。従って、出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0126】

なお、センスアンプSAおよびトライステートバッファTBではそれぞれ伝搬の遅延が生じるため、出力ノードN1およびN2における読み出しデータの出力タイミングが少しずつずれている。

【0127】

データ保持手段L3においては、サイクル1になっても暫くの間は直前の状態を維持しており、出力ノードN2は“L”状態、出力ノードN3は“H”状態である。

【0128】

そして、サイクル1で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“H”状態になる)と、出力ノードN3は“H”状態にあるので、EXNOR回路G1の出力ノードN4は“H”状態となる。

【0129】

また、サイクル1で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“H”状態になった)時点では、出力ノードN2はLである。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0130】

やがて、出力ノードN2が“H”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0131】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられ、AND回路G3の出力ノードN9は“L”状態のままである。従って、OR回路G4の出力ノードN10は、出力ノードN4の変化に合わせて“H”状態となり、出力ノードN4が“L”状態となると出力ノードN10も“L”状態となる。

【0132】

出力ノードN10が“H”状態になると、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0133】

なお、出力ノードN3の読み出しデータはインバータI2に与えられ、再度反転増幅され、出力ノードN11を介して出力バッファOBに与えられ、出力バッファOBでさらに増幅されてデータ出力ポートDOに与えられる。

【0134】

次に、サイクル1からサイクル2に変わると、入出力線IOおよびバーIOに出力される読み出しデータが変わる。サイクル2の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”状態である。また、EXNOR回路G1の出力ノードN4は“L”状態である。従って、OR回路G4の出力ノードN10は“L”状態であり、リセット回路RSの出力ノードN5からセンスイネーブル信号SEがそのまま出力される。出力ノードN5が“H”状態の期間は、読み出しデータがセンスアンプSAおよびトライステートバッファTBで増幅され、出力ノードN2から出力される。

【0135】

データ保持手段L3においては、サイクル2になっても暫くの間は直前の状態を維持しており、出力ノードN2は“H”状態、出力ノードN3は“L”状態なのでEXNOR回路G1の出力ノードN4は“L”状態である。

【0136】

そして、サイクル2で新たに読みだしたデータがデータ保持手段L1に到達する(出力ノードN2が“L”状態になる)と、出力ノードN3は“L”状態にあるので、EXNOR回路G1の出力ノードN4は“H”状態となる。

【0137】

また、サイクル2で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“H”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“L”状態となる。

【0138】

やがて、出力ノードN2が“L”状態になると、EXNOR回路G2の出力ノードN8は“H”状態となる。

【0139】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられ、AND回路G3の出力ノードN9は“L”状態のままである。従って、OR回路G4の出力ノードN10は、出力ノードN4の変化に合わせて“H”状態となり、出力ノードN4が“L”状態となると出力ノードN10も“L”状態となる。

【0140】

出力ノードN10が“H”状態になると、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0141】

次に、サイクル2からサイクル3に変わっても、入出力線IOおよびバーIOに出力される読み出しデータは変化しない。サイクル3の直前においては、EXNOR回路G2の出力ノードN8は“H”状態であり、パルス生成手段PGの出力ノードN7は“L”状態であるので、AND回路G3の出力ノードN9は“L”である。また、サイクル3の直前においてはEXNOR回路G1の出力ノードN4は“L”状態であるので、OR回路G4の出力ノードN10は“L”であり、リセット回路RSはセンスイネーブル信号SEをそのまま出力ノードN5から出力する。

【0142】

しかし、サイクル3においては、出力ノードN2は“L”状態、出力ノードN3は“H”状態であり、サイクル3で新たに読みだしたデータがセンスアンプSAの出力ノードN1から出力された(出力ノードN1が“L”状態になった)時点では、トライステートバッファTBの出力ノードN2は“L”状態である。ここで、センスイネーブル信号SEは“H”状態にあるので、セレクタSLの出力ノードN6には出力ノードN1のデータが与えられる。従って、EXNOR回路G2の出力ノードN8は“H”状態のままである。

【0143】

また、センスイネーブル信号SEが“H”状態になるのに対応して、パルス生成手段PGの出力ノードN7にパルス信号が与えられるが、EXNOR回路G2の出力ノードN8が“H”状態であるので、当該パルス信号に対応してAND回路G3の出力ノードN9が“H”状態となる。

【0144】

一方、読み出しデータが変化しないので、出力ノードN2は“L”状態、出力ノードN3は“H”状態を維持し、EXNOR回路G1の出力ノードN4は“L”状態を維持する。従ってOR回路G4の出力ノードN10は“H”状態となり、リセット回路RSの出力ノードN5は“L”状態になる。これは、“H”状態にあったセンスイネーブル信号SEを途中で“L”状態とするに等しい動作である。

【0145】

<C−3.特徴的作用効果>

以上説明したように、入出力線IOおよびバーIOに出力される読み出しデータが、その前後で変化するサイクル1およびサイクル2において、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態とし、また、入出力線IOおよびバーIOに出力される読み出しデータが、その前のサイクルと変わらないサイクル3において、“H”状態にあるセンスイネーブル信号SEを、実質的に途中で“L”状態にすることにより、センスイネーブル時間を最適化してセンスアンプSAが活性状態にある期間を短縮するので、保持データと現在読み出しているデータが異なっている場合でも同一の場合でも、センスアンプSAで消費される電力を大幅に低減することができる。

【0146】

<C−4.変形例>

ここで、データ変化検出期間である、EXNOR回路G1の出力ノードN4が“H”状態にある期間、およびEXNOR回路G2の出力ノードN8が“L”状態にある期間を調整して、出力ノードN4を確実に“H”状態に、出力ノードN8を確実に“L”状態にするために、増幅手段(ドライバやバッファ等)や論理反転手段(インバータ等)を出力ノードN2、N3、N11、およびデータ出力ポートDOに付加しても良いことは実施の形態1および実施の形態2と同様である。

【0147】

【発明の効果】

本発明に係る請求項1記載の半導体記憶装置によれば、データ比較手段により、データ保持手段に保持された保持データと、データ保持手段に保持される前の保持前データとを比較し、その比較結果が所定の結果を呈する場合には、信号変更手段により、読み出し制御信号のうち、センス増幅手段を活性化させる活性化信号を、強制的に非活性化信号に転化させるので、センス増幅手段が活性状態にある期間を短縮し、センス増幅手段で消費される電力を低減して、低消費電力の半導体記憶装置を得ることができる。

【0148】

本発明に係る請求項2記載の半導体記憶装置によれば、保持データと保持前データとが異なる結果の場合、組み合わせ論理回路からパルス状の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させるので、保持データと保持前データとが異なる場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが異なる場合には、センス増幅手段が活性状態にある期間を短縮し、センス増幅手段で消費される電力を低減して、低消費電力の半導体記憶装置を得ることができる。

【0149】

本発明に係る請求項3記載の半導体記憶装置によれば、データ保持手段の少なくとも1の第1の信号反転手段の出力ノードから保持データを検出し、少なくとも1の第1の信号反転手段の入力ノードから保持前データを検出することにより、保持データと保持前データとの間に少なくとも1の第1の信号反転手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。

【0150】

本発明に係る請求項4記載の半導体記憶装置によれば、組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の比較結果信号を信号変更手段に与えることができる。

【0151】

本発明に係る請求項5記載の半導体記憶装置によれば、第1の組み合わせ論理回路から、保持前データと保持データとが異なる場合にのみパルス状の信号を出力し、第2の組み合わせ論理回路において、当該パルス状の信号とタイミング信号とを比較し、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合にのみ、第2の組み合わせ論理回路からタイミング信号に対応したパルス状の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させるので、保持データと保持前データとが同一の場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが同一の場合には、センス増幅手段が活性状態にある期間を短縮し、センス増幅手段で消費される電力を低減して、低消費電力の半導体記憶装置を得ることができる。

【0152】

本発明に係る請求項6記載の半導体記憶装置によれば、少なくとも1の第1の信号反転手段の入力ノードから保持データを検出し、切り替え手段の出力ノードから保持前データを検出することにより、保持データと保持前データとの間に遅延手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。また、活性化信号が与えられるタイミングに対応してタイミング信号を生成するパルス生成手段を備えるので、外部からタイミング信号を与えることが不要になる。

【0153】

本発明に係る請求項7記載の半導体記憶装置によれば、第1の組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の信号を出力することができ、第2の組み合わせ論理回路をAND回路とすることで、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合には、タイミング信号に対応したパルス状の比較結果信号を信号変更手段に与えることができる。

【0154】

本発明に係る請求項8記載の半導体記憶装置によれば、保持データと保持前データとが異なる結果の場合、第1の組み合わせ論理回路からパルス状の第1の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させ、第2の組み合わせ論理回路から、保持前データと保持データとが異なる場合にのみパルス状の信号を出力し、第3の組み合わせ論理回路において、当該パルス状の信号とタイミング信号とを比較し、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合にのみ、第3の組み合わせ論理回路からタイミング信号に対応したパルス状の第2の比較結果信号を信号変更手段に与え、センス増幅手段を活性化させる活性化信号を強制的に非活性化信号に転化させるので、保持データと保持前データとが異なる場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが異なる場合に、センス増幅手段が活性状態にある期間を短縮するとともに、保持データと保持前データとが同一の場合、すなわち第1のサイクルと第2のサイクルとで読み出しデータが同一の場合にも、センス増幅手段が活性状態にある期間を短縮するので、センス増幅手段で消費される電力を大幅に低減して、低消費電力の半導体記憶装置を得ることができる。

【0155】

本発明に係る請求項9記載の半導体記憶装置によれば、データ保持手段の少なくとも1の第1の信号反転手段の出力ノードから保持データを検出し、少なくとも1の第1の信号反転手段の入力ノードから保持前データを検出することにより、保持データと保持前データとの間に少なくとも1の第1の信号反転手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。また、少なくとも1の第1の信号反転手段の入力ノードから保持データを検出し、切り替え手段の出力ノードから保持前データを検出することにより、保持データと保持前データとの間に遅延手段の通過に伴う時間差が生じることになり、保持データと保持前データとの比較を確実に行うことができる。また、活性化信号が与えられるタイミングに対応してタイミング信号を生成するパルス生成手段を備えるので、外部からタイミング信号を与えることが不要になる。

【0156】

本発明に係る請求項10記載の半導体記憶装置によれば、第1の組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の第1の比較結果信号を出力することができ、第2の組み合わせ論理回路をEXNOR回路とすることで、保持データと保持前データとが異なる場合には、それぞれの変化のタイミングに合わせてパルス状の信号を出力することができ、第3の組み合わせ論理回路をAND回路とすることで、パルス状の信号が与えられていない場合、すなわち保持前データと保持データとが同一の結果の場合には、タイミング信号に対応したパルス状の第2の比較結果信号を出力することができ、第4の組み合わせ論理回路をOR回路とすることで、保持前データと保持データとが異なる場合には第1の比較結果信号を、保持前データと保持データとが同一の場合には第2の比較結果信号を信号変更手段に与えることができる。

【図面の簡単な説明】

【図1】 本発明に係る半導体記憶装置の実施の形態1の構成を示す図である。

【図2】 センスアンプの構成を示す図である。

【図3】 トライステートバッファの構成を示す図である。

【図4】 リセット回路の構成を示す図である。

【図5】 リセット回路の動作を説明するタイミングチャートである。

【図6】 本発明に係る半導体記憶装置の実施の形態1の動作を説明するタイミングチャートである。

【図7】 本発明に係る半導体記憶装置の実施の形態2の構成を示す図である。

【図8】 パルス生成手段の構成を示す図である。

【図9】 パルス生成手段の動作を説明するタイミングチャートである。

【図10】 セレクタの構成を示す図である。

【図11】 本発明に係る半導体記憶装置の実施の形態2の動作を説明するタイミングチャートである。

【図12】 本発明に係る半導体記憶装置の実施の形態3の構成を示す図である。

【図13】 本発明に係る半導体記憶装置の実施の形態3の動作を説明するタイミングチャートである。

【図14】 従来の半導体記憶装置の構成を示す図である。

【図15】 従来の半導体記憶装置の動作を説明するタイミングチャートである。

【符号の説明】

RS リセット回路、SA センスアンプ、TB トライステートバッファ、SL セレクタ、PG パルス生成手段。

Claims (10)

- メモリセルに保持されたデータを読み出すデータ読み出し手段を備える半導体記憶装置であって、

前記データ読み出し手段は、

周期的に与えられる読み出し制御信号に応答して前記データを増幅して出力するセンス増幅手段と、

前記センス増幅手段の出力を受け、前記データを一時的に保持した後、外部出力端子に出力するデータ保持手段と、

前記読み出し制御信号の第1のサイクルで前記センス増幅手段から出力され、前記データ保持手段に保持された保持データと、前記読み出し制御信号の第2のサイクルで前記センス増幅手段から出力され、前記データ保持手段に保持される前の保持前データとを比較して、その比較結果を出力するデータ比較手段と、

前記データ比較手段に接続され、前記比較結果に応じて前記読み出し制御信号を変更する信号変更手段とを備え、

前記読み出し制御信号は、前記センス増幅手段を活性状態にして前記データを増幅して出力させる活性化信号と、前記センス増幅手段を非活性状態にする非活性化信号とで1のサイクルを構成し、

前記信号変更手段は、前記比較結果が所定の結果を呈する場合には、前記活性化信号を、強制的に前記非活性化信号に転化させることを特徴とする半導体記憶装置。 - 前記所定の結果は、前記保持前データと前記保持データとが異なる結果であって、

前記データ比較手段は、

一方の入力を前記保持データを検出することが可能なノードに接続され、他方の入力を前記保持前データを検出することが可能なノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の比較結果信号を出力する組み合わせ論理回路を有する請求項1記載の半導体記憶装置。 - 前記データ保持手段は、

直列に接続された少なくとも1の第1および第2の信号反転手段を有し、

前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、

前記保持データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の出力ノードであって、

前記保持前データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の入力ノードである請求項2記載の半導体記憶装置。 - 前記組み合わせ論理回路はEXNOR回路である請求項3記載の半導体記憶装置。

- 前記所定の結果は、前記保持前データと前記保持データとが同一の結果であって、

前記データ比較手段は、

一方の入力を前記保持データを検出することが可能なノードに接続され、他方の入力を前記保持前データを検出することが可能なノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の信号を出力する第1の組み合わせ論理回路と、

前記第1の組み合わせ論理回路の出力と、前記活性化信号が与えられるタイミングに対応して与えられるパルス状のタイミング信号とを受け、前記保持前データと前記保持データとが同一の場合にのみ、前記タイミング信号に対応したパルス状の比較結果信号を出力する第2の組み合わせ論理回路とを有する請求項1記載の半導体記憶装置。 - 前記データ読み出し手段は、前記センス増幅手段の出力部と前記データ保持手段の入力部との間に介挿され、前記データを所定の期間遅延させて出力する遅延手段を備え、

前記データ比較手段は、

前記センス増幅手段の出力と前記遅延手段の出力とを受け、前記読み出し制御信号のうち、前記活性化信号が与えられている期間は、前記センス増幅手段の出力を出力し、前記非活性化信号が与えられている期間は、前記遅延手段の出力を出力する切り替え手段と、

前記読み出し制御信号を受け、前記活性化信号が与えられるタイミングに対応して前記タイミング信号を生成するパルス生成手段とを有し、

前記データ保持手段は、

直列に接続された少なくとも1の第1および第2の信号反転手段を有し、

前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、

前記保持データを検出することが可能なノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、

前記保持前データを検出することが可能なノードは、前記切り替え手段の出力ノードである請求項5記載の半導体記憶装置。 - 前記第1の組み合わせ論理回路はEXNOR回路であり、

前記第2の組み合わせ論理回路はAND回路である請求項6記載の半導体記憶装置。 - 前記所定の結果は、

前記保持前データと前記保持データとが異なる第1の結果と、

前記保持前データと前記保持データとが同一である第2の結果とを含み、

前記データ比較手段は、

一方の入力を前記保持データを検出することが可能な第1のノードに接続され、他方の入力を前記保持前データを検出することが可能な第2のノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の第1の比較結果信号を出力する第1の組み合わせ論理回路と、

一方の入力を前記保持データを検出することが可能な第3のノードに接続され、他方の入力を前記保持前データを検出することが可能な第4のノードに接続され、前記保持前データと前記保持データとが異なる場合にのみ、パルス状の信号を出力する第2の組み合わせ論理回路と、

前記第2の組み合わせ論理回路の出力と、前記活性化信号が与えられるタイミングに対応して与えられるパルス状のタイミング信号とを受け、前記保持前データと前記保持データとが同一の場合にのみ、前記タイミング信号に対応したパルス状の第2の比較結果信号を出力する第3の組み合わせ論理回路と、

前記第1の組み合わせ論理回の出力と、前記第3の組み合わせ論理回路の出力とを受け、前記保持前データと前記保持データとが異なる場合には前記第1の比較結果信号を、前記保持前データと前記保持データとが同一の場合には前記第2の比較結果信号を出力する第4の組み合わせ論理回路とを有する請求項1記載の半導体記憶装置。 - 前記データ読み出し手段は、前記センス増幅手段の出力部と前記データ保持手段の入力部との間に介挿され、前記データを所定の期間遅延させて出力する遅延手段を備え、

前記データ比較手段は、

前記センス増幅手段の出力と前記遅延手段の出力とを受け、前記読み出し制御信号のうち、前記活性化信号が与えられている期間は、前記センス増幅手段の出力を出力し、前記非活性化信号が与えられている期間は、前記遅延手段の出力を出力する切り替え手段と、

前記読み出し制御信号を受け、前記活性化信号が与えられるタイミングに対応して前記タイミング信号を生成するパルス生成手段とを有し、

前記データ保持手段は、

直列に接続された少なくとも1の第1および第2の信号反転手段を有し、

前記少なくとも1の第1の信号反転手段の入力ノードには前記センス増幅手段の出力が与えられ、前記少なくとも1の第2の信号反転手段の出力は前記外部出力端子に接続されるとともに、前記センス増幅手段の出力側に接続されてループ経路を形成し、

前記保持データを検出することが可能な第1のノードは、前記少なくとも1の第1の信号反転手段の出力ノードであり、

前記保持前データを検出することが可能な第2のノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、

前記保持データを検出することが可能な第3のノードは、前記少なくとも1の第1の信号反転手段の入力ノードであり、

前記保持前データを検出することが可能な第4のノードは、前記切り替え手段の出力ノードである請求項8記載の半導体記憶装置。 - 前記第1の組み合わせ論理回路はEXNOR回路であり、

前記第2の組み合わせ論理回路はEXNOR回路であり、

前記第3の組み合わせ論理回路はAND回路であり、

前記第4の組み合わせ論理回路はOR回路である請求項9記載の半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18761396A JP3846748B2 (ja) | 1996-07-17 | 1996-07-17 | 半導体記憶装置 |

| US08/756,822 US5710736A (en) | 1996-07-17 | 1996-11-26 | Semiconductor storage device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18761396A JP3846748B2 (ja) | 1996-07-17 | 1996-07-17 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1031893A JPH1031893A (ja) | 1998-02-03 |

| JP3846748B2 true JP3846748B2 (ja) | 2006-11-15 |

Family

ID=16209179

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP18761396A Expired - Fee Related JP3846748B2 (ja) | 1996-07-17 | 1996-07-17 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US5710736A (ja) |

| JP (1) | JP3846748B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100322535B1 (ko) * | 1999-06-29 | 2002-03-18 | 윤종용 | 소비전력을 최소화하는 메모리 장치 및 이를 이용한 데이터 기입 및 독출방법 |

| JP3723477B2 (ja) * | 2001-09-06 | 2005-12-07 | 松下電器産業株式会社 | 半導体記憶装置 |

| DE10219649C1 (de) | 2002-05-02 | 2003-11-27 | Infineon Technologies Ag | Differentielle Strombewerterschaltung und Leseverstärkerschaltung zum Bewerten eines Speicherzustands einer SRAM-Halbleiterspeicherzelle |

| JP2006053981A (ja) * | 2004-08-11 | 2006-02-23 | Fujitsu Ltd | 記憶装置、記憶装置リード方法 |

| US9710403B2 (en) * | 2011-11-30 | 2017-07-18 | Intel Corporation | Power saving method and apparatus for first in first out (FIFO) memories |

| US10978139B2 (en) | 2019-06-04 | 2021-04-13 | Qualcomm Incorporated | Dual-mode high-bandwidth SRAM with self-timed clock circuit |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2648840B2 (ja) * | 1988-11-22 | 1997-09-03 | 株式会社日立製作所 | 半導体記憶装置 |

| JPH02154392A (ja) * | 1988-12-07 | 1990-06-13 | Hitachi Ltd | 半導体集積回路 |

| JP3037377B2 (ja) * | 1990-08-27 | 2000-04-24 | 沖電気工業株式会社 | 半導体記憶装置 |

| JPH05274885A (ja) * | 1992-03-26 | 1993-10-22 | Nec Corp | 半導体記憶装置 |

| KR960009953B1 (ko) * | 1994-01-27 | 1996-07-25 | 삼성전자 주식회사 | 반도체 메모리 장치의 센스앰프 제어회로 |

| US5642317A (en) * | 1995-05-16 | 1997-06-24 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor memory device incorporating a test mechanism |

-

1996

- 1996-07-17 JP JP18761396A patent/JP3846748B2/ja not_active Expired - Fee Related

- 1996-11-26 US US08/756,822 patent/US5710736A/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH1031893A (ja) | 1998-02-03 |

| US5710736A (en) | 1998-01-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP0337202A2 (en) | Static random access memory with address transition detector | |

| EP0302795B1 (en) | Semiconductor memory circuit having a delay circuit | |

| US20040130926A1 (en) | Semiconductor memory device having potential amplitude of global bit line pair restricted to partial swing | |

| JPH05325569A (ja) | 半導体記憶装置 | |

| CN113539312B (zh) | 具有改进的抗亚稳态性的ddr5四相产生器 | |

| JPH10208484A (ja) | 半導体記憶装置のデータ読出回路及び半導体記憶装置 | |

| US5963484A (en) | High speed single-ended amplifier of a latched type | |

| KR100304195B1 (ko) | 외부클럭신호를가지는동기형반도체메모리장치 | |

| US5459689A (en) | Memory device with current path cut-off circuit for sense amplifier | |

| JP4200101B2 (ja) | カスコードセンス増幅器及び列選択回路及び動作方法。 | |

| JPH09320261A (ja) | 半導体記憶装置および制御信号発生回路 | |

| JP3846748B2 (ja) | 半導体記憶装置 | |

| JP4574772B2 (ja) | 検出回路および方法 | |

| JP2845264B2 (ja) | セルフカットオフ型センスアンプ回路 | |

| US5751649A (en) | High speed memory output circuitry and methods for implementing same | |

| CN211555473U (zh) | 感测放大器控制电路 | |

| JPH11191293A (ja) | データ読み出し回路 | |

| JP4383028B2 (ja) | 半導体記憶装置及びその制御方法 | |

| KR950005171B1 (ko) | 전류 미러 증폭회로 및 그의 구동 방법 | |

| EP0329177A2 (en) | Semiconductor memory device which can suppress operation error due to power supply noise | |

| US6920068B2 (en) | Semiconductor memory device with modified global input/output scheme | |

| JP3181759B2 (ja) | 半導体記憶装置 | |

| KR0179859B1 (ko) | 반도체 메모리의 출력 제어 회로 | |

| KR100373221B1 (ko) | 동기식메모리장치 | |

| JPH07287995A (ja) | 半導体メモリー素子のデータ出力装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060810 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060817 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060818 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |