JP3736070B2 - アクティブインダクタンス回路 - Google Patents

アクティブインダクタンス回路 Download PDFInfo

- Publication number

- JP3736070B2 JP3736070B2 JP26026597A JP26026597A JP3736070B2 JP 3736070 B2 JP3736070 B2 JP 3736070B2 JP 26026597 A JP26026597 A JP 26026597A JP 26026597 A JP26026597 A JP 26026597A JP 3736070 B2 JP3736070 B2 JP 3736070B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- differential

- phase shifter

- degree phase

- inductance

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Networks Using Active Elements (AREA)

Description

【発明の属する技術分野】

本発明は、ラジオ受信機、テレビジョン受信機、衛星放送受信機、ビデオテープレコーダ(VTR)、移動体通信機等に使用して好適なアクティブインダクタンス回路に関するものである。

【0002】

【従来の技術】

ラジオ受信機、テレビジョン受信機、衛星放送受信機、ビデオテープレコーダ(VTR)、移動体通信機等の機器においては、回路構成の一部としてフィルター回路が用いられている。そこでこのようなフィルター回路を、例えば集積回路(IC)の内部に構築する場合に、従来から抵抗器やコンデンサーは2端子の素子で形成することが可能であるものの、いわゆるインダクタンス成分をIC内に2端子で形成することは容易になし得るものではなかった。

【0003】

【発明が解決しようとする課題】

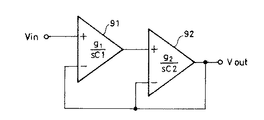

例えば図9は、バイクワッド回路と呼ばれるインダクタンス成分を形成するための回路の構成を示す。

【0004】

この回路において、2つの演算増幅器91、92が従属に設けられる。そして入力信号Vinが演算増幅器91の非反転入力に供給され、この演算増幅器91の出力が演算増幅器92の非反転入力に供給され、この演算増幅器92の出力信号Vout が取り出されると共に、この出力信号Vout が演算増幅器91、92の反転入力に帰還される。従ってこの回路において、演算増幅器91、92の2組の積分器によって構成する帰還回路によりインダクタンス成分が形成される。

【0005】

しかしながらこの回路においては、回路的に電圧帰還が掛かるために、いわゆるQの高いフィルター回路を形成する場合に、入力と出力とでオフセット電圧が生じ、回路設計が極めて困難になるものである。またこの回路の場合に、積分器の入出力はシングルであるために、回路全体もシングル入力のシングル出力となり、差動性に欠けるものとなる。このことは、特に回路のIC化を行う場合には致命的な欠陥であった。

【0006】

すなわち上述の回路においては、インダクタンス成分を単独でIC回路内に形成することができず、このため特に急峻なカットオフ特性を示すチェビシュフ型などの分布定数型のフィルターを組むことができないのである。

【0007】

この出願はこのような点に鑑みて成されたものであって、解決しようとする問題点は、従来の回路では、インダクタンス成分をIC回路内に単独の2端子素子として形成することができなかったというものである。

【0008】

【課題を解決するための手段】

このため本発明の請求項1においては、90度移相器の出力電圧を一組の差動対を介して電流に変換し、この電流を90度移相器の入力側に戻すようにしたものであって、これによれば、シングル入力時に完全な2端子のインダクタンス成分として動作させることができる。

【0009】

また、本発明の請求項3においては、90度移相器の出力電圧を2組の差動対で受け、その一方を電流に変換して90度移相器の入力側に戻すと共に、他方の出力を抵抗マトリクスを介して出力側に電圧帰還するようにしたものであって、これによれば、差動入力、差動出力の形態を持った4端子のインダクタンス回路を形成することができる。

【0010】

さらに本発明の請求項2、4においては、上述の請求項1、3のアクティブインダクタンス回路に電流可変回路を挿入することにより、得られるインダクタンスの値を可変とすることができる。

【0011】

【発明の実施の形態】

すなわち本発明の請求項1においては、正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量を付加することにより形成した差動型の90度移相器を有し、90度移相器の出力電圧を一組の差動対で受け、この差動対のエミッタ間抵抗により電圧−電流変換し、この電流を90度移相器の入力側に戻すことにより、90度移相器の入力側からみたインピーダンスを2端子のインダクタンスとして作用させるものである。

【0012】

また本発明の請求項2は、請求項1において差動対の電圧−電流変換部に電流可変回路を挿入することによりインダクタンスの値を可変とするものである。

【0013】

さらに本発明の請求項3においては、正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量を付加することにより形成した差動型の90度移相器を有し、90度移相器の出力電圧を第1及び第2の差動対で受け、この第1の差動対のエミッタ間抵抗により電圧−電流変換し、この電流を90度移相器の入力側に戻すと共に、この第2の差動対の出力部分をトランジスタのベースで受けて、90度移相器の出力側に抵抗を介して電圧帰還することにより、90度移相器の入力側からみたインピーダンスを差動入力及び差動出力の形態を持った4端子のインダクタンスとして作用させるものである。

【0014】

また本発明の請求項4は、請求項3において第1の差動対の電圧−電流変換部及び第2の差動対の出力部分にそれぞれ電流可変回路を挿入することによりインダクタンスの値を可変とするものである。

【0015】

ところで本願発明者は、先に負性抵抗を用いたハイインピーダンスバイアス回路にコンデンサを付加して構成した90度移相器を提案した(特願平9−237162号参照)。本発明のアクティブインダクタンス回路は、この90度移相器を応用したものである。

【0016】

【実施例】

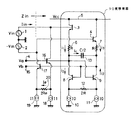

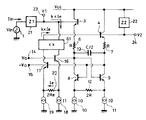

以下、図面を参照して本発明を説明するに、図1は本発明の請求項1によるアクティブインダクタンス回路の一例の構成を示す接続図である。

【0017】

この図1において、差動の入力信号Vinと−Vinを形成する信号源電圧源1、2が設けられ、これらの電圧源1、2の一端が互いに接続されてその接続中点が接地されると共に、信号源電圧源1、2の他端がそれぞれトランジスタ3、4のベースに接続される。さらにこれらのトランジスタ3、4のコレクタが電源Vccの電源路5に接続される。

【0018】

また、これらのトランジスタ3、4のエミッタが、それぞれ抵抗値Rの抵抗器6、7を通じて差動対を構成するトランジスタ8、9のコレクタに接続される。さらにこれらのトランジスタ8、9のエミッタがそれぞれ電流値I0 の電流源10、11を通じて接地されると共に、これらのトランジスタ8、9のエミッタ間に抵抗値2Rの抵抗器12が接続される。そしてこれらのトランジスタ8、9のコレクタ間に容量値C/2のコンデンサ13が接続される。

【0019】

さらにこれらのトランジスタ8、9のコレクタから出力信号Va とVb の出力端子14、15が導出される。

【0020】

また、これらの出力端子14、15がそれぞれトランジスタ16、17のベースに接続される。さらにこれらのトランジスタ16、17のエミッタがそれぞれ電流値I1 の電流源18、19を通じて接地されると共に、これらのトランジスタ16、17のエミッタ間に抵抗値2Re の抵抗器20が接続される。そしてこれらのトランジスタ16、17のコレクタが、それぞれ信号源電圧源1、2とトランジスタ3、4のベースの接続中点に接続される。

【0021】

この図1の回路において、線で囲った部分は90度移相器である。ただし上述の先願では、この90度移相器を電流ドライブとしたが、図1では電圧ドライブに構成している。

【0022】

そこでこの90度移相器において、各部の電流を図示のように値i1 、i2 、i3 、ic に定めると、トランジスタ3側では、i1 =ic +i2 から、

【数1】

となる。

【0023】

同様に、トランジスタ4側では、i3 =−ic +i2 から、

【数2】

となる。

【0024】

そこで〔数1〕〔数2〕から、これらを加算して

【数3】

となり、トランジスタ3、4のベースに差動の入力信号Vinと−Vinが印加された場合には、出力信号Va 、Vb の関係も位相が反転したものになる。

【0025】

そこでこの〔数3〕を〔数1〕に代入することによって、

【数4】

となる。

【0026】

よって、

【数5】

となり、入力信号Vinに対して、出力信号Va 、Vb は±90度位相のずれた出力となるものである。

【0027】

そこで図1の回路において、入力信号Vinの信号源電圧源1からみた入力インピーダンスを値Zinとすると、入力電流Iinは、

【数6】

である。

【0028】

よって、この〔数6〕と上述の〔数4〕とから

【数7】

となる。

【0029】

すなわちこの図1の回路において、入力インピーダンスZinは、〔数7〕から明らかなように入力信号Vinに対してインダクタンスL=C・R・Re が対接地間に入っているように見えるものである。言い換えると、入力信号Vin、−Vinの信号源電圧源1、2間に、インダクタンス2L=2・C・R・Re が存在しているように見えるものである。

【0030】

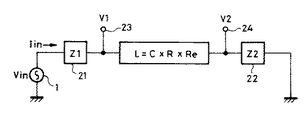

さらに、図1のアクティブインダクタンス回路が完全に2端子素子として存在していることを図2を用いて説明する。この図2は、入力信号Vinの信号源電圧源1とトランジスタ3のベースとの間に値Z1 のドライブインピーダンス21を挿入すると共に、トランジスタ4のベースを値Z2 のインピーダンス22にて終端したものである。

【0031】

そしてこの図2の回路において、トランジスタ3のベースポイント23の信号電位を値V1 、トランジスタ4のベースポイント24の信号電位を値V2 としたときに、値V1 、V2 間にインダクタンスが存在するように伝達関数が表されればよいことになる。

【0032】

そこで図2において、上述の〔数1〕から、

【数8】

となる。

【0033】

同様に、〔数2〕から、

【数9】

となる。

【0034】

従って、これらの〔数8〕〔数9〕から、

【数10】

となる。

【0035】

また、

【数11】

から、

【数12】

となる。

【0036】

一方、

【数13】

であるから、

【数14】

となる。

【0037】

すなわち

【数15】

ただし、

【数16】

であるから、

【数17】

となる。

【0038】

そしてこれらの式より、

【数18】

が求められる。

【0039】

すなわち、これらの〔数18〕から明らかなように、電圧値V1 、V2 は入力信号Vinに対して同一の分母で表され、さらに入力信号Vinに対してインピーダンスの順序もZ1 、L=C・R・Re 、Z2 となっている。以上のことから、上述の図1で形成されるアクティブインダクタンス回路は、完全に2端子素子として浮いた状態で形成されることがわかるものである。なお図3には、2端子素子としてのイメージを上述の図2の回路について示す。

【0040】

従ってこの装置において、90度移相器の出力電圧を一組の差動対を介して電流に変換し、この電流を90度移相器の入力側に戻すことによって、シングル入力時に完全な2端子のインダクタンス成分として動作させることができる。

【0041】

これによって、従来の回路では、インダクタンス成分をIC回路内に単独の2端子素子として形成することができなかったものを、本発明によればこの問題点を容易に解消することができるものである。

【0042】

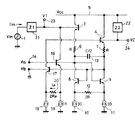

さらに、図4は本発明の請求項3によるアクティブインダクタンス回路の一例の構成を示す接続図である。

【0043】

この図4において、第2の差動の入力信号V2 と−V2 を形成する信号源電圧源31、32が設けられ、これらの電圧源31、32の一端が互いに接続されてその接続中点が接地されると共に、信号源電圧源31、32の他端がそれぞれトランジスタ33、34のベースに接続される。さらにこれらのトランジスタ33、34のコレクタが電源Vccの電源路5に接続される。そしてこれらのトランジスタ33、34のエミッタが、それぞれ抵抗値Rの抵抗器35、36を通じてトランジスタ8、9のベースに接続される。

【0044】

また出力信号Va とVb の出力端子14、15がそれぞれトランジスタ37、38のベースに接続される。さらにこれらのトランジスタ37、38のエミッタがそれぞれ電流値I1 の電流源39、40を通じて接地されると共に、これらのトランジスタ37、38のエミッタ間に抵抗値2Rp の抵抗器41が接続される。そしてこれらのトランジスタ37、38のコレクタが、それぞれ信号源電圧源31、32とトランジスタ33、34のベースの接続中点に接続される。

【0045】

なお図4において、この他の構成は上述の図1と同様とし、対応する部分には同一の符号を付して示す。ただし図4においては、説明の都合上、信号源電圧源1、2で形成される差動の入力信号を値V1 と−V1 とし、抵抗器12の抵抗値を2Rx とする。

【0046】

すなわちこの回路は、上述の図1に示したアクティブインダクタンス回路に、出力側の電圧を帰還する抵抗マトリクスを形成する部分と、電流出力を形成する差動対を追加したものである。そこでこの図4の回路において、信号源電圧源1から供給される入力電流を値Iin1 、信号源電圧源31から供給される入力電流を値Iin2 と置いて、入力電圧V1 、V2 間のインピーダンスを求める。

【0047】

ここで

【数19】

であることを踏まえると、

【数20】

となる。

【0048】

従って、

【数21】

から、

【数22】

となる。

【0049】

そこで入力電圧V1 、V2 間のインピーダンスを値Z12とすると、

【数23】

となる。ただし、2Rx =Rの条件を用いる。

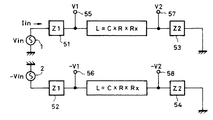

【0050】

さらに、図4のアクティブインダクタンス回路が完全に2端子対(差動4端子)素子として存在していることを図5を用いて説明する。この図5は、入力信号V1 と−V1 の信号源電圧源1、2とトランジスタ3、4のベースとの間に、それぞれ値Z1 のドライブインピーダンス51、52を挿入すると共に、トランジスタ33、34のベースをそれぞれ値Z2 のインピーダンス53、54にて終端したものである。

【0051】

そしてこの図5の回路において、それぞれのトランジスタ3のベースポイント55の信号電位を値V11、トランジスタ4のベースポイント56の信号電位を値V12、トランジスタ33のベースポイント57の信号電位を値V21、トランジスタ34のベースポイント58の信号電位を値V22としたときに、値V11、V12、V21、V22間にインダクタンスが存在するように伝達関数が表されればよいことになる。なおこの図5の回路において、トランジスタ8、9のエミッタ抵抗は、上述の条件に従ってRになっている。

【0052】

そこで上述の〔数20〕から、

【数24】

となる。

【0053】

従って、この〔数24〕から、

【数25】

となる。

【0054】

また、

【数26】

であるから、

【数27】

となる。

【0055】

また、

【数28】

であるから、

【数29】

となる。

【0056】

次に、

【数30】

であるから、

【数31】

となる。

【0057】

また、

【数32】

であるから、

【数33】

となる。

【0058】

よって、

【数34】

となる。

【0059】

さらに〔数27〕から、

【数35】

となる。

【0060】

従って

【数36】

【0061】

また、〔数29〕から、

【数37】

となる。

【0062】

すなわち、これらの〔数36〕〔数37〕から明らかなように、電圧値V11、V21は入力信号Vinに対して同一の分母で表され、さらに入力信号Vinに対してインピーダンスの順序もZ1 、L=C・R・Rp 、Z2 となっている。これは、電圧値V12、V22に対しても同様に表される。以上のことから、上述の図4で形成されるアクティブインダクタンス回路は、完全に2端子対(差動4端子)素子として浮いた状態で形成されることがわかるものである。なお図6には、2端子対素子としてのイメージを上述の図5の回路について示す。

【0063】

従ってこの装置において、90度移相器の出力電圧を2組の差動対で受け、その一方を電流に変換して90度移相器の入力側に戻すと共に、他方の出力を抵抗マトリクスを介して出力側に電圧帰還することによって、差動入力、差動出力の形態を持った4端子のインダクタンス回路を形成することができる。

【0064】

さらに図7、図8には電流可変回路を用いて、上述のアクティブインダクタンス回路のインダクタンス値を可変とするものである。すなわち図7においては、例えば上述の図2の回路についてトランジスタ16、17のコレクタに、k倍(kは+1から−1まで可変可能)の電流可変回路61を挿入する。

【0065】

この回路において、

【数38】

から、

【数39】

となる。

【0066】

従って、

【数40】

となる。

【0067】

これによって、端子23、24間に存在するインダクタンス値L1 は、

【数41】

となる。

【0068】

同様にして、図8においては、例えば上述の図5の回路についてトランジスタ16、17、37、38のコレクタに、それぞれk倍(kは+1から−1まで可変可能)の電流可変回路61、62を挿入する。これによって、端子55、56、57、58間に存在するインダクタンス値L2 は、

【数42】

となる。

【0069】

従ってこの装置において、上述のアクティブインダクタンス回路に電流可変回路を挿入することにより、得られるインダクタンスの値を可変とすることができる。

【0070】

こうして上述のアクティブインダクタンス回路によれば、正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量を付加することにより形成した差動型の90度移相器を有し、90度移相器の出力電圧を一組の差動対で受け、この差動対のエミッタ間抵抗により電圧−電流変換し、この電流を90度移相器の入力側に戻すことにより、90度移相器の入力側からみたインピーダンスを2端子のインダクタンスとして作用させるものである。

【0071】

また、上述の回路において、差動対の電圧−電流変換部に電流可変回路を挿入することによりインダクタンスの値を可変とするものである。

【0072】

さらに上述のアクティブインダクタンス回路によれば、正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量を付加することにより形成した差動型の90度移相器を有し、90度移相器の出力電圧を第1及び第2の差動対で受け、この第1の差動対のエミッタ間抵抗により電圧−電流変換し、この電流を90度移相器の入力側に戻すと共に、この第2の差動対の出力部分をトランジスタのベースで受けて、90度移相器の出力側に抵抗マトリクスを用いて電圧帰還することにより、90度移相器の入力側からみたインピーダンスを差動入力及び差動出力の形態を持った4端子のインダクタンスとして作用させるものである。

【0073】

また、上述の回路において、第1の差動対の電圧−電流変換部及び第2の差動対の出力部分にそれぞれ電流可変回路を挿入することによりインダクタンスの値を可変とするものである。

【0074】

すなわち本発明のアクティブインダクタンス回路によれば、従来、単独でIC回路内に作ることが困難であったインダクタンス素子を、完全な2端子素子として作りだすことができる。従ってその2端子素子となったインダクタンスの前後にドライブインピーダンスと終端インピーダンスを置けることになり、分布定数回路の選択特性の実現が可能となり、急峻な特性を得ることができる。

【0075】

また、このインダクタンスを完全な4端子対とすることにより、差動入力、差動出力のフィルターを完成することができ、これにより従来のアクティブフィルターで問題であった入力と出力のDCオフセットが完全になくなり、高いQのアクティブフィルターを作ることが可能になる。

【0076】

また差動であるため、従来のアクティブフィルターでは信号電流がアースを回って回路に影響を与える恐れがあったが、本発明の回路によれば差動とすることにより全ての信号がIC回路内にとどまり、回路の性能を向上させることができる。さらに本発明の回路によれば、PNPトランジスタを使用しないので、低電圧に充分対応できる。

【0077】

また、全て差動で信号が流れるため、IC内に使用するコンデンサを全て差動的に付加することができ、シングル動作時に比して半分の容量値で済むことになり、ICチップの面積を大幅に縮小することができる。

【0078】

従ってこれらの理由により、結果として商品の性能向上、製造コストの削減、基板面積の縮小等の効果をもたらすことができる。

【0079】

さらにアクティブインダクタンスを作りだすことによって、例えば位相ロックループや、AM復調器、FM復調器、フィルター等の用途にも本発明を応用することができるものである。

【0080】

【発明の効果】

従って本発明の請求項1によれば、正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量を付加することにより形成した差動型の90度移相器を有し、90度移相器の出力電圧を一組の差動対で受け、この差動対のエミッタ間抵抗により電圧−電流変換し、この電流を90度移相器の入力側に戻すことにより、90度移相器の入力側からみたインピーダンスを2端子のインダクタンスとして作用させることができるものである。

【0081】

また、本発明の請求項3によれば、90度移相器の出力電圧を2組の差動対で受け、その一方を電流に変換して90度移相器の入力側に戻すと共に、他方の出力を抵抗マトリクスを介して出力側に電圧帰還することによって、差動入力、差動出力の形態を持った4端子のインダクタンス回路を形成することができるものである。

【0082】

さらに本発明の請求項2、4によれば、上述のアクティブインダクタンス回路に電流可変回路を挿入することにより、得られるインダクタンスの値を可変とすることができるものである。

【図面の簡単な説明】

【図1】本発明の請求項1のアクティブインダクタンス回路の一例の構成図である。

【図2】その説明のための図である。

【図3】その説明のための図である。

【図4】本発明の請求項3のアクティブインダクタンス回路の一例の構成図である。

【図5】その説明のための図である。

【図6】その説明のための図である。

【図7】本発明の請求項2のアクティブインダクタンス回路の一例の構成図である。

【図8】本発明の請求項4のアクティブインダクタンス回路の一例の構成図である。

【図9】従来の回路の説明のための図である。

【符号の説明】

1,2…差動の入力電圧Vinと−Vinを形成する信号源電圧源、3,4…電圧ドライブを行うトランジスタ、5…電源Vccの電源路、6,7…抵抗値2Re の抵抗器、8,9…差動対を構成するトランジスタ、10,11…電流値I0 の電流源、12…抵抗値2Rの抵抗器、13…容量値C/2のコンデンサ、14,15…出力電圧Va とVb の出力端子、16,17…トランジスタ、18,19…電流値I1 の電流源、20…抵抗値2Re の抵抗器

Claims (4)

- 正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量を付加することにより形成した差動型の90度移相器を有し、

上記90度移相器の出力電圧を一組の差動対で受け、この差動対のエミッタ間抵抗により電圧−電流変換し、この電流を上記90度移相器の入力側に戻すことにより、

上記90度移相器の入力側からみたインピーダンスを2端子のインダクタンスとして作用させる

ことを特徴とするアクティブインダクタンス回路。 - 請求項1記載のアクティブインダクタンス回路において、

上記差動対の電圧−電流変換部に電流可変回路を挿入することにより上記インダクタンスの値を可変とする

ことを特徴とするアクティブインダクタンス回路。 - 正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量を付加することにより形成した差動型の90度移相器を有し、

上記90度移相器の出力電圧を第1及び第2の差動対で受け、この第1の差動対のエミッタ間抵抗により電圧−電流変換し、この電流を上記90度移相器の入力側に戻すと共に、この第2の差動対の出力部分をトランジスタのベースで受けて、上記90度移相器の出力側に抵抗を介して電圧帰還することにより、

上記90度移相器の入力側からみたインピーダンスを差動入力及び差動出力の形態を持った4端子のインダクタンスとして作用させる

ことを特徴とするアクティブインダクタンス回路。 - 請求項3記載のアクティブインダクタンス回路において、

上記第1の差動対の電圧−電流変換部及び上記第2の差動対の出力部分にそれぞれ電流可変回路を挿入することにより上記インダクタンスの値を可変とする

ことを特徴とするアクティブインダクタンス回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP26026597A JP3736070B2 (ja) | 1997-09-25 | 1997-09-25 | アクティブインダクタンス回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP26026597A JP3736070B2 (ja) | 1997-09-25 | 1997-09-25 | アクティブインダクタンス回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1197981A JPH1197981A (ja) | 1999-04-09 |

| JP3736070B2 true JP3736070B2 (ja) | 2006-01-18 |

Family

ID=17345658

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP26026597A Expired - Fee Related JP3736070B2 (ja) | 1997-09-25 | 1997-09-25 | アクティブインダクタンス回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3736070B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4867352B2 (ja) * | 2006-01-10 | 2012-02-01 | ソニー株式会社 | フィルタ回路及び受信回路 |

-

1997

- 1997-09-25 JP JP26026597A patent/JP3736070B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH1197981A (ja) | 1999-04-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5124592A (en) | Active filter | |

| JP2766264B2 (ja) | 差動増幅回路 | |

| US6335655B1 (en) | Filter circuit | |

| US6664854B2 (en) | Base band filter including a semiconductor integrated circuit | |

| JP3316038B2 (ja) | 演算トランスコンダクタンス増幅器・キャパシタ対用の周波数同調システム | |

| JPS626722Y2 (ja) | ||

| EP0827275B1 (en) | Frequency-dependent resistor | |

| JP3736070B2 (ja) | アクティブインダクタンス回路 | |

| EP0078574B1 (en) | All-pass circuit arrangement | |

| JPH02309710A (ja) | リープフロッグ・フィルタ | |

| EP0410536B1 (en) | Combined current differencing and operational amplifier circuit | |

| JP3700338B2 (ja) | 90度移相器 | |

| JP4210873B2 (ja) | インピーダンス変換回路、映像機器、オーディオ機器及び通信装置 | |

| JPH0936702A (ja) | アクティブロ−パスフィルタ | |

| JPH0626297B2 (ja) | 2次アクテイブ位相等価器 | |

| JPH10198909A (ja) | 磁気情報読取り装置 | |

| JPH11103237A (ja) | ハイインピーダンス回路 | |

| US5302910A (en) | FM detector circuit with error voltage applied to phase shifting circuit | |

| JPH11205085A (ja) | バンドパスフィルタ回路、映像機器、オーディオ機器及び通信装置 | |

| JP2962936B2 (ja) | 共振回路 | |

| JPH0114726B2 (ja) | ||

| JP2991727B2 (ja) | アクティブフィルタ回路 | |

| JPS623937Y2 (ja) | ||

| JP2000114929A (ja) | インピーダンス回路及び移相器 | |

| JP3148458B2 (ja) | アクティブフィルタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050301 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050621 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050805 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20051004 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20051017 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091104 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |