JP3720275B2 - 画像表示パネル、画像表示装置、並びに画像表示方法 - Google Patents

画像表示パネル、画像表示装置、並びに画像表示方法 Download PDFInfo

- Publication number

- JP3720275B2 JP3720275B2 JP2001117453A JP2001117453A JP3720275B2 JP 3720275 B2 JP3720275 B2 JP 3720275B2 JP 2001117453 A JP2001117453 A JP 2001117453A JP 2001117453 A JP2001117453 A JP 2001117453A JP 3720275 B2 JP3720275 B2 JP 3720275B2

- Authority

- JP

- Japan

- Prior art keywords

- gradation processing

- pseudo gradation

- image display

- video signal

- display panel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2011—Display of intermediate tones by amplitude modulation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0408—Integration of the drivers onto the display substrate

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0297—Special arrangements with multiplexing or demultiplexing of display data in the drivers for data electrodes, in a pre-processing circuitry delivering display data to said drivers or in the matrix panel, e.g. multiplexing plural data signals to one D/A converter or demultiplexing the D/A converter output to multiple columns

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2044—Display of intermediate tones using dithering

- G09G3/2051—Display of intermediate tones using dithering with use of a spatial dither pattern

Description

【発明の属する技術分野】

本発明は、複数の走査信号線と複数のデータ信号線とが互いに直交する方向に配設され、上記両信号線の各交差部に画素が配置されるマトリクス型の画像表示装置に関するものであり、特に、配線の駆動回路を画素と同一の基板上に形成して構成する駆動回路一体型の画像表示装置に関するものである。

【0002】

【従来の技術】

従来の画像表示装置の一つとして、アクティブマトリクス駆動方式の液晶表示装置が知られている。この液晶表示装置は、図23に示すように、画素アレイ(ARY)101、走査信号線駆動回路(GD)102、データ信号線駆動回路(SD)103、タイミング信号生成回路(CTL)104、および映像信号処理回路(SIG)105を備えている。

【0003】

画素アレイ101には、互いに交差する多数の走査信号線GLと多数のデータ信号線SLとが備えており、各走査信号線GLとデータ信号線SLとの交点に対応して画素(PIX)106が設けられる。すなわち、隣接する2本の走査信号線GLと隣接する2本のデータ信号線SLとで囲まれた各領域に、各画素106が設けられ、マトリクス状に配列された画素106によって表示画面が構成される。

【0004】

走査信号線駆動回路102は、タイミング信号生成回路104から入力されるクロック信号GCK等のタイミング信号に同期して、走査信号線GLを順次選択し、画素106内にあるスイッチング素子の開閉を制御することにより、各データ信号線SLに書き込まれた映像信号(データ)を各画素106に書き込むとともに、各画素106に書き込まれたデータを保持させる働きをする。

【0005】

データ信号線駆動回路103は、タイミング信号生成回路104から入力されるクロック信号SCK等のタイミング信号に同期して、映像信号処理回路105から入力される映像信号DATをサンプリングし、必要に応じて増幅して、各データ信号線SLに書き込む働きをする。

【0006】

図23における各画素106は、図24に示すように、スイッチング素子である電界効果トランジスタSWと、画素容量(液晶容量CL、および必要によって付加される補助容量CSTよりなる)とによって構成される。図24において、画素容量の一方の電極はトランジスタSWのドレイン及びソースを介してデータ信号線SLと接続される。トランジスタSWのゲートは、走査信号線GLに接続される。また、画素容量の他方の電極は、全画素に共通の共通電極線に接続される。そして、各液晶容量CLに印加される電圧により、液晶の透過率または反射率が変調され、表示に供する。

【0007】

また、近年、液晶表示装置の小型化や高解像度化、実装コストの低減などのために、画素アレイ101と駆動回路102,103とを、同一基板上に一体形成する技術が開発されている。

【0008】

このような駆動回路一体型の液晶表示装置では、現在広く用いられている透過型液晶表示装置を構成する場合、その基板に透明基板である石英基板やガラス基板を使う必要がある。また、石英基板やガラス基板上に回路を構成する場合、基板の耐熱性の観点より、600℃以下の製造温度で製造が可能な多結晶シリコン薄膜トランジスタが能動素子として用いられる。

【0009】

図25は、そのような駆動回路一体型の液晶表示装置の例を示した図である。上記液晶表示装置では、同一の基板(SUB)107上において、画素アレイ101、走査信号線駆動回路102、データ信号線駆動回路103が形成されている。また、上記基板107上には、さらにプリチャージ回路(PC)108が備えられているが、これは、多結晶シリコン薄膜トランジスタにより構成されたデータ信号線駆動回路103の駆動能力が小さく、データ信号線SLへのデータの書き込みを補助する必要がある場合に設けられるものである。

【0010】

次に、データ信号線の駆動方式について説明する。アナログ方式の駆動方式としてはアナログ点順次駆動方式、アナログ線順次駆動方式があり、デジタル方式の駆動方式としては、セレクタ型駆動方式、R−DAC型駆動方式、C−DAC型駆動方式がある。

【0011】

これらの駆動方式のうち、アナログ線順次駆動方式、セレクタ型駆動方式、R−DAC型駆動方式、C−DAC型駆動方式については、駆動回路一体型の液晶表示装置に採用しようとする場合、デザインルールが大きく基板上への配置が困難、多階調表示への対応が困難、あるいは表示品位が低下するといった問題がある。

【0012】

すなわち、駆動回路一体型の液晶表示装置では、上述したように、回路中の半導体層において多結晶シリコン薄膜が用いられるが、多結晶シリコンは単結晶シリコンに比べ基板上での配置面積が大きくなる。

【0013】

これに対し、アナログ線順次駆動方式では、入力された映像信号を増幅するための高精度のアンプが必要であるが、このアンプを半導体材料に多結晶シリコンを用いて高精度かつ小面積に形成することは困難である。

【0014】

また、R−DAC型駆動方式、C−DAC型駆動方式では、多階調表示を行なうための基準電圧を抵抗分割または容量分割による分圧にて生成しているが、これらの分圧手段に用いられる抵抗や容量の素子を多結晶シリコン薄膜にて形成する場合に、これらの素子を小面積に形成することは困難である。また、多結晶シリコン薄膜にて形成される抵抗や容量では、特性のばらつきが大きくなり、設計通りの分圧比が得られず表示品位が低下する。尚、半導体材料に多結晶シリコンを用いた素子にて駆動回路を構成する場合、各素子の特性のばらつきによる表示品位の低下を抑制するためには、駆動回路をロジック素子のみで構成することが必要である。

【0015】

また、セレクタ型駆動方式は、外部から入力される基準電圧を、映像信号に応じて選択回路にてデータ信号線SLに接続する構成であり、ロジック回路と転送スイッチのみで構成されるため、デジタル方式の駆動方式の中では最も単純な回路構成を有している。しかし一方で、外部に表示階調に対応するだけの基準電圧源が必要であるため、実際の使用に際しては8ないし16階調が限界であり、表示階調が多い場合には極めて不利となる。

【0016】

以上の理由により、駆動回路一体型の液晶表示装置において、さらに多階調表示を行なおうとする場合には、アナログ線順次駆動方式、セレクタ型駆動方式、R−DAC型駆動方式、C−DAC型駆動方式は採用されず、アナログ点順次駆動方式が最も一般的に用いられている。

【0017】

ここで、アナログ点順次駆動方式でのデータ信号線駆動回路について説明する。アナログ点順次駆動方式のデータ信号線駆動回路においては、図26に示すように、入力された映像信号DATを、シフトレジスタを構成するフリップフロップの各段FFの出カパルスに同期させてサンプリング回路ASを開閉することにより、データ信号線SLに書き込む。

【0018】

すなわち、アナログ点順次駆動方式のデータ信号線駆動回路では、外部から入力された映像信号DATをデータ信号線に転送するだけであるので、その回路構成は極めて単純であり、駆動回路一体型の液晶表示装置への適用が可能であると共に、表示品位を低下させることなく多階調表示が可能である。

【0019】

【発明が解決しようとする課題】

ところが、アナログ点順次駆動方式のデータ信号線駆動回路では、外部に駆動能力の高いアナログ映像信号出力回路を備える必要があり、システムとしての消費電力が大きくなるとともに、コストも大幅に上昇するといった問題がある。

【0020】

さらに、上述のアナログ点順次駆動方式の駆動回路は、デジタルインターフェースを備えていない。このため、液晶表示装置がデジタル信号の入力によって駆動されるものであっても、画素アレイと駆動回路とが同一基板上に形成されてなる表示パネルの外にD/A(digital/analog)変換回路を備える必要があり、さらなるコストアップを招来する。

【0021】

ここで、デジタルインターフェースを備えた駆動方式であって、かつ、半導体材料に多結晶シリコンを用いた場合でも高い表示品位での多階調表示が可能であり、消費電力も小さい駆動方式として、疑似階調処理を用いた駆動方式がある。

【0022】

ここで、疑似階調処理を用いた従来の駆動回路の構成例を図27に示す。疑似階調処理を用いたデータ信号線駆動回路においては、図27に示すように、入力されたデジタル映像信号DATは、シフトレジスタを構成するフリップフロップの各段FFの出力パルスに同期させてラッチLATに取り込む。そして、デコーダ回路DECにより取り込んだ映像信号をデコードし、デコードされた映像信号に対し、各ライン毎に疑似階調処理を行なう。

【0023】

ここで、図27の構成における疑似階調処理を簡単に説明すると以下の通りである。ここでの疑似階調処理は、固定のノイズパターンを画像データに重畳させた後、下位ビットを切り捨てることにより、低ビットの駆動回路でより多ビットの画像を擬似的に表示するものであり、疑似階調処理の中でも最も構成のシンプルなものの1つである。高精細の画像表示装置では、擬似的に階調数を増す手法は、画質の劣化が極めて小さいため、影響は問題にならない場合が多い。

【0024】

図27の構成では、入力された映像信号DATIとメモリROMに記憶されている固定ノイズパターンとを、各データ信号線に出力される映像信号毎に、加算器ADDERで加算し、例外処理回路OFPでオーバーフロー時などの例外処理を行った後、量子化回路QNTで下位ビットを切り捨てている。こうして、疑似階調処理の施された映像信号は、該映像信号に対応する基準電圧VREFを、選択回路SELでデータ信号線SLに接続する。

【0025】

以上のように、疑似階調処理を用いた駆動回路では、デジタルインターフェースを備えていると同時に、かつ、半導体材料に多結晶シリコンを用いた場合でも高い表示品位での多階調表示が可能であり、消費電力も比較的小さい。

【0026】

しかしながら、疑似階調処理に係る構成、すなわち、加算器ADDER,例外処理回路OFP,量子化回路QNTが各データ信号線毎に設けられているため、画素アレイと駆動回路とを同一基板上に形成する駆動回路一体型の表示装置では、駆動回路の構成が極めて複雑となる。このため、半導体材料に多結晶シリコンを用いた素子にて駆動回路を構成する場合、駆動回路のサイズが大きくなりすぎて実際の製造は困難であるといった問題がある。

【0027】

本発明は、上記の問題点を解決するためになされたもので、その目的は、疑似階調処理を用いた駆動回路において、その回路構成を簡略なものとし、画素アレイと駆動回路とを同一の基板上に形成する駆動回路一体型の画像表示装置を提供することにある。

【0028】

【課題を解決するための手段】

本発明の画像表パネルは、上記の課題を解決するために、画像を表示する複数の画素からなる画素アレイと、該画素アレイに映像信号を供給するデータ信号線駆動回路とを、同一の基板上に有する画像表示パネルにおいて、上記データ信号線駆動回路は、画素アレイ上の画素に映像信号を送出するn本のデータ信号線を駆動するものであると共に、各データ信号線に送出される映像信号に対して疑似階調処理を施す、データ信号線の数よりも少ないm段の疑似階調処理手段を備えており、各疑似階調処理手段は、データ信号線に対してmライン毎に疑似階調処理された映像信号を出力し、上記疑似階調処理手段は、一定周期で繰り返される固定パターンデータの信号を映像信号に加算することにより重畳する処理と、重畳された映像信号の下位ビットを切り捨てる処理とを行なうことを特徴としている。

【0029】

上記の構成によれば、n本のデータ信号線を駆動するデータ信号線駆動回路を画素アレイと同一基板上の形成する画像表示パネルにおいて、疑似階調処理手段をデータ信号線の本数(n本)よりも少ないm段とし、複数の異なるデータ信号線に出力される映像信号に対して疑似階調処理手段を共通化することで、データ信号線駆動回路の構成を簡略化でき、駆動回路一体型の画像表示パネルに適用が可能となる簡単な回路構成にて多階調表示が可能となる。

【0030】

また、疑似階調処理手段において1ライン分の映像信号にかかる疑似階調処理時間は、1ライン分の映像信号の入力にかかる時間よりも長いことが通常であるが、データ信号線に対してmライン毎に疑似階調処理された映像信号を出力することで、各疑似階調処理手段では、1ライン分の映像信号の疑似階調処理において、映像信号の入力周期のm倍の時間の処理時間を確保することができる。

上記の構成によれば、映像信号に重畳する信号として一定周期で繰り返される固定パターンデータの信号を用いることにより、固定パターンデータを記憶する記憶手段の容量を抑制できる。また、複雑な演算処理を必要とせず、非常に簡単に疑似階調処理を実現することができるため、駆動回路一体型の画像表示装置への適用が容易となる。

【0031】

また、上記画像表示パネルでは、第1の構成として、上記データ信号線駆動回路は、第1のシフトレジスタの出力に同期して、順次映像信号を取り込むm段の第1のラッチ手段と、上記ラッチ回路にて取り込まれた映像信号を並列化するm段の並列化手段と、上記疑似階調処理手段によって疑似階調処理が施された映像信号を、第2のシフトレジスタの出力に同期して、順次取り込むn段の第2のラッチ手段とを備えており、上記各疑似階調処理手段は、上記並列化手段にて並列化された映像信号に対して疑似階調処理を施すと共に、上記各疑似階調処理手段にて疑似階調処理を施された映像信号は、上記第1のシフトレジスタよりも動作周波数の小さい第2のシフトレジスタの出力に同期させて、上記第2のラッチ手段に対し、mライン分の映像信号毎に一括して取り込まれた後、各データ信号線に送出される構成とすることができる。

【0032】

上記第1の構成によれば、第2のシフトレジスタの各段が、複数のデータ信号線(m本)に対応しているので、第2のシフトレジスタの段数をデータ信号線の本数(n本)の1/mにすることができ、駆動回路の規模を小さくすることが可能となる。また、第2のシフトレジスタの周波数が第1のシフトレジスタの周波数の1/mになるので、第2のラッチ手段でデータ信号線にデータ信号線にデータを送出する時間を長く取ることができる。

【0033】

また、上記画像表示パネルでは、第2の構成として、上記データ信号線駆動回路は、第1のシフトレジスタの出力に同期して、順次映像信号を取り込むm段の第1のラッチ手段と、上記疑似階調処理手段によって疑似階調処理が施された映像信号を、第2のシフトレジスタの出力に同期して、順次取り込むn段の第2のラッチ手段とを備えており、上記各疑似階調処理手段は、上記第1のラッチ手段から上記第1のシフトレジスタの出力と同周期で映像信号を取り込み、該映像信号に対して疑似階調処理を施すと共に、上記各疑似階調処理手段にて疑似階調処理を施された映像信号は、上記第1のシフトレジスタと同一の動作周波数にて動作する第2のシフトレジスタの出力に同期させて、上記第2のラッチ手段に対し、1ライン分の映像信号毎に取り込まれた後、各データ信号線に送出される構成とすることができる。

【0034】

上記第2の構成によれば、第2のシフトレジスタからの複数の出力信号の和を用いることにより、第2のラッチ手段でデータ信号線にデータ信号線にデータを送出する時間を長く取ることができる。また、この構成では、第2のシフトレジスタを制御するクロック信号として、第1のシフトレジスタを制御するクロック信号と同じ信号を用いることができるので、新たな信号を生成する回路が不要となる。さらに、データ信号線へのデータの送出が連続的に行なわれるので、複数のデータを一括して送出される場合に危惧されるブロック毎の境界(表示上の不具合)が生じにくいといったメリットがある。

【0035】

また、上記第1の構成の画像表示パネルでは、上記第1のシフトレジスタの動作周波数は、第2のシフトレジスタの動作周波数の整数倍であることが好ましい。

【0036】

上記の構成によれば、第1のシフトレジストの動作周波数を与えるクロック信号と、第2のシフトレジスタの動作周波数を与えるクロック信号とのタイミング関係が単純になり、データ信号線駆動回路全体の構成が簡単になる。

【0037】

また、上記第1の構成の画像表示パネルでは、上記第2のシフトレジスタを駆動させるクロック信号は、第1のシフトレジスタの最終段からの出力信号より生成される構成とすることが好ましい。

【0038】

上記の構成によれば、第2のフトレジスタを駆動するためのクロック信号を、データ信号線駆動回路の外部から別途入力する必要がなくなり、データ信号線駆動回路全体の構成が簡単になる。

【0039】

また、上記画像表示パネルでは、上記疑似階調処理手段にて疑似階調処理が施されたデジタル映像信号を、アナログ映像信号に変換するデジタル/アナログ変換手段を備えており、上記デジタル/アナログ変換手段による変換処理が、上記第2のラッチ手段によるラッチ後に行なわれる構成とすることができる。

【0040】

上記の構成によれば、デジタル/アナログ変換手段による映像信号の変換処理が、上記第2のラッチ手段によるラッチ後に行なわれるため、上記映像信号は、データ信号線への出力の直前までデジタル信号として扱われることとなる。このため、上記映像信号が雑音や微妙なタイミングずれの影響を受けることがなく、高画質の表示を得ることができる。

【0041】

また、上記画像表示パネルでは、上記疑似階調処理手段にて疑似階調処理が施されたデジタル映像信号を、アナログ映像信号に変換するデジタル/アナログ変換手段を備えており、上記デジタル/アナログ変換手段による変換処理が、疑似階調処理手段による疑似階調処理の後、かつ上記第2のラッチ手段によるラッチ前に行なわれる構成とすることができる。

【0042】

上記の構成によれば、デジタル/アナログ変換手段による映像信号の変換処理が、疑似階調処理手段による疑似階調処理の後、かつ上記第2のラッチ手段によるラッチ前に行なわれるため、デジタル/アナログ変換手段の数を疑似階調処理手段と同じくm段とすることができ、データ信号線駆動回路の構成を簡略化することができる。また、デジタル/アナログ変換手段の回路構成は、シフトレジスタと、インバータやNAND等の簡単なゲートとアナログスイッチとから構成でき、非常に単純でコンパクトに形成できる。

【0045】

また、上記画像表示パネルでは、上記固定パターンデータは、データ信号線の配列方向における幅が、mの整数倍のライン数に相当する構成とすることができる。

【0046】

上記の構成によれば、上記固定パターンデータの繰り返し周期が疑似階調処理手段の処理周期(データ信号線のmライン)の整数倍の関係となるため、各疑似階調処理手段は一部の固定パターンデータのみを具備すればよく、固定パターンデータを格納する記憶手段の容量を少なくすることができる。

【0047】

また、上記画像表示パネルでは、上記疑似階調処理手段は、上記固定パターンデータを格納する記憶手段を備えており、各疑似階調処理手段内の記憶手段(例えば、ROM)は、各疑似階調処理手段に対応するデータ信号線用の固定パターンデータのみを格納している構成とすることができる。

【0048】

上記の構成によれば、各疑似階調処理手段に内蔵すべき記憶手段のデータ量を最小化することができ、また、記憶手段からの固定パターンデータの読み出しを管理するメモリー制御回路の構造や駆動方法も単純化される。

【0049】

また、上記画像表示パネルでは、上記疑似階調処理手段は、上記固定パターンデータの垂直方向の周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を一定量だけずらす構成とすることができる。

【0050】

上記の構成によれば、映像信号に重畳される固定パターンデータの信号によるブロック状の疑似パターンが認識されにくくなるため、表示品位を向上することができる。

【0051】

また、上記画像表示パネルでは、上記疑似階調処理手段は、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を一定量だけずらす構成とすることができる。

【0052】

上記構成によれば、映像信号に重畳される固定パターンデータの信号によるブロック状の疑似パターンが認識されにくくなるため、表示品位を向上することができる。

【0053】

また、固定パターンデータをずらす周期については、1フレーム期間毎とする場合が、同一の固定パターンの連続が最も短く、ブロック状の疑似パターンを認識しにくくするためには最も効果が高い。但し、固定パターンデータをずらす周期を2フレーム期間毎とした場合には、疑似パターンを認識しにくくして表示品位を向上すると共に、液晶の交流駆動に対応して、液晶に印加される電圧のDC成分が相殺されるため、液晶材料の劣化が抑えられ、表示装置の信頼性向上に有効である。

【0054】

また、上記画像表示パネルでは、上記疑似階調処理回路は、上記固定パターンデータの垂直方向の周期毎、または、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を1/k(kは2以上の整数)周期分だけずらす構成とすることができる。

【0055】

上記の構成によれば、映像信号へ重畳される固定パターンデータの読み出しタイミングの制御(読み出し開始アドレスの切替え)が簡単になるため、疑似階調処理手段の構成が簡単となる。

【0056】

また、上記画像表示パネルでは、上記疑似階調処理手段は、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータを変化させる構成とすることができる。

【0057】

上記の構成によれば、映像信号に重畳する固定パターンデータを水平方向にずらす場合では、ブロック状の疑似パターンの移動が認識される可能性があるが、フレーム毎に全く異なる固定パターンデータを用いることにより、ブロック状の疑似パターンがさらに認識されにくくなるため、表示品位をより一層向上させることができる。

【0058】

もちろん、固定パターンデータをずらす周期については、1フレーム期間毎とする場合にブロック状の疑似パターンを認識しにくくするうえで最も効果が高く、2フレーム期間毎とした場合に、表示品位を向上と表示装置の信頼性向上と同時にを図ることができる。

【0059】

また、上記画像表示パネルでは、上記疑似階調処理手段は、映像信号に重畳する固定パターンデータとして、一定のフレーム周期毎に、同一の固定パターンデータを繰り返す構成とすることができる。

【0060】

上記の構成によれば、固定パターンデータの種類を制限することができ、固定パターンデータを格納する記憶手段の容量を少なくすることができる。

【0061】

また、上記画像表示パネルでは、上記デジタル/アナログ変換手段は、疑似階調処理を施された映像信号に応じて、複数の基準電圧源の内の1つを選択する構成とすることができる。

【0062】

上記の構成によれば、複数の基準電圧源の内の1つを選択するセレクタ型のデジタル駆動方式をデジタル/アナログ変換手段に採用することにより、単純な構成で多階調表示を実現することができる。

【0063】

また、各データ信号線毎にアンプやR−DAC,C−DACを内蔵していないので、特性バラツキによる垂直方向の表示ムラの発生を避けることができる。更に、定常電流が流れる回路を採用していないので、消費電力も低減される。

【0064】

また、上記画像表示パネルでは、上記複数の基準電圧源は、外部から入力されるより少数の基準電圧源より、上記基板上にて生成される構成とすることができる。

【0065】

上記の構成によれば、外部の基準電圧源の数を削減することができるため、データ信号線駆動回路全体の構成を簡略化することができる。また、データ信号線毎でなく、データ信号線駆動回路全体に対して、1つの基準電圧源生成回路を備えることで、特性バラツキによる縦縞状の表示不良を抑制できる。

【0066】

また、上記画像表示パネルでは、上記疑似階調処理手段における疑似階調処理の動作および非動作は、外部より入力される制御信号によって切り替えられる構成とすることができる。

【0067】

上記の構成によれば、表示階調の少ない画像表示の場合(疑似階調処理による効果が得られない)には、疑似階調処理回路を動作させないようにすることができ、より低消費電力での画像表示を実現することができる。

【0068】

また、上記画像表示パネルでは、上記疑似階調処理手段における疑似階調処理の動作および非動作は、外部より入力される制御信号によって切り替えられる構成とすることができる。

【0069】

上記の構成によれば、疑似階調処理手段の動作を外部より制御することにより、表示画像の種類や使用環境、使用者の意図に応じて、表示品位(表示階調)と消費電力について選択することができる。

【0070】

また、上記画像表示パネルでは、上記疑似階調処理手段における疑似階調処理の動作および非動作は、入力されるデジタル映像信号のビット数に基づいて切り替えられる構成とすることができる。

【0071】

上記の構成によれば、疑似階調処理手段の動作をデジタル映像信号で制御することにより、表示画像の種類(階調数)に応じて、表示品位(表示階調)と消費電力について、自動的に最適な駆動方法をとることができる。

【0072】

また、上記画像表示パネルでは、上記データ信号線駆動回路を構成する能動素子が、多結晶シリコン薄膜トランジスタによって形成されている構成とすることができる。

【0073】

上記の構成によれば、表示を行うための画素と、画素を駆動するためのデータ信号線駆動回路を、同一基板上に同一工程で製造することができるので、製造コストや実装コストの低減と、実装良品率のアップが期待できる。

【0074】

また、このように多結晶シリコン薄膜を用いてトランジスタを形成すると、従来の画像表示装置に用いられていた非晶質シリコン薄膜トランジスタに較べて、極めて駆動力の高い特性が得られるので、上記効果に加えて、画素およびデータ信号線駆動回路を、容易に同一基板上に形成することができる。

【0075】

また、多結晶シリコン薄膜トランジスタは、単結晶シリコントランジスタに較べて、バラツキが大きく、また、経時変化も大きいため、これを用いてデータ信号線駆動回路を構成した場合、アンプやR−DAC,C−DACではその精度が低下したり、占有面積が大きくなったりすることがあるが、本発明のような構成とすることによる表示品位向上効果は、極めて大きくなる。

【0076】

また、上記画像表示パネルでは、上記多結晶シリコン薄膜トランジスタは、600℃以下の製造温度で、ガラス上に構成されたものである構成とすることができる。

【0077】

上記の構成によれば、600℃以下のプロセス温度で、多結晶シリコン薄膜トランジスタを形成する場合には、歪み点温度が低いが安価でかつ大型化の容易なガラスを基板として用いることができるので、大型の画像表示装置を低コストで製造することが可能となる。

【0078】

【発明の実施の形態】

本発明の実施の一形態について図1ないし図22に基づいて説明すれば、以下の通りである。

【0079】

本実施の形態に係る画像表示装置の構成例を図2に示す。尚、本発明に係る画像表示装置においては、その表示方式が特に限定されるものではなく、画素がマトリクス状に配置されてなる画素アレイに対し、データ信号線駆動回路によって映像信号を送出するものであれば、液晶表示装置、プラズマ表示装置、EL表示装置等に本発明を適用可能である。

【0080】

上記画像表示装置は、図2に示すように、画素アレイ(ARY)1、データ信号線駆動回路(SD)2、走査信号線駆動回路(GD)3、タイミング信号を生成するタイミング回路(CTL)4、および映像信号を生成する映像信号回路(SIG)5を備えている。

【0081】

画素アレイ1、データ信号線駆動回路2、および走査信号線駆動回路3は、同一の基板(SUB)6上に形成される。また、画素アレイ1は、データ信号線駆動回路2によって駆動されるデータ信号線SL…、該データ信号線SL…と直交して配置され走査信号線駆動回路3によって駆動される走査信号線GL…、そしてデータ信号線SL…および走査信号線GL…の各交差部に対応してマトリクス状に配置される画素(PIX)7…にて構成されている。

【0082】

タイミング回路4は、入力制御信号TINの入力を受け、データ信号線駆動回路2にはスタート信号SSTおよびクロック信号SCKを出力し、走査信号線駆動回路3にはスタート信号GST,クロック信号GCKおよびパルス幅制御信号GENを出力する。映像信号回路5は、入力映像信号DINの入力を受け、映像信号DATをデータ信号線駆動回路2へ出力する。

【0083】

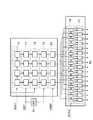

次に、データ信号線駆動回路2の具体的な構成例を図1に示す。データ信号線駆動回路2は、図1に示すように、機能的には第1のブロック8と、第2のブロック9とに分けられる。第1のブロック8は入力されるデジタル映像信号DATに疑似階調処理を行なう機能部であり、第2のブロック9は疑似階調処理の施された映像信号をデータ信号線SL…に出力する機能部である。また、第2のブロックに与えられるクロック周波数SCK2は、第1のブロックに与えられるクロック周波数SCK1に比べて小さいものとなっている。また、データ信号線駆動回路2は、n本のデータ信号線を駆動するものであるが、図1の構成では、説明を簡略化するためデータ信号線の本数を16本としている。

【0084】

第1のブロック8は、シフトレジスタ10、ラッチ回路11、並列化回路12、および疑似階調処理回路13を備えている。シフトレジスタ10は、m(m<n)段のシフトレジスタ部14…を有している。同様に、ラッチ回路11はm段のラッチ部15…を、並列化回路12はm段の並列化部16…を、疑似階調処理回路13はm段の疑似階調処理部17…を有している。すなわち、第1のブロック8は、シフトレジスタ部14、ラッチ部15、並列化部16、疑似階調処理部17が直列に配列されたm段の処理ラインを備えた構成となっている。

【0085】

上記第1のブロック8では、入力されたデジタル映像信号DATは、シフトレジスタ10のシフトレジスタ部14…の各出力に同期して、ラッチ回路11のラッチ部15…に順次取り込まれ、並列化回路12により多相化される。そして、疑似階調処理回路13は、多相化されたデジタル映像信号を、低周波数で処理することにより、入力された映像信号よりも少ないビット数の信号に変換する。

【0086】

この処理を、図3のタイミングチャートを参照して説明すると以下の通りである。先ず、シフトレジスタ10には、第1のクロック信号SCK1および第1のスタート信号SST1が入力される。ここで、第1のスタートクロック信号SCK1の周波数は、第1のスタート信号SST1のm倍である。すなわち、シフトレジスタ10では、第1のスタート信号SST1のONパルスを、第1のクロック信号SCK1のクロックパルスにて、m段のシフトレジスタ部14において順次シフトする。尚、第1のスタート信号SST1については、最終段のシフトレジスタ部14から初段のシフトレジスタ部14へ繰り返し入力される構成とすれば、最初のONパルスのみを与える構成としても良い。

【0087】

これにより、上記シフトレジスタ10の各シフトレジスタ部14は、第1のクロック信号SCK1の1パルス毎に順次ON信号を出力し、ラッチ回路11の各ラッチ部15では、図3のLAT1−1ないし1−4に示すように、この出力に同期して映像信号DATを順次取り込み、所定の期間これを保持する。尚、図3において、DAT1〜16は、16本のデータ信号線のそれぞれに出力される映像信号を示している。

【0088】

並列化回路12には、シフトレジスタ10の最終段から出力される第1のスタート信号SST1が入力されるようになっており、これにより、並列化回路12では、図3のPRL1〜4に示すように、ラッチ部15…に保持されている映像信号DATが一括して並列化部16…に取り込まれる。

【0089】

疑似階調処理回路13の各疑似階調処理部17…には、図3のBDE1〜4に示すように、各並列化部16…から映像信号DATが入力され、該映像信号DATに疑似階調処理が施される。ここで、1ライン分の映像信号に係る疑似階調処理は、1ライン分の映像信号の入力に対し、より多くの時間を要するものである。しかしながら、上記データ信号線駆動回路2の構成では、図3からも明らかなように、疑似階調処理部17への信号の取り込みは、クロック信号SCK1の入力パルスの4周期毎に発生しており、データ信号線駆動回路2の動作周波数を下げることなく、疑似階調処理にかかる時間を十分に確保することが可能となっている。

【0090】

次に、第2のブロック9は、シフトレジスタ18、ラッチ回路19、DA(digital/analog) 変換回路20、および出力回路21を備えている。シフトレジスタ10は、n/m段のシフトレジスタ部22…を有している。また、ラッチ回路19はn段のラッチ部23…を、DA変換回路20はn段のDA変換部24…を、出力回路21はn段の出力部25…を有している。すなわち、第2のブロック9は、n/m段のシフトレジスタ部14を備え、該シフトレジスタ部14の各段に、ラッチ部23、DA変換部24、出力部25が直列に配列されたm段の処理ラインを備えた構成となっている。

【0091】

上記第2のブロック9の処理を、図4のタイミングチャートを参照して説明すると以下の通りである。尚、第2のブロック9での処理は、第1のブロック8での処理が終了した映像信号DATに対して実施されるものであるため、図4では、第1のブロック8から第2のブロック9の処理の流れが分かるように、図3で示した第1のクロック信号SCK1,第1のスタート信号SST1,疑似階調処理部17…での処理BDE1〜4を併せて示している。

【0092】

先ず、シフトレジスタ18には、第2のクロック信号SCK2および第2のスタート信号SST2が入力される。ここで、第2のクロック信号SCK2の周波数は、第2のスタート信号SST2のn/m倍である。すなわち、シフトレジスタ18では、第2のスタート信号SST2のONパルスを、第2のクロック信号SCK2のクロックパルスにて、n/m段のシフトレジスタ部22において順次シフトする。尚、第2のスタート信号SST2については、最終段のシフトレジスタ部22から初段のシフトレジスタ部22へ繰り返し入力される構成とすれば、最初のONパルスのみを与える構成としても良い。

【0093】

これにより、上記シフトレジスタ18の各シフトレジスタ部22は、第2のクロック信号SCK2の1パルス毎に順次ON信号を出力する。また、各シフトレジスタ部22には、それぞれm段のラッチ部23が接続されている(図1参照)ため、同一のシフトレジスタ部22に接続されるラッチ部23…には、第1のブロック8の疑似階調処理回路13から同時に映像信号DATが取り込まれる。

【0094】

具体的には、m=4,n=16の場合、初段のシフトレジスタ部22がON信号を出力した時点で、1〜4段目のラッチ部23において1〜4本目のデータ信号線に出力される映像信号DAT1〜4が取り込まれる(図4のLAT2−1〜2−4参照)。同様に、2段目のシフトレジスタ部22がON信号を出力した時点で、5〜8段目のラッチ部23において5〜8本目のデータ信号線に出力される映像信号DAT5〜8が取り込まれ、3段目のシフトレジスタ部22がON信号を出力した時点で、9〜12段目のラッチ部23において9〜12本目のデータ信号線に出力される映像信号DAT9〜12が取り込まれ、最終段のシフトレジスタ部22がON信号を出力した時点で、13〜16段目のラッチ部23において13〜16本目のデータ信号線に出力される映像信号DAT13〜16が取り込まれる。

【0095】

上記ラッチ回路19に取り込まれた映像データDATは、DA変換回路20、出力回路21に対して、m段分ずつ一括して送られ、DA変換回路20の各DA変換部24において液晶を駆動するためのアナログ信号に変換され、出力回路21の各出力部25を介して各データ信号線SLへ出力される。

【0096】

ここで、第1のクロック信号SCK1は、第2のクロック信号SCK2よりも周波数が大きいものとなるが、第1のクロック信号SCK1の周波数を第2のクロック信号SCK2の周波数の整数倍にすることにより、図1に示すように、第1のブロック8の出力と、第2のブロック9の入力との関係を単純にする(第1のブロック8の1つの出力を、第2のブロック9の複数の入力に接続させる)ことができるので、回路構成が容易になる。

【0097】

また、図4からも明らかなように、第2のクロック信号SCK2の周波数は、第1のスタート信号SST1の周波数と同じであり、シフトレジスタ10の最終段からのスタート信号ST1の出力を用いて、第2のクロック信号SCK2を生成することができる。これにより、外部から第2のクロック信号SCK2を入力する必要がなくなる。これは、図1のように、第1のクロック信号SCK1を第2のクロック信号SCK2の整数倍にした場合には容易に実現できる。

【0098】

また、上記図1の構成の変形例として、図5に示す構成のデータ信号線駆動回路2’を用いることも可能である。図5におけるデータ信号線駆動回路2’では、図1に示したデータ信号線駆動回路2と同一の構成については、同一の部材番号を付し、その説明を省略する。

【0099】

データ信号線駆動回路2’は、機能的には第1のブロック8’と、第2のブロック9’とに分けられる。第1のブロック8’は、シフトレジスタ10、ラッチ回路11、並列化回路12、疑似階調処理回路13、およびDA変換回路26を備えている。第2のブロック9’は、シフトレジスタ18および出力回路27を備えている。

【0100】

すなわち、図5の構成では、図1の構成に対してDA変換回路の配置位置が異なっており、このデータ信号線駆動回路2’においては、入力されたデジタル映像信号DATは、シフトレジスタ10の各出力に同期してラッチ回路11に取り込まれ、並列化回路12により多相化される。疑似階調処理回路13は、多相化された映像信号DATを、低周波数で処理することにより、入力された映像信号よりも少ないビット数の信号に変換する。

【0101】

変換された映像信号DATは、DA変換回路26により、液晶を駆動するためのアナログ映像信号に変換された後、シフトレジスタ18の各出力に同期して動作する出力回路27を介してデータ信号線SLに出力される。

【0102】

ここで、図1に示す構成のデータ信号線駆動回路2と、図5に示す構成のデータ信号線駆動回路2’とでは、それぞれ以下に示すような利点がある。すなわち、データ信号線駆動回路2では、疑似階調処理回路13で疑似階調処理を施した映像信号DATに対し、ラッチ回路19でラッチした後、出力回路21へ送る前の段階でD/A変換を行なっているため、データ信号線SLへの出力の直前まで映像データがデジタル信号として扱われ、雑音や微妙なタイミングずれの影響を受けにくいといった利点がある。

【0103】

一方、データ信号線駆動回路2’では、疑似階調処理回路13で疑似階調処理を施した映像信号DATに対し、該疑似階調処理の直後にD/A変換を行なっている。このため、データ信号線駆動回路2に比べると雑音や微妙なタイミングずれの影響を受けやすいものの、DA変換部24を各ライン毎(n段)に必要とするデータ信号線駆動回路2の構成に比べ、DA変換部の数がm段でよく、回路の構成を簡略化することができる。また、DA変換部24の回路構成は、シフトレジスタと、インバータやNAND等の簡単なゲートとアナログスイッチとから構成でき、DA変換部24自体を非常に単純でコンパクトに形成できる。

【0104】

また、データ信号線駆動回路のさらに他の変形例として図6に示すような構成も考えられる。図6におけるデータ信号線駆動回路2”では、図1に示したデータ信号線駆動回路2と同一の構成については、同一の部材番号を付し、その説明を省略する。

【0105】

データ信号線駆動回路2”は、機能的には第1のブロック28と、第2のブロック29とに分けられる。第1のブロック28は、シフトレジスタ10、ラッチ回路11、および疑似階調処理回路13を備えている。第2のブロック29は、シフトレジスタ30、ラッチ回路19、DA変換回路20および出力回路21を備えている。

【0106】

第1のブロック28では、シフトレジスタ10、ラッチ回路11の動作は、データ信号線駆動回路2の第1のブロック8と同じである。しかしながら、第1のブロック28では、並列化回路12が省略されているため、疑似階調処理回路13の各疑似階調処理部17…への映像信号データDATの入力が、図7のタイミングチャートに示すように、第1のクロック信号SCK1の1パルスずつずれたものとなる(図7のBDE1〜4)。

【0107】

また、第2のブロック28では、シフトレジスタ30の構成が、データ信号線駆動回路2のシフトレジスタ10の構成とは異なり、シフトレジスタ部31の段数がn/m段ではなく、n段となっている。また、シフトレジスタ30に入力される第2のクロック信号SCK2は、第1のクロック信号SCK1と同じ周波数である。このため、第2のブロック28では、ラッチ回路19の各ラッチ部23では、第2のクロック信号SCK2に応じて1ライン毎に疑似階調処理された映像信号DATが取り込まれる(図7のLAT2−1〜2−16)。また、図7のタイミングチャートでは図示は省略するが、DA変換回路20、出力回路21の処理も第2のクロック信号SCK2に応じて1ライン毎に実施される。

【0108】

尚、上記6のデータ信号線駆動回路2”において、DA変換回路20は図1の構成と同様にラッチ回路19の下流(映像信号の処理の流れについて、データ信号線駆動回路への入力側を上流、出力側を下流としている)にn段で設けられているが、図5の構成のようにDA変換回路26を疑似階調処理回路13の直後にm段で設ける構成としても良い。

【0109】

ここで、上記図1または図5の構成(第1の構成)によれば、シフトレジスタ18におけるシフトレジスタ部22の各段が、複数のデータ信号線SL(m本)に対応しているので、シフトレジスタ部22の段数をデータ信号線の本数(n本)の1/mにすることができ、データ信号線駆動回路2または2’の規模を小さくすることが可能となる。また、シフトレジスタ18に与えられる周波数SLK2がシフトレジスタ10に与えられる周波数の1/mになるので、ラッチ回路19(または出力回路27)でデータ信号線SLにデータ信号線にデータを送出する時間を長く取ることができる。

【0110】

また、上記図6の構成(第2の構成)によれば、シフトレジスタ30からの複数の出力信号の和を用いることにより、ラッチ回路19でデータ信号線SLにデータを送出する時間を長く取ることができる。また、この構成では、シフトレジスタ30を制御する第2のクロック信号SLK2として、シフトレジスタ10を制御する第1のクロック信号SLK1と同じ信号を用いることができるので、新たな信号を生成する回路が不要となる。さらに、データ信号線SLへのデータの送出が連続的に行なわれるので、複数のデータを一括して送出される場合に危惧されるブロック毎の境界(表示上の不具合)が生じにくいといったメリットがある。

【0111】

上記データ信号線駆動回路において、疑似階調処理回路13の構成としては様々なものが適用できるが、ここでは、その例として図8に示す構成について説明する。これは、固定のノイズパターンを画像データに重畳させた後、下位ビットを切り捨てることにより、低ビットの駆動回路でより多ビットの画像を擬似的に表示するものであり、疑似階調処理の中でも最も構成のシンプルなものの1つである。高精細の画像表示装置では、擬似的に階調数を増す手法は、画質の劣化が極めて小さいため、影響は問題にならない場合が多い。

【0112】

図8において、入力された映像信号DATIに対し、メモリ(ROM)32に記憶されている固定ノイズパターンNDをメモリ制御回路(MCTL)33によって読み出し、加算器(ADDER)34で加算する。映像信号DATIと固定ノイズパターンNDとの加算データは、例外処理回路(OFP)35でオーバーフロー時などの例外処理を行った後、量子化回路(QNT)36で下位ビットを切り捨てることで、ビット数の下げられた映像信号DATOが得られる。このように非常に簡単な構成で、疑似階調処理を実現することができるのが、この方式の特徴である。

【0113】

このときの画像表示の例を図9に示す。本来の画像(原画像)と固定ノイズパターンを合成した合成画像は、原画像より品位は落ちるが、原画像を単に低階調で表示した場合よりは視認性が高くなる。

【0114】

上記疑似階調処理回路13において、ROM32に記憶させる固定ノイズパターンは、画面全体にわたって最適化することが、表示品位の点からは望ましいが、この場合には、一方でメモリのデータ量が大きくなるという問題がある。そこで、映像データに重畳する固定ノイズパターンを、ある一定の大きさ(例えば、縦と横がそれぞれ16画素など)のパターンデータの繰り返しによって得られる固定ノイズパターンとすることも有効である。

【0115】

このとき、パターンデータの周期(水平方向の周期)を、上記の並列化回路12で並列化した映像信号DATの周期の整数倍とする(すなわち、パターンデータのデータ信号線の配列方向における幅を、mの整数倍のライン数に相当させる)と、疑似階調処理回路13の構成が非常にシンプルになる。

【0116】

例えば、図10に示すように、パターンデータの周期を16画素とし、第1のブロック8の出力数(映像信号の並列化周期)を4とすると、疑似階調処理回路13の各疑似階調処理部17の各加算器34には、メモリ32からメモリ制御回路33により読み出されるパターンデータ信号の内、決まった信号のみが入力され、接続関係を切り替えたりする必要がなくなる。

【0117】

より具体的な例を示すと、図11のように、疑似階調処理回路13内の4個の加算器34−1〜34−4には、それぞれ対応するメモリ(ROM1〜4)32−1〜32−4が接続され、それぞれのメモリ32−1〜32−4には各加算器34−1〜34−4が使用するパターンデータのみを記憶させている。このような構成により、メモリのデータ量を増やすことなく、メモリ32と加算器34との接続を単純化させることができる。上記図10,11で説明したように、固定ノイズパターンをある決まった大きさのパターンデータの繰り返しによって生成する場合、メモリのデータ量を削減することができる。しかし、この方法は、繰り返しピッチに対応した縦縞やブロック縞(疑似パターン)が見えやすくなり、表示品位の点からは好ましくない場合がある。

【0118】

そこで、図12にように、固定ノイズパターンを構成するパターンデータを、固定ノイズパターンの垂直周期毎に水平方向に一定量だけずらすことで、表示品位の劣化を抑えることができる。また、図13に示すように、水平方向のずらし量をパターンデータの1/k(kは2以上の整数:図13はk=2の場合)周期とすることにより、メモリからの読み出しタイミングの制御(読み出し開始アドレスの切替)を容易なものとすることができ、疑似階調処理回路13の構成を簡略化することができる。

【0119】

また、固定ノイズパターンを構成するパターンデータをずらすのは、固定ノイズパターンの垂直方向の周期毎でなく、一定のフレーム周期毎に行なっても良い。この場合も、連続するフレームにおいて、同一個所の同一パターンが連続して存在することを回避でき、映像信号に重畳されるパターンデータの信号によるブロック状の疑似パターンが認識されにくくなるため、表示品位を向上することができる。

【0120】

また、パターンデータをずらす周期については、1フレーム期間毎とする場合が、同一の固定パターンの連続が最も短く、ブロック状の疑似パターンを認識しにくくするためには最も効果が高い。但し、固定パターンデータをずらす周期を2フレーム期間毎とした場合には、疑似パターンを認識しにくくして表示品位を向上すると共に、液晶の交流駆動に対応して、液晶に印加される電圧のDC成分が相殺されるため、液晶材料の劣化が抑えられ、表示装置の信頼性向上に有効である。

【0121】

また、この場合も、水平方向のずらし量をパターンデータの1/k(kは2以上の整数:図13はk=2の場合)周期とすることにより、メモリからの読み出しタイミングの制御(読み出し開始アドレスの切替)を容易なものとすることができ、疑似階調処理回路13の構成を簡略化することができる。

【0122】

さらに、疑似パターンの認識をさらに抑制して表示品位を向上させるためには、一定のフレーム周期毎に、映像信号に重畳するパターンデータを変化させることも可能である。

【0123】

すなわち、映像信号に重畳するパターンデータを一定のフレーム周期毎に水平方向にずらす場合では、ブロック状の疑似パターンの移動が認識される可能性があるが、フレーム毎に全く異なるパターンデータを用いることにより、ブロック状の疑似パターンがさらに認識されにくくなり、表示品位をより一層向上する。

【0124】

もちろん、パターンデータをずらす周期については、1フレーム期間毎とする場合にブロック状の疑似パターンを認識しにくくするうえで最も効果が高く、2フレーム期間毎とした場合に、表示品位を向上と表示装置の信頼性向上と同時にを図ることができる。

【0125】

また、一定のフレーム周期毎に、映像信号に重畳するパターンデータを変化させる場合、映像信号に重畳するパターンデータを一定周期で同一のものを繰り返すことにより、パターンデータの種類を制限することができ、パターンデータを格納する記憶手段の容量を少なくすることができる。

【0126】

次に、DA変換回路の構成について説明する。DA変換回路の構成については、従来から提案されている様々な方式を用いることができるが、本発明のメリットを最大限に発揮するためには、複数の基準電圧源から、表示階調に対応する電圧を選択して出力するセレクタ型のDA変換回路がもっとも望ましい。

【0127】

このセレクタ型のデジタルーアナログ変換回路は、図14に示すように、4bitのデジタル映像信号DATをデコーダ37によってデコードした信号により、複数(図では16本)の基準電圧線VREFと出力線(図ではデータ信号線SL)との間のスイッチ38…を制御し、1つの基準電圧を選択するものであり、ロジック回路であるデコーダと転送ゲートであるスイッチのみから構成されている。

【0128】

したがって、上記DA変換回路を、半導体材料に多結晶シリコンを用いて作成しても、特性バラツキや特性変動などの影響を殆ど受けることなく、高品位の画像表示を実現することができる。また、定常電流が流れる経路がなく、低消費電力のデータ信号線駆動回路および画像表示装置を実現することができる。

【0129】

ここで、複数の基準電圧源VREFは、外部から直接入力されていてもよいが、外部電源回路を簡単にするために、データ信号線駆動回路内部で生成することも可能である。例えば、図15に示す例では、高電圧側電源VCCと低電圧側電源VEEとの2本の外部電源から、16レベルの基準電源を生成することができる。また、図16の例では、5本の外部電源V0〜V4から、16レベルの基準電源を生成している。

【0130】

このような基準電源生成部は、データ信号線駆動回路の各ライン毎に設けると、特性のバラツキなどのために、縦方向の縞などの表示不良につながることがある。したがって、データ信号線駆動回路全体で1つの基準電源生成部を備える構成とすることが望ましい。

【0131】

上記の疑似階調処理は、データ信号線駆動回路の出力部の能力よりも多階調(多ビット)の画像表示を行うときに有効である。一方、原画像の階調が少ない場合などでは、そのメリットはなく、疑似階調処理を行わない方が、表示品位の点でも、消費電力の点でも望ましい。また、その他に、画像表示装置をバッテリ駆動する時には消費電力の少ない疑似階調処理なしで駆動するなど、使用環境などによっても、使い分けることが考えられる。

【0132】

したがって、本実施の形態に係る画像表示装置では、疑似階調処理回路の動作のオン/オフを切り替えられるようにすることが、表示品位と消費電力の観点から極めて有効である。図17(a)および(b)は、ぞれぞれ、疑似階調処理回路を動作させた場合、および、動作させない場合の画像表示の様子を示した図である。

【0133】

また、図18は、疑似階調処理回路の動作をオン/オフ可能とさせる場合の構成を示す図である。上記疑似階調処理回路では、加算器34の前と量子化回路36との前にそれぞれスイッチ39,40を設け、疑似階調処理回路を非動作にする場合には、制御信号BCによってスイッチ39,40を切り替え、加算器34と例外処理回路35とをバイパスさせる構成になっている。

【0134】

上記スイッチ39,40の切替方法としては、図19のように、外部から制御信号BCを入力し、これによってスイッチ39,40を直接制御する方法でもよいし、図20のように、映像信号DATを基準に自動的に切り替えるようにしてもよい。

【0135】

すなわち、図20の構成のように、疑似階調処理回路の動作を映像信号DATを基準に自動的に切り替える場合には、例えば、映像データ監視部(BDT)41において映像信号DATの下位ビット(量子化回路で切り捨てるビット)を監視して、1フレーム期間にわたって下位ビットにデータがなければ、次のフレームで映像データ監視部41が疑似階調処理回路を非動作にするための制御信号を出力することなどが考えられる。

【0136】

以上の説明における、本実施形態に係る画像表示装置では、データ信号線駆動回路における能動素子を多結晶シリコン薄膜トランジスタにて構成する場合に有効なものである。

【0137】

図21に上記画像表示装置で使用される多結晶シリコン薄膜トランジスタの構成例れを示す。図21の多結晶シリコン薄膜トランジスタは、絶縁性基板42上の多結晶シリコン薄膜43を活性層とする順スタガー(トップゲート)構造のものであるが、本発明はこれに限るものではなく、逆スタガー構造等の他の構造のものであってよい。

【0138】

上記のような多結晶シリコン薄膜トランジスタを用いることによって、実用的な駆動能力を有するデータ信号線駆動回路および走査信号線駆動回路を、画素アレイと同一基板上にほぼ同一の製造工程で構成することができる。

【0139】

また、一般に、多結晶シリコン薄膜トランジスタは、単結晶シリコントランジスタ(MOSトランジスタ)に較べて、特性のバラツキが大きく、また、経時変化の量も大きい。更に、素子の駆動電圧が高く、サイズやデザインルールも大きいため、複雑な回路を構成すると、占有面積が大きくなるとともに、消費電力の増加も無視できなくなる。したがって、上述した単純な疑似階調処理回路を用いることによる多階調表示の実現のメリットは極めて大きい。

【0140】

以下に、摂氏600℃以下で上記多結晶シリコン薄膜トランジスタを形成するときの製造プロセスについて、図22を参照して簡単に説明する。

【0141】

まず、に示すように、ガラス基板44(図22(a)参照)上に非晶質シリコン薄膜45を堆積し(図22(b)参照)、この非晶質シリコン薄膜45にエキシマレーザを照射して、多結晶シリコン薄膜46を形成する(図22(c)参照)。

【0142】

次に、この多結晶シリコン薄膜46を所望の形状にパターニングし(図22(d)参照)、パターニングされた多結晶シリコン薄膜46上に二酸化シリコンからなるゲート絶縁膜47を形成する(図22(e)参照)。更に、薄膜トランジスタのゲート電極48をアルミニウム等で形成(図22(f)参照)した後、薄膜トランジスタのソース・ドレイン領域に不純物(n型領域には燐、P型領域には瑚素)を注入する(図22(g)〜(h)参照)。

【0143】

その後、二酸化シリコンまたは窒化シリコン等からなる層間絶縁膜49を堆積し(図22(i)参照)、コンタクトホール50を開口(図22(j)参照)した後、アルミニウム等の金属配線51を形成する(図22(k)参照)。

【0144】

この工程において、プロセスの最高温度は、ゲート絶縁膜形成時の600℃であるので、上記ガラス基板44として米国コーニング社の1737ガラス等の高耐熱性ガラスが使用できる。

【0145】

尚、液晶表示装置においては、この後に、更に、別の層間絶縁膜を介して、透明電極(透過型液晶表示装置の場合)や反射電極(反射型液晶表示装置の場合)を形成することになる。

【0146】

ここで、図22に示すような製造工程で、多結晶シリコン薄膜トランジスタを、摂氏600度以下で形成することにより、安価で大面積のガラス基板を用いることができるようになるので、画像表示装置の低価格化と大面積化が実現される。

【0147】

尚、本発明に係る画像表示装置は、液晶表示装置、プラズマ表示装置、EL表示装置等に適用可能なものであるが、透過型液晶表示装置以外では、基板をガラス基板とする必要はなく、シリコン基板を用いることも可能である。しかしながら、シリコン基板はガラス基板に比べコストが大幅に高いこと、また、基板サイズが150〜200mm径(最大でも300mm径)と大型の表示装置に適用できないなどのデメリットがある。このため、透過型液晶表示装置以外の画像表示装置でも、本発明の適用は、コストダウンや大型画面の適用といった点で有効で

【0148】

【発明の効果】

本発明の画像表パネルは、以上のように、上記データ信号線駆動回路は、画素アレイ上の画素に映像信号を送出するn本のデータ信号線を駆動するものであると共に、各データ信号線に送出される映像信号に対して疑似階調処理を施す、データ信号線の数よりも少ないm段の疑似階調処理手段を備えており、各疑似階調処理手段は、データ信号線に対してmライン毎に疑似階調処理された映像信号を出力し、上記疑似階調処理手段は、一定周期で繰り返される固定パターンデータの信号を映像信号に加算することにより重畳する処理と、重畳された映像信号の下位ビットを切り捨てる処理とを行なう構成である。

【0149】

それゆえ、疑似階調処理手段をデータ信号線の本数(n本)よりも少ないm段とし、複数の異なるデータ信号線に出力される映像信号に対して疑似階調処理手段を共通化することで、データ信号線駆動回路の構成を簡略化でき、駆動回路一体型の画像表示パネルに適用が可能となる簡単な回路構成にて多階調表示が可能となるという効果を奏する。

【0150】

また、データ信号線に対してmライン毎に疑似階調処理された映像信号を出力することで、各疑似階調処理手段では、1ライン分の映像信号の疑似階調処理において映像信号の入力周期のm倍の時間の処理時間を確保することができ、疑似階調処理に十分なタイミングマージンが得られるという効果を併せて奏する。

それゆえ、映像信号に重畳する信号として一定周期で繰り返される固定パターンデータの信号を用いることにより、固定パターンデータを記憶する記憶手段の容量を抑制できると共に、複雑な演算処理を必要とせず、非常に簡単に疑似階調処理を実現することができ、駆動回路一体型の画像表示装置への適用が容易となるという効果を奏する。

【0151】

また、上記画像表示パネルでは、第1の構成として、上記データ信号線駆動回路は、第1のシフトレジスタの出力に同期して、順次映像信号を取り込むm段の第1のラッチ手段と、上記ラッチ回路にて取り込まれた映像信号を並列化するm段の並列化手段と、上記疑似階調処理手段によって疑似階調処理が施された映像信号を、第2のシフトレジスタの出力に同期して、順次取り込むn段の第2のラッチ手段とを備えており、上記各疑似階調処理手段は、上記並列化手段にて並列化された映像信号に対して疑似階調処理を施すと共に、上記各疑似階調処理手段にて疑似階調処理を施された映像信号は、上記第1のシフトレジスタよりも動作周波数の小さい第2のシフトレジスタの出力に同期させて、上記第2のラッチ手段に対し、mライン分の映像信号毎に一括して取り込まれた後、各データ信号線に送出される構成とすることができる。

【0152】

また、上記画像表示パネルでは、第2の構成として、上記データ信号線駆動回路は、第1のシフトレジスタの出力に同期して、順次映像信号を取り込むm段の第1のラッチ手段と、上記疑似階調処理手段によって疑似階調処理が施された映像信号を、第2のシフトレジスタの出力に同期して、順次取り込むn段の第2のラッチ手段とを備えており、上記各疑似階調処理手段は、上記第1のラッチ手段から上記第1のシフトレジスタの出力と同周期で映像信号を取り込み、該映像信号に対して疑似階調処理を施すと共に、上記各疑似階調処理手段にて疑似階調処理を施された映像信号は、上記第1のシフトレジスタと同一の動作周波数にて動作する第2のシフトレジスタの出力に同期させて、上記第2のラッチ手段に対し、1ライン分の映像信号毎に取り込まれた後、各データ信号線に送出される構成とすることができる。

【0153】

また、上記第1の構成の画像表示パネルでは、上記第1のシフトレジスタの動作周波数は、第2のシフトレジスタの動作周波数の整数倍とすることで、第1のシフトレジストの動作周波数を与えるクロック信号と、第2のシフトレジスタの動作周波数を与えるクロック信号とのタイミング関係を単純にでき、データ信号線駆動回路全体の構成が簡単になるという効果を奏する。

【0154】

また、上記第1の構成の画像表示パネルでは、上記第2のシフトレジスタを駆動させるクロック信号は、第1のシフトレジスタの最終段からの出力信号より生成される構成とすることで、第2のフトレジスタを駆動するためのクロック信号を、データ信号線駆動回路の外部から別途入力する必要がなくなり、データ信号線駆動回路全体の構成が簡単になるという効果を奏する。

【0155】

また、上記画像表示パネルでは、上記疑似階調処理手段にて疑似階調処理が施されたデジタル映像信号を、アナログ映像信号に変換するデジタル/アナログ変換手段を備えており、上記デジタル/アナログ変換手段による変換処理が、上記第2のラッチ手段によるラッチ後に行なわれる構成とすることができる。

【0156】

それゆえ、上記映像信号は、データ信号線への出力の直前までデジタル信号として扱われることとなり、上記映像信号が雑音や微妙なタイミングずれの影響を受けることがなく、高画質の表示を得ることができるという効果を奏する。

【0157】

また、上記画像表示パネルでは、上記疑似階調処理手段にて疑似階調処理が施されたデジタル映像信号を、アナログ映像信号に変換するデジタル/アナログ変換手段を備えており、上記デジタル/アナログ変換手段による変換処理が、疑似階調処理手段による疑似階調処理の後、かつ上記第2のラッチ手段によるラッチ前に行なわれる構成とすることができる。

【0158】

それゆえ、デジタル/アナログ変換手段の数を疑似階調処理手段と同じくm段とすることができ、データ信号線駆動回路の構成を簡略化することができるという効果を奏する。

【0161】

また、上記画像表示パネルでは、上記固定パターンデータは、データ信号線の配列方向における幅が、mの整数倍のライン数に相当する構成とすることができる。

【0162】

それゆえ、固定パターンデータの信号を映像信号に加算する加算器を疑似階調処理手段の下流に疑似階調処理手段と同数のm段設ける構成にて実現でき、データ信号線駆動回路全体の構成が簡単になるという効果を奏する。

【0163】

また、上記画像表示パネルでは、上記疑似階調処理手段は、上記固定パターンデータを格納する記憶手段を備えており、各疑似階調処理手段内の記憶手段(例えば、ROM)は、各疑似階調処理手段に対応するデータ信号線用の固定パターンデータのみを格納している構成とすることができる。

【0164】

それゆえ、各疑似階調処理手段に内蔵すべき記憶手段のデータ量を最小化することができ、また、記憶手段からの固定パターンデータの読み出しを管理するメモリー制御回路の構造や駆動方法も単純化されるという効果を奏する。

【0165】

また、上記画像表示パネルでは、上記疑似階調処理手段は、上記固定パターンデータの垂直方向の周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を一定量だけずらす構成とすることができる。

【0166】

それゆえ、映像信号に重畳される固定パターンデータの信号によるブロック状の疑似パターンが認識されにくくなり、表示品位を向上することができるという効果を奏する。

【0167】

また、上記画像表示パネルでは、上記疑似階調処理手段は、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を一定量だけずらす構成とすることができる。

【0168】

それゆえ、映像信号に重畳される固定パターンデータの信号によるブロック状の疑似パターンが認識されにくくなり、表示品位を向上することができるという効果を奏する。

。

【0169】

また、上記画像表示パネルでは、上記疑似階調処理回路は、上記固定パターンデータの垂直方向の周期毎、または、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を1/k(kは2以上の整数)周期分だけずらす構成とすることができる。

【0170】

それゆえ、映像信号へ重畳される固定パターンデータの読み出しタイミングの制御(読み出し開始アドレスの切替え)が簡単になり、疑似階調処理手段の構成が簡単となるという効果を奏する。

【0171】

また、上記画像表示パネルでは、上記疑似階調処理手段は、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータを変化させる構成とすることができる。

【0172】

それゆえ、フレーム毎に全く異なる固定パターンデータを用いることにより、ブロック状の疑似パターンがさらに認識されにくくなるため、表示品位をより一層向上させることができるという効果を奏する。

【0173】

また、上記画像表示パネルでは、上記疑似階調処理手段は、映像信号に重畳する固定パターンデータとして、一定のフレーム周期毎に、同一の固定パターンデータを繰り返す構成とすることができる。

【0174】

それゆえ、固定パターンデータの種類を制限することができ、固定パターンデータを格納する記憶手段の容量を少なくすることができるという効果を奏する。

【0175】

また、上記画像表示パネルでは、上記デジタル/アナログ変換手段は、疑似階調処理を施された映像信号に応じて、複数の基準電圧源の内の1つを選択する構成とすることができる。

【0176】

それゆえ、セレクタ型のデジタル駆動方式をデジタル/アナログ変換手段に採用することにより、単純な構成で多階調表示を実現することができるという効果を奏する。

【0177】

また、上記画像表示パネルでは、上記複数の基準電圧源は、外部から入力されるより少数の基準電圧源より、上記基板上にて生成される構成とすることができる。

【0178】

それゆえ、外部の基準電圧源の数を削減することができるため、データ信号線駆動回路全体の構成を簡略化することができるという効果を奏する。

【0179】

また、上記画像表示パネルでは、上記疑似階調処理手段における疑似階調処理の動作および非動作は、外部より入力される制御信号によって切り替えられる構成とすることができる。

【0180】

それゆえ、表示階調の少ない画像表示の場合には、疑似階調処理回路を動作させないようにすることができ、より低消費電力での画像表示を実現することができるという効果を奏する。

【0181】

また、上記画像表示パネルでは、上記疑似階調処理手段における疑似階調処理の動作および非動作は、外部より入力される制御信号によって切り替えられる構成とすることができる。

【0182】

それゆえ、表示画像の種類や使用環境、使用者の意図に応じて、表示品位(表示階調)と消費電力について選択することができるという効果を奏する。

【0183】

また、上記画像表示パネルでは、上記疑似階調処理手段における疑似階調処理の動作および非動作は、入力されるデジタル映像信号のビット数に基づいて切り替えられる構成とすることができる。

【0184】

それゆえ、表示画像の種類(階調数)に応じて、表示品位(表示階調)と消費電力について、自動的に最適な駆動方法をとることができるという効果を奏する。

【0185】

また、上記画像表示パネルでは、上記データ信号線駆動回路を構成する能動素子が、多結晶シリコン薄膜トランジスタによって形成されている構成とすることができる。

【0186】

多結晶シリコン薄膜トランジスタは、単結晶シリコントランジスタに較べて、特性のバラツキが大きく、また、経時変化も大きいため、これを用いてデータ信号線駆動回路を構成した場合、アンプやR−DAC,C−DACを用いると精度が低下したり、占有面積が大きくなったりすることがあるが、本発明においては、表示品位向上効果を極めて大きなものとすることができる。

【0187】

また、上記画像表示パネルでは、上記多結晶シリコン薄膜トランジスタは、600℃以下の製造温度で、ガラス上に構成されたものである構成とすることができる。

【0188】

それゆえ、600℃以下のプロセス温度で、多結晶シリコン薄膜トランジスタを形成する場合には、歪み点温度が低いが安価でかつ大型化の容易なガラスを基板として用いることができるので、大型の画像表示装置を低コストで製造することが可能となる。

【図面の簡単な説明】

【図1】本発明の一実施形態を示すものであり、画像表示装置におけるデータ信号線駆動回路の構成例を示す回路図である。

【図2】上記画像表示装置の構成例を示すブロック図である。

【図3】図1に示すデータ信号線駆動回路の動作の一部を示すタイミングチャートである。

【図4】図1に示すデータ信号線駆動回路の動作の一部を示すタイミングチャートである。

【図5】本発明に係る画像表示装置におけるデータ信号線駆動回路の他の構成例を示す回路図である。

【図6】本発明に係る画像表示装置におけるデータ信号線駆動回路のさらに他の構成例を示す回路図である。

【図7】図6に示すデータ信号線駆動回路の動作を示すタイミングチャートである。

【図8】図1,5,6に示すデータ信号線駆動回路における疑似階調処理回路の構成例を示すブロック図である。

【図9】上記疑似階調処理回路による画像処理の例を示す説明図である。

【図10】本発明に係る画像表示装置におけるデータ信号線駆動回路のさらに他の構成例を示す回路図である。

【図11】本発明に係る画像表示装置におけるデータ信号線駆動回路において、第1のブロックのさらに他の構成例を示す回路図である。

【図12】上記疑似階調処理回路における固定パターンの例を示す説明図である。

【図13】上記疑似階調処理回路における固定パターンの他の例を示す説明図である。

【図14】本発明に係る画像表示装置におけるDA変換部の構成例を示す回路図である。

【図15】上記DA変換部における基準電圧源の生成部の例を示す回路図である。

【図16】上記DA変換部における基準電圧源の生成部の他の例を示す回路図である。

【図17】本発明に係る画像表示装置において、疑似階調処理回路のオン/オフ切り替えでの表示を示す説明図であり、(a)が疑似階調処理回路のオン時、(b)が疑似階調処理回路のオフ時である。

【図18】本発明に係る画像表示装置において、疑似階調処理のオン/オフ切り替えを可能にする疑似階調処理回路の例を示すブロック図である。

【図19】本発明に係る画像表示装置におけるデータ信号線駆動回路のさらに他の構成例を示す回路図である。

【図20】本発明に係る画像表示装置におけるデータ信号線駆動回路のさらに他の構成例を示す回路図である。

【図21】本発明に係る画像表示装置を構成する多結晶シリコン薄膜トランジスタの構造例を示す断面図である。

【図22】(a)〜(k)は、図21に示す多結晶シリコン薄膜トランジスタの製造工程の例を示す図である。

【図23】従来の画像表示装置の構成例を示すブロック図である。

【図24】上記従来の画像表示装置における画素の内部構造の例を示す回路図である。

【図25】従来の画像表示装置において、駆動回路一体型とした画像表示装置の構成例を示すブロック図である。

【図26】アナログ点順次方式を採用する従来のデータ信号線駆動回路の例を示す回路図である。

【図27】疑似階調処理を適用した従来のデータ信号線駆動回路の例を示す回路図である。

【符号の説明】

1 画素アレイ

2 データ信号線駆動回路

6 基板

7 画素

10 シフトレジスタ(第1のシフトレジスタ)

15 ラッチ部(第1のラッチ手段)

16 並列化部(並列化手段)

17 疑似階調処理部(疑似階調処理手段)

18・30 シフトレジスタ(第2のシフトレジスタ)

20・26 DA変換部(デジタル/アナログ変換手段)

23 ラッチ部(第2のラッチ手段)

27 出力回路(第2のラッチ手段)

32 メモリ(記憶手段)

34 加算器

SL データ信号線

SCK1 第1のクロック信号

SST1 第1のスタート信号

SCK2 第2のクロック信号

SST2 第2のスタート信号

DAT 映像信号

VREF 基準電圧源

BC 制御信号

Claims (23)

- 画像を表示する複数の画素からなる画素アレイと、該画素アレイに映像信号を供給するデータ信号線駆動回路とを、同一の基板上に有する画像表示パネルにおいて、

上記データ信号線駆動回路は、画素アレイ上の画素に映像信号を送出するn本のデータ信号線を駆動するものであると共に、各データ信号線に送出される映像信号に対して疑似階調処理を施す、データ信号線の数よりも少ないm段の疑似階調処理手段を備えており、

各疑似階調処理手段は、データ信号線に対してmライン毎に疑似階調処理された映像信号を出力し、

上記疑似階調処理手段は、一定周期で繰り返される固定パターンデータの信号を映像信号に加算することにより重畳する処理と、重畳された映像信号の下位ビットを切り捨てる処理とを行なうことを特徴とする画像表示パネル。 - 上記データ信号線駆動回路は、第1のシフトレジスタの出力に同期して、順次映像信号を取り込むm段の第1のラッチ手段と、

上記第1のラッチ手段にて取り込まれた映像信号を並列化するm段の並列化手段と、

上記疑似階調処理手段によって疑似階調処理が施された映像信号を、第2のシフトレジスタの出力に同期して、順次取り込むn段の第2のラッチ手段とを備えており、

上記各疑似階調処理手段は、上記並列化手段にて並列化された映像信号に対して疑似階調処理を施すと共に、

上記各疑似階調処理手段にて疑似階調処理を施された映像信号は、上記第1のシフトレジスタよりも動作周波数の小さい第2のシフトレジスタの出力に同期させて、上記第2のラッチ手段に対し、mライン分の映像信号毎に一括して取り込まれた後、各データ信号線に送出されることを特徴とする請求項1に記載の画像表示パネル。 - 上記データ信号線駆動回路は、第1のシフトレジスタの出力に同期して、順次映像信号を取り込むm段の第1のラッチ手段と、

上記疑似階調処理手段によって疑似階調処理が施された映像信号を、第2のシフトレジスタの出力に同期して、順次取り込むn段の第2のラッチ手段とを備えており、

上記各疑似階調処理手段は、上記第1のラッチ手段から上記第1のシフトレジスタの出力と同周期で映像信号を取り込み、該映像信号に対して疑似階調処理を施すと共に、

上記各疑似階調処理手段にて疑似階調処理を施された映像信号は、上記第1のシフトレジスタと同一の動作周波数にて動作する第2のシフトレジスタの出力に同期させて、上記第2のラッチ手段に対し、1ライン分の映像信号毎に取り込まれた後、各データ信号線に送出されることを特徴とする請求項1に記載の画像表示パネル。 - 上記第1のシフトレジスタの動作周波数は、第2のシフトレジスタの動作周波数の整数倍であることを特徴とする請求項2に記載の画像表示パネル。

- 上記第2のシフトレジスタを駆動させるクロック信号は、第1のシフトレジスタの最終段からの出力信号より生成されることを特徴とする請求項4に記載の画像表示パネル。

- 上記疑似階調処理手段にて疑似階調処理が施されたデジタル映像信号を、アナログ映像信号に変換するデジタル/アナログ変換手段を備えており、

上記デジタル/アナログ変換手段による変換処理が、上記第2のラッチ手段によるラッチ後に行なわれることを特徴とする請求項2ないし5の何れかに記載の画像表示パネル。 - 上記疑似階調処理手段にて疑似階調処理が施されたデジタル映像信号を、アナログ映像信号に変換するデジタル/アナログ変換手段を備えており、

上記デジタル/アナログ変換手段による変換処理が、疑似階調処理手段による疑似階調処理の後、かつ上記第2のラッチ手段によるラッチ前に行なわれることを特徴とする請求項2ないし5の何れかに記載の画像表示パネル。 - 上記固定パターンデータは、データ信号線の配列方向における幅が、mの整数倍のライン数に相当することを特徴とする請求項1に記載の画像表示パネル。

- 上記疑似階調処理手段は、上記固定パターンデータを格納する記憶手段を備えており、各疑似階調処理手段内の記憶手段は、各疑似階調処理手段に対応するデータ信号線用の固定パターンデータのみを格納していることを特徴とする請求項8に記載の画像表示パネル。

- 上記疑似階調処理手段は、上記固定パターンデータの垂直方向の周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を一定量だけずらすことを特徴とする請求項1に記載の画像表示パネル。

- 上記疑似階調処理手段は、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を一定量だけずらすことを特徴とする請求項1に記載の画像表示パネル。

- 上記疑似階調処理回路は、上記固定パターンデータの垂直方向の周期毎、または、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータの水平方向の位置を1/k(kは2以上の整数)周期分だけずらすことを特徴とする請求項10または11の何れかに記載の画像表示パネル。

- 上記疑似階調処理手段は、一定のフレーム周期毎に、映像信号に重畳する固定パターンデータを変化させることを特徴とする請求項1に記載の画像表示パネル。

- 上記疑似階調処理手段は、映像信号に重畳する固定パターンデータとして、一定のフレーム周期毎に、同一の固定パターンデータを繰り返すことを特徴とする請求項13に記載の画像表示パネル。

- 上記デジタル/アナログ変換手段は、疑似階調処理を施された映像信号に応じて、複数の基準電圧源の内の1つを選択することを特徴とする請求項6または7に記載の画像表示パネル。

- 上記複数の基準電圧源は、外部から入力されるより少数の基準電圧源より、上記基板上にて生成されることを特徴とする請求項15に記載の画像表示パネル。

- 上記疑似階調処理手段は、疑似階調処理の動作および非動作を切り替え可能とされていることを特徴とする請求項1ないし16の何れかに記載の画像表示パネル。

- 上記疑似階調処理手段における疑似階調処理の動作および非動作は、外部より入力される制御信号によって切り替えられることを特徴とする請求項17に記載の画像表示パネル。

- 上記疑似階調処理手段における疑似階調処理の動作および非動作は、入力されるデジタル映像信号のビット数に基づいて切り替えられることを特徴とする請求項17に記載の画像表示パネル。

- 上記データ信号線駆動回路を構成する能動素子が、多結晶シリコン薄膜トランジスタに よって形成されていることを特徴とする請求項1ないし19の何れかに記載の画像表示パネル。

- 上記多結晶シリコン薄膜トランジスタは、600℃以下の製造温度で、ガラス上に構成されたものであることを特徴とする請求項20に記載の画像表示パネル。

- 上記請求項1ないし21の何れかに記載の画像表示パネルを備えていることを特徴とする画像表示装置。

- 画像を表示する複数の画素からなる画素アレイと、画素アレイ上の画素に映像信号を送出するn本のデータ信号線を駆動し、該画素アレイに映像信号を供給するデータ信号線駆動回路とを、同一の基板上に有する画像表示パネルにて用いられる画像表示方法において、

各データ信号線に送出される映像信号に対して、データ信号線のmライン毎に同一の疑似階調処理手段を用いて疑似階調処理を施し、

疑似階調処理の施された映像信号をデータ信号線に対してmライン毎に出力し、

上記疑似階調処理手段は、一定周期で繰り返される固定パターンデータの信号を映像信号に加算することにより重畳する処理と、重畳された映像信号の下位ビットを切り捨てる処理とを行なうことを特徴とする画像表示方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001117453A JP3720275B2 (ja) | 2001-04-16 | 2001-04-16 | 画像表示パネル、画像表示装置、並びに画像表示方法 |

| TW091105329A TW565818B (en) | 2001-04-16 | 2002-03-20 | Image display panel, image display apparatus and image display method |

| US10/105,652 US7375708B2 (en) | 2001-04-16 | 2002-03-25 | Image display panel, image display apparatus and image display method |

| KR10-2002-0016333A KR100437346B1 (ko) | 2001-04-16 | 2002-03-26 | 화상표시패널, 화상표시장치 및 화상표시방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001117453A JP3720275B2 (ja) | 2001-04-16 | 2001-04-16 | 画像表示パネル、画像表示装置、並びに画像表示方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002311883A JP2002311883A (ja) | 2002-10-25 |

| JP2002311883A5 JP2002311883A5 (ja) | 2005-02-03 |

| JP3720275B2 true JP3720275B2 (ja) | 2005-11-24 |

Family

ID=18968004

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001117453A Expired - Fee Related JP3720275B2 (ja) | 2001-04-16 | 2001-04-16 | 画像表示パネル、画像表示装置、並びに画像表示方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7375708B2 (ja) |

| JP (1) | JP3720275B2 (ja) |

| KR (1) | KR100437346B1 (ja) |

| TW (1) | TW565818B (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4410997B2 (ja) * | 2003-02-20 | 2010-02-10 | パナソニック株式会社 | 表示パネルの駆動装置 |

| TW591586B (en) * | 2003-04-10 | 2004-06-11 | Toppoly Optoelectronics Corp | Data-line driver circuits for current-programmed electro-luminescence display device |

| JP4050240B2 (ja) * | 2004-02-26 | 2008-02-20 | シャープ株式会社 | 表示装置の駆動システム |

| GB2448753A (en) * | 2007-04-27 | 2008-10-29 | Sharp Kk | Encoding of display scan direction by an optional additional clock pulse |

| JP6828247B2 (ja) * | 2016-02-19 | 2021-02-10 | セイコーエプソン株式会社 | 表示装置及び電子機器 |

| KR20200025878A (ko) * | 2018-08-31 | 2020-03-10 | 엘지디스플레이 주식회사 | 게이트 구동부와 그를 포함한 표시장치 |

| JP2020154230A (ja) * | 2019-03-22 | 2020-09-24 | 株式会社Jvcケンウッド | 液晶表示装置及びその製造方法 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3751412T2 (de) * | 1986-09-02 | 1995-12-14 | Fuji Photo Film Co Ltd | Verfahren und Vorrichtung zur Bildverarbeitung mit Gradationskorrektur des Bildsignals. |

| US5459587A (en) * | 1991-05-02 | 1995-10-17 | Minolta Camera Kabushiki Kaisha | Processing apparatus capable of discriminating between pseudo half-tone/non-half-tone image data based upon the number of adjacencies of similar type of pixels within a block |

| JP2639763B2 (ja) * | 1991-10-08 | 1997-08-13 | 株式会社半導体エネルギー研究所 | 電気光学装置およびその表示方法 |

| US5495287A (en) * | 1992-02-26 | 1996-02-27 | Hitachi, Ltd. | Multiple-tone display system |

| US5649031A (en) * | 1992-03-31 | 1997-07-15 | Hitachi, Ltd. | Image information processor for producing high-quality output image |

| JPH0682754A (ja) | 1992-07-16 | 1994-03-25 | Toshiba Corp | アクティブマトリクス型表示装置 |

| JPH07219491A (ja) * | 1994-02-01 | 1995-08-18 | Fujitsu General Ltd | ディスプレイ装置の中間調表示回路 |

| JP3125560B2 (ja) | 1994-02-01 | 2001-01-22 | 株式会社富士通ゼネラル | ディスプレイ装置の中間調表示回路 |

| JPH07219494A (ja) * | 1994-02-01 | 1995-08-18 | Fujitsu General Ltd | ディスプレイ装置の中間調表示回路 |

| JPH0950262A (ja) | 1995-08-08 | 1997-02-18 | Toshiba Corp | ディザ法を適用した多階調制御装置及び方法 |

| US6040876A (en) | 1995-10-13 | 2000-03-21 | Texas Instruments Incorporated | Low intensity contouring and color shift reduction using dither |

| JPH09153624A (ja) * | 1995-11-30 | 1997-06-10 | Sony Corp | 半導体装置 |

| JP3618024B2 (ja) * | 1996-09-20 | 2005-02-09 | パイオニア株式会社 | 自発光表示器の駆動装置 |

| JPH1098662A (ja) * | 1996-09-20 | 1998-04-14 | Pioneer Electron Corp | 自発光表示器の駆動装置 |

| US6369782B2 (en) * | 1997-04-26 | 2002-04-09 | Pioneer Electric Corporation | Method for driving a plasma display panel |

| JP3675113B2 (ja) | 1997-06-10 | 2005-07-27 | ソニー株式会社 | 表示装置 |

| JPH1195251A (ja) | 1997-09-19 | 1999-04-09 | Sony Corp | 液晶表示装置 |

| JP3977498B2 (ja) | 1997-11-19 | 2007-09-19 | 沖電気工業株式会社 | 液晶セルの駆動回路 |

| TW525138B (en) * | 2000-02-18 | 2003-03-21 | Semiconductor Energy Lab | Image display device, method of driving thereof, and electronic equipment |

| JP3763397B2 (ja) * | 2000-03-24 | 2006-04-05 | シャープ株式会社 | 画像処理装置、画像表示装置、パーソナルコンピュータ、画像処理方法 |

| JP3748786B2 (ja) * | 2000-06-19 | 2006-02-22 | アルプス電気株式会社 | 表示装置および画像信号の処理方法 |

-

2001

- 2001-04-16 JP JP2001117453A patent/JP3720275B2/ja not_active Expired - Fee Related

-

2002

- 2002-03-20 TW TW091105329A patent/TW565818B/zh not_active IP Right Cessation

- 2002-03-25 US US10/105,652 patent/US7375708B2/en not_active Expired - Fee Related

- 2002-03-26 KR KR10-2002-0016333A patent/KR100437346B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| TW565818B (en) | 2003-12-11 |

| KR20020081554A (ko) | 2002-10-28 |

| KR100437346B1 (ko) | 2004-06-25 |

| US7375708B2 (en) | 2008-05-20 |

| JP2002311883A (ja) | 2002-10-25 |

| US20020149606A1 (en) | 2002-10-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5389507B2 (ja) | 表示装置及び半導体装置 | |

| JP4942012B2 (ja) | 表示装置の駆動回路、および駆動方法 | |

| KR100696915B1 (ko) | 표시 장치 및 표시 제어 회로 | |

| JP3710728B2 (ja) | 液晶駆動装置 | |

| JPH07281636A (ja) | 液晶表示装置に用いられる駆動装置ならびに列電極駆動用半導体集積回路および行電極駆動用半導体集積回路 | |

| JP2005326633A (ja) | コントローラドライバ及び表示装置 | |

| US20070030192A1 (en) | Time division sampling digital to analog converter for driving flat panel display, method of implementing the same, and data driver circuit using the same | |

| KR19980018562A (ko) | 데이터 신호 출력 회로 및 이를 구비한 화상 표시 장치 | |

| JP4158658B2 (ja) | 表示ドライバ及び電気光学装置 | |

| JP4492334B2 (ja) | 表示装置および携帯端末 | |

| KR100430451B1 (ko) | 액정 디스플레이 장치의 구동 회로와 이 회로에 의해구동되는 액정 디스플레이 장치 | |

| JP2007140511A (ja) | 駆動電圧をディスプレイパネルに提供するシステム、及び、方法 | |

| US6380920B1 (en) | Electro-optical device drive circuit, electro-optical device and electronic equipment using the same | |

| JP3720275B2 (ja) | 画像表示パネル、画像表示装置、並びに画像表示方法 | |

| KR101202981B1 (ko) | 액정표시장치용 소스 드라이버 구동회로 | |

| US20070159439A1 (en) | Liquid crystal display | |

| JP3836721B2 (ja) | 表示装置、情報処理装置、表示方法、プログラム、及び記録媒体 | |

| JPH10301545A (ja) | 液晶パネルの駆動方法、セグメントドライバ、表示コントローラ及び液晶表示装置 | |

| US5673061A (en) | Driving circuit for display apparatus | |

| JP4147480B2 (ja) | データ転送回路及びフラットディスプレイ装置 | |

| JP4085323B2 (ja) | フラットディスプレイ装置及び携帯端末装置 | |

| JP2007219091A (ja) | 駆動回路、電気光学装置及び電子機器 | |

| JP2003029716A (ja) | 液晶表示装置及び液晶表示装置の駆動装置及び液晶表示装置の駆動方法 | |

| JP3775188B2 (ja) | 液晶表示装置及びその液晶表示装置を備えた情報機器 | |

| JPH10326089A (ja) | 表示装置の駆動回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040301 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040301 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050314 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050322 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050520 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20050520 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050906 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050907 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080916 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090916 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090916 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100916 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110916 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120916 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130916 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |