JP3710329B2 - 半導体レーザ素子およびその製造方法 - Google Patents

半導体レーザ素子およびその製造方法 Download PDFInfo

- Publication number

- JP3710329B2 JP3710329B2 JP18813999A JP18813999A JP3710329B2 JP 3710329 B2 JP3710329 B2 JP 3710329B2 JP 18813999 A JP18813999 A JP 18813999A JP 18813999 A JP18813999 A JP 18813999A JP 3710329 B2 JP3710329 B2 JP 3710329B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor laser

- sio

- film

- laser device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Lasers (AREA)

Description

【発明の属する技術分野】

本発明は、共振器端面およびその近傍に窓構造領域を設けて高出力動作時の特性を向上させた半導体レーザ素子およびその製造方法に関する。

【0002】

【従来の技術】

従来、高出力動作時における半導体レーザ素子の共振器端面の破壊、いわゆるCOD(Catastrophic Optical Damage)レベルを向上させるために、例えば特開平9−23037号公報には図9に示すような窓構造を有する半導体レーザ素子が開示されている。

【0003】

この図9において、(a)は光出射端面を含む斜視図であり、(b)は(a)のIIa−IIa’線における導波路の断面図であり、(c)は(a)のIIb−IIb’線における層厚方向の断面図である。

【0004】

図9において、1はn型GaAs基板、2はn型AlGaAs第1クラッド層、3は量子井戸活性層、4aはp型AlGaAs第2クラッド層、4bはp型AlGaAs第3クラッド層、5はp型GaAsコンタクト層、6(斜線部)は空孔拡散領域、8(斜線部)はプロトン注入領域、9はn側電極、10はp側電極、20はレーザ共振器の光出射端面、3aは活性層3のレーザ発光に寄与する活性領域、3bは活性層3の光出射端面20およびその近傍に形成された窓構造領域である。

【0005】

この半導体レーザ素子の製造について、図10を用いて説明する。

【0006】

まず、図10(a)に示すように、n型GaAs基板1上にn型AlGaAs第1クラッド層2、量子井戸活性層3およびp型AlGaAs第2クラッド層4aを順次エピタキシャル成長する。

【0007】

次に、図10(b)に示すように、第2クラッド層4a表面をSiO2膜16で覆い、レーザ共振器端面に達しない長さでレーザ共振器方向に延びるストライプ状開口部16aを形成する。

【0008】

続いて、このウエハをAs雰囲気下において800℃以上の温度でアニールすると、SiO2膜16がそれに接する第2クラッド層4a表面からGa原子を吸収し、第2クラッド層4a中にGa空孔を生じさせる。さらに、この空孔がアニールによって結晶内部に拡散し、量子井戸活性層に達すると量子井戸構造を無秩序化させる。無秩序化した活性層領域では実効的な禁制帯幅が広がるため、発振レーザ光に対して透明な窓構造領域として機能する。

【0009】

その後、SiO2膜16を除去し、図10(c)に示すように、第2クラッド層層4a上にp型AlGaAs第3クラッド層4bおよびp型GaAsコンタクト層5を順次エピタキシャル再成長する。

【0010】

次に、コンタクト層5上にレジスト膜を形成し、フォトリソグラフィ技術によって上記SiO2膜のストライプ状開口部16aと同じ領域に図10(d)に示すようなストライプ状レジスト17を形成する。そして、このレジスト17をマスクとしてコンタクト層5の上方からプロトン注入を行って電流ブロック層となる高抵抗領域8を形成する。

【0011】

最後に、GaAs基板1側にn側電極9、コンタクト層5上にp側電極10を形成し、ウエハを劈開することにより共振器端面を形成して図9に示した半導体レーザ素子を得る。

【0012】

上記公報には、この従来の半導体レーザ素子によれば、イオン注入によって活性層を無秩序化する場合に比べて、窓構造を備えた半導体レーザ素子が本来有する高光出力動作を可能にできると共に端面破壊レベルを高くして高信頼性を得ることができる旨が記載されている。

【0013】

【発明が解決しようとする課題】

しかしながら、上記従来の半導体レーザ素子の製造方法には、以下のような問題点がある。

【0014】

窓構造領域を形成後にSiO2膜を除去すると、窓構造領域と活性領域の境界を判別することができない。よって、電流ブロック層を形成する際にプロトン注入マスクとなるレジスト領域と窓構造領域とを位置合わせするために、別途位置合わせ用のマーキング工程等を行う必要がある。

【0015】

さらに、活性領域がレーザ端面に達したり、窓構造領域とプロトン領域にずれが生じると、半導体レーザ素子の信頼性や諸特性が悪化するため、上記位置合わせには高い精度が要求される。

【0016】

このような理由から、上記従来の半導体レーザ素子構造では、工程数の増加や精度保持に高い技術が要求され、半導体レーザ素子の量産時に歩留りを高くすることができないという問題があった。

【0017】

本発明はこのような従来技術の課題を解決すべくなされたものであり、高出力動作時の信頼性に優れ、高い歩留りで作製することができる窓構造の半導体レーザ素子およびその製造方法を提供することを目的とする。

【0018】

【課題を解決するための手段】

本発明の半導体レーザ素子の製造方法は、第1導電型の基板上に、少なくとも第1導電型の第1クラッド層、量子井戸活性層、第2導電型の第2クラッド層、第2導電型の第3クラッド層および第2導電型のキャップ層を順次成長させる工程と、該第3クラッド層および該キャップ層を共振器方向のリッジストライプ状に加工する工程と、該リッジストライプの両側面、および該リッジストライプ上にわたって第1導電型の電流ブロック層を成長させる工程と、該電流ブロック層上に、該リッジストライプと略直交する方向のストライプ状SiO2膜を形成する工程と、次いで、アニールにより該SiO2膜直下の該量子井戸活性層部分を選択的に無秩序化する工程と、次いで、該ストライプ状SiO2膜をマスクとして、リッジストライプ上における該SiO2膜が設けられた領域以外の前記電流ブロック層を除去して、前記キャップ層部分を露出させる工程と、その後に、少なくとも光出射端面が該量子井戸活性層の無秩序化領域を含むように共振器を形成する工程とを含む。

前記SiO2膜をスパッタリング法により形成するのが好ましい。

前記SiO2膜をレジストマスクを用いたリフトオフ法によりストライプ状に形成するのが好ましい。

【0019】

前記量子井戸活性層を構成する全井戸層厚が50nm以下であるのが好ましい。

【0020】

前記第3クラッド層の層厚が1.0μm以上1.5μm以下であるのが好ましい。

【0021】

前記電流ブロック層のドーパントがSiであり、そのキャリア濃度が7×1017cm-3以上5×1018cm-3以下であるのが好ましい。

【0022】

前記端面およびその近傍のリッジストライプ上部分に設けられた電流ブロック層は、共振器方向の長さが10μm以上60μm以下であるのが好ましい。

【0023】

前記端面およびその近傍のリッジストライプ上部分に設けられた電流ブロック層は、層厚が0.5μm以上1.5μm以下であるのが好ましい。

【0027】

以下、本発明の作用について説明する。

【0028】

本発明にあっては、光出射端面およびその近傍に量子井戸活性層を無秩序化した窓構造領域を有しているので、高出力動作時に端面での光吸収が抑制されて端面劣化を防ぐことができる。さらに、共振器端面およびその近傍のリッジストライプ上部分に第1導電型の電流ブロック層を備えているので、導波路部で端面への電流注入を防いで端面破壊レベルを向上させることができる。このリッジストライプは第2導電型の第3クラッド層で構成され、さらに第2導電型のキャップ層を有していてもよい。

【0029】

この半導体レーザ素子は、例えば共振器端面およびその近傍のリッジストライプ上部分に電流非注入領域を形成するためのマスクとしてSiO2膜を用いれば、このSiO2膜によって量子井戸活性層の無秩序化領域を形成することができる。よって、両領域の位置合わせ工程等を行わなくても、セルフアラインで電流非注入領域と窓構造領域とを形成することができる。

【0030】

上記量子井戸活性層を構成する全井戸層厚が50nm以下であれば、全井戸層を均一に無秩序化させることが可能である。

【0031】

さらに、第3クラッド層の層厚が1.5μm以下であれば、量子井戸活性層とSiO2マスクとの距離が短いので、全井戸層を均一に無秩序化させることが可能である。さらに、第3クラッド層の層厚が1μm以上であれば、高出力動作時にも光出力が飽和しないので好ましい。

【0032】

上記電流ブロック層のドーパントとしてSiを用いれば、空孔の拡散を促進させて確実に無秩序化させることが可能である。さらに、電流ブロック層のキャリア濃度が7×1017cm-3以上であれば、量子井戸活性層を均一に無秩序化させることが可能であり、5×1018cm-3以下であれば、Si自身の異常拡散による特性悪化を防ぐことが可能である。

【0033】

上記端面およびその近傍のリッジストライプ上部分に設けられた電流ブロック層は、共振器方向の長さが10μm以上60μm以下であれば、十分な窓効果を保持することができる。

【0034】

さらに、端面およびその近傍のリッジストライプ上部分に設けられた電流ブロック層の層厚が0.5μm以上であれば、コンタクト層を形成した後でもその電流ブロック層部分を容易に確認可能である。さらに、その電流ブロック層部分が1.5μm以下であれば、再成長後にリッジストライプ状部分を露出させるためのエッチング除去工程が容易であり、量産時の歩留りが向上する。

【0035】

本発明の半導体レーザ素子の製造方法にあっては、レーザ構造およびリッジストライプ形成し、基板全面に電流ブロック層を成長させた後、電流通路となるキャップ層を露出させる際に、リッジストライプと略直交する方向のストライプ状SiO2膜を形成してこのSiO2膜と直交していないキャップ層部分を露出させている。このSiO2膜は共振器端面およびその近傍に電流ブロック層を残して電流非注入領域を形成するためのエッチングマスクとして役割を有すると共に、SiO2膜直下の量子井戸活性層部分を選択的に無秩序化させる役割も有している。従って、電流非注入領域と量子井戸活性層の無秩序化領域とを、両領域の位置合わせ工程等を行わなくても、セルフアラインで形成することが可能である。

【0036】

上記SiO2膜をスパッタリング法によって形成することにより、無秩序化に必要なGa空孔を確実に生じさせることができるので好ましい。

【0037】

さらに、上記SiO2膜をレジストマスクを用いたリフトオフ法によってストライプ状に形成することにより、後工程での活性領域の構造変化を抑制することができ、信頼性が向上するので好ましい。

【0038】

【発明の実施の形態】

以下に、本発明の実施の形態について、図面を参照しながら説明する。

【0039】

(実施形態1)

図1に本実施形態の半導体レーザ素子の構造を示す。(a)は光出射端面を含む斜視図であり、(b)は(a)のIa−Ia’線における導波路の断面図であり、(c)は(a)のIb−Ib’線における層厚方向の断面図である。

【0040】

この半導体レーザ素子は、n−GaAs基板1上に、n−Al0.5Ga0.5As第1クラッド層102、ノンドープ量子井戸活性層103、p−Al0.5Ga0.5As第2クラッド層104およびp−GaAsエッチング停止層105が設けられている。

【0041】

その上にp−Al0.5Ga0.5As第3クラッド層106およびp−GaAsキャップ層107で構成されたリッジストライプ109が設けられ、リッジストライプ109の側面はn−Al0.7Ga0.3As電流ブロック層110で埋め込まれている。共振器の光出射端面120およびその近傍ではキャップ層107上にも電流ブロック層110が設けられて電流非注入領域115が構成され、共振器内部および光非出射端面121にはこのような電流非注入領域115を有していない。その上に電流ブロック層110および電流ブロック層が設けられていないリッジストライプ109上にわたってp−GaAsコンタクト層116が設けられてその上にp型電極117が設けられ、基板101側にはn型電極118が設けられている。

【0042】

さらに、光出射端面120およびその近傍の量子井戸活性層103は、電流非注入領域115の下方に、無秩序化により実効的な禁制帯幅が広くなった窓構造領域112を有している。

【0043】

なお、図1(c)において、キャップ層107が図1(a)の形状と異なるのは、エッチングを行った際に多少侵食されるためである。また、図1(c)において、キャップ層107を点線で示しているのは、キャップ層107とコンタクト層116とが同じ材料および導電型であり、機能的にも視角的にも分離できないからである。

【0044】

この半導体レーザ素子は、例えば以下のようにして作製することができる。

【0045】

まず、n−GaAs基板101を成長装置内にセットして第1回目の結晶成長により、図2(a)に示すようにキャリア濃度1×1018cm-3で厚さ1.0μmのn−Al0.5Ga0.5As第1クラッド層102、ノンドープ量子井戸活性層103、キャリア濃度1×1018cm-3で厚さ0.17μmのp−Al0.5Ga0.5As第2クラッド層104、キャリア濃度1×1018cm-3で厚さ0.003μmのp−GaAsエッチング停止層105、キャリア濃度1×1018cm-3で厚さ1.2μmのp−Al0.5Ga0.5As第3クラッド層106およびキャリア濃度1×1018cm-3で厚さ0.7μmのp−GaAsキャップ層107を順次成長させる。

【0046】

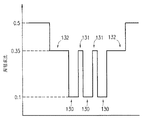

このとき、ノンドープ量子井戸活性層103として、図3に示すような厚さ0.01μmのAl0.1Ga0.9As量子井戸層130、厚さ0.005μmの2層のAl0.35Ga0.65As障壁層131および厚さ0.03μmのAl0.35Ga0.65As光ガイド層132からなる3重量子井戸構造を形成する。

【0047】

次に、上記半導体層が形成された基板を成長装置から取り出し、公知のフォトリソグラフィ法技術を用いてキャップ層107上に図2(b)に示すようなストライプ状のレジストマスク108を形成する。そして、公知の選択エッチング技術を用いてエッチング停止層105に達するように第3クラッド層106およびキャップ層107をリッジストライプ109状に加工する。本実施形態では、硫酸と過酸化水素水の混合溶液を用いて第3クラッド層106の途中までエッチングし、その後、GaAsに対して選択性を有するフッ化水素酸を用いてGaAsからなるエッチング停止層105で深さ方向のエッチングを停止させた。このときのリッジ幅はエッチング停止層105との界面において2μm〜3μmとなるように調整した。

【0048】

続いて、レジストマスクを除去し、基板を再度成長装置内にセットして第2回目の結晶成長により、図2(c)に示すようにキャリア濃度3×1018cm-3で厚さ1.0μmのn−Al0.7Ga0.3As電流ブロック層110を成長させる。

【0049】

その後、基板を再度成長装置から取り出し、図2(d)に示すように、厚さ0.1μmのSiO2ストライプ111をリッジストライプ109と直交するように形成する。このときのSiO2ストライプ111の共振器方向の長さは40μmとし、ストライプ間隔はレーザ共振器長と同じ800μmとした。

【0050】

次に、この基板をAs雰囲気下において800℃で5分間アニールする。このアニール中に、SiO2ストライプ111直下のn−AlGaAs結晶表面からGa原子が吸収され、n−AlGaAs結晶内部にGa空孔が生成される。このGa空孔は拡散定数が大きいため、直ちに基板方向に拡散し、量子井戸活性層103に達すると量子井戸構造を無秩序化させる。これにより、図2(e)に示すように、SiO2ストライプ111直下以外の量子井戸活性領域よりも実効的な禁制帯幅が広い窓構造領域112が形成される。

【0051】

続いて、図2(f)に示すように、レジストマスク113およびSiO2ストライプ111をマスクとして、レジスト開口部114から露出した電流ブロック層110をキャップ層107に達するまでエッチング除去する。本実施形態では、硫酸と過酸化水素水の混合溶液を用いて時間制御でエッチングを行った。この工程により、SiO2ストライプ111直下の電流ブロック層110は電流非注入領域115として残される。その後、図2(g)に示すように、レジストマスク113およびSiO2ストライプ111を除去する。

【0052】

次に、基板を再度成長装置内にセットして第3回目の結晶成長により、図2(h)に示すようにキャリア濃度5×1018cm-3で厚さ2.0μmのp−GaAsコンタクト層116を成長させる。

【0053】

その後、コンタクト層116の上面および基板101の下面に各々オーミック電極117、118を形成し、ウエハを劈開して共振器長を800μmに調整する。このとき、劈開位置が電流非注入領域115を含むように共振器を形成する。

【0054】

最後に、劈開された両端面120、121にコーティング膜を形成する。本実施形態では光出射端面120に反射率15%のAl2O3膜を形成し、光非出射端面121に反射率90%のAl2O3膜を形成した。以上により図1に示した本実施形態の半導体レーザ素子が得られる。

【0055】

このように、本実施形態の半導体レーザ素子は、SiO2ストライプ111によって、光出射端面およびその近傍のリッジストライプ上部分に残した電流ブロック層110による電流非注入領域115と、量子井戸活性層103の無秩序化による窓構造領域112とがセルフアラインで形成される。従って、両領域を別工程で作製する従来の半導体レーザ素子と比べて、両領域の位置合わせ等の工程を必要とせず、また、位置ずれによる特性不良等も生じない。

【0056】

さらに、電流非注入領域115はその他の平坦部に比べて電流ブロック層110の層厚分だけ表面が高くなっており、MOCVD法やMBE法によるコンタクト層116の形成後もその段差が存在する。従って、劈開によるレーザ共振器形成の際に、劈開位置が電流非注入領域115を含むように共振器を形成するのが容易である。このとき、端面およびその近傍のリッジストライプ上部分に設けられた電流ブロック層の層厚が0.1μm以上であればその機能を充分に果たすことができるが、コンタクト層116の形成後に段差確認を容易にするためには、0.5μm以上であるのが好ましい。また、2回目の結晶成長後にキャップ層107上に成長される電流非注入領域115以外の電流ブロック層110部分を歩留まり良くエッチング除去するためには、電流ブロック層の層厚が1.5μm以下であるのが好ましい。

【0057】

次に、量子井戸活性層103中の量子井戸層130の層数と層厚を変化させて本実施形態の半導体レーザ素子を作製し、全量子井戸層厚と半導体レーザ素子のCODレベルとの関係を調べた結果を図4に示す。このときの量子井戸層130のAl組成比はレーザ発振波長が780nmとなるように調整した。

【0058】

この図4から、層数によらず、全量子井戸層厚が50nmを超えるとCODレベルが低下することがわかる。この理由としては、全量子井戸層厚が50nmを超えると全ての量子井戸層が均一に無秩序化されず、レーザ光を吸収してCODに至ることが考えられる。従って、本発明の半導体レーザ素子において、全量子井戸層厚は50nm以下であるのが好ましいことがわかる。

【0059】

次に、p−AlGaAs第3クラッド層106の層厚を変化させて本実施形態の半導体レーザ素子を作製し、第3クラッド層の層厚と半導体レーザ素子のCODレベルとの関係を調べた結果を図5に示す。

【0060】

この図5から、第3クラッド層106の層厚が1.0μm未満ではキャップ層107による光吸収のために光出力が飽和し、CODに至らなかった。一方、第3クラッド層106の層厚が1.5μmを超えるとCODレベルが低下した。この理由としては、Ga空孔の発生源であるSiO2ストライプ111から量子井戸活性層103との距離が長くなるために量子井戸層が均一に無秩序化されず、レーザ光を吸収してCODに至ることが考えられる。従って、本発明の半導体レーザ素子において、第3クラッド層の層厚は1.0μm以上で、かつ、1.5μm以下であるのが好ましいことがわかる。

【0061】

次に、n−AlGaAs電流ブロック層110のドーパントおよびキャリア濃度を変化させて本実施形態の半導体レーザ素子を作製し、電流ブロック層のドーパント種およびキャリア濃度と半導体レーザ素子のCODレベルとの関係を調べた結果を図6に示す。このときのドーパントとしてはSiおよびSeを用いた。

【0062】

この図6から、ドーパントとしてSeを用いるよりもSiを用いる方がCODレベルが高くなることがわかる。この理由としては以下のことが考えられる。Siは両性種であるのでIII族およびV族のいずれの格子位置にも入るが、このSi(III)とSi(V)の対は電気的に中性であるため、価電状態を変えることなく結晶格子内を容易に移動することができる。これにより、Ga空孔の拡散を助長する働きがあると推察され、確実に無秩序化を生じさせることができると考えられる。

【0063】

さらに、図6から、電流ブロック層のキャリア濃度については7×1017cm-3以上でCODレベルが急激に高くなることがわかる。この理由は、7×1017cm-3未満ではSi(III)とSi(V)の対を作りにくいので、Ga空孔の拡散による無秩序化が助長されないためであると考えられる。一方、キャリア濃度が5×1018cm-3を超えるとキャリア濃度が高すぎるため、p−AlGaAs第2クラッド層104のn型化やp−n接合位置のシフト等が生じ、良好なレーザ特性が得られなかった。従って、本発明の半導体レーザ素子において、電流ブロック層のキャリア濃度が7×1017cm-3以上5×1018cm-3以下であれるのが好ましいことがわかる。

【0064】

次に、光出射端面120およびその近傍に形成した電流ブロック層110による電流非注入領域115の共振器方向の長さを変化させて本実施形態の半導体レーザ素子を作製し、電流非注入領域115の長さと半導体レーザ素子のCODレベルおよび動作電圧との関係を調べた結果を図7に示す。

【0065】

この図7から、電流非注入領域115の共振器方向の長さが10μm未満では充分な端面非注入効果が得られず、CODレベルが低下することがわかる。一方、電流非注入領域115の共振器方向の長さが60μmを超えると、CODレベルは高いが、電流通路が狭くなるために動作電圧が増大した。従って、本発明の半導体レーザ素子において、電流非注入領域115の共振器方向の長さは10μm以上60μm以下であるのが好ましいことがわかる。

【0066】

(実施形態2)

本実施形態では、SiO2ストライプ111をスパッタリング法、プラズマCVD法および電子ビーム蒸着法によって各々形成し、CODレベルを比較した。その他の構造および作製方法は実施形態1と同様にした。

【0067】

下記表1に各SiO2膜形成方法によるCODレベルを示す。

【0068】

【表1】

【0069】

この表1から、スパッタリング法によってSiO2膜を形成した半導体レーザ素子が最もCODレベルが高いことがわかる。

【0070】

この理由は、スパッタリング法によるSiO2膜は下地への密着性に優れており、Ga空孔の生成と拡散を生じ易いためであると考えられる。従って、本発明の半導体レーザ素子において、SiO2膜をスパッタリング法により形成するのが好ましいことがわかる。

【0071】

(実施形態3)

本実施形態では、SiO2ストライプ111を形成する際に、ストライプと反対のパターンのレジスト膜を予め形成してその上にSiO2膜を形成した後、不要なSiO2膜部分をレジスト共に除去する、いわゆる「リフトオフ法」によって非注入領域分を形成して半導体レーザ素子を作製した。さらに、比較のためにSiO2膜を全面に形成した後でレジストストライプを形成し、エッチングによってSiO2ストライプ111を形成して半導体レーザ素子を作製した。その他の構造および作製方法は実施形態1と同様にした。

【0072】

図8に、両半導体レーザ素子について、1000時間の寿命試験を行ったエージング結果を示す。なお、寿命試験は動作温度60℃、レーザ出力120mWの連続駆動条件で行った。

【0073】

通常、エージング寿命が1000時間以上であれば使用上問題は生じない。図8に示すように、エッチング法によってSiO2膜をストライプ加工した半導体レーザ素子においてもこの基準を満たしているが、リフトオフ法によってSiO2膜を加工した半導体レーザ素子はさらに長寿命であることがわかる。

【0074】

この理由としては、以下のようなことが考えられる。SiO2ストライプ111の下にGa空孔が生成されるのは主としてアニール処理を行った後であるが、アニール処理前であってもSiO2膜が接しているAlGaAs界面においてはSiO2膜形成時の温度や衝撃によって若干のGa空孔が生成される。リフトオフ法を用いる場合には、無秩序化領域以外は予めマスクされているので、SiO2膜によるGa空孔生成が起こらない。従って、その後のアニール処理を経ても量子井戸活性層の構造変化が起こらないためであると考えられる。従って、本発明のの半導体レーザ素子において、SiO2膜ををレジストマスクを用いたリフトオフ法によりストライプ状に加工するのが好ましいことがわかる。

【0075】

なお、上記実施形態1〜実施形態3では、光出射端面およびその近傍に窓構造領域と電流非注入領域を設けたが、光出射端面と光非出射端面側の両方に窓構造領域と電流非注入領域を設けてもよい。

【0076】

さらに、上記実施形態では多重量子井戸活性層の例について説明したが、単一量子井戸活性層に対しても同様に本発明は適用可能である。また、半導体層の材料としてはAlGaAs系材料を用いたが、赤色レーザ材料として用いられるInGaP系材料およびInGaAlP系材料、通信用長波長レーザ材呂うとして用いられるInGaAs系材料およびInGaAsP系材料等の他の材料系を用いることもできる。さらに、第1導電型としてn型、第2導電型としてp型の半導体層を成長させた半導体レーザ素子、および第1導電型としてp型、第2導電型としてn型の半導体層を成長させた半導体レーザ素子のいずれについても本発明は適用可能である。但し、Ga空孔の拡散を助長するためには電流ブロック層のドーパントとしてSiを用いるのが好ましく、このSiはn型ドーパントであるので、第1導電型としてn型の半導体層を成長させるのが好ましい。

【0077】

本発明の半導体レーザ素子の製造工程において、成長法としてはMOCVD法やMBE法等を用いることができる。

【0078】

【発明の効果】

以上詳述したように、本発明の半導体レーザ素子によれば、光出射端面およびその近傍に量子井戸活性層を無秩序化した窓構造領域を有しているので、高出力動作時に導波路端面での光吸収を抑制して端面劣化を防ぐことができる。さらに、共振器端面およびその近傍のリッジストライプ上部分に第1導電型の電流ブロック層を備えているので、導波路部で端面への電流注入を防いで端面破壊レベルを向上させることができる。

【0079】

この半導体レーザ素子の製造においては、電流ブロック層による電流非注入領域を形成するためのマスクとして、量子井戸活性層に無秩序化領域を形成するためのSiO2マスクを用いることができるので、両領域の位置合わせ工程等を付け加えることなく、セルフアラインで電流非注入領域と窓構造領域とを形成することができる。よって、所望の窓構造を備えた半導体レーザ素子の製造工程を簡素化して高歩留まりで作製することができる。

【0080】

さらに、量子井戸活性層を構成する全井戸層厚を50nm以下とすることにより、全井戸層を均一に無秩序化させることができる。よって、窓構造を備えた半導体レーザ素子をさらに高歩留まりで作製することができる。

【0081】

さらに、第3クラッド層の厚みを1μm以上1μm以下にすることにより、光出力の飽和を防ぐと共に量子井戸活性層の無秩序化を均一にすることができる。よって、高出力時の特性に優れた窓構造の半導体レーザ素子を高歩留まりで作製することができる。

【0082】

さらに、電流ブロック層のドーパントとしてSiを用いることにより、空孔の拡散を促進させて確実に無秩序化を生じさせることができる。また、電流ブロック層のSiキャリア濃度を7×1017cm-3以上5×1018cm-3以下にすることにより、量子井戸活性層を均一に無秩序化させると共にSi自身の異常拡散による特性悪化を防ぐことができる。よって、特性に優れた窓構造の半導体レーザ素子を高歩留まりで作製することができる。

【0083】

さらに、端面およびその近傍のリッジストライプ上部分に設けた電流ブロック層の共振器方向の長さを10μm以上60μm以下にすることにより、動作電圧上昇を抑えると共に十分な窓効果を保持することができる。よって、信頼性に優れた窓構造の半導体レーザ素子を得ることができる。

【0084】

さらに、端面およびその近傍のリッジストライプ上部分に設けた電流ブロック層の層厚を0.5μm以上1.0μm以下にすれば、コンタクト層を形成した後でもその電流ブロック層部分を容易に確認できるので、無秩序化領域を確認することができ、しかも、再成長後のエッチング除去工程が容易である。よって、所望の窓構造を備えた半導体レーザ素子を高歩留まりで作製することができる。

【0085】

本発明の半導体レーザ素子の製造方法によれば、電流非注入領域と量子井戸活性層の無秩序化領域とを、両領域の位置合わせ工程等を行わなくても、セルフアラインで形成することができる。よって、所望の窓構造を有する半導体レーザ素子を高歩留まりで作製することができる。

【0086】

さらに、このSiO2膜をスパッタリング法によって形成することにより、量子井戸活性層の無秩序化に必要なGa空孔を確実に生じさせることができる。よって、信頼性に優れた窓構造の半導体レーザ素子を得ることができる。

【0087】

さらに、ストライプ状のSiO2膜をレジストマスクを用いたリフトオフ法によって形成することにより、後工程での活性領域の構造変化を抑制することができ、信頼性を向上させることができる。よって、信頼性に優れた窓構造の半導体レーザ素子を得ることができる。

【図面の簡単な説明】

【図1】本実施形態の半導体レーザ素子の構造を示す図であり、(a)は光出射端面を含む斜視図であり、(b)は(a)のIa−Ia’線における導波路の断面図であり、(c)は(a)のIb−Ib’線における層厚方向の断面図である。

【図2】実施形態1の半導体レーザ素子の製造工程を説明するための図であり、(a)は断面図、(b)〜(h)は斜視図である。

【図3】実施形態1の半導体レーザ素子における量子井戸活性層のAl組成プロファイルを示す図である。

【図4】実施形態1の半導体レーザ素子における全量子井戸層厚とCODレベルとの関係を示す図である。

【図5】実施形態1の半導体レーザ素子におけるp−AlGaAs第3クラッド層厚とCODレベルとの関係を示す図である。

【図6】実施形態1の半導体レーザ素子におけるn−AlGaAs電流ブロック層のキャリア濃度とCODレベルとの関係を示す図である。

【図7】実施形態1の半導体レーザ素子における電流非注入領域の長さとCODレベルとの関係を示す図である。

【図8】実施形態3の半導体レーザ素子におけるエージング結果を示す図である。

【図9】従来の窓構造の半導体レーザ素子の構造を示す図であり、(a)は光出射端面を含む斜視図であり、(b)は(a)のIIa−IIa’線における導波路の断面図であり、(c)は(a)のIIb−IIb’線における層厚方向の断面図である。

【図10】従来の窓構造の半導体レーザ素子の製造工程を説明するための図であり、(a)は断面図、(b)〜(d)は斜視図である。

【符号の説明】

101 基板

102 第1クラッド層

103 量子井戸活性層

104 第2クラッド層

105 エッチング停止層

106 第3クラッド層

107 キャップ層

108 ストライプ状レジストマスク

109 リッジストライプ

110 電流ブロック層

111 SiO2ストライプ

112 窓構造領域

113 レジストマスク

114 開口部

115 電流非注入領域

116 コンタクト層

117 p型電極

118 n型電極

120 光出射端面

121 光非出射端面

130 量子井戸層

131 障壁層

132 光ガイド層

Claims (3)

- 第1導電型の基板上に、少なくとも第1導電型の第1クラッド層、量子井戸活性層、第2導電型の第2クラッド層、第2導電型の第3クラッド層および第2導電型のキャップ層を順次成長させる工程と、

該第3クラッド層および該キャップ層を共振器方向のリッジストライプ状に加工する工程と、

該リッジストライプの両側面、および該リッジストライプ上にわたって第1導電型の電流ブロック層を成長させる工程と、

該電流ブロック層上に、該リッジストライプと略直交する方向のストライプ状SiO2膜を形成する工程と、

次いで、アニールにより該SiO2膜直下の該量子井戸活性層部分を選択的に無秩序化する工程と、

次いで、該ストライプ状SiO2膜をマスクとして、リッジストライプ上における該SiO2膜が設けられた領域以外の前記電流ブロック層を除去して、前記キャップ層部分を露出させる工程と、

その後に、少なくとも光出射端面が該量子井戸活性層の無秩序化領域を含むように共振器を形成する工程と

を含む半導体レーザ素子の製造方法。 - 前記SiO2膜をスパッタリング法により形成する請求項1に記載の半導体レーザ素子の製造方法。

- 前記SiO2膜をレジストマスクを用いたリフトオフ法によりストライプ状に形成する請求項1または請求項2に記載の半導体レーザ素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18813999A JP3710329B2 (ja) | 1999-07-01 | 1999-07-01 | 半導体レーザ素子およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18813999A JP3710329B2 (ja) | 1999-07-01 | 1999-07-01 | 半導体レーザ素子およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001015859A JP2001015859A (ja) | 2001-01-19 |

| JP3710329B2 true JP3710329B2 (ja) | 2005-10-26 |

Family

ID=16218436

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP18813999A Expired - Fee Related JP3710329B2 (ja) | 1999-07-01 | 1999-07-01 | 半導体レーザ素子およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3710329B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4102554B2 (ja) | 2000-10-31 | 2008-06-18 | シャープ株式会社 | 半導体レーザ素子及びその製造方法 |

| JP2002261379A (ja) * | 2001-03-02 | 2002-09-13 | Mitsubishi Electric Corp | 半導体デバイスおよびそれを応用した光半導体デバイス |

| JP2003031894A (ja) * | 2001-07-19 | 2003-01-31 | Sony Corp | 半導体レーザおよびその製造方法 |

| GB0212072D0 (en) * | 2002-05-25 | 2002-07-03 | Intense Photonics Ltd | Control of contact resistance in quantum well intermixed devices |

| JP4833664B2 (ja) * | 2003-12-15 | 2011-12-07 | 古河電気工業株式会社 | 半導体素子の製造方法 |

| JP4502867B2 (ja) * | 2005-04-12 | 2010-07-14 | パナソニック株式会社 | 半導体レーザ装置および半導体レーザ装置の製造方法 |

| US10033154B2 (en) | 2010-03-03 | 2018-07-24 | Furukawa Electronic Co., Ltd. | Semiconductor optical element, semiconductor laser element, and method for manufacturing semiconductor optical element and semiconductor laser element, and method for manufacturing semiconductor laser module and semiconductor element |

| JP4904413B2 (ja) | 2010-04-26 | 2012-03-28 | 古河電気工業株式会社 | 半導体レーザ素子および半導体レーザ素子の製造方法 |

| JP5998460B2 (ja) * | 2011-11-21 | 2016-09-28 | 三菱電機株式会社 | 半導体レーザダイオードとその製造方法 |

| JP5731084B2 (ja) | 2013-02-13 | 2015-06-10 | 古河電気工業株式会社 | 半導体光素子、半導体レーザ素子、及びその製造方法、並びに半導体レーザモジュール及び半導体素子の製造方法 |

| WO2016024609A1 (ja) | 2014-08-12 | 2016-02-18 | 古河電気工業株式会社 | 半導体素子 |

-

1999

- 1999-07-01 JP JP18813999A patent/JP3710329B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001015859A (ja) | 2001-01-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5764669A (en) | Semiconductor laser including disordered window regions | |

| JP3387076B2 (ja) | 半導体レーザ及びその製造方法 | |

| JP2008227551A (ja) | 半導体素子の製造方法および半導体素子 | |

| US5737351A (en) | Semiconductor laser including ridge structure extending between window regions | |

| JP3710329B2 (ja) | 半導体レーザ素子およびその製造方法 | |

| KR100232993B1 (ko) | 반도체 레이저장치 및 그 제조방법 | |

| JPH07162086A (ja) | 半導体レーザの製造方法 | |

| JPH10233556A (ja) | リッジ型半導体レーザダイオードとその製造方法 | |

| JP2001210907A (ja) | 半導体素子の製造方法および半導体素子 | |

| JP2686306B2 (ja) | 半導体レーザ装置とその製造方法 | |

| JPH10261835A (ja) | 半導体レーザ装置、及びその製造方法 | |

| JP2001057459A (ja) | 半導体レーザ | |

| KR100417096B1 (ko) | 반도체 레이저 장치 및 그 제조방법 | |

| US5770471A (en) | Method of making semiconductor laser with aluminum-free etch stopping layer | |

| JP3501676B2 (ja) | 半導体レーザ装置の製造方法 | |

| JP2001185809A (ja) | 半導体光デバイス装置及びその製造方法 | |

| KR100372479B1 (ko) | 반도체 레이저장치 및 그 제조방법 | |

| JP2865160B2 (ja) | 半導体レーザの製造方法 | |

| JP2002026451A (ja) | 半導体光デバイス装置 | |

| JP2001053381A (ja) | 半導体レーザ装置およびその製造方法 | |

| JP4502867B2 (ja) | 半導体レーザ装置および半導体レーザ装置の製造方法 | |

| JP2003152282A (ja) | 半導体レーザ素子 | |

| JPH11145553A (ja) | 半導体レーザ素子及びその作製法 | |

| JPH08125280A (ja) | 半導体レーザ装置,及びその製造方法 | |

| JP3722532B2 (ja) | 半導体レーザ素子およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040702 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040903 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041028 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050311 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050428 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050809 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050809 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080819 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090819 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090819 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100819 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110819 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110819 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120819 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120819 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130819 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |