JP3665570B2 - コンデンサ電極装置 - Google Patents

コンデンサ電極装置 Download PDFInfo

- Publication number

- JP3665570B2 JP3665570B2 JP2000591655A JP2000591655A JP3665570B2 JP 3665570 B2 JP3665570 B2 JP 3665570B2 JP 2000591655 A JP2000591655 A JP 2000591655A JP 2000591655 A JP2000591655 A JP 2000591655A JP 3665570 B2 JP3665570 B2 JP 3665570B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- oxygen

- silicide

- iridium

- silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000003990 capacitor Substances 0.000 title claims description 14

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 154

- 239000001301 oxygen Substances 0.000 claims description 154

- 229910052760 oxygen Inorganic materials 0.000 claims description 154

- 229910052741 iridium Inorganic materials 0.000 claims description 114

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 claims description 112

- 239000000758 substrate Substances 0.000 claims description 49

- 229910021332 silicide Inorganic materials 0.000 claims description 46

- 229910052710 silicon Inorganic materials 0.000 claims description 46

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 45

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 claims description 45

- 239000010703 silicon Substances 0.000 claims description 45

- 230000004888 barrier function Effects 0.000 claims description 43

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 40

- 238000004377 microelectronic Methods 0.000 claims description 32

- 229910052751 metal Inorganic materials 0.000 claims description 31

- 239000002184 metal Substances 0.000 claims description 31

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 28

- 229920005591 polysilicon Polymers 0.000 claims description 28

- HTXDPTMKBJXEOW-UHFFFAOYSA-N dioxoiridium Chemical compound O=[Ir]=O HTXDPTMKBJXEOW-UHFFFAOYSA-N 0.000 claims description 27

- 229910052697 platinum Inorganic materials 0.000 claims description 23

- 239000012298 atmosphere Substances 0.000 claims description 22

- 229910044991 metal oxide Inorganic materials 0.000 claims description 22

- 150000004706 metal oxides Chemical class 0.000 claims description 22

- 238000000034 method Methods 0.000 claims description 14

- 239000004065 semiconductor Substances 0.000 claims description 13

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 claims description 13

- 229910021342 tungsten silicide Inorganic materials 0.000 claims description 13

- 230000015654 memory Effects 0.000 claims description 12

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 claims description 10

- 238000004544 sputter deposition Methods 0.000 claims description 9

- 239000010955 niobium Substances 0.000 claims description 8

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 claims description 7

- 229910017052 cobalt Inorganic materials 0.000 claims description 5

- 239000010941 cobalt Substances 0.000 claims description 5

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 5

- 229910052758 niobium Inorganic materials 0.000 claims description 5

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 claims description 5

- 229910052763 palladium Inorganic materials 0.000 claims description 5

- 229910021339 platinum silicide Inorganic materials 0.000 claims description 5

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 claims description 4

- 238000004519 manufacturing process Methods 0.000 claims description 4

- 229910052715 tantalum Inorganic materials 0.000 claims description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 3

- 229910021341 titanium silicide Inorganic materials 0.000 claims description 3

- WEAMLHXSIBDPGN-UHFFFAOYSA-N (4-hydroxy-3-methylphenyl) thiocyanate Chemical compound CC1=CC(SC#N)=CC=C1O WEAMLHXSIBDPGN-UHFFFAOYSA-N 0.000 claims description 2

- TWRSDLOICOIGRH-UHFFFAOYSA-N [Si].[Si].[Hf] Chemical compound [Si].[Si].[Hf] TWRSDLOICOIGRH-UHFFFAOYSA-N 0.000 claims description 2

- VKTGMGGBYBQLGR-UHFFFAOYSA-N [Si].[V].[V].[V] Chemical compound [Si].[V].[V].[V] VKTGMGGBYBQLGR-UHFFFAOYSA-N 0.000 claims description 2

- YXTPWUNVHCYOSP-UHFFFAOYSA-N bis($l^{2}-silanylidene)molybdenum Chemical compound [Si]=[Mo]=[Si] YXTPWUNVHCYOSP-UHFFFAOYSA-N 0.000 claims description 2

- 229910021357 chromium silicide Inorganic materials 0.000 claims description 2

- 229910021360 copper silicide Inorganic materials 0.000 claims description 2

- 229910052742 iron Inorganic materials 0.000 claims description 2

- 229910021344 molybdenum silicide Inorganic materials 0.000 claims description 2

- 229910021334 nickel silicide Inorganic materials 0.000 claims description 2

- 229910052727 yttrium Inorganic materials 0.000 claims description 2

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical group [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 claims description 2

- 229910021355 zirconium silicide Inorganic materials 0.000 claims description 2

- 150000002503 iridium Chemical class 0.000 claims 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 claims 1

- 238000000151 deposition Methods 0.000 description 19

- 230000008021 deposition Effects 0.000 description 17

- 229910052581 Si3N4 Inorganic materials 0.000 description 14

- 239000010936 titanium Substances 0.000 description 13

- 230000003647 oxidation Effects 0.000 description 11

- 238000007254 oxidation reaction Methods 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- 229910000457 iridium oxide Inorganic materials 0.000 description 9

- 229910000510 noble metal Inorganic materials 0.000 description 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 8

- 238000010586 diagram Methods 0.000 description 8

- 238000009792 diffusion process Methods 0.000 description 8

- 239000000463 material Substances 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- 230000008569 process Effects 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 238000002955 isolation Methods 0.000 description 5

- 238000012360 testing method Methods 0.000 description 5

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 4

- 238000000137 annealing Methods 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 229910052707 ruthenium Inorganic materials 0.000 description 4

- ZXEYZECDXFPJRJ-UHFFFAOYSA-N $l^{3}-silane;platinum Chemical compound [SiH3].[Pt] ZXEYZECDXFPJRJ-UHFFFAOYSA-N 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- UGACIEPFGXRWCH-UHFFFAOYSA-N [Si].[Ti] Chemical compound [Si].[Ti] UGACIEPFGXRWCH-UHFFFAOYSA-N 0.000 description 3

- 230000003750 conditioning effect Effects 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 229910052746 lanthanum Inorganic materials 0.000 description 3

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 229910052454 barium strontium titanate Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 238000012512 characterization method Methods 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 238000005546 reactive sputtering Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052702 rhenium Inorganic materials 0.000 description 2

- WUAPFZMCVAUBPE-UHFFFAOYSA-N rhenium atom Chemical compound [Re] WUAPFZMCVAUBPE-UHFFFAOYSA-N 0.000 description 2

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 229910052712 strontium Inorganic materials 0.000 description 2

- 238000009864 tensile test Methods 0.000 description 2

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- 229910018921 CoO 3 Inorganic materials 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229910000566 Platinum-iridium alloy Inorganic materials 0.000 description 1

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 1

- 229910004121 SrRuO Inorganic materials 0.000 description 1

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- VVTSZOCINPYFDP-UHFFFAOYSA-N [O].[Ar] Chemical compound [O].[Ar] VVTSZOCINPYFDP-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 1

- 229910002115 bismuth titanate Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- VIUKNDFMFRTONS-UHFFFAOYSA-N distrontium;niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[Sr+2].[Sr+2].[Nb+5].[Nb+5] VIUKNDFMFRTONS-UHFFFAOYSA-N 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 229910052745 lead Inorganic materials 0.000 description 1

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 1

- 229910000487 osmium oxide Inorganic materials 0.000 description 1

- JIWAALDUIFCBLV-UHFFFAOYSA-N oxoosmium Chemical compound [Os]=O JIWAALDUIFCBLV-UHFFFAOYSA-N 0.000 description 1

- DYIZHKNUQPHNJY-UHFFFAOYSA-N oxorhenium Chemical compound [Re]=O DYIZHKNUQPHNJY-UHFFFAOYSA-N 0.000 description 1

- SJLOMQIUPFZJAN-UHFFFAOYSA-N oxorhodium Chemical compound [Rh]=O SJLOMQIUPFZJAN-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- HWLDNSXPUQTBOD-UHFFFAOYSA-N platinum-iridium alloy Chemical class [Ir].[Pt] HWLDNSXPUQTBOD-UHFFFAOYSA-N 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 239000011591 potassium Substances 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 229910003449 rhenium oxide Inorganic materials 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000010948 rhodium Substances 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 229910003450 rhodium oxide Inorganic materials 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 1

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 1

- 238000012916 structural analysis Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000010998 test method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/75—Electrodes comprising two or more layers, e.g. comprising a barrier layer and a metal layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28568—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table the conductive layers comprising transition metals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/55—Capacitors with a dielectric comprising a perovskite structure material

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Memories (AREA)

- Physical Vapour Deposition (AREA)

- Electrodes Of Semiconductors (AREA)

Description

本発明は、半導体技術の分野にあり、かつベース基板、シリコン含有層及び酸素バリア層を有するマイクロエレクトロニック構造に関する。

【0002】

半導体メモリのメモリ容量を一層高めるために、高ε誘電体(ε>20)又は強誘電性の誘電体の利用が望まれる。そのために有利な材料は、その堆積及びコンディショニングの際に酸素含有雰囲気及び800℃までの温度を必要とする。しかし、これらの条件においては、電極のために従来利用された材料の急速な酸化が考慮されるべきである。それ故に、同様に耐酸化性電極材料の利用が提案された。傑出した代替品は、例えば白金である。しかし、白金を利用する場合、シリコンと白金を直接接触した際に高いプロセス温度において障害となる白金ケイ化物が形成されるという問題が生じる。酸素は、比較的容易に白金を通過して拡散することができ、かつその下にあるシリコンを酸化することがある。これらの理由により、白金電極とポリシリコンによって満たされかつ選択トランジスタに電極を接続するスルーホールとの間にバリアが不可欠である。

【0003】

バリアには、とくに次の要求が課される。これは、シリコンの電気的に絶縁する酸化を排除するために、一方においてスルーホールから白金電極へのシリコン拡散を防止しなければならず、かつ他方において白金からスルーホールへの酸素拡散を阻止しなければならない。その上さらに、バリア自体は、プロセス条件において安定でなければならない。

【0004】

電極バリアシステムの形の初めに挙げたマイクロエレクトロニック構造の可能な構成は、例えば米国特許第5,581,439号明細書に記載されている。ここではシリコン窒化物層内にシリコン拡散を阻止するチタン窒化物層が埋め込まれており、このシリコン窒化物層は、少なくともチタン窒化物層を側方において酸化から保護する。シリコン窒化物カラー上に、白金被覆を有するパラジウムベース部材があり、これらは一緒になって電極を形成する。同時に、少なくともパラジウムによって、チタン窒化物層の酸化を防止することを目的としている。

【0005】

それに対して、別の材料による別の電極バリアシステムの構成が、J.Kudoeet al.,“A High Stability Electrode Technology for Stacked SrBi2Ta2O9 Capacitors Applicatable to Advanced Ferroelectric Memory”,IEDM 1997、第609〜612頁の専門文献に記載されている。ここに開示された構成は、チタン−シリコン窒化物からなるバリアを優先し、このバリアは純粋なイリジウム層及びイリジウム酸化物層によって覆われている。チタン−シリコン窒化物バリアはシリコン拡散を阻止するが、それ自体酸化から保護されなければならない。この役割をイリジウム酸化物層及び純粋なイリジウム層が引受ける。しかし、高い温度において、とくに800℃において、純粋なイリジウム層は、チタン−シリコン窒化物バリアとともに、電気的に粗悪な伝導性のイリジウムケイ化物を形成することがわかった。

【0006】

同じ問題は、Seanger et al.,“Buried, self−aligned barrier layer structures for peroviskite-based memory devices comprising Pt or Ir bottom electrodes on silicon-contributing substrates”, J. Appl. Phys. 83(2), 1998, 第802〜813頁によって望まれる構成においても生じる。この専門文献から、窒素雰囲気中におけるアニール工程中に純粋なイリジウム及びポリシリコンから、妨害となるイリジウムケイ化物が生じることを推察すことができる。それ故に、このけい化は酸素含有雰囲気における先行するアニール工程によって、イリジウムの完全な酸化によって阻止されるという。不都合にも酸素雰囲気における、このアニール工程はとくにイリジウムの深い酸化に関して管理困難であるので、イリジウム層の不均一な層厚さの際にポリシリコンの酸化を惹起し、それによりポリシリコンとイリジウムとの間の電気的な接触が中断されることもある。

【0007】

後続の酸素処理を含む堆積された純粋なイリジウム層の使用は、同様にJeoneet al.,“Thermal stability of Ir/polycrystallen-Si structure for bottom electrode of integrated ferroelectric capacitors”, Appl. Phys. Lett. 71 (4), 1997, 第467〜469頁の専門文献に開示されている。それに対して、バリアとしての二酸化イリジウムの利用は、Cho et al.,“Preparation and Characterization of Iridium Oxide Thin Fulm Grown by DC Reactive Sputtering”, Jpn. J. Appl. Phys. 36, 1997, 第1722〜1727頁に記載されている。それに対して白金、ルテニウム及びレニウムからなる多層システムの使用は、Onishi et al.,“A New High Temperature Electrode-Barrier Technology On High Density Ferroelectric Capacitor Structure”, IEDM 96, 第699〜702頁;“Bhatt et al.,“Novel high temperatuer multilayer electrode−barrier structuer for high-density ferroelectric memories”, Appl. Phys. Lett. 71 (5), 1997, 第719〜721頁; Onishi et al., “High Temperature Barrier Electrode Technology for High Density Ferroelectric Memories with Stacked Capacitor Structure”, Electrochem. Soc. 145, 1998, 第2563〜2568頁; Aoyama et al.,“Interfacial Layer between Si and Ru Films Deposited by Sputtering in Ar/O2 Mixture Ambient”、Jap. J. Appl. Phys. 37, 1998, 第L242〜L244頁から公知である。

【0008】

その他のバリアのアプローチは、米国特許第5852307号明細書に提案されており、これは、軽く酸化したルテニウム層及び二酸化ルテニウム層の使用を記載している。

【0009】

しかし、従来公知のすべてのバリア層において、これらは必要な高いプロセス温度においてとくに高ε材料又は強誘電体材料のコンディショニングのための必要な温度ステップにおいて、もはや十分に安定ではないという危険が存在する。

【0010】

従って、本発明の課題は、800℃までの温度においても十分に安定であるマイクロエレクトロニック構造、及びこのような構造を製造する方法を提供することにある。

【0011】

この課題は、本発明によれば、冒頭に記載したようなマイクロエレクトロニック構造において、シリコン含有層と酸素バリア層との間に酸素含有イリジウム層があり、このイリジウム層が酸素含有雰囲気中におけるスパッタリング法(スパッタ)によって製造可能であり、その際雰囲気中の酸素の体積割合が2.5%〜15%であることにより解決される。

【0012】

マクロエレクトロニック構造内に含まれる酸素含有イリジウム層は、シリコン含有層から酸素バリア層への、かつ場合によってはその上に配置された別の層へのシリコン拡散を阻止する。そのために酸素含有イリジウム層は、所定の割合の酸素を有し、この酸素はイリジウムケイ化物の形成、ひいてはシリコンのそれ以上の拡散を阻止する。さらに、酸素含有イリジウム層とシリコン含有層との間の境界面は、少なくとも800℃までの温度においてもかなりの程度までイリジウムケイ化物を含まない。このことは、例えば酸素含有イリジウム層における抵抗測定によって証明することができる。イリジウムケイ化物の不在は、例えば100μオーム・cmより小さな、有利にはそれどころか30μオーム・cmより小さな酸素含有イリジウム層のきわめて小さな抵抗率で表れる。ほぼ6オーム・cmのきわめて大きな抵抗率を有するイリジウムケイ化物の存在する際、シリコン含有層と酸素含有イリジウム層から形成される構造の抵抗率は、100μオーム・cmからはっきりと上にある。マイクロエレクトロニック構造の小さな電気抵抗は、とくにきわめて高集積度の半導体構成要素において、とくに0.25μm及びそれ以下の構造大きさを有する半導体メモリにおいて、大きな利点である。

【0013】

その上さらに酸素含有イリジウム層によって、シリコン含有層及びそれに結び付いたシリコン含有層の酸化による酸素バリア層の可能な減少を阻止するために、シリコン含有層と酸素バリア層との間の接触がかなりの程度まで防止される。

【0014】

前記の特性を有する酸素含有イリジウム層は、例えばわずかな酸素割合を有する酸素含有雰囲気におけるスパッタリング法(スパッタ)によって製造することができ、その際、雰囲気中の酸素の体積割合は2.5%〜15%である。雰囲気中における酸素の制限された体積割合によって、酸素は所定の程度までだけでもイリジウム層内に組込まれるので、無酸化イリジウム層と称することもできる。有利には雰囲気中の酸素の体積割合はほぼ5%にある。

【0015】

実験において、ほぼ2.5%の酸素の体積割合で製造された酸素含有イリジウム層はまだかなりの程度までけい化に抗するが、一方2.5%より少ないの酸素を含む雰囲気中において製造された酸素含有イリジウム層は、すでにはっきりとけい化の傾向を有することが判明した。他方において、最大15%の酸素容積濃度において堆積された酸素含有イリジウム層は、まだ酸素含有イリジウム層の下にあるシリコン含有層の有害な酸化を惹起しない。

【0016】

酸素含有イリジウム層の付着能力を改善するために、酸素含有イリジウム層を、少なくとも250°Cの温度において堆積するのが望ましい。それによりとくに酸素含有イリジウム層と例えばシリコン窒化物及びシリコン酸化物からなるシリコン含有アイソレーション層との間の付着能力が改善される。ベース基板自体はシリコン酸化物又はシリコン窒化物からなることができるので、高温での酸素含有イリジウム層の堆積によって、ベース基板への酸素含有イリジウム層の良好な付着も達成される。基本的に堆積温度はベース基板への十分な付着が保証されるように、高く選定されるようにし、その際、それにより少なくとも100kg/cm2の付着強さを達成できる。

【0017】

少なくとも250°Cの温度において酸素含有イリジウム層を堆積するもう1つの利点は、酸素含有イリジウム層の付着を改善するさらなるコンディショニングステップが必要ない点にある。堆積温度をそれほど高く選定しないかぎり、例えば250°C〜400°Cに選定するかぎり、すでに提供された構造はほとんど熱的な負荷を受けない。

【0018】

有利には酸素バリアは導電性の金属酸化物からなり、その際、とくに二酸化イリジウム及び二酸化ルテニウムが、金属酸化物として優れているとわかった。これらの金属酸化物の使用によって、酸素含有イリジウム層における酸素バリア層の良好な付着も保証されている。通常酸素含有イリジウム層の下にあるシリコン含有層は、有利にはポリシリコンから、金属ケイ化物又は積層体からなり、この積層体は、少なくとも1種のポリシリコン層、及びポリシリコン層と酸素含有イリジウム層との間にある金属ケイ化物層を含む。有利には金属ケイ化物は、イットリウムケイ化物、チタンケイ化物、ジルコニウムケイ化物、ハフニウムケイ化物、バナジウムケイ化物、ニオブケイ化物、タンタルケイ化物、クロムケイ化物、モリブデンケイ化物、タングステンケイ化物、鉄ケイ化物、コバルトケイ化物、ニッケルケイ化物、パラジウムケイ化物、白金ケイ化物及び銅ケイ化物の群から選択されるからなる少なくとも1種のケイ化物からなる。その際、金属及びシリコンは、種々の化学量論的な比において存在することができる。利用される金属ケイ化物は、その上さらに三元構造でもよく、かつ一般的な形MSiNを満たすことができ、その際Mは金属及びNは窒素を表す。

【0019】

シリコン含有層をベース基板内に埋め込み、かつ酸素含有イリジウム層によって完全に覆うのが望ましいとわかった。それによりシリコン含有層は、少なくとも側方においてベース基板によって酸素の作用から保護され、かつシリコン含有層内にあるシリコンは、酸素含有イリジウム層を通る拡散を阻止される。シリコン含有層は、この構造において例えばポリシリコンによって満たされたスルーホールの形で存在することができ、このスルーホールは任意に酸素含有イリジウム層に向かって金属ケイ化物層によって制限されている。

【0020】

しかし、シリコン含有層と酸素含有イリジウム層を一緒にしてベース基板内に埋め込み、かつ酸素バリア層によって完全に覆うことも有利である。この構造において、ベース基板における酸素含有イリジウム層の場合によっては生じる付着の問題は、酸素含有イリジウム層が、その側方境界面(縁)においてのみベース基板に接触することによって避けられる。それに対して、導電性シリコン含有層における、とくにポリシリコンにおける又は金属ケイ化物における酸素含有イリジウム層の付着は通常十分に良好である。

【0021】

酸素含有イリジウム層はほぼ10〜100nm、その上有利にはほぼ20nm〜50nmの厚さを有する。酸素含有イリジウム層をできるだけ場所を節約しかつ薄く構成することが望まれる。マイクロエレクトロニック構造に含まれるバリア層(酸素バリア層、酸素含有イリジウム層)は、有利には、金属含有電極層によって覆われている。とくに酸素バリア層は、できるだけ完全にこの層によって覆われるようにする。金属含有電極層は、有利には金属(例えば白金、ルテニウム、イリジウム、パラジウム、ロジウム、レニウム、オスミウム)から、又は導電性の金属酸化物(MOx、例えばルテニウム酸化物、オスミウム酸化物、ロジウム酸化物、イリジウム酸化物、レニウム酸化物又は導電性のペロブスカイト、例えばSrRuO3又は(La、Sr)CoO3)からなる。金属としてとくに白金が有利である。金属含有電極層上に、誘電体の金属酸化物含有層があり、この層は、とくに半導体メモリにおいて、高ε誘電体又は強誘電性のコンデンサ誘電体をなしている。誘電性の金属酸化物含有層のために、とくに一般的なABOx又はDOxの金属酸化物が利用され、その際、Aは、とくにストロンチウム(Sr)、ビスマス(Bi)、ニオブ(Nb)、鉛(Pb)、ジルコニウム(Zr)、ランタン(La)、リチウム(Li)、カリウム(K)、カルシウム(Ca)及びバリウム(Ba)の群から選択される少なくとも1種の金属を表し、Bは、とくにチタン(Ti)、ニオブ(Nb)、ルテニウム(Ru)、マグネシウム(Mg)、マンガン(Mn)、ジルコニウム(Zr)又はチタン(Ti)の群から選択されるからなる少なくとも1種の金属をい表し、Dはチタン(Ti)又はタンタル(Ta)を表し、かつOは酸素を表す。xは2〜12である。これらの金属酸化物は、組成に応じて誘電性又は強誘電性の特性を有し、その際、これらの特性は、場合によっては金属酸化物の結晶化のための高温ステップの後に初めて証明できる。場合によってはこれらの材料は、多結晶の形で存在し、その際、しばしばペロブスカイトに似た結晶構造、混晶又は超格子を観察することができる。基本的に誘電性の金属酸化物含有層の形成のために、一般的な形ABOxのあらゆるペロブスカイトに似た金属酸化物が適している。大きなε(ε>20)を有する誘電性材料又は強誘電性特性を有する材料は、例えばバリウム−ストロンチウム−チタネート(BST、Ba1−xSrxTiO3)、ニオブドーピングされたストロンチウム−ビスマス−タンタレート(SBTN、SrxBiy(TazNb1−z)O3)、ストロンチウム−チタネート(STO、SrTiO3)、ストロンチウム−ビスマス−タンタレート(SBT、SrxBiyTa2O9)、ビスマス−チタネート(BTO、Bi4Ti3O12)、鉛−ジルコネート−チタネート(PZT、Pb(ZrxTi1−x)O3)、ストロンチウム−ニオベート(SNO、Sr2Nb2O7)、カリウム−チタネート−ニオベート(KTN)及び鉛−ランタン−チタネート(PLTO、(Pb、La)TiO3)である。その上さらに高ε誘電体としてタンタル酸化物(Ta2O5)も適用される。以下において、誘電性とは誘電性、常誘電性又は強誘電性の層のこととするので、誘電性の金属酸化物含有層は誘電性、常誘電性又は強誘電性の特性を有することができる。

【0022】

有利にはマイクロエレクトロニック構造は、半導体メモリ装置において利用され、この半導体メモリ装置は、少なくとも1種の第1及び第2の電極、及びその間に金属酸化物含有層を有し、これらは、一緒になってメモリコンデンサを形成する。その際、この半導体メモリ装置の第1の電極は、少なくとも酸素含有イリジウム層及び酸素バリア層を含むので、第1の電極は、任意の貴金属層の他に、必要な拡散バリアも含んでいる。

【0023】

有利なマイクロエレクトロニック構造において、ベース基板はとくにシリコン酸化物、シリコン窒化物から又はこれらの材料の層組合せからなる。ベース基板は少なくとも1つのコンタクトホールによって貫通され、このコンタクトホールはポリシリコン又はその他の導電性材料によって満たされている。場合によっては満たされたコンタクトホールは、ベース基板の表面と同一面内において、コンタクトホール内に配置された金属ケイ化物層によって終っている。最後にベース基板の表面に、酸素含有イリジウム層があり、このイリジウム層は、コンタクトホールを完全に覆い、側方においてこれを越えて突出し、かつここにおいてベース基板に直接接触する。

【0024】

次に本発明を実施例によって説明し、かつ図面に概略的に示す。

【0025】

マイクロエレクトロニック構造の製造の際、二酸化シリコン(例えばテトラ−エチル−オルソ−シラン(TEOS)を使用した堆積によって製造される)又はシリコン窒化物からなり、かつポリシリコン8によって満たされたコンタクトホール10によって貫通されているベース基板5から出発する。満たされたコンタクトホール10は、ベース基板5の表面15と同一面内において終ってる。このことは、例えば適当な研磨ステップによって、例えば化学的機械的な研磨(CMP)によって達成する。引き続き、ベース基板15の表面15上に、ポリシリコン層8から天然の酸化物を除去する0.3%のふっ化水素酸(HF)によるポリシリコンのほぼ1分間の清掃の後に、30〜100nmの厚さを有するタングステンケイ化物層20を堆積させる。任意にタングステンケイ化物の代わりに、同じ厚さのチタン層を被着することもできるが、その際にはチタンを後の高温ステップにおいてかなりの程度まで完全にコンタクトホール10内のポリシリコン8によってけい化する。タングステン−ケイ化物層20は、ここではシリコン含有層をなしている。タングステンケイ化物層20の代わりに、ポリシリコン層を被着することも可能なので、次に被着すべき酸素含有イリジウム層とベース基板との間に付着層(ポリシリコン、ケイ化物)がある。

【0026】

タングステンケイ化物層20の上に、続いてイリジウムの反応スパッタリングによって酸素含有イリジウム層25を被着する。これは、0.005〜0.02mbarの間、有利には0.015mbarにおける圧力ならびに酸素−アルゴン−混合物中で行い、その際、酸素の体積割合は2.5%〜15%、有利には5%である(2.5%≦O2/(O2+Ar)≦15%)。ほぼ100秒のスパッタリングプロセスの後に、タングステンケイ化物層20を完全に覆うほぼ50〜150nmの厚さの酸素含有イリジウム層25が形成された。堆積した酸素含有イリジウム層25は、例えば後に行なわれるいわゆるフェロアニール(ferroaneal)の際に800℃にまでなることがあるきわめて高い温度の際にも、タングステンケイ化物との接触の際におけるイリジウムケイ化物形成に耐える。この耐性は、直接ポリシリコン上に堆積した酸素含有イリジウム層25においても観察される。

【0027】

有利には、酸素含有イリジウム層25及びタングステンケイ化物層20を一緒に異方性エッチングする。その際両方の層は、ここにあるポリシリコンを完全に覆うために、エッチングの後にコンタクトホール10をさらに側方にわずかに越えて突出するようにする。このようにして得られた構造は、図1bに示されている。

【0028】

その後の図1cによる方法ステップにおいて、二酸化イリジウムからなるほぼ100nmの厚さの酸素バリア層30を、酸素含有イリジウム層25及びベース基板5上に被着し、かつマスクを利用して異方性エッチングする。その際二酸化イリジウム層30がその側部範囲32においても酸素含有イリジウム層25及びタングステンケイ化物層20を完全に覆うように注意する。それにより酸素の作用からの酸素含有イリジウム層25及びタングステンケイ化物層20の完全な保護が保証され、かつ酸素含有イリジウム層25と次に被着すべき白金からなる貴金属層35との間の接触が阻止される。白金層35からの酸素含有イリジウム層25の切離しによって、とくに、白金層35の不所望な境界面特性を惹起する恐れがある白金イリジウム合金の形成を阻止する。

【0029】

任意にルテニウムからなるともできる図1dに示された貴金属層35上に、ベータ−ジケトネートを使用して、金属有機CVD法又はMOD法(例えばスピン・オン法)によってストロンチウム−ビスマス−タンタレート層(SBT)40を堆積させる。この堆積は、有利には300〜800℃の温度ならびにとくにMOCVD法の際には、ストロンチウム−及びビスマス−ベータ−ジケトネートを酸化するために、酸素含有雰囲気中で行う。引き続き、白金からなる別の貴金属層45を全面的に被着する。SBT層40は、この実施例において誘電性の金属酸化物含有層を形成している。

【0030】

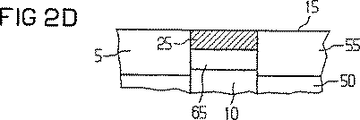

埋め込まれた酸素含有イリジウム層を有するマイクロエレクトロニック構造を製造する方法ステップは、図2a〜2fに示されている。ここでも任意に2つの層から構成することができるベース基板5から出発する。そのためにベース基板5は、下側の二酸化シリコン層50とその上にあるシリコン窒化物又はTEOS層55からなる。さらに、ベース基板5はコンタクトホール10を有するが、このコンタクトホールにはベース基板5の表面15までにはポリシリコンが満たされていない。この構造は、とくにコンタクトホールを満たした後に、ポリシリコンのバックエッチングステップによって達成される。この図2aに示された構造の上に、まずふっ化水素酸による清掃の後に、30〜100nmの厚さを有する白金、チタン、又はコバルト層を被着し、かつケイ化物を形成させる。その際、ポリシリコンによって満たされたコンタクトホール10の範囲にだけに金属ケイ化物が生じる。けい化されていない金属に対する形成された金属ケイ化物の異なるエッチング特性によって、チタン、白金又はコバルト層を、形成され自己調節される金属ケイ化物65まで除去する。しかし、チタン、白金又はコバルトケイ化物からなる形成された金属ケイ化物65は、ベース基板5の表面15にまで達していないので、コンタクトホール10はまだ完全に満たされていない。

【0031】

この充満は、今やベース基板5上に被着される、50〜150nmの材料厚さの酸素含有イリジウム層25によって初めてにおいて行なわれる。引き続き、酸素含有イリジウム層25をTEOS層55にまでバック研磨する。このようにして得られた、酸素含有イリジウム層25がベース基板5の表面と同一面において終っている構造は、図2dに示されている。

【0032】

酸素含有イリジウム層25を少なくとも部分的にベース基板5の表面15上に残すことも可能である。その際に場合によっては生じる酸素含有イリジウム層25とベース基板5との間の付着問題を回避するために、酸素含有イリジウム層25の堆積の際にベース基板5を少なくとも250°Cに加熱することが推奨される。例えばほぼ300°Cの温度が望ましい。その上さらに、温度を高めると金属ケイ化物上における酸素含有イリジウム層の付着も改善される。

【0033】

次に、二酸化イリジウムからなる酸素バリア層30を被着し、かつ構造化する。その際、コンタクトホール10は、この層によって完全に覆われている。その後、なお貴金属層35、誘電性の金属酸化物含有層40ならびに別の貴金属層45を被着しかつ適当に構造化する。

【0034】

これに引き続き、誘電性の金属酸化物含有層40の結晶化のために酸素含有雰囲気中における高温治療ステップ(例えばフェロアニール)を実施する。とくに誘電性の金属酸化物含有層40としてSBTを利用する際には、この処理は800°Cでほぼ1時間にわたって行なわなければならない。この処理の間にSBTは完全に結晶化されるべきであり、それによりSBT層40のできるだけ大きな残留分極が達成される。任意に、高温アニールステップを別の貴金属層45を堆積する前に行うこともできる。

【0035】

本発明によるマイクロエレクトロニック構造を含む半導体メモリ装置は、図3に示されている。この装置は、選択トランジスタ70及びメモリコンデンサ75を含む。選択トランジスタ70は、単結晶のシリコン基板90内に互いに切離されたドーピングされた2つの領域80及び85を有し、これらは選択トランジスタ70のソース及びドレイン領域(80、85)をなしている。両方のドーピングされた領域80及び85の間のシリコン基板90上に、ゲート電極95とその下に配置されたゲート誘電体100を有する。ゲート電極95及びゲート誘電体100は、側方アイソレーションウエブ105及び上側アイソレーション層110によって囲まれている。全構造はベース基板5によって完全に覆われている。ベース基板5を通ってドーピングされた領域85にまでコンタクトホール10が達しており、それによりベース基板5上にあるメモリコンデンサ75は選択トランジスタに接続されている。

【0036】

他方において、メモリコンデンサ75は下側電極115、コンデンサ誘電体40及び上側電極45からなる。下側電極115は本実施例において白金層35、二酸化イリジウム層30及び酸素含有イリジウム層25を含んでいる。したがって、下側電極1115は多層に構成されており、かつ酸化からコンタクトホール10内にあるポリシリコン8を保護するため及び意図しないシリコン拡散を防止するための必要なすべてのバリア層も含んでいる。

【0037】

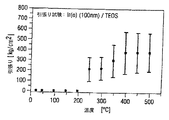

酸素含有イリジウム層25はきわめて小さな抵抗率によって特徴づけることができる。このことは例として種々のシリコン含有層上における酸化イリジウム(Ir(O)によって酸素含有イリジウム層が表わされる)の測定曲線を示す図4に示されている。そのために5%の酸素の雰囲気においてポリシリコン、チタンケイ化物又は白金ケイ化物上に酸化イリジウムを堆積させ、かつ続いて種々の温度においてほぼ1・1/2時間にわたって処理した。抵抗率は室温と800°Cと間の温度範囲において常に20μオーム・cmより小さく、しかも白金ケイ化物上における酸化イリジウムにおいてはっきりと10μオーム・cmより下にある。

【0038】

酸化イリジウム層の堆積の際の雰囲気の酸素含有量に関する抵抗率の依存性は、図5に示されている。酸素の2〜2・1/2%の体積割合での抵抗率の強力な降下をはっきりと認めることができる。さらに、650〜800°Cの比較的高い温度における後からの熱処理の際に抵抗率のそれ以上の減少を考慮すべきことを、認めることができる。

【0039】

図8及び9に、ポリシリコン上に堆積した酸素含有イリジウム層のX線構造解析の結果が示されている。図8は、酸素含有イリジウム層の堆積直後に得られた結果を示し、それに対して図9に、窒素の雰囲気中700°Cで熱処理した後に得られた結果が記入されている。図8と9の比較によって、少なくとも2.5%の酸素含有量で堆積させた酸素含有イリジウム層の場合には、高温処理の間にケイ化物形成が生じなかったことを、はっきりと認識すことができる。

【0040】

さらに、酸素含有イリジウム層は、その比較的わずかな酸素含有量によって特徴づけることもできる。酸素含有イリジウム層の化学量論的な比は、二酸化イリジウム層(IrO2)のものとは明らかに相違している。このことは、例えば酸素含有イリジウム層内に、酸素より多くのイリジウムを含んでいることに表われている。

【0041】

酸素含有イリジウム層に対するもう1つの特徴づけ可能性は、この層は導電性のシリコン含有層上では800°Cまでの温度においても、電気抵抗の上昇を生じる関連するイリジウムケイ化物層を形成しないということにある。従って、酸素含有イリジウム層は、とくに強誘電性のSBT又はPZTをコンデンサ誘電体として使用される半導体メモリにおけるバリア層としても適している。

【0042】

堆積温度に関する酸化イリジウム層(Ir(O))の付着強さは、図6及び7に示されている。図6は、TEOS堆積により得られたシリコン酸化物層に対するIr(O)の付着強さを示し、かつ図7は、化学量論的シリコン窒化物層(Si3N4)に対する付着強さを示している。両方の下地に対して、付着強さはほぼ250°Cにおけるジャンプの後に堆積温度の上昇とともに上昇することが当てはまる。従って、堆積温度を十分に高く選択するのが望ましい。

【0043】

付着強さは、とくにいわゆる“引張り試験”によって検出され、この引張り試験は文献において、しばしば“剥離試験”、“端面剥離試験”又は“セバスチャンファイブテスト”とも称される。引張り試験は、基板上における薄い層の付着強さに関する証言を行なうことを可能にする。この試験法では、通常円筒形の部材(“スタッド”)を、その一方の端面によってきわめて良好な付着特性を有する結合層を使用して、基板上にある層に固定する。その際、結合層は円筒形の部材を層に十分に固定結合すべきである。次に、測定装置によって、基板から円筒形の部材を剥離するためにどのくらいの力が必要かを確認する。円筒形の部材と試験すべき層との間、層と基板との間、又は基板もしくは層内における剥離が生じ得るので、その後でそれに応じた検査を行なわなければならない。付着強さの判定の際には、層(この場合、イリジウム層)上に円筒形の部材を固定する結合層は、基板に対する酸素含有イリジウム層の予測される付着強さより上にある十分に大きな付着強さを有するべきである。

【図面の簡単な説明】

【図1】 a〜eは、マイクロエレクトロニック構造を製造する個々の方法ステップの図である。

【図2】 a〜fは、マイクロエレクトロニック構造を製造する別の方法ステップの図である。

【図3】 半導体メモリの一部としてのマイクロエレクトロニック構造の図である。

【図4】 温度負荷に関する酸素含有イリジウム層の抵抗率の図である。

【図5】 堆積の際の雰囲気中の酸素割合に関する酸素含有イリジウム層の抵抗率の図である。

【図6】 堆積温度に関するシリコン酸化物層上における酸素含有イリジウム層の付着強さの図である。

【図7】 堆積温度に関するシリコン窒化物層上における酸素含有イリジウム層の付着強さの図である。

【図8】 堆積した酸素含有イリジウム層におけるX線構造試験の結果の図である。

【図9】 堆積した酸素含有イリジウム層におけるX線構造試験の結果の図である。

【符号の説明】

5 ベース基板、 8 ポリシリコン層、 10 コンタクトホール、 15 ベース基板の表面、 20 タングステンケイ化物層/金属ケイ化物層/シリコン含有層、 25 酸素含有イリジウム層、 30 酸素バリア層/二酸化イリジウム層、 32 側面範囲、 35 貴金属層/白金層/金属含有電極層、 40 誘電性の金属酸化物層、 45 別の貴金属層/白金層、 50 シリコン酸化物層、 55 TEOS層/シリコン窒化物層、 65 金属ケイ化物 70 選択トランジスタ、 75 メモリーコンデンサ、 80/85 ドーピングした領域、 90 シリコン基板、 95 ゲート電極、 100 ゲート誘電体、 105 側面アイソレーションウエブ、110 アイソレーション層、 115 下部電極

Claims (17)

- ベース基板(5);

シリコン含有層(8,20);

酸素含有イリジウム層(25);及び

酸素バリア層(30)

を有するマイクロエレクトロニック構造において、

シリコン含有層(8,20)と酸素バリア層(30)との間に酸素含有イリジウム層(25)があり、このイリジウム層は酸素の体積割合が2.5%〜15%である酸素含有雰囲気中におけるスパッタリング法によって少なくとも250°Cの温度で製造されたものであることを特徴とする、マイクロエレクトロニック構造。 - 雰囲気中の酸素の体積割合がほぼ5%である、請求項1記載のマイクロエレクトロニック構造。

- 酸素バリア(30)が導電性金属酸化物からなる、請求項1又は2記載のマイクロエレクトロニック構造。

- 導電性金属酸化物が二酸化イリジウム又は二酸化ルテニウムからなる、請求項3記載のマイクロエレクトロニック構造。

- シリコン含有層(8,20)がポリシリコンから又は少なくとも1種の金属ケイ化物からなる、請求項1から4までのいずれか1項に記載のマイクロエレクトロニック構造。

- シリコン含有層(8,20)がポリシリコン層(8)及び少なくとも1種の金属ケイ化物層(20)からなり、その際金属ケイ化物層(20)がポリシリコン層(8)と酸素含有イリジウム層(25)との間にある、請求項1から4までのいずれか1項に記載のマイクロエレクトロニック構造。

- 金属ケイ化物がイットリウムケイ化物、チタンケイ化物、ジルコニウムケイ化物、ハフニウムケイ化物、バナジウムケイ化物、ニオブケイ化物、タンタルケイ化物、クロムケイ化物、モリブデンケイ化物、タングステンケイ化物、鉄ケイ化物、コバルトケイ化物、ニッケルケイ化物、パラジウムケイ化物、白金ケイ化物及び銅ケイ化物の群から選択される少なくとも1種のケイ化物を含有する、請求項5又は6に記載のマイクロエレクトロニック構造。

- シリコン含有層(8,20)がベース基板(5)内に埋め込まれており、かつ、酸素含有イリジウム層(25)によって完全に覆われている、請求項1から7までのいずれか1項に記載のマイクロエレクトロニック構造。

- シリコン含有層(8,20)と酸素含有イリジウム層(25)が一緒にベース基板(5)内に埋め込まれており、かつ酸素バリア層(30)によって完全に覆われている、請求項1から7までのいずれか1項に記載のマイクロエレクトロニック構造。

- 酸素含有イリジウム層(25)がほぼ10〜100nm、有利にはほぼ20nm〜50nmの厚さを有する、請求項1から9までのいずれか1項に記載のマイクロエレクトロニック構造。

- 金属含有電極層(35)が酸素バリア層(30)を覆っている、請求項1から10までのいずれか1項に記載のマイクロエレクトロニック構造。

- 金属含有電極層(35)が金属酸化物含有層(40)によって覆われている、請求項11に記載のマイクロエレクトロニック構造。

- ベース基板(5)を有し;

シリコン含有層(8,20)を有し;

酸素バリア層(30)を有し;

シリコン含有層(8,20)と酸素バリア層(30)との間にある酸素含有イリジウム層(25)を有し、その際、酸素含有イリジウム層(25)が、酸素含有雰囲気中におけるスパッタリング法によって少なくとも250°Cの温度で製造されたものであり、かつ酸素含有雰囲気中の酸素の体積割合が2.5%〜15%であり;

酸素含有イリジウム層(25)を完全に覆ったIrO2層(30)を有し;かつ

IrO2層(30)上に配置された白金層(35)を有する、マイクロエレクトロニック構造。 - ベース基板(5);

シリコン含有層(8,20);

酸素含有イリジウム層(25);及び

酸素バリア層(30)

を有するマイクロエレクトロニック構造の製造方法において、

酸素含有イリジウム層(25)を酸素含有雰囲気中におけるスパッタリング法によって少なくとも250°Cの温度で堆積させ、その際酸素含有雰囲気中の酸素の体積割合が2.5%〜15%であり;

シリコン含有層(8,20)と酸素バリア層(30)との間に酸素含有イリジウム層(25)が存在することを特徴とする、マイクロエレクトロニック構造の製造方法。 - 雰囲気中における酸素の体積割合がほぼ5%である、請求項14記載の方法。

- 酸素含有イリジウム層(25)を0.005mbar〜0.02mbarの圧力で被着する、請求項14又は15記載の方法。

- 少なくとも第1の電極(115)及び第2の電極(45)、及びそれらの間に金属酸化物含有層(40)を有する半導体メモリ装置の場合に、これら第1の電極(115)及び第2の電極(45)、及びそれらの間の金属酸化物含有層(40)が一緒になってメモリコンデンサ(75)を形成しており、半導体メモリ装置の第1の電極(115)の一部が酸素含有イリジウム層(25)および酸素バリア層(30)からなり、シリコン含有層(8,20)と酸素バリア層(30)との間に酸素含有イリジウム層(25)が存在する半導体メモリ装置における請求項1から13のいずれか1項に記載のマイクロエレクトロニック構造の使用。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE19860080.1 | 1998-12-23 | ||

| DE1998160080 DE19860080B4 (de) | 1998-12-23 | 1998-12-23 | Mikroelektronische Struktur |

| DE19909295.8 | 1999-03-03 | ||

| DE1999109295 DE19909295A1 (de) | 1999-03-03 | 1999-03-03 | Mikroelektronische Struktur |

| PCT/DE1999/004081 WO2000039842A1 (de) | 1998-12-23 | 1999-12-22 | Kondensatorelektrodenanordnung |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002533953A JP2002533953A (ja) | 2002-10-08 |

| JP3665570B2 true JP3665570B2 (ja) | 2005-06-29 |

Family

ID=26051038

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000591655A Expired - Fee Related JP3665570B2 (ja) | 1998-12-23 | 1999-12-22 | コンデンサ電極装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6573542B2 (ja) |

| EP (1) | EP1153424A1 (ja) |

| JP (1) | JP3665570B2 (ja) |

| KR (1) | KR100430324B1 (ja) |

| WO (1) | WO2000039842A1 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6475911B1 (en) * | 2000-08-16 | 2002-11-05 | Micron Technology, Inc. | Method of forming noble metal pattern |

| KR100391987B1 (ko) * | 2000-09-18 | 2003-07-22 | 삼성전자주식회사 | 강유전체 캐퍼시터를 갖는 반도체 장치 및 그 제조방법 |

| US6794705B2 (en) | 2000-12-28 | 2004-09-21 | Infineon Technologies Ag | Multi-layer Pt electrode for DRAM and FRAM with high K dielectric materials |

| DE10114406A1 (de) * | 2001-03-23 | 2002-10-02 | Infineon Technologies Ag | Verfahren zur Herstellung ferroelektrischer Speicherzellen |

| JP2002359353A (ja) * | 2001-03-26 | 2002-12-13 | Seiko Epson Corp | 強誘電体メモリ及び電子機器 |

| KR100359299B1 (en) * | 2001-03-26 | 2002-11-07 | Samsung Electronics Co Ltd | Semiconductor memory device having resist pattern and method for forming metal contact thereof |

| KR100410981B1 (ko) * | 2001-05-18 | 2003-12-12 | 삼성전자주식회사 | 저저항을 갖는 반도체 소자의 금속배선구조 및 그의형성방법 |

| KR20030002863A (ko) * | 2001-06-30 | 2003-01-09 | 주식회사 하이닉스반도체 | 코어를 가진 플러그 구조 상의 강유전체 메모리소자 및 그제조방법 |

| JP2003045960A (ja) * | 2001-08-01 | 2003-02-14 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| KR100423906B1 (ko) * | 2001-08-08 | 2004-03-22 | 삼성전자주식회사 | 강유전성 메모리 장치 및 그 제조방법 |

| KR100422594B1 (ko) * | 2001-09-12 | 2004-03-16 | 주식회사 하이닉스반도체 | 반도체 소자의 커패시터 및 제조방법 |

| US6885570B2 (en) * | 2001-11-09 | 2005-04-26 | Interuniversitair Microelektronica Centrum vzw (IMEC vzw) | Simplified bottom electrode-barrier structure for making a ferroelectric capacitor stacked on a contact plug |

| DE10207130B4 (de) * | 2002-02-20 | 2007-09-27 | Infineon Technologies Ag | Verfahren zur Herstellung eines Bauelements sowie Bauelement mit einer Edelmetallschicht, einer Edelmetallsilizidschicht und einer oxidierten Silizidschicht |

| KR100471163B1 (ko) * | 2002-03-14 | 2005-03-09 | 삼성전자주식회사 | 커패시터들을 갖는 반도체소자의 제조방법 |

| US6583507B1 (en) * | 2002-04-26 | 2003-06-24 | Bum Ki Moon | Barrier for capacitor over plug structures |

| JP2003332539A (ja) * | 2002-05-17 | 2003-11-21 | Nec Electronics Corp | 強誘電体キャパシタ及びその製造方法並びに半導体記憶装置 |

| WO2005074032A1 (ja) * | 2004-01-28 | 2005-08-11 | Fujitsu Limited | 半導体装置及びその製造方法 |

| US20050161717A1 (en) * | 2004-01-28 | 2005-07-28 | Fujitsu Limited | Semiconductor device and method of fabricating the same |

| KR100615092B1 (ko) * | 2004-08-16 | 2006-08-23 | 삼성전자주식회사 | 노드 도전막 패턴들에 각각 자기 정렬시킨 하부 전극들을갖는 에프. 램들 및 그 형성방법들 |

| JP4998461B2 (ja) * | 2006-03-30 | 2012-08-15 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| KR100881055B1 (ko) * | 2007-06-20 | 2009-01-30 | 삼성전자주식회사 | 상변화 메모리 유닛, 이의 제조 방법, 이를 포함하는상변화 메모리 장치 및 그 제조 방법 |

| US8021940B2 (en) * | 2007-12-31 | 2011-09-20 | Intel Corporation | Methods for fabricating PMOS metal gate structures |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5566045A (en) | 1994-08-01 | 1996-10-15 | Texas Instruments, Inc. | High-dielectric-constant material electrodes comprising thin platinum layers |

| US5576579A (en) * | 1995-01-12 | 1996-11-19 | International Business Machines Corporation | Tasin oxygen diffusion barrier in multilayer structures |

| JPH09102591A (ja) * | 1995-07-28 | 1997-04-15 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP3396131B2 (ja) * | 1996-06-28 | 2003-04-14 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

-

1999

- 1999-12-22 JP JP2000591655A patent/JP3665570B2/ja not_active Expired - Fee Related

- 1999-12-22 WO PCT/DE1999/004081 patent/WO2000039842A1/de active IP Right Grant

- 1999-12-22 KR KR10-2001-7008073A patent/KR100430324B1/ko not_active IP Right Cessation

- 1999-12-22 EP EP99967896A patent/EP1153424A1/de not_active Withdrawn

-

2001

- 2001-06-25 US US09/891,114 patent/US6573542B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP1153424A1 (de) | 2001-11-14 |

| KR100430324B1 (ko) | 2004-05-03 |

| WO2000039842A1 (de) | 2000-07-06 |

| JP2002533953A (ja) | 2002-10-08 |

| KR20010109274A (ko) | 2001-12-08 |

| US6573542B2 (en) | 2003-06-03 |

| US20020070404A1 (en) | 2002-06-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3665570B2 (ja) | コンデンサ電極装置 | |

| US5626906A (en) | Electrodes comprising conductive perovskite-seed layers for perovskite dielectrics | |

| US6407422B1 (en) | Oxygen diffusion blocking semiconductor capacitor | |

| US5605858A (en) | Method of forming high-dielectric-constant material electrodes comprising conductive sidewall spacers of same material as electrodes | |

| JP3319994B2 (ja) | 半導体記憶素子 | |

| KR100244933B1 (ko) | 전극의 제조방법 | |

| JP3636900B2 (ja) | 強誘電体集積回路の製造方法 | |

| US6740533B2 (en) | Semiconductor device having a ferroelectric capacitor and fabrication process thereof | |

| US5789268A (en) | Method of forming a electrode structure for ferroelectric capacitors for integrated circuits | |

| JP3452763B2 (ja) | 半導体記憶装置および半導体記憶装置の製造方法 | |

| JPH09102591A (ja) | 半導体装置及びその製造方法 | |

| JPH06326250A (ja) | 高誘電率材料へのコンタクト構造および形成方法 | |

| US20010013614A1 (en) | Iridium oxide diffusion barrier between local interconnect layer and thin film of layered superlattice material | |

| JP2008066644A (ja) | 半導体装置及びその製造方法 | |

| JP5076890B2 (ja) | 半導体装置及びその製造方法 | |

| US6284587B1 (en) | Fabricating method for semiconductor device | |

| JP4438963B2 (ja) | 強誘電体キャパシタ | |

| JPH09246490A (ja) | 半導体装置及びその製造方法 | |

| US20010024868A1 (en) | Microelectronic structure and method of fabricating it | |

| JP4421814B2 (ja) | 容量素子の製造方法 | |

| JP2000223666A (ja) | 半導体メモリ素子の製造方法 | |

| JP2002203948A (ja) | 半導体装置 | |

| JP2002231903A (ja) | 誘電体素子およびその製造方法 | |

| KR100652354B1 (ko) | 하부전극과 콘택 플러그 사이에 낮은 접촉 저항을 갖는 반도체장치의 커패시터 및 그 제조방법 | |

| KR100616211B1 (ko) | 반도체 소자의 캐패시터 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041105 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050302 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050401 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090408 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100408 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110408 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120408 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120408 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130408 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140408 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |