JP3645463B2 - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP3645463B2 JP3645463B2 JP2000013476A JP2000013476A JP3645463B2 JP 3645463 B2 JP3645463 B2 JP 3645463B2 JP 2000013476 A JP2000013476 A JP 2000013476A JP 2000013476 A JP2000013476 A JP 2000013476A JP 3645463 B2 JP3645463 B2 JP 3645463B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- silicon oxide

- gate electrode

- contact hole

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/485—Bit line contacts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/488—Word lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/692—Electrodes

- H10D1/711—Electrodes having non-planar surfaces, e.g. formed by texturisation

- H10D1/716—Electrodes having non-planar surfaces, e.g. formed by texturisation having vertical extensions

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/906—Dram with capacitor electrodes used for accessing, e.g. bit line is capacitor plate

Landscapes

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

【発明の属する技術分野】

本発明は、半導体集積回路装置およびその製造技術に関し、特に、DRAM(Dynamic Random Access Memory)を有する半導体集積回路装置の製造に適用して有効な技術に関する。

【0002】

【従来の技術】

近年のDRAMは、メモリセルの微細化に伴う情報蓄積用容量素子の蓄積電荷量の減少を補うために、情報蓄積用容量素子をメモリセル選択用MISFETの上方に配置する、いわゆるスタックド・キャパシタ構造を採用している。このスタックド・キャパシタ構造を採用するDRAMには、大別してビット線の下方に情報蓄積用容量素子を配置するキャパシタ・アンダー・ビットライン(Capacitor Under Bitline;CUB)構造(例えば特開平7−192723号公報、特開平8−204144号公報など)と、ビット線の上方に情報蓄積用容量素子を配置するキャパシタ・オーバー・ビットライン(Capacitor Over Bitline;COB)構造(例えば特開平7−122654号公報、特開平7−106437号公報など)とがある。

【0003】

上記した2種のスタックド・キャパシタ構造のうち、ビット線の上方に情報蓄積用容量素子を配置するCOB構造は、CUB構造に比べてメモリセルの微細化に適している。これは、微細化された情報蓄積用容量素子の蓄積電荷量を増やそうとすると、その構造を立体化して表面積を増やす必要があるため、情報蓄積用容量素子の上部にビット線を配置するCUB構造では、ビット線とメモリセル選択用MISFETとを接続するコンタクトホールのアスペクト比が極端に大きくなってしまい、その開孔が困難になるからである。

【0004】

また、64メガビット(Mbit)あるいは256メガビットといった最近の大容量DRAMは、微細化されたメモリセル選択用MISFETのゲート電極のスペースにビット線や情報蓄積用容量素子と基板とを接続するためのコンタクトホールを形成する際に、ゲート電極の上部と側壁とを窒化シリコン膜で覆い、酸化シリコン膜と窒化シリコン膜とのエッチングレート差を利用してコンタクトホールをゲート電極のスペースに対して自己整合的に開孔するセルフアライン・コンタクト(Self Align Contact;SAC)技術(例えば特開平9−252098号公報)を採用したり、ゲート電極の低抵抗化を推進するために、ゲート電極をW(タングステン)などの高融点金属材料を主体として構成するポリメタルゲート構造(特開平7−94716号公報)を採用したりしている。

【0005】

【発明が解決しようとする課題】

本発明者は、256メガビット(Mbit)DRAMおよび1ギガビット(Gbit)DRAMの開発を進めるなかで、リフレッシュ時間間隔を長くするための一対策として、ビット線容量の低減を図ることを検討している。

【0006】

ビット線容量の成分は、対隣接ビット線、対基板、対蓄積電極、対ワード線および対プレート電極に分けられるが、ビット線の上方に情報蓄積用容量素子を配置するCOB構造の場合には、対ワード線容量成分が主要な成分となる。従って、ビット線容量を低減するためには、まず対ワード線容量を低減することが最優先課題となる。

【0007】

前述したように、セルフアライン・コンタクト(SAC)技術を採用する従来の製造プロセスでは、ゲート電極の上部と側壁とを酸化シリコン膜に対するエッチング選択比が大きい窒化シリコン膜で覆っている。しかし、窒化シリコン膜の比誘電率は、酸化シリコン膜のそれよりも約2倍程度大きいため、ゲート電極の上部と側壁とを窒化シリコン膜で覆うと、ビット線の対ワード線容量が大きくなってしまう。

【0008】

本発明の目的は、メモリセルサイズが微細化されたDRAMにおいて、ビット線容量を低減することのできる技術を提供することにある。

【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【0010】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

(1)本発明の半導体集積回路装置は、半導体基板上に形成されたMISFETと、前記MISFETのソース、ドレイン領域上に形成されたコンタクトホールと、前記コンタクトホールの内部に形成され、前記ソース、ドレイン領域と電気的に接続された導電体と、前記導電体の周囲に形成された第1の絶縁膜とを有し、前記第1の絶縁膜は、前記コンタクトホールの底部では、前記導電体の周囲を囲むように形成されており、前記コンタクトホールの上部では、少なくとも一部が除去されており、前記導電体の周囲を取り囲むようには形成されていない。

(2)本発明の半導体集積回路装置は、半導体基板上に形成されたMISFETと、前記MISFETのソース、ドレイン領域上に形成されたコンタクトホールと、前記コンタクトホールの内部に形成され、前記ソース、ドレイン領域と電気的に接続された導電体と、前記導電体の周囲を囲むように形成された第1の側壁絶縁膜と、前記第1の側壁絶縁膜の周囲を囲むように形成された第2の側壁絶縁膜とを有し、前記第1の側壁絶縁膜は、前記第2の側壁絶縁膜に比べて部分的にまたは全体の高さが低くなっている。

(3)本発明の半導体集積回路装置は、半導体基板上に形成された第1および第2のワード線と、前記第1および第2のワード線上にそれぞれ形成された第1および第2の絶縁膜と、前記第1および第2のワード線の間に形成されたコンタクトホールと、前記コンタクトホールの内部に形成された導電体とを有し、前記第1および第2のワード線の間には、前記コンタクトホールの側壁を構成する第3および第4の絶縁膜が形成されており、前記導電体の周囲には第5の絶縁膜が形成されており、前記第5の絶縁膜の高さは、部分的にまたは全体が前記第3および第4の絶縁膜の上端部よりも低い。

(4)本発明の半導体集積回路装置の製造方法は、以下の工程を有している。

(a)半導体基板上に第1の導電体膜を形成した後、前記第1の導電体膜の上部に第1の絶縁膜を形成する工程、

(b)前記第1の導電体膜および第1の絶縁膜をエッチングすることにより、第1および第2のワード線と、前記第1および第2のワード線の上部を覆う第1および第2のキャップ絶縁膜とを形成する工程、

(c)前記第1のワード線の一部をゲート電極とする第1のMISFETおよび前記第2のワード線の一部をゲート電極とする第2のMISFETを形成する工程、

(d)前記第1および第2のワード線の間を含む前記半導体基板上に第2の絶縁膜を形成した後、前記第2の絶縁膜上にスリット状の開孔部を有するマスクパターンを形成する工程、

(e)前記スリット状の開孔部を有するマスクパターンと、前記第1および第2のキャップ絶縁膜とをマスクに用いて前記第2の絶縁膜をエッチングすることにより、前記第1および第2のMISFETのソース、ドレイン領域の一方の上部に第1の開孔部を形成し、前記ソース、ドレイン領域の他方の上部に第2の開孔部を形成する工程、

(f)前記第1および第2の開孔の内部に第2導体膜を形成する工程、

(g)前記第1の開孔を通して前記ソース、ドレイン領域の一方と電気的に接続されるビット線を形成し、前記第2の開孔を通して前記ソース、ドレイン領域の他方と電気的に接続される容量素子を形成する工程。

(5)本発明の半導体集積回路装置の製造方法は、以下の工程を有している。

(a)半導体基板上に第1の導電体膜を形成した後、前記第1の導電体膜の上部に第1の絶縁膜を形成する工程、

(b)前記第1の導電体膜および第1の絶縁膜をエッチングすることにより、第1および第2の配線と、前記第1および第2の配線の上部を覆う第1および第2のキャップ絶縁膜とを形成する工程、

(c)前記第1および第2の配線の間を含む前記半導体基板上に第2の絶縁膜を形成した後、前記第2の絶縁膜上に開孔部を有する第1の膜を形成する工程、

(d)前記第1の膜をマスクとし、前記第1および第2のキャップ絶縁膜をエッチングストッパとして前記第2の絶縁膜をエッチングすることにより、前記第2の絶縁膜に開孔部を形成する工程、

(e)前記開孔部の内部に側壁絶縁膜を形成する工程、

(f)前記側壁絶縁膜の一部を除去する工程、

(g)前記側壁絶縁膜が形成された前記開孔部の内部にプラグを形成する工程。

(6)本発明の半導体集積回路装置の製造方法は、以下の工程を有している。

(a)半導体基板上に第1の導電体膜を形成した後、前記第1の導電体膜の上部に第1の絶縁膜を形成する工程、

(b)前記第1の絶縁膜上に第2の絶縁膜を形成した後、前記第2の絶縁膜上にフォトレジスト膜を形成する工程、

(c)前記フォトレジスト膜をマスクとして、前記第1および第2の絶縁膜をエッチングする工程、

(d)前記第1の絶縁膜をマスクとして前記第1の導電体膜をエッチングすることにより、第1および第2の配線を形成する工程、

(e)前記第1および第2の配線の間を含む前記半導体基板の主面上に第3の絶縁膜を形成した後、前記第3の絶縁膜上に第1の膜を形成する工程、

(f)前記第1の膜および前記第1の絶縁膜に対するエッチング速度が前記第2の絶縁膜に対するエッチング速度よりも遅い方法で、前記第2の絶縁膜をエッチングすることにより、前記第1および第2の配線の間に開孔部を形成する工程。

【0011】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

【0012】

(実施の形態1)

図1は、本実施形態のDRAM(Dynamic Random Access Memory)を形成した半導体チップ1Aの全体平面図である。

【0013】

長方形の半導体チップ1Aの主面には、例えば256Mbit(メガビット)の記憶容量を有するDRAMが形成されている。このDRAMは、複数のメモリアレイ(MARY)からなる記憶部とそれらの周囲に配置された周辺回路部PCとを有している。また、半導体チップ1Aの中央部には、ワイヤやバンプ電極などが接続される複数のボンディングパッドBPが1列に配置されている。

【0014】

図2は、上記記憶部の一端部を示す半導体基板(以下、基板という)の断面図である。

【0015】

例えばp型の単結晶シリコンからなる基板1の主面にはp型ウエル2が形成されており、p型ウエル2には素子分離溝4が形成されている。この素子分離溝4によって周囲を規定されたp型ウエル2のアクティブ領域には複数のメモリセルが形成されている。メモリセルのそれぞれは、nチャネル型MISFET(Metal Insulator Semiconductor Field Effect Transistor)によって構成された一個のメモリセル選択用MISFETQtとその上部に形成された一個の情報蓄積用容量素子Cとによって構成されている。メモリセル選択用MISFETQtは、主としてゲート絶縁膜6、アクティブ領域以外の領域においてワード線WLを構成するゲート電極7および一対のn型半導体領域(ソース、ドレイン領域)8によって構成されている。ゲート電極7(ワード線WL)は、例えばP(リン)がドープされたn型多結晶シリコン膜、WN(窒化タングステン)膜およびW(タングステン)膜を積層した3層の導電体膜によって構成されている。

【0016】

図には示さない周辺回路部(PC)の基板1にはp型ウエルおよびn型ウエルが形成されている。p型ウエルのアクティブ領域にはnチャネル型MISFETが形成され、n型ウエルのアクティブ領域にはpチャネル型MISFETが形成されている。nチャネル型MISFETは、主としてゲート絶縁膜、ゲート電極および一対のn型半導体領域(ソース、ドレイン領域)によって構成され、pチャネル型MISFETは、主としてゲート絶縁膜、ゲート電極および一対のp型半導体領域(ソース、ドレイン領域)によって構成されている。すなわち、周辺回路部(PC)は、nチャネル型MISFETとpチャネル型MISFETとを組み合わせた相補型MISFETによって構成されている。

【0017】

図2に示すように、メモリセル選択用MISFETQtのゲート電極7(ワード線WL)の側壁には、2層の側壁絶縁膜10、11が形成されている。これらの側壁絶縁膜10、11のうち、外側の第1の側壁絶縁膜11は、例えば30nm程度の膜厚を有する酸化シリコン膜によって構成され、内側の第2の側壁絶縁膜10は、第1の側壁絶縁膜11よりも薄い膜厚(例えば10nm〜15nm程度)の窒化シリコン膜によって構成されている。酸化シリコン膜によって構成された側壁絶縁膜11の高さは、ゲート電極7(ワード線WL)の上面よりも高く、かつゲート電極7(ワード線WL)の上部を覆っているキャップ絶縁膜9の上端部よりも低くなっている。

【0018】

ゲート電極7のスペースには、上記2層の側壁絶縁膜10、11によって周囲を囲まれたコンタクトホール(開孔部)12、13が形成されており、コンタクトホール12、13の内部には、例えばP(リン)がドープされたn型多結晶シリコン膜によって構成されるプラグ14が埋め込まれている。

【0019】

メモリセル選択用MISFETQtの上部には酸化シリコン膜31が形成されており、酸化シリコン膜31の上部にはメモリセルのデータを読み出すビット線BLが形成されている。ビット線BLは、例えばTiN(窒化チタン)膜の上部にW(タングステン)膜を積層した導電体膜によって構成されている。ビット線BLは、酸化シリコン膜31に形成されたスルーホール32およびその下部の前記コンタクトホール12を通じてメモリセル選択用MISFETQtのn型半導体領域(ソース、ドレイン)8の一方と電気的に接続されている。スルーホール32の内部には、例えばTiN膜の上部にW膜を積層した導電体膜によって構成されるプラグ33が埋め込まれている。

【0020】

ビット線BLの上部には酸化シリコン膜34および窒化シリコン膜35が形成されており、窒化シリコン膜35の上部には情報蓄積用容量素子Cが形成されている。情報蓄積用容量素子Cは、窒化シリコン膜35の上部の厚い膜厚の酸化シリコン膜39をエッチングして形成した深い溝40の内部に形成され、下部電極41、容量絶縁膜42および上部電極43によって構成されている。

【0021】

情報蓄積用容量素子Cの下部電極41は、例えばRu(ルテニウム)膜によって構成され、スルーホール36およびその下部のコンタクトホール13を通じてメモリセル選択用MISFETQtのn型半導体領域(ソース、ドレイン)8の他方と電気的に接続されている。容量絶縁膜42は、例えばBST(BaXSr1-XTiO3;Barium Strontium Titanate)膜によって構成され、上部電極43は例えばRu膜によって構成されている。

【0022】

次に、上記のように構成された本実施形態のDRAMの製造方法を図3〜図41を用いて工程順に説明する。

【0023】

まず、図3(記憶部の一端部を示す平面図)、図4(図3のA−A線に沿った断面図)および図5(図3のB−B線に沿った断面図)に示すように、基板1の主面の素子分離領域に素子分離溝4を形成する。素子分離溝4は、基板1の主面をエッチングして深さ300〜400nm程度の溝を形成し、続いてこの溝の内部を含む基板1上にCVD法で膜厚600nm程度酸化シリコン膜5を堆積した後、溝の外部の酸化シリコン膜5を化学機械研磨(Chemical Mechanical Polishing;CMP)法で研磨、除去することにより形成する。図3に示すように、この素子分離溝4を形成することにより、周囲が素子分離溝4で囲まれた細長い島状のパターンを有する多数のアクティブ領域Lが同時に形成される。

【0024】

次に、図6および図7に示すように、基板1にP(リン)をイオン打ち込みした後、基板1を熱処理してこの不純物を基板1内に拡散させることにより、p型ウエル2を形成する。

【0025】

次に、図8に示すように、基板1を熱酸化してp型ウエル2の表面に膜厚6nm〜7nm程度の酸化シリコンからなるゲート絶縁膜6を形成し、続いてゲート絶縁膜6の上部にゲート電極材料である第1の導電体膜7Aを形成した後、導電体膜7Aの上部にキャップ絶縁膜材料である第1の絶縁膜9Aを形成する。

【0026】

上記導電体膜7Aを形成するには、例えばP(リン)をドープした膜厚70nm程度のn型多結晶シリコン膜をゲート絶縁膜6上にCVD法で堆積し、続いてその上部に膜厚5nm程度のWN(窒化タングステン)膜および膜厚60nm程度のW(タングステン)膜をスパッタリング法で堆積する。また、絶縁膜9Aを形成するには、従来のセルフアライン・コンタクト(SAC)技術で行われているように、導電体膜9A上にCVD法で窒化シリコン膜を堆積してもよいが、本実施形態では、例えば膜厚50nm程度の酸化シリコン膜、膜厚70nm程度の窒化シリコン膜および膜厚80nm程度の酸化シリコン膜をCVD法で堆積する。すなわち、絶縁膜9Aは、2層の酸化シリコン膜の間に窒化シリコン膜を設けた3層の絶縁膜によって構成される。

【0027】

次に、図9に示すように、フォトレジスト膜20をマスクにして絶縁膜9Aをドライエッチングすることにより、ゲート電極を形成する領域の導電体膜7A上に前述した3層の絶縁膜(絶縁膜9A)によって構成されるキャップ絶縁膜9を形成する。

【0028】

通常、酸化シリコンは、フォトレジストに対するエッチング選択比(対レジスト選択比)が窒化シリコンよりも大きい(窒化シリコンが約1.3であるのに対し、酸化シリコンは約1.6)。そのため、キャップ絶縁膜材料(絶縁膜9A)を2層の酸化シリコン膜と1層の窒化シリコン膜とで構成した場合は、キャップ絶縁膜材料を1層の窒化シリコン膜だけで構成した場合に比べて対レジスト選択比が大きくなり、その分、フォトレジスト膜20の膜減りが少なくなるために、キャップ絶縁膜9の加工寸法精度が向上する。

【0029】

次に、フォトレジスト膜20を除去した後、図10に示すように、キャップ絶縁膜9をマスクにして導電体膜7Aをドライエッチングすることにより、多結晶シリコン膜、WN膜およびW膜によって構成されるゲート電極7(ワード線WL)を形成する。W膜と多結晶シリコン膜とを主体として構成される、いわゆるポリメタル構造のゲート電極7(ワード線WL)は、多結晶シリコン膜やポリサイド膜(高融点金属シリサイド膜と多結晶シリコン膜との積層膜)で構成されたゲート電極に比べて電気抵抗が低いので、ワード線の信号遅延を低減することができる。なお、W膜と多結晶シリコン膜との間に設けられたWN膜は、高温熱処理時にW膜と多結晶シリコン膜とが反応して両者の界面に高抵抗のシリサイド層が形成されるのを防止するバリア層として機能する。バリア層には、WN膜の他、例えばTiN(窒化チタン)膜などを使用することもできる。

【0030】

図11に示すように、ゲート電極7(ワード線WL)は、アクティブ領域Lの長辺と交差する方向に延在し、そのゲート長は、例えば0.13μm〜1.4μm程度、隣接するゲート電極7(ワード線WL)とのスペースは、例えば0.12μm程度である。

【0031】

通常、ゲート電極材料(導電体膜7A)の一部を構成するW膜は、酸化シリコンに対するエッチング選択比(対酸化シリコン選択比9が窒化シリコン膜に対する選択比(対窒化シリコン選択比)よりも大きい(対窒化シリコン選択比が約1.0であるのに対し、対酸化シリコン選択比は約1.2である)。そのため、キャップ絶縁膜9の最上部を酸化シリコン膜で構成した場合は、最上部を窒化シリコン膜で構成した場合に比べてW膜の選択比を大きく取ることができる。これにより、キャップ絶縁膜9の膜減りが少ない状態でゲート電極7を加工することができ、その分、キャップ絶縁膜9の加工寸法精度およびゲート電極7の加工寸法精度を向上させることができるので、キャップ絶縁膜9を1層の窒化シリコン膜だけで構成した場合に比べて、微細なゲート長を有するゲート電極7を高い寸法精度で形成することができる。なお、窒化シリコン膜を挟む2層の酸化シリコン膜のうちのいずれか一方を省略することもできる。

【0032】

次に、図12に示すように、p型ウエル2にAs(ヒ素)をイオン打ち込みしてゲート電極7の両側のp型ウエル2にn型半導体領域(ソース、ドレイン領域)8を形成する。ここまでの工程により、メモリセル選択用MISFETQtが略完成する。続いて、基板1上にCVD法で膜厚10nm〜15nm程度の薄い窒化シリコン膜10Aを堆積する。窒化シリコン膜10Aは、後の工程でゲート電極7のスペースにコンタクトホール(開孔部)を形成するためのドライエッチングを行う際、素子分離溝4の内部の酸化シリコン膜5が削られるのを防ぐエッチングストッパとして使用される。従って、酸化シリコン膜5の削れ量が問題とならないような場合は、窒化シリコン膜10Aを形成しなくともよい。

【0033】

次に、図13に示すように、基板1上にCVD法で膜厚70nm程度の酸化シリコン膜21を堆積することにより、ゲート電極7(ワード線WL)のスペースに酸化シリコン膜21を埋め込む。酸化シリコン膜21は、周辺回路部のMISFET(nチャネル型MISFETおよびpチャネル型MISFET)をLDD(lightly Doped Drain)構造にするために使用される。すなわち、図示は省略するが、上記酸化シリコン膜21を堆積した後、記憶部の基板1上をフォトレジスト膜で覆い、周辺回路部の酸化シリコン膜21を異方的にエッチングすることにより、周辺回路部のゲート電極の側壁に側壁絶縁膜を形成する。その後、周辺回路部のp型ウエルにAsまたはPをイオン打込みして高不純物濃度のn+型半導体領域(ソース、ドレイン)を形成し、n型ウエルにBをイオン打込みして高不純物濃度のp+型半導体領域(ソース、ドレイン)を形成する。ここまでの工程により、周辺回路部のnチャネル型MISFETおよびpチャネル型MISFETが略完成する。

【0034】

次に、図14に示すように、基板1上にCVD法で膜厚600nm程度の厚い酸化シリコン膜22を堆積した後、この酸化シリコン膜22を化学機械研磨法で研磨、平坦化することにより、酸化シリコン膜22の表面の高さを記憶部と図示しない周辺回路部とで均一にする。このとき、キャップ絶縁膜9の一部を構成する窒化シリコン膜を研磨のストッパに用い、酸化シリコン膜22の表面の高さをキャップ絶縁膜9の上面まで後退させてもよい。

【0035】

次に、図15および図16に示すように、酸化シリコン膜22の上部にCVD法で膜厚10nm程度の薄い酸化シリコン膜23を堆積し、続いて酸化シリコン膜23の上部にCVD法で膜厚70nm程度の多結晶シリコン膜24Aを堆積した後、多結晶シリコン膜24Aの上部に膜厚60nm程度の反射防止膜25および膜厚400nm程度のフォトレジスト膜26をスピン塗布する。酸化シリコン膜23は、化学機械研磨法で研磨されたときに生じた下層の酸化シリコン膜22の表面の微細な傷を補修するために堆積する。

【0036】

次に、図17および図18に示すように、フォトレジスト膜26をマスクにして反射防止膜25および多結晶シリコン膜24Aのそれぞれの一部をドライエッチングすることにより、耐エッチングマスク24を形成する。図19は、多結晶シリコン膜24Aによって構成された上記耐エッチングマスク24のパターン(グレイの着色を施した部分)を示す平面図である。図示のように、耐エッチングマスク24は、記憶部を横切ってアクティブ領域Lの長辺方向に延在する細長いスリット状または溝状の開孔部27を有している。ゲート電極7のスペースにコンタクトホール(開孔部)12、13を形成するための耐エッチングマスク24にこのようなスリット状(溝状)の開孔部27を設けた理由については後述する。

【0037】

次に、フォトレジスト膜26および反射防止膜25を除去した後、図20および図21に示すように、耐エッチングマスク24をマスクにして開孔部27内の酸化シリコン膜21、22、23をドライエッチングすることにより、n型半導体領域(ソース、ドレイン領域)8の上部、すなわちゲート電極7のスペースにコンタクトホール(開孔部)12、13を形成する。コンタクトホール12、13の一方(コンタクトホール12)は、n型半導体領域(ソース、ドレイン領域)8の一方とビット線BLとを接続するために使用され、他方(コンタクトホール13)は、n型半導体領域(ソース、ドレイン領域)8の他方と情報蓄積用容量素子Cの下部電極41とを接続するために使用される。

【0038】

上記酸化シリコン膜21、22、23のドライエッチングは、窒化シリコン膜10Aおよびキャップ絶縁膜9の一部を構成する窒化シリコン膜をエッチングストッパにして行う。これにより、酸化シリコン膜21、22、23をドライエッチングする際に素子分離溝4の内部の酸化シリコン膜5が削られる不具合を防止することができると共に、キャップ絶縁膜9が削られてゲート電極7(ワード線WL)の上面が露出する不具合を防止することができる。また、ここまでの工程により、ゲート電極7(ワード線WL)の側壁に窒化シリコン膜10Aによって構成される側壁絶縁膜10が形成される。

【0039】

次に、図22および図23に示すように、基板1上にCVD法で膜厚30nm程度の酸化シリコン膜11Aを堆積した後、図24に示すように、酸化シリコン膜11Aを異方的にエッチングすることにより、ゲート電極7(ワード線WL)の側壁に膜厚30nm程度の酸化シリコン膜11Aによって構成される側壁絶縁膜11を形成する。このとき、図25に示すように、スリット状(溝状)の開孔部27の延在方向に沿った酸化シリコン膜22、21の側壁にも、酸化シリコン膜11Aによって構成される側壁絶縁膜11が形成される。

【0040】

上記酸化シリコン膜11Aの異方性エッチングは、前述した酸化シリコン膜21、22、23のドライエッチングと同様、窒化シリコン膜10Aおよびキャップ絶縁膜9の一部である窒化シリコン膜をエッチングストッパにして行う。これにより、ゲート電極7の側壁に形成される側壁絶縁膜11の高さがキャップ絶縁膜9の上面よりも低くなる(図24)。このとき側壁絶縁膜11に対して施される異方性エッチングのエッチング量は、後にキャップ絶縁膜9の窒化シリコン膜をストッパにして行われる化学機械研磨によるキャップ絶縁膜9の膜減りを考慮しても、側壁絶縁膜11の上端がキャップ絶縁膜9の上面よりも確実に低くなるように、側壁絶縁膜11の上端とキャップ絶縁膜9の上面との高さの差を確保しておくことが望ましい。一方、酸化シリコン膜22、21の側壁に形成される側壁絶縁膜11は、ゲート電極7の側壁に形成される側壁絶縁膜11よりも上端部の位置が高くなる(図25)。

【0041】

ここまでの工程により、ゲート電極7の側壁には、薄い膜厚の窒化シリコン膜(10A)とそれよりも厚い膜厚の酸化シリコン膜(11A)とによって構成される2層の側壁絶縁膜10、11が形成される。また、酸化シリコン膜(11A)によって構成される側壁絶縁膜11は、ゲート電極7の側壁における高さがキャップ絶縁膜9の上面よりも低いため、ゲート電極7のスペースに形成されたコンタクトホール12、13のゲート長方向に沿った断面は、図24に示すように、上部の径(a)が底部の径(b)よりも大きくなる(a>b)。

【0042】

次に、図26および図27に示すように、コンタクトホール12、13の底部に残った薄い膜厚の窒化シリコン膜10Aをドライエッチングで除去してn型半導体領域(ソース、ドレイン領域)8の表面を露出させた後、このドライエッチングでダメージを受けたn型半導体領域(ソース、ドレイン領域)8の表面を薄くドライエッチングする。

【0043】

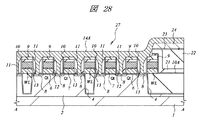

次に、図28および図29に示すように、例えばPをドープした膜厚100nm程度のn型多結晶シリコン膜14AをCVD法で堆積することにより、コンタクトホール12、13の内部にn型多結晶シリコン膜14Aを埋め込む。なお、図示しない周辺回路領域にコンタクトホール12、13よりも径の大きいコンタクトホールがある場合は、コンタクトホール内部のn型多結晶シリコン膜14Aの膜厚が不足し、次の工程でn型多結晶シリコン膜14Aを研磨したときに周辺回路領域のコンタクトホールの底部の基板1が削れる虞れがあるので、n型多結晶シリコン膜14Aの上部に例えばCVD法で膜厚200nm程度の酸化シリコン膜をさらに堆積しておいてもよい。

【0044】

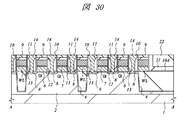

次に、図30および図31に示すように、n型多結晶シリコン膜14A、多結晶シリコンからなる耐エッチングマスク24およびその下層の酸化シリコン膜21、22、23を化学機械研磨法で研磨することにより、コンタクトホール12、13の外部のn型多結晶シリコン膜14Aを除去し、コンタクトホール12、13の内部にn型多結晶シリコン膜14Aによって構成されるプラグ14を形成する。この化学機械研磨は、キャップ絶縁膜9の一部である窒化シリコン膜をストッパにして行う。

【0045】

このように、本実施形態では、まずアクティブ領域Lの長辺方向に延在するスリット状(溝状)の開孔部27を有する耐エッチングマスク24を使って酸化シリコン膜21、22、23をドライエッチングすることにより、ゲート電極7のスペースにコンタクトホール(開孔部)12、13を形成する。次に、コンタクトホール12、13の壁面を構成するゲート電極7の側壁および酸化シリコン膜22、21の側壁に酸化シリコン膜11Aによって構成される側壁絶縁膜11を形成した後、コンタクトホール12、13の内部にプラグ14を形成する。

【0046】

また、本実施形態では、キャップ絶縁膜9の一部を窒化シリコン膜で構成する積層構造とすることにより、前記n型多結晶シリコン膜14Aに化学機械研磨を施す際に前記窒化シリコン膜をストッパとして使用することができ、キャップ絶縁膜9の膜厚の制御が容易になる。

【0047】

さらに、本実施形態のキャップ絶縁膜9は、前記化学機械研磨の際にストッパとして使用される窒化シリコン膜の下層に酸化シリコン膜を設けた積層構造となっているので、前記ゲート電極7の加工の際に対レジスト選択比や対タングステン選択比の観点からは好ましくない窒化シリコン膜の膜厚を抑えつつ、化学機械研磨終了時点でのキャップ絶縁膜9の膜厚を確保することができる。

【0048】

図32(a)は、上記したスリット状(溝状)の開孔部27を有する耐エッチングマスク24を使って形成したコンタクトホール12の概略平面図である。このコンタクトホール12の側壁には酸化シリコン膜によって構成される側壁絶縁膜11が形成されるので、この側壁絶縁膜11の内側の領域(グレイの着色を施した領域)がコンタクトホール12の底部に露出したn型半導体領域8とプラグ14とが接触する領域になる。

【0049】

一方、図32(b)は、コンタクトホール開孔領域に穴状の開孔部30を有する耐エッチングマスクを使って形成したコンタクトホール12の概略平面図である。この場合もコンタクトホール12の側壁に側壁絶縁膜11が形成されるので、この側壁絶縁膜11の内側の領域(グレイの着色を施した領域))がコンタクトホール12の底部に露出したn型半導体領域8とプラグ14とが接触する領域になる。ところが、このような穴状の開孔部30を有する耐エッチングマスクを使って形成したコンタクトホール12は、フォトマスクの合わせずれによって開孔部30の位置がアクティブ領域Lの長辺方向にずれた場合、図32(c)に示すように、n型半導体領域8とプラグ14とが接触する領域が小さくなる。これに対し、アクティブ領域Lの長辺方向に延在するスリット状(溝状)の開孔部27を有する耐エッチングマスクを使って形成したコンタクトホール12の場合は、フォトマスクの合わせずれによって開孔部27の位置がアクティブ領域Lの長辺方向にずれた場合でも、n型半導体領域8とプラグ14とが接触する領域が小さくなることはない。すなわち、スリット状(溝状)の開孔部27を有する耐エッチングマスクを使ってコンタクトホール12を形成する本実施形態によれば、コンタクトホール12に埋め込んだプラグ14とn型半導体領域8との接触面積を最大限に確保することができるので、プラグ14とn型半導体領域8との間の接触抵抗の増大を抑制することができる。

【0050】

耐エッチングマスクに形成された開孔部の形状によるプラグ14とn型半導体領域8とのコンタクト面積の差は、従来のセルフアライン・コンタクト(SAC)技術で行われているように、ゲート電極の側壁に側壁絶縁膜を形成した後、ゲート電極のスペースにコンタクトホールを形成する場合と、本実施形態のように、ゲート電極のスペースにコンタクトホールを形成した後、ゲート電極の側壁に側壁絶縁膜を形成する場合とで異なってくる。

【0051】

図33(a)は、ゲート電極の側壁に側壁絶縁膜を形成した後、ゲート電極のスペースにコンタクトホールを形成した場合における、スリット状(溝状)の開孔部27の幅および穴状の開孔部30の径と上記コンタクト面積との関係を示すグラフである。図示のように、この場合は、開孔部の形状による接触面積の差は小さい。一方、図33(b)は、ゲート電極のスペースにコンタクトホールを形成した後、ゲート電極の側壁に側壁絶縁膜を形成した場合における、スリット状(溝状)の開孔部27の幅および穴状の開孔部30の径と上記接触面積との関係を示すグラフである。図示のように、この場合は、開孔部の形状による接触面積の差が顕在化し、しかも加工寸法の微細化が進むほど接触面積の差が大きくなる。

【0052】

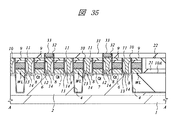

次に、図34〜図36に示すように、基板1上にCVD法で膜厚300nm程度の酸化シリコン膜31を堆積した後、フォトレジスト膜(図示せず)をマスクにしてコンタクトホール12の上部の酸化シリコン膜31をドライエッチングすることにより、後に形成されるビット線BLとコンタクトホール12とを接続するためのスルーホール32を形成する。このとき、図示しない周辺回路領域にも、第1層目の配線と素子とを接続するためのコンタクトホールを形成する。なお、コンタクトホール12の上部の酸化シリコン膜31をドライエッチングする際にコンタクトホール12に埋め込んだプラグ14が削られるのを防ぐ対策として、酸化シリコン膜31の下層に膜厚10nm程度の窒化シリコン膜(図示せず)を堆積し、この窒化シリコン膜をエッチングストッパにして酸化シリコン膜31をドライエッチングした後、窒化シリコン膜をエッチングしてもよい。

【0053】

次に、スルーホール32の内部にプラグ33を形成する。プラグ33を形成するには、例えばCVD法で酸化シリコン膜31の上部にTiNなどからなるバリアメタル膜を堆積し、続いてバリアメタル膜の上部にCVD法でW膜を堆積することによってスルーホール32の内部にこれらの膜を埋め込んだ後、スルーホール32の外部のこれらの膜を化学機械研磨法で除去する。このとき、図示しない周辺回路領域のコンタクトホールの内部にもプラグ33を形成する。

【0054】

次に、図37〜図39に示すように、酸化シリコン膜31の上部にビット線BLを形成する。ビット線BLを形成するには、例えば酸化シリコン膜31の上部にスパッタリング法で膜厚10nm程度のTiN膜(またはWN膜)および膜厚50nm程度のW膜を堆積した後、フォトレジスト膜をマスクにしてこれらの膜をドライエッチングする。ビット線BLは、スルーホール32の内部に埋め込まれたプラグ33およびコンタクトホール12の内部に埋め込まれたプラグ14を介してメモリセル選択用MISFETQtのn型半導体領域(ソース、ドレイン領域)8の一方と電気的に接続される。なお、ビット線BLは、例えば特願平11−115871号に記載されているようなダマシン(Damascene)法によって形成することもできる。

【0055】

このように、本実施形態のDRAMは、メモリセル選択用MISFETQtのゲート電極7の側壁に窒化シリコン膜によって構成される側壁絶縁膜10と酸化シリコン膜によって構成される側壁絶縁膜11とを形成し、これらの側壁絶縁膜10、11によって周囲を囲まれたゲート電極7のスペース(コンタクトホール12、13)にプラグ14を埋め込む。これにより、酸化シリコン膜よりも比誘電率が大きい窒化シリコン膜だけで側壁絶縁膜を構成する従来のセルフアライン・コンタクト(SAC)技術に比べて側壁絶縁膜の実効的な比誘電率を小さくすることができるため、ビット線容量の主要な成分である対ワード線容量成分を小さくすることができる。

【0056】

また、本実施形態のDRAMは、ゲート電極7の上部のキャップ絶縁膜9を酸化シリコン膜と窒化シリコン膜との積層膜で構成する。これにより、酸化シリコン膜よりも比誘電率が大きい窒化シリコン膜だけでキャップ絶縁膜を構成する従来のセルフアライン・コンタクト(SAC)技術に比べてキャップ絶縁膜の実効的な比誘電率を小さくすることができるため、対ワード線容量成分をさらに小さくすることができる。

【0057】

次に、図40に示すように、ビット線BLの上部にCVD法で膜厚300nm程度の酸化シリコン膜34を堆積した後、その表面を化学機械研磨法で平坦化する。次に、酸化シリコン膜34の上部にCVD法で膜厚50nm程度の窒化シリコン膜35を堆積した後、窒化シリコン膜35および酸化シリコン膜35、31をドライエッチングすることによって、前記プラグ14が埋め込まれたコンタクトホール13の上部にスルーホール36を形成する。

【0058】

次に、スルーホール36の内部にプラグ37を形成し、さらにプラグ37の表面にバリアメタル膜38を形成する。プラグ37およびバリアメタル膜38を形成するには、例えば窒化シリコン膜35の上部にPをドープしたn型多結晶シリコン膜をCVD法で堆積することによってスルーホール36の内部にn型多結晶シリコン膜を埋め込んだ後、スルーホール36の外部のn型多結晶シリコン膜をドライエッチングで除去する。このとき、スルーホール36の内部のn型多結晶シリコン膜をオーバーエッチングし、プラグ37の表面を窒化シリコン膜35の表面よりも下方に後退させることによって、プラグ37の上部にバリアメタル膜38を埋め込むためのスペースを確保する。次に、窒化シリコン膜35の上部にスパッタリング法でTiN膜を堆積することにより、スルーホール36内のプラグ37の上部にTaN(窒化タンタル)膜を埋め込んだ後、スルーホール36の外部のTaN膜を化学機械研磨法で除去する。

【0059】

後の工程でスルーホール36の上部に形成する情報蓄積用容量素子Cの下部電極とプラグ37との間に介在する上記バリアメタル膜38は、情報蓄積容量素子Cの容量絶縁膜形成工程で行われる高温熱処理の際に、下部電極を構成するRu膜とプラグ37を構成する多結晶シリコン膜との界面で所望しない反応が生じるのを抑制するために形成する。

【0060】

前述したように、ゲート電極7の側壁に形成された2層の側壁絶縁膜10、11のうち、外側の側壁絶縁膜11は、ゲート電極7の側壁における高さがキャップ絶縁膜9の上面よりも低いため、ゲート長方向に沿ったコンタクトホール12、13の断面は、上部の径が底部の径よりも大きい(図24参照)。すなわち、コンタクトホール12、13の内部に埋め込まれたプラグ14の径は、コンタクトホール12、13の底部よりも上部の方が大きい。

【0061】

これにより、コンタクトホール13の上部にスルーホール36を形成した際、フォトマスクの合わせずれなどによってスルーホール36の中心がコンタクトホール13の中心からずれたとしても、コンタクトホール13の表面積が大きいために、両者の接触面積を十分に確保することができる。

【0062】

その後、スルーホール36の上部に下部電極41、容量絶縁膜42および上部電極43によって構成される情報蓄積用容量素子Cを形成し、スルーホール36の内部に埋め込まれたプラグ37およびコンタクトホール13の内部に埋め込まれたプラグ14を介して情報蓄積用容量素子Cの下部電極41とメモリセル選択用MISFETQtのn型半導体領域(ソース、ドレイン領域)8の他方とを電気的に接続することにより、前記図2に示すDRAMのメモリセルが完成する。

【0063】

情報蓄積用容量素子Cを形成するには、例えば図41に示すように、窒化シリコン膜35の上部にCVD法で膜厚1μm程度の厚い酸化シリコン膜39を堆積し、続いてフォトレジスト膜をマスクにして酸化シリコン膜39ドライエッチングすることにより、スルーホール36の上部に溝40を形成する。酸化シリコン膜39のエッチングは、窒化シリコン膜35をエッチングストッパにして行い、下層の酸化シリコン膜34が削られないようにする。

【0064】

次に、フォトレジスト膜を除去した後、溝40の内部を含む酸化シリコン膜39の上部にCVD法で膜厚70nm〜80nm程度のRu膜を堆積する。次に、溝40の内部のRu膜が除去されるのを防ぐために溝40の内部にフォトレジスト膜を埋め込んだ後、このフォトレジスト膜で覆われていない溝40の外部のRu膜をドライエッチングによって除去し、溝40の内部に埋め込んだフォトレジスト膜をアッシングで除去することにより、溝40の側壁および底面にRu膜によって構成される下部電極41を形成する。

【0065】

次に、下部電極41が形成された溝40の内部を含む酸化シリコン膜39上に容量絶縁膜42を形成する。容量絶縁膜42は、例えばCVD法で堆積した膜厚は20nm程度のBST膜によって構成する。容量絶縁膜42は、BST膜の他、例えばBaTiO3(チタン酸バリウム)、PbTiO3(チタン酸鉛)、PZT、PLT、PLZTなどのペロブスカイト型金属酸化物からなる高(強)誘電体膜によって構成することもできる。次に、容量絶縁膜42の上部に上部電極43を形成する。上部電極43は、例えばCVD法またはスパッタリング法で堆積した膜厚200nm程度のRu膜によって構成する。ここまでの工程により、Ru膜によって構成される下部電極41、BST膜によって構成される容量絶縁膜42およびRu膜によって構成される上部電極43からなる情報蓄積用容量素子Cが完成する。その後、情報蓄積用容量素子Cの上部に層間絶縁膜を挟んで2層程度のAl配線を形成し、最上層のAl配線の上部にパッシベーション膜を形成するがそれらの図示は省略する。

【0066】

(実施の形態2)

本実施形態のDRAMの製造方法を図42〜図45を用いて工程順に説明する。まず、図42に示すように、前記実施の形態1と同様の方法でメモリセル選択用MISFETQtを形成し、続いてその上部に酸化シリコン膜21〜23を形成した後、酸化シリコン膜23の上部に耐エッチングマスク24を形成する。ここまでの工程は、前記実施の形態1の図3〜図18に示した工程と同じである。

【0067】

次に、図43に示すように、耐エッチングマスク24をマスクにして酸化シリコン膜21、22、23をドライエッチングすることにより、ゲート電極7のスペースにコンタクトホール(開孔部)12、13を形成する。このとき、本実施形態では、n型半導体領域(ソース、ドレイン領域)8の上部を覆っている窒化シリコン膜10Aもエッチングし、コンタクトホール(開孔部)12、13の底部にn型半導体領域(ソース、ドレイン領域)8の表面を露出させる。前記実施の形態1と同様、ここまでの工程により、ゲート電極7(ワード線WL)の側壁に窒化シリコン膜10Aによって構成される側壁絶縁膜10が形成される。

【0068】

次に、上記ドライエッチングでダメージを受けたn型半導体領域(ソース、ドレイン領域)8の表面を薄くドライエッチングした後、図44に示すように、基板1上にCVD法で膜厚30nm程度の酸化シリコン膜11Aを堆積し、続いて図45に示すように、酸化シリコン膜11Aを異方的にエッチングすることにより、ゲート電極7(ワード線WL)の側壁に膜厚30nm程度の酸化シリコン膜11Aによって構成される側壁絶縁膜11を形成する。その後の工程は、前記実施の形態1と同じである。

【0069】

このように、本実施形態の製造方法は、コンタクトホール12、13の底部の窒化シリコン膜10Aを除去した後、ゲート電極7(ワード線WL)の側壁に側壁絶縁膜11を形成するので、側壁絶縁膜11の底部には窒化シリコン膜10Aが残らない(図45)。

【0070】

一方、ゲート電極7(ワード線WL)の側壁に側壁絶縁膜11を形成した後にコンタクトホール12、13の底部の窒化シリコン膜10Aを除去する前記実施の形態1の製造方法では、側壁絶縁膜11の底部に窒化シリコン膜10Aが残る(図26)。このように、ゲート電極7(ワード線WL)の側壁端部に窒化シリコン膜10Aが残ると、この窒化シリコン膜10Aとその下層のゲート絶縁膜6との界面が帯電し、メモリセルのリーク電流を変動させる要因となる。

【0071】

従って、ゲート電極7(ワード線WL)の側壁端部に窒化シリコン膜10Aを残さない本実施形態の製造方法によれば、上記した不具合を防止してメモリセルの特性変動を抑制することができる。

【0072】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0073】

【発明の効果】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0074】

本発明によれば、ビット線の容量を低減することができる。これにより、情報蓄積用容量素子に蓄積された電荷(情報)を読み出すときの信号電圧を大きくすることができるので、信号のノイズマージンが大きくなり、リフレッシュサイクルを延ばし、消費電力を低減することができる。

【0075】

また、一本のビット線に接続するメモリセルの数を増やすことができるので、センスアンプの数を減らすことができ、その分、チップ面積を縮小することができるので、ウエハ当たりのチップ取得数を増やして製造歩留まりを向上させることができる。

【図面の簡単な説明】

【図1】本発明の一実施の形態であるDRAMを形成した半導体チップの全体平面図である。

【図2】本発明の一実施の形態であるDRAMの構成を示す半導体基板の要部断面図である。

【図3】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部平面図である。

【図4】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図5】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図6】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図7】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図8】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図9】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図10】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図11】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部平面図である。

【図12】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図13】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図14】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図15】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図16】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図17】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図18】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図19】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部平面図である。

【図20】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図21】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図22】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図23】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図24】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図25】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図26】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図27】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図28】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図29】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図30】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図31】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図32】(a)は、スリット状(溝状)の開孔部を有する耐エッチングマスクを使って形成したコンタクトホールの概略平面図、(b)および(c)は、穴状の開孔部を有する耐エッチングマスクを使って形成したコンタクトホールの概略平面図である。

【図33】(a)は、ゲート電極の側壁に側壁絶縁膜を形成した後、ゲート電極のスペースにコンタクトホールを形成した場合における、スリット状(溝状)の開孔部の幅および穴状の開孔部の径とコンタクト面積との関係を示すグラフであり、(b)は、ゲート電極のスペースにコンタクトホールを形成した後、ゲート電極の側壁に側壁絶縁膜を形成した場合における、スリット状(溝状)の開孔部の幅および穴状の開孔部の径とコンタクト面積との関係を示すグラフである。

【図34】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部平面図である。

【図35】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図36】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図37】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部平面図である。

【図38】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図39】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図40】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図41】本発明の一実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図42】本発明の他の実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図43】本発明の他の実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図44】本発明の他の実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【図45】本発明の他の実施の形態であるDRAMの製造方法を示す半導体基板の要部断面図である。

【符号の説明】

1 半導体基板

1A 半導体チップ

2 p型ウエル

4 素子分離溝

5 酸化シリコン膜

6 ゲート絶縁膜

7 ゲート電極

7A 導電体膜

8 n型半導体領域(ソース、ドレイン)

9 キャップ絶縁膜

9A 絶縁膜

10 側壁絶縁膜

10A 窒化シリコン膜

11 側壁絶縁膜

11A 窒化シリコン膜

12、13 コンタクトホール(開孔部)

14 プラグ

14A n型多結晶シリコン膜

20 フォトレジスト膜

21、22、23 酸化シリコン膜

24A 多結晶シリコン膜

24 耐エッチングマスク

25 反射防止膜

26 フォトレジスト膜

27 開孔部

30 開孔部

31 酸化シリコン膜

32 スルーホール

33 プラグ

34 酸化シリコン膜

35 窒化シリコン膜

36 スルーホール

37 プラグ

38 バリアメタル膜

39 酸化シリコン膜

40 溝

41 下部電極

42 容量絶縁膜

43 上部電極

BL ビット線

BP ボンディングパッド

C 情報蓄積用容量素子

L アクティブ領域

MARY メモリアレイ

PC 周辺回路部

WL ワード線

Claims (6)

- 半導体基板上に形成されたMISFETと、前記MISFETのソース、ドレイン領域上に形成されたコンタクトホールと、前記コンタクトホールの内部に形成され、前記ソース、ドレイン領域と電気的に接続された導電体と、前記導電体の周囲に形成された第1および第2の絶縁膜とを有する半導体集積回路装置であって、前記第1の絶縁膜は、前記コンタクトホールの底部では、前記導電体の周囲を囲むように形成され、前記コンタクトホールの上部では、少なくとも一部が除去されて前記導電体の高さより低く形成されており、前記第2の絶縁膜は、前記コンタクトホールを内側にして前記第1の絶縁膜を挟むように形成され、前記導電体の高さとほぼ同じで、その膜厚が前記第1の絶縁膜の膜厚より薄く形成されていることを特徴とする半導体集積回路装置。

- 請求項1記載の半導体集積回路装置において、前記第1の絶縁膜は、その高さが低くなっている部分では、前記導電体に覆われていることを特徴とする半導体集積回路装置。

- 請求項1記載の半導体集積回路装置において、前記MISFETのゲート電極上にキャップ絶縁膜が形成されており、前記第1の絶縁膜の低くなっている部分の高さは、前記ゲート電極の上端部よりも高く、前記キャップ絶縁膜の上端部よりも低いことを特徴とする半導体集積回路装置。

- 請求項3記載の半導体集積回路装置において、前記第1の絶縁膜の比誘電率は、前記キャップ絶縁膜の比誘電率よりも小さいことを特徴とする半導体集積回路装置。

- 請求項1記載の半導体集積回路装置において、前記第1の絶縁膜は、酸化シリコンを主成分とし、前記第2の絶縁膜は、窒化シリコンを主成分とすることを特徴とする半導体集積回路装置。

- 請求項1記載の半導体集積回路装置において、前記第1の絶縁膜の比誘電率は、前記第2の絶縁膜の比誘電率よりも小さいことを特徴とする半導体集積回路装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000013476A JP3645463B2 (ja) | 2000-01-21 | 2000-01-21 | 半導体集積回路装置 |

| TW090100268A TW508757B (en) | 2000-01-21 | 2001-01-05 | Semiconductor integrated circuit device and process for manufacturing the same |

| KR1020010003400A KR100737200B1 (ko) | 2000-01-21 | 2001-01-20 | 반도체 집적 회로 장치 |

| US09/765,574 US6555861B2 (en) | 2000-01-21 | 2001-01-22 | Semiconductor integrated circuit device and process for manufacturing the same |

| US10/396,339 US6791137B2 (en) | 2000-01-21 | 2003-03-26 | Semiconductor integrated circuit device and process for manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000013476A JP3645463B2 (ja) | 2000-01-21 | 2000-01-21 | 半導体集積回路装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004367664A Division JP4215711B2 (ja) | 2004-12-20 | 2004-12-20 | 半導体集積回路装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001203337A JP2001203337A (ja) | 2001-07-27 |

| JP2001203337A5 JP2001203337A5 (ja) | 2005-02-03 |

| JP3645463B2 true JP3645463B2 (ja) | 2005-05-11 |

Family

ID=18541062

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000013476A Expired - Fee Related JP3645463B2 (ja) | 2000-01-21 | 2000-01-21 | 半導体集積回路装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6555861B2 (ja) |

| JP (1) | JP3645463B2 (ja) |

| KR (1) | KR100737200B1 (ja) |

| TW (1) | TW508757B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002217383A (ja) * | 2001-01-12 | 2002-08-02 | Hitachi Ltd | 半導体集積回路装置の製造方法および半導体集積回路装置 |

| JP4528504B2 (ja) * | 2003-08-22 | 2010-08-18 | ルネサスエレクトロニクス株式会社 | 半導体装置とその製造方法 |

| KR100809597B1 (ko) * | 2006-04-06 | 2008-03-04 | 삼성전자주식회사 | 미세 패턴 형성 방법 및 이를 이용한 반도체 메모리 장치의형성 방법 |

| JP2008021809A (ja) * | 2006-07-12 | 2008-01-31 | Elpida Memory Inc | 半導体装置およびその製造方法 |

| KR100891329B1 (ko) * | 2007-01-26 | 2009-03-31 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

| JP2010287853A (ja) * | 2009-06-15 | 2010-12-24 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| US8487369B2 (en) * | 2009-10-30 | 2013-07-16 | Hynix Semiconductor Inc. | Semiconductor device with buried gates and buried bit lines and method for fabricating the same |

| JP2011216526A (ja) * | 2010-03-31 | 2011-10-27 | Renesas Electronics Corp | 半導体装置の製造方法、及び半導体装置 |

| JP2012134395A (ja) * | 2010-12-22 | 2012-07-12 | Elpida Memory Inc | 半導体装置および半導体装置の製造方法 |

| US20160322473A1 (en) * | 2015-04-30 | 2016-11-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Buffer Layer on Gate and Methods of Forming the Same |

| CN116133436A (zh) * | 2021-11-12 | 2023-05-16 | 联华电子股份有限公司 | 半导体元件及其制作方法 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07106437A (ja) | 1993-10-01 | 1995-04-21 | Hitachi Ltd | 半導体記憶装置 |

| JP3203118B2 (ja) | 1993-12-27 | 2001-08-27 | 三洋電機株式会社 | 非水電解液二次電池 |

| JPH08204144A (ja) | 1995-01-24 | 1996-08-09 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2953404B2 (ja) * | 1995-12-08 | 1999-09-27 | ソニー株式会社 | 半導体装置及びその製造方法 |

| JPH1027906A (ja) * | 1996-07-09 | 1998-01-27 | Nippon Steel Corp | 半導体装置の製造方法 |

| JPH1032245A (ja) * | 1996-07-17 | 1998-02-03 | Toshiba Corp | 半導体装置の製造方法 |

| JP3869089B2 (ja) * | 1996-11-14 | 2007-01-17 | 株式会社日立製作所 | 半導体集積回路装置の製造方法 |

| JPH10335652A (ja) * | 1997-05-30 | 1998-12-18 | Hitachi Ltd | 半導体集積回路装置の製造方法 |

| JP3701469B2 (ja) * | 1998-06-12 | 2005-09-28 | 株式会社ルネサステクノロジ | 半導体集積回路装置の製造方法 |

| JP2000013476A (ja) | 1998-06-24 | 2000-01-14 | Matsushita Electric Ind Co Ltd | 電話装置 |

-

2000

- 2000-01-21 JP JP2000013476A patent/JP3645463B2/ja not_active Expired - Fee Related

-

2001

- 2001-01-05 TW TW090100268A patent/TW508757B/zh not_active IP Right Cessation

- 2001-01-20 KR KR1020010003400A patent/KR100737200B1/ko not_active Expired - Lifetime

- 2001-01-22 US US09/765,574 patent/US6555861B2/en not_active Expired - Lifetime

-

2003

- 2003-03-26 US US10/396,339 patent/US6791137B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20030183941A1 (en) | 2003-10-02 |

| US6791137B2 (en) | 2004-09-14 |

| US6555861B2 (en) | 2003-04-29 |

| TW508757B (en) | 2002-11-01 |

| US20020043680A1 (en) | 2002-04-18 |

| KR20010076421A (ko) | 2001-08-11 |

| KR100737200B1 (ko) | 2007-07-10 |

| JP2001203337A (ja) | 2001-07-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7196368B2 (en) | Semiconductor memory arrangements with crown shaped capacitor arrangements trenched in interlayer dielectric film | |

| KR100704244B1 (ko) | 반도체기억장치및그제조방법 | |

| US20020060334A1 (en) | Semiconductor integrated circuit device and method of manufacturing the same | |

| JPWO1997019468A1 (ja) | 半導体記憶装置およびその製造方法 | |

| US7361552B2 (en) | Semiconductor integrated circuit including a DRAM and an analog circuit | |

| US6335241B1 (en) | Semiconductor device and manufacturing method thereof | |

| KR20000022861A (ko) | 반도체집적회로장치 및 그 제조방법 | |

| JP3943294B2 (ja) | 半導体集積回路装置 | |

| US7141471B2 (en) | Method of producing semiconductor integrated circuit device and semiconductor integrated circuit device | |

| US6184079B1 (en) | Method for fabricating a semiconductor device | |

| JP3645463B2 (ja) | 半導体集積回路装置 | |

| US5930623A (en) | Method of forming a data storage capacitor with a wide electrode area for dynamic random access memory using double spacers | |

| US5854106A (en) | Method of forming a data storage capacitor with a wide electrode area for dynamic random access memory | |

| US6482727B2 (en) | Method of producing a semiconductor integrated circuit device and the semiconductor integrated circuit device | |

| JP4215711B2 (ja) | 半導体集積回路装置およびその製造方法 | |

| US20050087874A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP2725652B2 (ja) | 半導体記憶装置 | |

| JP4133039B2 (ja) | 半導体集積回路装置の製造方法および半導体集積回路装置 | |

| JPH1117116A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040701 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040720 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040921 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050118 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050203 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080210 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090210 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100210 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110210 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110210 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120210 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120210 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130210 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140210 Year of fee payment: 9 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |