JP2017538293A - 歪みの少ないセラミックの支持プレート及び製造のための方法 - Google Patents

歪みの少ないセラミックの支持プレート及び製造のための方法 Download PDFInfo

- Publication number

- JP2017538293A JP2017538293A JP2017531824A JP2017531824A JP2017538293A JP 2017538293 A JP2017538293 A JP 2017538293A JP 2017531824 A JP2017531824 A JP 2017531824A JP 2017531824 A JP2017531824 A JP 2017531824A JP 2017538293 A JP2017538293 A JP 2017538293A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- support plate

- ceramic

- tension

- glass

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/16—Printed circuits incorporating printed electric components, e.g. printed resistors, capacitors or inductors

- H05K1/162—Printed circuits incorporating printed electric components, e.g. printed resistors, capacitors or inductors incorporating printed capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01C—RESISTORS

- H01C7/00—Non-adjustable resistors formed as one or more layers or coatings; Non-adjustable resistors made from powdered conducting material or powdered semi-conducting material with or without insulating material

- H01C7/10—Non-adjustable resistors formed as one or more layers or coatings; Non-adjustable resistors made from powdered conducting material or powdered semi-conducting material with or without insulating material voltage responsive, i.e. varistors

- H01C7/105—Varistor cores

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0271—Arrangements for reducing stress or warp in rigid printed circuit boards, e.g. caused by loads, vibrations or differences in thermal expansion

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/16—Printed circuits incorporating printed electric components, e.g. printed resistors, capacitors or inductors

- H05K1/167—Printed circuits incorporating printed electric components, e.g. printed resistors, capacitors or inductors incorporating printed resistors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0044—Mechanical working of the substrate, e.g. drilling or punching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/67—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their insulating layers or insulating parts

- H10W70/68—Shapes or dispositions thereof

- H10W70/685—Shapes or dispositions thereof comprising multiple insulating layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/67—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their insulating layers or insulating parts

- H10W70/69—Insulating materials thereof

- H10W70/692—Ceramics or glasses

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/63—Vias, e.g. via plugs

- H10W70/635—Through-vias

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Inorganic Chemistry (AREA)

- Electromagnetism (AREA)

- Physics & Mathematics (AREA)

- Compositions Of Oxide Ceramics (AREA)

- Thermistors And Varistors (AREA)

- Ceramic Capacitors (AREA)

- Apparatuses And Processes For Manufacturing Resistors (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Laminated Bodies (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

Description

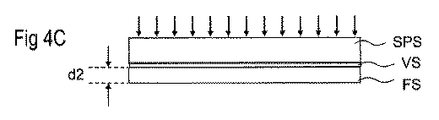

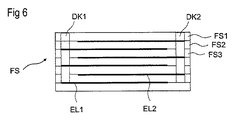

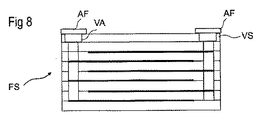

FS セラミックの機能層

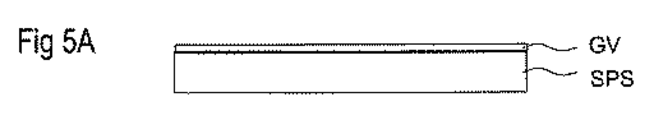

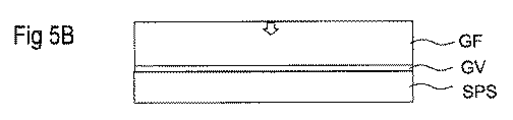

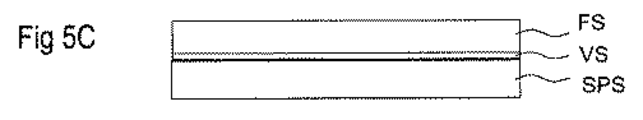

SPS セラミックのテンション層

VS 結合層

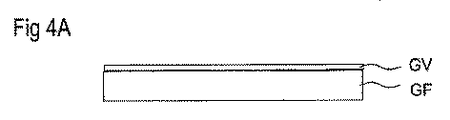

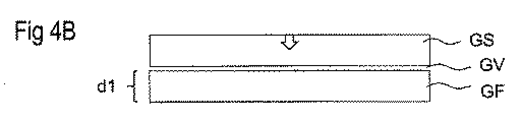

GV 結合層のためのガラスペースト層

CTE 熱膨張係数

GF セラミックの機能層のためのグリーン体

GS セラミックのテンション層のためのグリーン体

FS1,FS2 機能層の部分層

GS テンション層のためのグリーンシート

AF 電気的な接続面

VA 結合層を通るビア

Claims (17)

- −第1のセラミックの機能層と、

−結合層(VS)と、

−セラミックのテンション層(SPS)と、

を含み、

−前記セラミックの機能層(FS)が、支持プレート(TP)のために、前記結合層(VS)を介して前記セラミックのテンション層(SPS)に結合されており、

−前記セラミックの機能層(FS)には、電気部品と接続可能な受動電気構成要素が組み込まれており、

−前記機能層(FS)及び前記テンション層(SPS)はガラスを含んでいないか、又は5質量(%)より小さなわずかなガラス割合のみを有し、

−前記結合層(VS)が、ガラス成分を含むか、又はガラス層である、

電気部品のための支持プレート。 - 前記結合層(VS)の厚さが0.5〜10μmである、

請求項1に記載の支持プレート。 - 請求項1又は2に記載の支持プレート

前記結合層(VS)が、前記ガラス成分のほかに、焼結されていないセラミックの充填材料を更に含んでいる、

請求項1又は2に記載の支持プレート。 - 前記テンション層(SPS)が、前記機能層(FS)及び前記結合層(VS)の焼結温度を超える焼結温度を有している、

請求項1〜3のいずれか1項に記載の支持プレート。 - 前記テンション層(SPS)が、前記機能層(FS)の熱膨張係数CTEFよりも低い、比較的低い熱膨張係数CTESを備えている、

請求項1〜4のいずれか1項に記載の支持プレート。 - 第2の結合層(VS2)及び第2のテンション層(SPS2)を有し、該第2のテンション層が前記第2の結合層を介して前記機能層(FS)の、前記第1のテンション層から離れるように向いたその表面に結合されており、その結果、前記支持プレートが、層の順序、材料及び層厚に関して対称の構造を備えている、

請求項1〜5のいずれか1項に記載の支持プレート。 - 前記少なくとも1つの結合層(VS)が、主要成分として、合計で該結合層の少なくとも70質量%を含む、Si及び/又はGe、B並びにKの酸化物を含んでおり、前記結合層において100質量%まで不足している割合が高焼結された充填材料で形成されている、

請求項1〜6のいずれか1項に記載の支持プレート。 - 前記機能層(FS)が、バリスタ材料から成る層を含んでいるとともに、少なくとも2つの電極層(EL1,EL2)を備えている、

請求項1〜7のいずれか1項に記載の支持プレート。 - 前記機能層(FS)が、NTCセラミック又はPTCセラミックの層、セラミックの多層コンデンサ、フェライト層、圧電層及びLTCCセラミックから選択されている、

請求項1〜7のいずれか1項に記載の支持プレート。 - 前記機能層(FS)が、異なる電子セラミック特性及び異なる受動電気部品のための電極へ構造化されている少なくとも3つのメタライズ平面を有する少なくとも2つの異なる部分層(FS1,FS2)を備えており、前記異なる受動電気部品が前記機能層へ組み込まれている、

請求項8又は9に記載の支持プレート。 - 前記テンション層(SPS)がZrO2、MgO、SrCO3、BaCO3又はMgSiO4のような高焼結される酸化物及び化合物を基礎とする層である、

請求項1〜10のいずれか1項に記載の支持プレート。 - a)受動電気構成要素があらかじめ形成されたセラミックの機能層のためのグリーン体を設ける工程と、

b)前記グリーン体上へガラス粒子の比較的薄い層を設ける工程と、

c)セラミックのテンション層のためのグリーン体をガラス粒子上へ設ける工程と、

d)ガラス粒子及びセラミックの機能層の焼結温度より高い温度で構造を焼結する工程と、

e)前記構造をコントロールしつつ冷却する工程であって、1〜10μmの厚さのガラス層を有する固体の結合部が生じ、側方の焼結収縮が軸線ごとに3%より小さい値に制限されている、工程と、

を含む、請求項1に記載の支持プレートを製造するための方法。 - 前記セラミックの機能層のための前記グリーン体が少なくとも1つのグリーンシートを含んでおり、該グリーンシートでは、ガラス粒子の層がペーストの形態で少なくとも1つのグリーンシート上に設けられており、該グリーンシートでは、前記セラミックのテンション層のためのグリーン体としてペースト又はグリーンシートがガラス粒子の層上へ設けられる、

請求項12に記載の方法。 - A)テンション層(SPS)のための固体のセラミックのプレートを設ける工程と、

B)ガラス粒子の比較的薄い層(GV)を前記テンション層上へ設ける工程と、

C)セラミックの機能層(GF)のためのグリーン体をガラス粒子の層(GV)上へ設け、その中に受動電気構成要素をあらかじめ形成する工程と、

d)ガラス粒子及びセラミックの機能層の焼結温度より高い温度で構造を焼結する工程と、

e)前記構造をコントロールしつつ冷却する工程であって、1〜10μmの厚さのガラス層VSを有する固体の結合部が生じ、側方の焼結収縮が軸線ごとに3%より小さい値に制限されている、工程と、

を代替的に含む、請求項1に記載の支持プレートを製造するための方法。 - f)冷却後に機械的な除去方法を実行する工程であって、その際、前記テンション層(SPS)が再び除去される、工程、

を更に含む、請求項1〜14のいずれか1項に記載の方法。 - 前記除去方法として、サンドブラスト、ブラッシング又は研磨が用いられる、請求項15に記載の方法。

- 工程E)又はe)の後に、固体の結合部において、受動構成要素の最上の接触部がガラス層の下方で露出し、

電気部品のための電気的な接続面が、導電的な接触部において、前記最上の接触部と共に前記結合部上へ設けられる、請求項12〜16のいずれか1項に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102014118749.0 | 2014-12-16 | ||

| DE102014118749.0A DE102014118749A1 (de) | 2014-12-16 | 2014-12-16 | Verzugsarme keramische Trägerplatte und Verfahren zur Herstellung |

| PCT/EP2015/079813 WO2016096870A1 (de) | 2014-12-16 | 2015-12-15 | Verzugsarme keramische trägerplatte und verfahren zur herstellung |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020126497A Division JP2020184646A (ja) | 2014-12-16 | 2020-07-27 | 歪みの少ないセラミックの支持プレート及び製造のための方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017538293A true JP2017538293A (ja) | 2017-12-21 |

| JP2017538293A5 JP2017538293A5 (ja) | 2018-12-27 |

Family

ID=55027717

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017531824A Withdrawn JP2017538293A (ja) | 2014-12-16 | 2015-12-15 | 歪みの少ないセラミックの支持プレート及び製造のための方法 |

| JP2020126497A Pending JP2020184646A (ja) | 2014-12-16 | 2020-07-27 | 歪みの少ないセラミックの支持プレート及び製造のための方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020126497A Pending JP2020184646A (ja) | 2014-12-16 | 2020-07-27 | 歪みの少ないセラミックの支持プレート及び製造のための方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20170332491A1 (ja) |

| EP (1) | EP3234957A1 (ja) |

| JP (2) | JP2017538293A (ja) |

| CN (1) | CN107004504A (ja) |

| DE (1) | DE102014118749A1 (ja) |

| WO (1) | WO2016096870A1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102464070B1 (ko) * | 2016-09-29 | 2022-11-07 | 주식회사 아모텍 | 정전기보호소자, 그 제조 방법 및 이를 구비한 휴대용 전자장치 |

| KR102732881B1 (ko) * | 2016-09-29 | 2024-11-22 | 주식회사 아모텍 | 정전기보호소자, 그 제조 방법 및 이를 구비한 휴대용 전자장치 |

| KR101963283B1 (ko) * | 2017-02-10 | 2019-03-28 | 삼성전기주식회사 | 커패시터 부품 |

| KR102404320B1 (ko) * | 2017-08-31 | 2022-06-07 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 제조방법 |

| JP6766849B2 (ja) | 2018-01-16 | 2020-10-14 | 株式会社デンソー | 回転角度検出装置 |

| CN111302789B (zh) * | 2020-03-17 | 2021-01-19 | 华南理工大学 | 一种具有三明治结构的脉冲储能介质材料及其制备方法与应用 |

| DE102020205305B4 (de) * | 2020-04-27 | 2022-06-30 | Eberspächer Catem Gmbh & Co. Kg | PTC-Heizeinrichtung und Verfahren zu deren Herstellung |

| CN114373632B (zh) * | 2022-01-22 | 2022-09-02 | 池州昀冢电子科技有限公司 | 多层陶瓷电容器及其制备方法 |

| CN118692985A (zh) * | 2024-08-26 | 2024-09-24 | 广东佛智芯微电子技术研究有限公司 | 一种玻璃键合三维堆叠结构及其制备方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06143239A (ja) * | 1992-11-02 | 1994-05-24 | Sumitomo Metal Ind Ltd | セラミックス基板の製造方法 |

| JP2002050869A (ja) * | 2000-07-31 | 2002-02-15 | Kyocera Corp | 多層配線基板の製造方法 |

| JP2002198647A (ja) * | 2000-12-26 | 2002-07-12 | Kyocera Corp | 低温焼成セラミック配線基板の製造方法 |

| WO2007004415A1 (ja) * | 2005-07-01 | 2007-01-11 | Murata Manufacturing Co., Ltd. | 多層セラミック基板およびその製造方法ならびに多層セラミック基板作製用複合グリーンシート |

| JP2008060332A (ja) * | 2006-08-31 | 2008-03-13 | Sanyo Electric Co Ltd | 積層セラミック基板の製造方法及び積層セラミック基板 |

| JP2009522792A (ja) * | 2006-01-05 | 2009-06-11 | エプコス アクチエンゲゼルシャフト | モノリシックセラミック素子および作製方法 |

| JP2014160694A (ja) * | 2013-02-19 | 2014-09-04 | Panasonic Corp | セラミック配線基板とバリスタ内蔵セラミック配線基板 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3692623B2 (ja) * | 1996-05-20 | 2005-09-07 | 株式会社デンソー | セラミック積層体及びその製造方法 |

| JP2000208074A (ja) * | 1999-01-19 | 2000-07-28 | Canon Inc | 画像表示装置および陰極管 |

| DE10145364A1 (de) * | 2001-09-14 | 2003-04-10 | Epcos Ag | Verfahren zur Herstellung eines keramischen Substrats |

| KR101108958B1 (ko) * | 2003-02-25 | 2012-01-31 | 쿄세라 코포레이션 | 적층 세라믹 콘덴서 및 그 제조방법 |

| US20100103634A1 (en) * | 2007-03-30 | 2010-04-29 | Takuo Funaya | Functional-device-embedded circuit board, method for manufacturing the same, and electronic equipment |

-

2014

- 2014-12-16 DE DE102014118749.0A patent/DE102014118749A1/de not_active Withdrawn

-

2015

- 2015-12-15 CN CN201580065212.0A patent/CN107004504A/zh active Pending

- 2015-12-15 US US15/531,361 patent/US20170332491A1/en not_active Abandoned

- 2015-12-15 WO PCT/EP2015/079813 patent/WO2016096870A1/de not_active Ceased

- 2015-12-15 EP EP15817170.2A patent/EP3234957A1/de not_active Withdrawn

- 2015-12-15 JP JP2017531824A patent/JP2017538293A/ja not_active Withdrawn

-

2020

- 2020-07-27 JP JP2020126497A patent/JP2020184646A/ja active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06143239A (ja) * | 1992-11-02 | 1994-05-24 | Sumitomo Metal Ind Ltd | セラミックス基板の製造方法 |

| JP2002050869A (ja) * | 2000-07-31 | 2002-02-15 | Kyocera Corp | 多層配線基板の製造方法 |

| JP2002198647A (ja) * | 2000-12-26 | 2002-07-12 | Kyocera Corp | 低温焼成セラミック配線基板の製造方法 |

| WO2007004415A1 (ja) * | 2005-07-01 | 2007-01-11 | Murata Manufacturing Co., Ltd. | 多層セラミック基板およびその製造方法ならびに多層セラミック基板作製用複合グリーンシート |

| JP2009522792A (ja) * | 2006-01-05 | 2009-06-11 | エプコス アクチエンゲゼルシャフト | モノリシックセラミック素子および作製方法 |

| JP2008060332A (ja) * | 2006-08-31 | 2008-03-13 | Sanyo Electric Co Ltd | 積層セラミック基板の製造方法及び積層セラミック基板 |

| JP2014160694A (ja) * | 2013-02-19 | 2014-09-04 | Panasonic Corp | セラミック配線基板とバリスタ内蔵セラミック配線基板 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN107004504A (zh) | 2017-08-01 |

| JP2020184646A (ja) | 2020-11-12 |

| US20170332491A1 (en) | 2017-11-16 |

| DE102014118749A1 (de) | 2016-06-16 |

| EP3234957A1 (de) | 2017-10-25 |

| WO2016096870A1 (de) | 2016-06-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2017538293A (ja) | 歪みの少ないセラミックの支持プレート及び製造のための方法 | |

| JP2017538293A5 (ja) | ||

| JP7148239B2 (ja) | セラミック電子部品およびその製造方法 | |

| US9136058B2 (en) | Laminated ceramic electronic component and manufacturing method therefor | |

| JP5132972B2 (ja) | 誘電体セラミックス及びその製造方法並びに積層セラミックコンデンサ | |

| JP5361635B2 (ja) | 振動体 | |

| TW505932B (en) | Chip-type electronic component and manufacturing method therefor | |

| JP5409198B2 (ja) | 振動体 | |

| KR100821274B1 (ko) | 칩 세라믹 전자부품 | |

| JP2011097016A (ja) | 積層セラミック電子部品、および積層セラミック電子部品の製造方法 | |

| CN115050576B (zh) | 陶瓷电子部件 | |

| JP2018098327A5 (ja) | ||

| JP2022530320A (ja) | 静電チャック用高密度耐食層配置 | |

| KR101452065B1 (ko) | 적층 세라믹 커패시터 및 적층 세라믹 커패시터의 실장 기판 | |

| WO2011122416A1 (ja) | 圧電素子使用装置 | |

| JP6496604B2 (ja) | 静電チャックおよびその製造方法 | |

| JP2014232850A (ja) | 積層型電子部品 | |

| JP6306316B2 (ja) | コンデンサ | |

| CN120020981A (zh) | 多层电子组件 | |

| JPWO2005104639A1 (ja) | 多層セラミック基板およびその製造方法ならびに圧電共振部品 | |

| TWI837343B (zh) | 用於靜電吸盤之高密度耐腐蝕層佈置 | |

| JP2010527143A5 (ja) | ||

| CN114180942B (zh) | 复合烧结体、半导体制造装置构件及复合烧结体的制造方法 | |

| WO2014027553A1 (ja) | Esd保護装置 | |

| KR102039802B1 (ko) | 정전척용 세라믹 본체 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181119 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190820 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190821 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191021 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20200324 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20200727 |

|

| C22 | Notice of designation (change) of administrative judge |

Free format text: JAPANESE INTERMEDIATE CODE: C22 Effective date: 20201222 |

|

| C13 | Notice of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: C13 Effective date: 20210216 |

|

| C23 | Notice of termination of proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C23 Effective date: 20210615 |

|

| C03 | Trial/appeal decision taken |

Free format text: JAPANESE INTERMEDIATE CODE: C03 Effective date: 20210720 |

|

| C30A | Notification sent |

Free format text: JAPANESE INTERMEDIATE CODE: C3012 Effective date: 20210720 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20211115 |