JP2014229814A - 薄膜トランジスタ、表示装置および電子機器 - Google Patents

薄膜トランジスタ、表示装置および電子機器 Download PDFInfo

- Publication number

- JP2014229814A JP2014229814A JP2013109773A JP2013109773A JP2014229814A JP 2014229814 A JP2014229814 A JP 2014229814A JP 2013109773 A JP2013109773 A JP 2013109773A JP 2013109773 A JP2013109773 A JP 2013109773A JP 2014229814 A JP2014229814 A JP 2014229814A

- Authority

- JP

- Japan

- Prior art keywords

- oxide semiconductor

- semiconductor layer

- barrier film

- barrier

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000010409 thin film Substances 0.000 title claims abstract description 36

- 239000010408 film Substances 0.000 claims abstract description 222

- 230000004888 barrier function Effects 0.000 claims abstract description 178

- 239000004065 semiconductor Substances 0.000 claims abstract description 115

- 239000000758 substrate Substances 0.000 claims abstract description 52

- 239000001257 hydrogen Substances 0.000 claims abstract description 32

- 229910052739 hydrogen Inorganic materials 0.000 claims abstract description 32

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims abstract description 29

- 239000012535 impurity Substances 0.000 claims abstract description 16

- 239000010410 layer Substances 0.000 claims description 132

- 239000003990 capacitor Substances 0.000 claims description 22

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 20

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 20

- 238000003860 storage Methods 0.000 claims description 19

- 239000000463 material Substances 0.000 claims description 18

- 230000001603 reducing effect Effects 0.000 claims description 16

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 13

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 11

- 229910052710 silicon Inorganic materials 0.000 claims description 11

- 239000010703 silicon Substances 0.000 claims description 11

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 9

- 239000011347 resin Substances 0.000 claims description 6

- 229920005989 resin Polymers 0.000 claims description 6

- 239000002356 single layer Substances 0.000 claims description 5

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 4

- 238000005401 electroluminescence Methods 0.000 claims description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims description 2

- 238000000034 method Methods 0.000 description 22

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 15

- 230000008569 process Effects 0.000 description 12

- 238000004544 sputter deposition Methods 0.000 description 11

- 238000005530 etching Methods 0.000 description 10

- 229910052751 metal Inorganic materials 0.000 description 10

- 239000002184 metal Substances 0.000 description 10

- 239000007789 gas Substances 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 8

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 8

- 239000011229 interlayer Substances 0.000 description 8

- 101100153525 Homo sapiens TNFRSF25 gene Proteins 0.000 description 7

- 102100022203 Tumor necrosis factor receptor superfamily member 25 Human genes 0.000 description 7

- 239000010949 copper Substances 0.000 description 7

- 229910052738 indium Inorganic materials 0.000 description 7

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 7

- 235000014692 zinc oxide Nutrition 0.000 description 7

- 239000011787 zinc oxide Substances 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 238000005070 sampling Methods 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 229910052786 argon Inorganic materials 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 229910052733 gallium Inorganic materials 0.000 description 4

- 238000006722 reduction reaction Methods 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 230000000052 comparative effect Effects 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 150000002431 hydrogen Chemical class 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- -1 polyethylene terephthalate Polymers 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 238000005033 Fourier transform infrared spectroscopy Methods 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 229920000106 Liquid crystal polymer Polymers 0.000 description 1

- 239000004977 Liquid-crystal polymers (LCPs) Substances 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 150000007513 acids Chemical class 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- 238000000231 atomic layer deposition Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000002178 crystalline material Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 101150013423 dsl-1 gene Proteins 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 229960001730 nitrous oxide Drugs 0.000 description 1

- 235000013842 nitrous oxide Nutrition 0.000 description 1

- NQBRDZOHGALQCB-UHFFFAOYSA-N oxoindium Chemical compound [O].[In] NQBRDZOHGALQCB-UHFFFAOYSA-N 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 238000001552 radio frequency sputter deposition Methods 0.000 description 1

- 238000012827 research and development Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 239000002904 solvent Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

- TYHJXGDMRRJCRY-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) tin(4+) Chemical compound [O-2].[Zn+2].[Sn+4].[In+3] TYHJXGDMRRJCRY-UHFFFAOYSA-N 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Abstract

【解決手段】薄膜トランジスタは、基板と、基板上に形成されると共に、基板側からの不純物に対するバリア性と酸化物半導体層に対する還元性とを有する第1のバリア膜と、第1のバリア膜上の選択的な領域に形成されると共に、水素に対してバリア性を有する第2のバリア膜と、第2のバリア膜上に形成されると共に活性層として機能する第1部分と、第1のバリア膜上に形成されると共に第1部分よりも電気抵抗値の低い第2部分とを含む酸化物半導体層と、酸化物半導体層の第1部分の上に、ゲート絶縁膜を介して形成されたゲート電極と、酸化物半導体層の第2部分に電気的に接続されたソース電極またはドレイン電極とを備える。

【選択図】図1

Description

1.実施の形態(第1バリア膜(SiN)と酸化物半導体層の活性層との間に第2バリア膜(SiO2)を有するトップゲート型薄膜トランジスタの例)

2.適用例(表示装置,電子機器の例)

[構成]

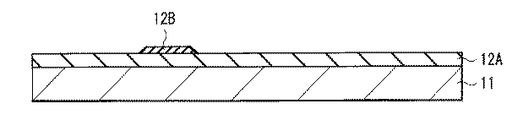

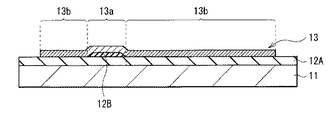

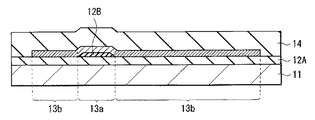

図1は、本開示の一の実施の形態に係る薄膜トランジスタ(トランジスタ10A)および保持容量(保持容量10B)の断面構成を表したものである。トランジスタ10Aは、例えばアクティブマトリクス型の有機ELディスプレイあるいは液晶ディスプレイなどの駆動素子として用いられ、いわゆるトップゲート構造を有する薄膜トランジスタである。

図3A〜図6は、トランジスタ10Aの製造方法を説明するための断面図である。トランジスタ10Aは、例えば次のようにして製造することができる。

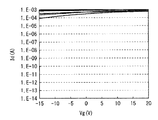

本実施の形態のトランジスタ10Aでは、基板11上に、第1バリア膜12Aが形成されると共に、この第1バリア膜12Aと酸化物半導体層13の第1部分13aとの間に、水素バリア性を有する第2バリア膜12Aが形成されている。第1バリア膜12Aにより、不純物による酸化物半導体層13全体の膜質劣化が抑制されると共に、酸化物半導体層の第2部分13bが選択的に低抵抗化されて形成される。つまり、本実施の形態では、第1バリア膜12Aが、基板11側からの不純物の浸入を防ぐバリアとして機能すると共に、酸化物半導体層13の所定の領域(第2部分13b)への水素供給源として機能する。

[表示装置]

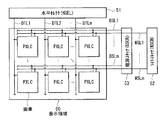

次に、上記実施の形態に係るトランジスタ10Aを適用した表示装置の全体構成および画素回路構成について説明する。図9は、有機ELディスプレイとして用いられる表示装置の周辺回路を含む全体構成を表すものである。このように、例えば基板11上には、有機EL素子を含む複数の画素PXLCがマトリクス状に配置されてなる表示領域50が形成され、この表示領域50の周辺に、信号線駆動回路としての水平セレクタ(HSEL)51と、走査線駆動回路としてのライトスキャナ(WSCN)52と、電源線駆動回路としての電源スキャナ(DSCN)53とが設けられている。但し、トランジスタ10Aは、ここで説明する有機ELディスプレイに限らず、他の表示装置、例えば液晶ディスプレイあるいは電子ペーパー等の様々なデバイスへ適用可能である。

以下、上記のようなトランジスタ10Aを用いた表示装置を搭載した電子機器の一例について説明する。電子機器としては、例えばテレビジョン装置,デジタルカメラ,ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラ等が挙げられる。言い換えると、上記表示装置は、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器に適用することが可能である。

図12は、テレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300が上記表示装置に相当する。

図13Aおよび図13Bは、デジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、この表示部420が上記表示装置に相当する。

図14は、ノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、この表示部530が上記表示装置に相当する。

図15は、ビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有している。この表示部640が上記表示装置に相当する。

図16Aおよび図16Bは、携帯電話機の外観を表したものである。この携帯電話機は、例えば上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そして、これらのうちのディスプレイ740またはサブディスプレイ750が、上記表示装置に相当する。

図17Aおよび図17Bは、スマートフォンの外観を表している。このスマートフォンは、例えば、表示部810および非表示部(筐体)820と、操作部830とを備えている。操作部830は、図17Aに示したように非表示部820の前面に設けられていてもよいし、図17Bに示したように上面に設けられていてもよい。

(1)

基板と、

前記基板上に形成されると共に、前記基板側からの不純物に対するバリア性と前記酸化物半導体層に対する還元性とを有する第1のバリア膜と、

前記第1のバリア膜上の選択的な領域に形成されると共に、水素に対してバリア性を有する第2のバリア膜と、

前記第2のバリア膜上に形成されると共に活性層として機能する第1部分と、前記第1のバリア膜上に形成されると共に前記第1部分よりも電気抵抗値の低い第2部分とを含む酸化物半導体層と、

前記酸化物半導体層の前記第1部分の上に、ゲート絶縁膜を介して形成されたゲート電極と、

前記酸化物半導体層の前記第2部分に電気的に接続されたソース電極またはドレイン電極と

を備えた薄膜トランジスタ。

(2)

前記第1のバリア膜は、窒化シリコンおよび酸窒化シリコンのうちの少なくとも1種を含み、

前記第2のバリア膜は、酸化シリコン、酸窒化シリコン、酸化アルミニウムおよび酸化チタンのうちの少なくとも1種を含む単層膜または積層膜である

上記(1)に記載の薄膜トランジスタ。

(3)

前記基板は、可撓性を有する樹脂材料から構成されている

上記(1)または(2)に記載の薄膜トランジスタ。

(4)

前記酸化物半導体層の前記第2部分は、前記第1のバリア膜に接して形成されている

上記(1)〜(3)のいずれかに記載の薄膜トランジスタ。

(5)

前記ゲート電極および前記ゲート絶縁膜は、互いに同一形状にパターニングされている

上記(1)〜(4)のいずれかに記載の薄膜トランジスタ。

(6)

前記酸化物半導体層の前記第2部分を利用して保持容量が形成されている

上記(1)〜(5)のいずれかに記載の薄膜トランジスタ。

(7)

前記ソース電極または前記ドレイン電極は、前記酸化物半導体層の前記第2部分の一部に対向して設けられている

上記(1)〜(6)のいずれかに記載の薄膜トランジスタ。

(8)

それぞれが薄膜トランジスタを含む複数の画素を有し、

前記薄膜トランジスタは、

基板と、

前記基板上に形成されると共に、前記基板側からの不純物に対するバリア性と前記酸化物半導体層に対する還元性とを有する第1のバリア膜と、

前記第1のバリア膜上の選択的な領域に形成されると共に、水素に対してバリア性を有する第2のバリア膜と、

前記第2のバリア膜上に形成されると共に活性層として機能する第1部分と、前記第1のバリア膜上に形成されると共に前記第1部分よりも電気抵抗値の低い第2部分とを含む酸化物半導体層と、

前記酸化物半導体層の前記第1部分の上に、ゲート絶縁膜を介して形成されたゲート電極と、

前記酸化物半導体層の前記第2部分に電気的に接続されたソース電極またはドレイン電極と

を備えた表示装置。

(9)

有機電界発光表示装置である

上記(8)に記載の表示装置。

(10)

それぞれが薄膜トランジスタを含む複数の画素を有する表示装置を備え、

前記薄膜トランジスタは、

基板と、

前記基板上に形成されると共に、前記基板側からの不純物に対するバリア性と前記酸化物半導体層に対する還元性とを有する第1のバリア膜と、

前記第1のバリア膜上の選択的な領域に形成されると共に、水素に対してバリア性を有する第2のバリア膜と、

前記第2のバリア膜上に形成されると共に活性層として機能する第1部分と、前記第1のバリア膜上に形成されると共に前記第1部分よりも電気抵抗値の低い第2部分とを含む酸化物半導体層と、

前記酸化物半導体層の前記第1部分の上に、ゲート絶縁膜を介して形成されたゲート電極と、

前記酸化物半導体層の前記第2部分に電気的に接続されたソース電極またはドレイン電極と

を備えた電子機器。

Claims (10)

- 基板と、

前記基板上に形成されると共に、前記基板側からの不純物に対するバリア性と前記酸化物半導体層に対する還元性とを有する第1のバリア膜と、

前記第1のバリア膜上の選択的な領域に形成されると共に、水素に対してバリア性を有する第2のバリア膜と、

前記第2のバリア膜上に形成されると共に活性層として機能する第1部分と、前記第1のバリア膜上に形成されると共に前記第1部分よりも電気抵抗値の低い第2部分とを含む酸化物半導体層と、

前記酸化物半導体層の前記第1部分の上に、ゲート絶縁膜を介して形成されたゲート電極と、

前記酸化物半導体層の前記第2部分に電気的に接続されたソース電極またはドレイン電極と

を備えた薄膜トランジスタ。 - 前記第1のバリア膜は、窒化シリコンおよび酸窒化シリコンのうちの少なくとも1種を含み、

前記第2のバリア膜は、酸化シリコン、酸窒化シリコン、酸化アルミニウムおよび酸化チタンのうちの少なくとも1種を含む単層膜または積層膜である

請求項1に記載の薄膜トランジスタ。 - 前記基板は、可撓性を有する樹脂材料から構成されている

請求項1に記載の薄膜トランジスタ。 - 前記酸化物半導体層の前記第2部分は、前記第1のバリア膜に接して形成されている

請求項1に記載の薄膜トランジスタ。 - 前記ゲート電極および前記ゲート絶縁膜は、互いに同一形状にパターニングされている

請求項1に記載の薄膜トランジスタ。 - 前記酸化物半導体層の前記第2部分を利用して保持容量が形成されている

請求項1に記載の薄膜トランジスタ。 - 前記ソース電極または前記ドレイン電極は、前記酸化物半導体層の前記第2部分の一部に対向して設けられている

請求項1に記載の薄膜トランジスタ。 - それぞれが薄膜トランジスタを含む複数の画素を有し、

前記薄膜トランジスタは、

基板と、

前記基板上に形成されると共に、前記基板側からの不純物に対するバリア性と前記酸化物半導体層に対する還元性とを有する第1のバリア膜と、

前記第1のバリア膜上の選択的な領域に形成されると共に、水素に対してバリア性を有する第2のバリア膜と、

前記第2のバリア膜上に形成されると共に活性層として機能する第1部分と、前記第1のバリア膜上に形成されると共に前記第1部分よりも電気抵抗値の低い第2部分とを含む酸化物半導体層と、

前記酸化物半導体層の前記第1部分の上に、ゲート絶縁膜を介して形成されたゲート電極と、

前記酸化物半導体層の前記第2部分に電気的に接続されたソース電極またはドレイン電極と

を備えた表示装置。 - 有機電界発光表示装置である

請求項8に記載の表示装置。 - それぞれが薄膜トランジスタを含む複数の画素を有する表示装置を備え、

前記薄膜トランジスタは、

基板と、

前記基板上に形成されると共に、前記基板側からの不純物に対するバリア性と前記酸化物半導体層に対する還元性とを有する第1のバリア膜と、

前記第1のバリア膜上の選択的な領域に形成されると共に、水素に対してバリア性を有する第2のバリア膜と、

前記第2のバリア膜上に形成されると共に活性層として機能する第1部分と、前記第1のバリア膜上に形成されると共に前記第1部分よりも電気抵抗値の低い第2部分とを含む酸化物半導体層と、

前記酸化物半導体層の前記第1部分の上に、ゲート絶縁膜を介して形成されたゲート電極と、

前記酸化物半導体層の前記第2部分に電気的に接続されたソース電極またはドレイン電極と

を備えた電子機器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013109773A JP2014229814A (ja) | 2013-05-24 | 2013-05-24 | 薄膜トランジスタ、表示装置および電子機器 |

| US14/273,847 US9053984B2 (en) | 2013-05-24 | 2014-05-09 | Thin-film transistor, display unit, and electronic apparatus |

| CN201410209127.4A CN104183647B (zh) | 2013-05-24 | 2014-05-16 | 薄膜晶体管、显示单元、以及电子设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013109773A JP2014229814A (ja) | 2013-05-24 | 2013-05-24 | 薄膜トランジスタ、表示装置および電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014229814A true JP2014229814A (ja) | 2014-12-08 |

| JP2014229814A5 JP2014229814A5 (ja) | 2015-08-06 |

Family

ID=51934793

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013109773A Pending JP2014229814A (ja) | 2013-05-24 | 2013-05-24 | 薄膜トランジスタ、表示装置および電子機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9053984B2 (ja) |

| JP (1) | JP2014229814A (ja) |

| CN (1) | CN104183647B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019012822A (ja) * | 2017-06-16 | 2019-01-24 | 株式会社半導体エネルギー研究所 | 半導体装置、および半導体装置の作製方法 |

| JP2021073716A (ja) * | 2015-01-26 | 2021-05-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110867469B (zh) * | 2014-03-17 | 2023-12-29 | 三星显示有限公司 | 有机el显示装置 |

| US9745645B2 (en) * | 2015-02-26 | 2017-08-29 | King Fahd University Of Petroleum And Minerals | Method of preparing silver nanoparticles and silver nanorings |

| CN106920754A (zh) * | 2017-02-17 | 2017-07-04 | 深圳市华星光电技术有限公司 | 一种薄膜晶体管及其制备方法 |

| CN106935659B (zh) * | 2017-05-11 | 2021-01-22 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制造方法、阵列基板以及显示装置 |

| CN112289813B (zh) * | 2020-10-29 | 2022-10-14 | 湖北长江新型显示产业创新中心有限公司 | 阵列基板、显示面板及显示装置 |

| CN113097289A (zh) * | 2021-03-30 | 2021-07-09 | 合肥维信诺科技有限公司 | 薄膜晶体管及其制备方法、阵列基板 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009075281A1 (ja) * | 2007-12-13 | 2009-06-18 | Idemitsu Kosan Co., Ltd. | 酸化物半導体を用いた電界効果型トランジスタ及びその製造方法 |

| JP2009272427A (ja) * | 2008-05-07 | 2009-11-19 | Canon Inc | 薄膜トランジスタ及びその製造方法 |

| JP2012049513A (ja) * | 2010-07-26 | 2012-03-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| JP2012160679A (ja) * | 2011-02-03 | 2012-08-23 | Sony Corp | 薄膜トランジスタ、表示装置および電子機器 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8059109B2 (en) * | 2005-05-20 | 2011-11-15 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic apparatus |

| KR101056250B1 (ko) * | 2009-10-21 | 2011-08-11 | 삼성모바일디스플레이주식회사 | 평판 표시 장치 및 그의 제조 방법 |

| JP2012015436A (ja) * | 2010-07-05 | 2012-01-19 | Sony Corp | 薄膜トランジスタおよび表示装置 |

| JP5636304B2 (ja) | 2011-02-08 | 2014-12-03 | 株式会社ジャパンディスプレイ | 薄膜トランジスタ回路基板及びその製造方法 |

| KR20140012693A (ko) * | 2011-03-01 | 2014-02-03 | 샤프 가부시키가이샤 | 박막 트랜지스터 및 그 제조 방법과 표시 장치 |

-

2013

- 2013-05-24 JP JP2013109773A patent/JP2014229814A/ja active Pending

-

2014

- 2014-05-09 US US14/273,847 patent/US9053984B2/en active Active

- 2014-05-16 CN CN201410209127.4A patent/CN104183647B/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009075281A1 (ja) * | 2007-12-13 | 2009-06-18 | Idemitsu Kosan Co., Ltd. | 酸化物半導体を用いた電界効果型トランジスタ及びその製造方法 |

| JP2009272427A (ja) * | 2008-05-07 | 2009-11-19 | Canon Inc | 薄膜トランジスタ及びその製造方法 |

| JP2012049513A (ja) * | 2010-07-26 | 2012-03-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| JP2012160679A (ja) * | 2011-02-03 | 2012-08-23 | Sony Corp | 薄膜トランジスタ、表示装置および電子機器 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021073716A (ja) * | 2015-01-26 | 2021-05-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP7112539B2 (ja) | 2015-01-26 | 2022-08-03 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2019012822A (ja) * | 2017-06-16 | 2019-01-24 | 株式会社半導体エネルギー研究所 | 半導体装置、および半導体装置の作製方法 |

| JP7094786B2 (ja) | 2017-06-16 | 2022-07-04 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US11626422B2 (en) | 2017-06-16 | 2023-04-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| US11943929B2 (en) | 2017-06-16 | 2024-03-26 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN104183647B (zh) | 2018-06-08 |

| US9053984B2 (en) | 2015-06-09 |

| US20140346499A1 (en) | 2014-11-27 |

| CN104183647A (zh) | 2014-12-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9721977B2 (en) | Display device and electronic unit | |

| JP5679143B2 (ja) | 薄膜トランジスタならびに表示装置および電子機器 | |

| US8748878B2 (en) | Thin film transistor, method of manufacturing the same, and display device | |

| JP6111398B2 (ja) | 表示装置および電子機器 | |

| JP5668917B2 (ja) | 薄膜トランジスタおよびその製造方法 | |

| US20110215328A1 (en) | Thin film transistor, method of manufacturing the thin film transistor, and display device | |

| JP5766481B2 (ja) | 表示装置および電子機器 | |

| US20120001167A1 (en) | Thin film transistor and display device | |

| JP6111458B2 (ja) | 半導体装置、表示装置および電子機器 | |

| US9053984B2 (en) | Thin-film transistor, display unit, and electronic apparatus | |

| JP2011222767A (ja) | 薄膜トランジスタならびに表示装置および電子機器 | |

| JP2012174723A (ja) | 薄膜トランジスタおよびその製造方法、並びに表示装置 | |

| US20150279871A1 (en) | Semiconductor device, display unit, and electronic apparatus | |

| JP6142136B2 (ja) | トランジスタの製造方法、表示装置の製造方法および電子機器の製造方法 | |

| JP2013211410A (ja) | 薄膜トランジスタおよびその製造方法並びに表示装置および電子機器 | |

| US8981368B2 (en) | Thin film transistor, method of manufacturing thin film transistor, display, and electronic apparatus | |

| JP2012204548A (ja) | 表示装置およびその製造方法 | |

| JP6019331B2 (ja) | トランジスタ、半導体装置、表示装置および電子機器、並びに半導体装置の製造方法 | |

| JP6019330B2 (ja) | 薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置および電子機器 | |

| JP2013080769A (ja) | 薄膜トランジスタならびに表示装置および電子機器 | |

| JP2013207015A (ja) | 半導体装置、表示装置および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20150327 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150617 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150617 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151001 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160630 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160712 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160810 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20161213 |