JP6019331B2 - トランジスタ、半導体装置、表示装置および電子機器、並びに半導体装置の製造方法 - Google Patents

トランジスタ、半導体装置、表示装置および電子機器、並びに半導体装置の製造方法 Download PDFInfo

- Publication number

- JP6019331B2 JP6019331B2 JP2012047586A JP2012047586A JP6019331B2 JP 6019331 B2 JP6019331 B2 JP 6019331B2 JP 2012047586 A JP2012047586 A JP 2012047586A JP 2012047586 A JP2012047586 A JP 2012047586A JP 6019331 B2 JP6019331 B2 JP 6019331B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- oxide semiconductor

- oxide

- gate electrode

- etching protective

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Thin Film Transistor (AREA)

Description

1.第1の実施の形態(酸化物半導体膜と酸化膜との間にチャネル保護膜を有する例:有機EL表示装置)

2.変形例1(酸化物半導体膜の側面とチャネル保護膜の側面とが揃っている例)

3.変形例2(酸化物半導体膜と保持容量素子の一方の電極とを接続する配線を有する例)

4.第2の実施の形態(液晶表示装置)

5.第3の実施の形態(電子ペーパー)

6.適用例

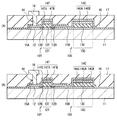

図1は本技術の第1の実施の形態に係る表示装置(表示装置1)の断面構成を表したも

のである。この表示装置1はアクティブマトリクス型の有機EL(Electroluminescence)表示装置であり、基板11上にトランジスタ10Tおよびトランジスタ10Tにより駆動される有機EL素子20をそれぞれ複数有している。図1には、一のトランジスタ10Tおよび有機EL素子20に対応する領域(サブピクセル)を示す。

基板11は、例えば、石英,ガラス,シリコンまたは樹脂(プラスチック)フィルムなどの板材により構成されている。後述のスパッタ法において、基板11を加熱することなく酸化物半導体膜12を成膜するため、安価な樹脂フィルムを用いることができる。樹脂材料としては、例えば、PET(ポリエチレンテレフタレート)またはPEN(ポリエチレンナフタレート)などが挙げられる。この他にも、目的に応じて、ステンレス鋼(SUS)などの金属基板を用いるようにしてもよい。

いる。ゲート電極14Tおよびゲート絶縁膜13Tは平面視で互いに同一形状を有してい

る。ゲート絶縁膜13Tは例えば厚みが300nm程度であり、シリコン酸化膜(SiO),シリコン窒化膜(SiN),シリコン窒化酸化膜(SiON)または酸化アルミニウム膜(AlO)などのうちの1種よりなる単層膜あるいはそれらのうちの2種以上よりなる積層膜により構成されている。ゲート絶縁膜13Tには酸化物半導体膜12を還元させにくい材料、例えば、シリコン酸化膜あるいは酸化アルミニウム膜を用いることが好ましい。

化物半導膜12(チャネル領域12T)中のキャリア密度を制御すると共に、電位を供給

す配線としての機能を有するものである。このゲート電極14Tは、例えばモリブデン(Mo),窒化モリブデニウム(MoN),チタン(Ti),窒化チタン(TiN),アルミニウム,銀(Ag),ネオジウム(Nd)および銅(Cu)のうちの1種からなる単体もしくはこれらの合金により構成されている。複数の単体または合金を用いた積層構造であってもよい。ゲート電極14Tは低抵抗な金属、例えば、アルミニウム,ネオジウムを含有するアルミニウム合金(Al−Nd)または銅等により構成することが好ましい。このような低抵抗な金属からなる層(低抵抗層14TA)に、例えばチタン,窒化チタン,モリブデンまたは窒化モリブデニウムからなる層(バリア層14TB)を積層させるようにしてもよい(図2(A))。2つのバリア層(バリア層14TB,14TC)の間に低抵抗層14TAを挟むようにしてもよい(図2(B))。バリア層14TB,14TCは、エッチングで使用される希フッ酸等の薬液に対する耐性が高いため、例えば、接続孔H1の形成時にこれを用いたウェッエッチングを行うことが可能となる。また、ゲート電極14TはITO等の透明導電膜により構成することも可能である。ゲート電極14Tの厚みは、例えば10nm〜500nmである。

保持容量素子10Cはトランジスタ10Tと共に基板11上に設けられ、例えば、後述の画素回路50Aにおいて電荷を保持する容量素子である。この保持容量素子10Cは、基板11側からトランジスタ10Tと共有のエッチング保護膜15B,容量絶縁膜13Cおよび上部電極14Cをこの順に有している。即ち、保持容量素子10Cの下部電極(一方の電極)はエッチング保護膜15Bの一部(電極領域15C)により構成されている。詳細は後述するが、これにより、容量値の印加電圧依存性をなくし、ゲート電圧の大きさに関わらず十分な容量を確保して表示特性を維持することができる。

有機EL素子20は、平坦化膜19上に設けられている。この有機EL素子20は平坦化膜19側から第1電極21、画素分離膜22、有機層23および第2電極24をこの順に有しており、素子保護層25により封止されている。素子保護層25上には熱硬化樹脂または紫外線硬化樹脂からなる接着層26を間にして封止用基板27が貼り合わされている。表示装置1は、有機層23で発生した光を基板11側から取り出すボトムエミッション方式(下面発光方式)であってもよく、封止用基板27側から取り出すトップエミッション方式(上面発光方式)であってもよい。

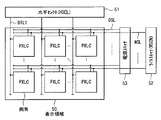

図5に示したように、表示装置1はこのような有機EL素子20を含む画素PXLCを複数有しており、画素PXLCは基板11上の表示領域50に例えばマトリクス状に配置されている。表示領域50の周辺には信号線駆動回路としての水平セレクタ(HSEL)51、走査線駆動回路としてのライトスキャナ(WSCN)52および電源線駆動回路としての電源スキャナ53が設けられている。

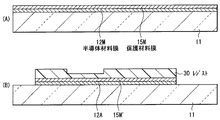

まず、図7(A)に示したように、基板11上に上述した材料よりなる酸化物半導体膜12を形成する。具体的には、まず基板11の全面にわたって、例えばスパッタリング法により、酸化物半導体材料膜(図示せず)を例えば50nm程度の厚みで成膜する。この際、ターゲットとしては、成膜対象の酸化物半導体と同一組成のセラミックを用いる。また、酸化物半導体中のキャリア濃度は、スパッタリングの際の酸素分圧に大きく依存するので、所望のトランジスタ特性が得られるように酸素分圧を制御する。酸化物半導体膜12を上述の酸化インジウムスズ亜鉛または結晶性材料により構成しておくと、後述のエッチング保護膜15A,15B、ゲート絶縁膜13Tそれぞれのエッチング工程において、容易にエッチング選択性を向上させることができる。次いで、例えばフォトリソグラフィおよびエッチングにより、成膜した酸化物半導体材料膜を所定の形状にパターニングする。その際、リン酸、硝酸および酢酸の混合液を用いたウェットエッチングにより加工することが好ましい。リン酸、硝酸および酢酸の混合液は、下地との選択比を十分に大きくすることが可能であり、比較的容易に加工が可能となる。

続いて、層間絶縁膜17およびソース・ドレイン電極18を覆うように、上述した材料よりなる平坦化膜19を、例えばスピンコート法やスリットコート法により成膜し、ソース・ドレイン電極18に対向する領域の一部に接続孔H2を形成する。

次いで、この平坦化膜19上に、有機EL素子20を形成する。具体的には、平坦化膜19上に、接続孔H2を埋め込むように、上述した材料よりなる第1電極21を例えばスパッタリング法により成膜した後、フォトリソグラフィおよびエッチングによりパターニングする。この後、第1電極21上に開口を有する画素分離膜22を形成した後、有機層23を例えば真空蒸着法により成膜する。続いて、有機層23上に、上述した材料よりなる第2電極24を例えばスパッタリング法により形成する。次いで、この第2電極24上に保護層25を例えばCVD法により成膜した後、この保護層25上に、接着層26を用いて封止用基板27を貼り合わせる。以上により、図1に示した表示装置1を完成する。

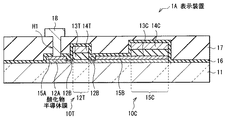

図14は、上記第1の実施の形態の変形例1に係る表示装置(表示装置1A)のトランジスタ10Tおよび保持容量素子10Cの断面構成を表したものである。この表示装置1Aでは、トランジスタ10Tの酸化物半導体膜(酸化物半導体膜12A)が保持容量素子10Cと基板11との間に延在している。この点を除き、表示装置1Aは上記実施の形態の表示装置1と同様の構成を有し、その作用および効果も同様である。

図17は、上記第1の実施の形態の変形例2に係る表示装置(表示装置1B)のトランジスタ10Tおよび保持容量素子10Cの断面構成を表したものである。この表示装置1Bは、酸化物半導体膜12の低抵抗領域12Bと電極領域15Cを有するエッチング保護膜15Bとを電気的に接続するための配線31を有するものである。この点を除き、表示装置1Bは上記実施の形態の表示装置1と同様の構成を有し、その作用および効果も同様である。

図18は、本技術の第2の実施の形態に係る表示装置(表示装置2)の断面構成を表したものである。この表示装置2は、上記第1の実施の形態(表示装置1)の有機EL素子20に代えて液晶表示素子40を有するものである。この点を除き、表示装置2は上記実施の形態の表示装置1と同様の構成を有し、その作用および効果も同様である。

図19は、本技術の第3の実施の形態に係る表示装置(表示装置3)の断面構成を表したものである。この表示装置3は所謂電子ペーパーであり、表示装置1の有機EL素子20に代えて電気泳動型表示素子50を有している。この点を除き、表示装置3は上記実施の形態の表示装置1と同様の構成を有し、その作用および効果も同様である。

以下、上記のような表示装置(表示装置1,1A,1B,2,3)の電子機器への適用例について説明する。電子機器としては、例えばテレビジョン装置,デジタルカメラ,ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラ等が挙げられる。言い換えると、上記表示装置は、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器に適用することが可能である。

上記表示装置は、例えば図20に示したようなモジュールとして、後述の適用例1〜7

などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板11の一辺に、封止用基板27または対向基板45,54から露出した領域61を設け、この露出した領域61に、水平セレクタ51、ライトスキャナ52および電源スキャナ53の配線を延長して外部接続端子(図示せず)を形成したものである。この外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)62が設けられていてもよい。

図21(A)および図21(B)はそれぞれ、上記実施の形態の表示装置が適用される電子ブックの外観を表したものである。この電子ブックは、例えば、表示部210および非表示部220を有しており、この表示部210が上記実施の形態の表示装置により構成されている。

図22は、上記実施の形態の表示装置が適用されるスマートフォンの外観を表したものである。このスマートフォンは、例えば、表示部230および非表示部240を有しており、この表示部230が上記実施の形態の表示装置により構成されている。

図23は、上記実施の形態の表示装置が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記実施の形態の表示装置により構成されている。

図24は、上記実施の形態の表示装置が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、この表示部420が上記実施の形態の表示装置により構成されている。

図25は、上記実施の形態の表示装置が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、この表示部530が上記実施の形態の表示装置により構成されている。

図26は、上記実施の形態の表示装置が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有している。そして、この表示部640が上記実施の形態の表示装置により構成されている。

図27は、上記実施の形態の表示装置が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そして、これらのうちのディスプレイ740またはサブディスプレイ750が、上記実施の形態の表示装置により構成されている。

(1)ゲート電極と、前記ゲート電極に対向してチャネル領域を有する酸化物半導体膜と 、少なくとも一部が前記酸化物半導体膜に接するエッチング保護膜と、前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜と、前記酸化膜の貫通孔を介して前記エッチング保護膜に電気的に接続されたソース・ドレイン電極とを備えたトランジスタ。

(2)前記酸化物半導体膜の前記酸化膜と接する部分に低抵抗領域を有する前記(1)記載のトランジスタ。

(3)前記ゲート電極を間にして一対の前記エッチング保護膜を有し、前記一対のエッチング保護膜の対向面の位置と前記低抵抗領域の端部の位置とが一致している前記(2)記載のトランジスタ。

(4)前記酸化物半導体膜に対向する位置に前記貫通孔を有する前記(1)乃至(3)のうちいずれか1つに記載のトランジスタ。

(5)前記酸化膜と前記ソース・ドレイン電極との間に保護膜を有し、前記貫通孔は、前記酸化膜と共に前記保護膜を貫通する前記(1)乃至(4)のうちいずれか1つに記載のトランジスタ。

(6)前記エッチング保護膜は、ドーパントとしてリン,ボロンまたはヒ素を含有するシリコンまたはゲルマニウムにより構成されている前記(1)乃至(5)のうちいずれか1つに記載のトランジスタ。

(7)前記エッチング保護膜は、モリブデン膜,ネオジウムを含むアルミニウム膜およびITO(酸化インジウムスズ)のうちのいずれか1つを含む前記(1)乃至(5)のうちいずれか1つに記載のトランジスタ。

(8)前記酸化物半導体膜は酸化インジウムスズ亜鉛または結晶性材料により構成されている前記(1)乃至(7)のうちいずれか1つに記載のトランジスタ。

(9)前記エッチング保護膜は前記酸化物半導体膜の外側に拡幅し、前記酸化物半導体膜の外側に対向する位置に前記貫通孔を有する前記(1)または(2)記載のトランジスタ。

(10)前記酸化膜は、酸化アルミニウムを含む前記(1)乃至(9)のうちいずれか1つに記載のトランジスタ。

(11)トランジスタを備え、前記トランジスタは、ゲート電極と、前記ゲート電極に対向してチャネル領域を有する酸化物半導体膜と、少なくとも一部が前記酸化物半導体膜に接するエッチング保護膜と、前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜と、前記酸化膜の貫通孔を介して前記エッチング保護膜に電気的に接続されたソース・ドレイン電極とを有する半導体装置。

(12)保持容量素子を有し、前記エッチング保護膜の一部が前記保持容量素子の一方の電極を構成する前記(11)記載の半導体装置。

(13)前記酸化物半導体膜の前記酸化膜と接する部分に設けられた低抵抗領域と、前記酸化物半導体膜の低抵抗領域と前記保持容量素子の一方の電極とを電気的に接続する配線とを有する前記(12)記載の半導体装置。

(14)前記酸化物半導体膜は前記保持容量素子の一方の電極と接し、前記酸化物半導体膜の側面の位置と前記エッチング保護膜の側面の位置とが一致している前記(12)または(13)記載の半導体装置。

(15)表示素子および前記表示素子を駆動するトランジスタを備え、前記トランジスタは、ゲート電極と、前記ゲート電極に対向してチャネル領域を有する酸化物半導体膜と、少なくとも一部が前記酸化物半導体膜に接するエッチング保護膜と、前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜と、前記酸化膜の貫通孔を介して前記エッチング保護膜に電気的に接続されたソース・ドレイン電極とを有する表示装置。

(16)前記表示素子として有機EL(Electroluminescence)素子を有する前記(15)記載の表示装置。

(17)表示素子および前記表示素子を駆動するトランジスタを有する表示装置を備え、前記トランジスタは、ゲート電極と、前記ゲート電極に対向してチャネル領域を有する酸化物半導体膜と、少なくとも一部が前記酸化物半導体膜に接するエッチング保護膜と、前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜と、前記酸化膜の貫通孔を介して前記エッチング保護膜に電気的に接続されたソース・ドレイン電極とを有する電子機器。

(18)トランジスタを形成する工程を含み、前記トランジスタを形成する工程は、チャネル領域を有する酸化物半導体膜を形成する工程と、前記酸化物半導体膜に接するエッチング保護膜を形成する工程と、前記酸化物半導体膜のチャネル領域に対向してゲート電極を形成する工程と、前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜を形成する工程と、前記酸化膜に貫通孔を設け、前記貫通孔を介してソース・ドレイン電極を前記エッチング保護膜に電気的に接続する工程とを含む半導体装置の製造方法。

(19)保持容量素子を形成する工程を有し、前記エッチング保護膜を形成する工程で、前記保持容量素子の一方の電極を前記エッチング保護膜の一部により形成する前記(1

8)記載の半導体装置の製造方法。

(20)ハーフトーンマスクを用いることにより、一のフォトリソグラフィ工程で前記酸化物半導体膜および前記エッチング保護膜を形成する前記(19)記載の半導体装置の製造方法。

Claims (17)

- トランジスタおよび保持容量素子を備え、

前記トランジスタは、

ゲート電極と、

前記ゲート電極に対向してチャネル領域を有する酸化物半導体膜と、

少なくとも一部が前記酸化物半導体膜に接するエッチング保護膜と、

前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜と、

前記酸化膜の貫通孔を介して前記エッチング保護膜に電気的に接続されたソース・ドレイン電極とを有し、

前記保持容量素子の一方の電極は、前記エッチング保護膜の一部により構成され、前記保持容量素子の他方の電極は、前記ゲート電極と同一材料により構成されている

半導体装置。 - 前記酸化物半導体膜の前記酸化膜と接する部分に低抵抗領域を有する

請求項1記載の半導体装置。 - 前記ゲート電極を間にして一対の前記エッチング保護膜を有し、

前記一対のエッチング保護膜の対向面の位置と前記低抵抗領域の端部の位置とが一致している

請求項2記載の半導体装置。 - 前記酸化物半導体膜に対向する位置に前記貫通孔を有する

請求項1乃至3のうちいずれか1つ記載の半導体装置。 - 前記酸化膜と前記ソース・ドレイン電極との間に保護膜を有し、

前記貫通孔は、前記酸化膜と共に前記保護膜を貫通する

請求項1乃至4のうちいずれか1つ記載の半導体装置。 - 前記エッチング保護膜は、ドーパントとしてリン,ボロンまたはヒ素を含有するシリコンまたはゲルマニウムにより構成されている

請求項1乃至5のうちいずれか1つ記載の半導体装置。 - 前記エッチング保護膜は、モリブデン膜,ネオジウムを含むアルミニウム膜およびITO(酸化インジウムスズ)のうちのいずれか1つを含む

請求項1乃至5のうちいずれか1つ記載の半導体装置。 - 前記酸化物半導体膜は酸化インジウムスズ亜鉛または結晶性材料により構成されている

請求項1乃至7のうちいずれか1つ記載の半導体装置。 - 前記エッチング保護膜は前記酸化物半導体膜の外側に拡幅し、

前記酸化物半導体膜の外側に対向する位置に前記貫通孔を有する

請求項1乃至3のうちいずれか1つ記載の半導体装置。 - 前記酸化膜は、酸化アルミニウムを含む

請求項1乃至9のうちいずれか1つ記載の半導体装置。 - 前記酸化物半導体膜の前記酸化膜と接する部分に設けられた低抵抗領域と、

前記酸化物半導体膜の低抵抗領域と前記保持容量素子の一方の電極とを電気的に接続する配線とを有する

請求項1乃至10のうちいずれか1つ記載の半導体装置。 - 前記酸化物半導体膜は前記保持容量素子の一方の電極に接し、

前記酸化物半導体膜の側面の位置と前記エッチング保護膜の側面の位置とが一致している

請求項1乃至8のうちいずれか1つ記載の半導体装置。 - 表示素子、前記表示素子を駆動するトランジスタおよび保持容量素子を備え、

前記トランジスタは、

ゲート電極と、

前記ゲート電極に対向してチャネル領域を有する酸化物半導体膜と、

少なくとも一部が前記酸化物半導体膜に接するエッチング保護膜と、

前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜と、

前記酸化膜の貫通孔を介して前記エッチング保護膜に電気的に接続されたソース・ドレイン電極とを有し、

前記保持容量素子の一方の電極は、前記エッチング保護膜の一部により構成され、前記保持容量素子の他方の電極は、前記ゲート電極と同一材料により構成されている

表示装置。 - 前記表示素子として有機EL(Electroluminescence)素子を有する

請求項13記載の表示装置。 - 表示素子、前記表示素子を駆動するトランジスタおよび保持容量素子を有する表示装置を備え、

前記トランジスタは、

ゲート電極と、

前記ゲート電極に対向してチャネル領域を有する酸化物半導体膜と、

少なくとも一部が前記酸化物半導体膜に接するエッチング保護膜と、

前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜と、

前記酸化膜の貫通孔を介して前記エッチング保護膜に電気的に接続されたソース・ドレイン電極とを有し、

前記保持容量素子の一方の電極は、前記エッチング保護膜の一部により構成され、前記保持容量素子の他方の電極は、前記ゲート電極と同一材料により構成されている

電子機器。 - トランジスタおよび保持容量素子を形成する工程を含み、

前記トランジスタを形成する工程は、

チャネル領域を有する酸化物半導体膜を形成する工程と、

前記酸化物半導体膜に接するエッチング保護膜を形成する工程と、

前記酸化物半導体膜のチャネル領域に対向してゲート電極を形成する工程と、

前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜を形成する工程と、

前記酸化膜に貫通孔を設け、前記貫通孔を介してソース・ドレイン電極を前記エッチング保護膜に電気的に接続する工程とを含み、

前記保持容量素子の一方の電極を、前記エッチング保護膜の一部により形成し、前記保持容量素子の他方の電極を、前記ゲート電極と同一材料により形成する

半導体装置の製造方法。 - トランジスタおよび保持容量素子を形成する工程を含み、

前記トランジスタを形成する工程は、

チャネル領域を有する酸化物半導体膜を形成する工程と、

前記酸化物半導体膜に接するエッチング保護膜を形成する工程と、

前記酸化物半導体膜のチャネル領域に対向してゲート電極を形成する工程と、

前記ゲート電極および前記エッチング保護膜を覆うと共に前記ゲート電極と前記エッチング保護膜との間で前記酸化物半導体膜に接する酸化膜を形成する工程と、

前記酸化膜に貫通孔を設け、前記貫通孔を介してソース・ドレイン電極を前記エッチング保護膜に電気的に接続する工程とを含み、

前記保持容量素子の一方の電極を前記エッチング保護膜の一部により形成し、

ハーフトーンマスクを用いることにより、一のフォトリソグラフィ工程で前記酸化物半導体膜および前記エッチング保護膜を形成する

半導体装置の製造方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012047586A JP6019331B2 (ja) | 2012-03-05 | 2012-03-05 | トランジスタ、半導体装置、表示装置および電子機器、並びに半導体装置の製造方法 |

| TW102103204A TW201338173A (zh) | 2012-02-28 | 2013-01-28 | 電晶體、製造電晶體之方法、顯示裝置及電子機器 |

| KR1020130016903A KR20130098906A (ko) | 2012-02-28 | 2013-02-18 | 트랜지스터, 트랜지스터 제조 방법, 반도체 장치 및 반도체 장치 제조 방법, 표시 장치, 및 전자 기기 |

| US13/770,201 US8883571B2 (en) | 2012-02-28 | 2013-02-19 | Transistor, method of manufacturing the transistor, semiconductor unit, method of manufacturing the semiconductor unit, display, and electronic apparatus |

| CN2013100558210A CN103295909A (zh) | 2012-02-28 | 2013-02-21 | 晶体管及其制造方法、半导体单元及其制造方法、显示器 |

| US14/530,943 US9276120B2 (en) | 2012-02-28 | 2014-11-03 | Transistor, method of manufacturing the transistor, semiconductor unit, method of manufacturing the semiconductor unit, display, and electronic apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012047586A JP6019331B2 (ja) | 2012-03-05 | 2012-03-05 | トランジスタ、半導体装置、表示装置および電子機器、並びに半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013183111A JP2013183111A (ja) | 2013-09-12 |

| JP6019331B2 true JP6019331B2 (ja) | 2016-11-02 |

Family

ID=49273538

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012047586A Active JP6019331B2 (ja) | 2012-02-28 | 2012-03-05 | トランジスタ、半導体装置、表示装置および電子機器、並びに半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6019331B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015056566A (ja) * | 2013-09-13 | 2015-03-23 | エルジー ディスプレイ カンパニー リミテッド | 薄膜トランジスタ、表示装置用電極基板およびそれらの製造方法 |

| TWI663726B (zh) * | 2014-05-30 | 2019-06-21 | Semiconductor Energy Laboratory Co., Ltd. | 半導體裝置、模組及電子裝置 |

| JP6539873B2 (ja) * | 2016-03-16 | 2019-07-10 | 株式会社Joled | 薄膜トランジスタ、及び薄膜トランジスタを備えた表示装置 |

| WO2018056117A1 (ja) * | 2016-09-20 | 2018-03-29 | シャープ株式会社 | 半導体装置および表示装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008218960A (ja) * | 2007-02-08 | 2008-09-18 | Mitsubishi Electric Corp | 薄膜トランジスタ装置、その製造方法、及び表示装置 |

| KR101065407B1 (ko) * | 2009-08-25 | 2011-09-16 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| JP5708910B2 (ja) * | 2010-03-30 | 2015-04-30 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法、並びに表示装置 |

| JP6005401B2 (ja) * | 2011-06-10 | 2016-10-12 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

-

2012

- 2012-03-05 JP JP2012047586A patent/JP6019331B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013183111A (ja) | 2013-09-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6111398B2 (ja) | 表示装置および電子機器 | |

| JP6019329B2 (ja) | 表示装置および電子機器 | |

| US9276120B2 (en) | Transistor, method of manufacturing the transistor, semiconductor unit, method of manufacturing the semiconductor unit, display, and electronic apparatus | |

| JP6561386B2 (ja) | トランジスタ、表示装置および電子機器 | |

| JP5766481B2 (ja) | 表示装置および電子機器 | |

| JP6111458B2 (ja) | 半導体装置、表示装置および電子機器 | |

| JP2015108731A (ja) | 半導体装置およびその製造方法、並びに表示装置および電子機器 | |

| JP6142136B2 (ja) | トランジスタの製造方法、表示装置の製造方法および電子機器の製造方法 | |

| JP2014093433A (ja) | 半導体装置、表示装置および電子機器 | |

| US20150179681A1 (en) | Semiconductor device, method of manufacturing the same, display unit, and electronic apparatus | |

| JP2016100585A (ja) | 半導体装置およびその製造方法、ならびに表示装置および電子機器 | |

| JP6019331B2 (ja) | トランジスタ、半導体装置、表示装置および電子機器、並びに半導体装置の製造方法 | |

| JP2013207015A (ja) | 半導体装置、表示装置および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150128 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20150327 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160223 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160414 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160823 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160826 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6019331 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S303 | Written request for registration of pledge or change of pledge |

Free format text: JAPANESE INTERMEDIATE CODE: R316303 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S803 | Written request for registration of cancellation of provisional registration |

Free format text: JAPANESE INTERMEDIATE CODE: R316803 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |