JP2010516063A - 集積回路用アンダーフィルアンカー構造 - Google Patents

集積回路用アンダーフィルアンカー構造 Download PDFInfo

- Publication number

- JP2010516063A JP2010516063A JP2009546014A JP2009546014A JP2010516063A JP 2010516063 A JP2010516063 A JP 2010516063A JP 2009546014 A JP2009546014 A JP 2009546014A JP 2009546014 A JP2009546014 A JP 2009546014A JP 2010516063 A JP2010516063 A JP 2010516063A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- die

- anchor structure

- underfill

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H10W74/10—

-

- H10W74/012—

-

- H10W74/01—

-

- H10W74/127—

-

- H10W74/15—

-

- H10W72/856—

Landscapes

- Wire Bonding (AREA)

Abstract

ダイと絶縁膜とを備えた集積回路製品を提供する。絶縁膜はダイに動作可能に結合している。絶縁膜は複数のバンプ開口部を含んでいる。絶縁膜はアンダーフィルアンカー構造も含んでいる。斯かる集積回路製品の製造方法も提供する。

Description

本発明は一般に半導体製造技術に関し、特に、ダイの絶縁膜を別の材料に付着させるための方法および装置に関する。

フリップチップ(flip-chip)とは一般的にはダイを“うつぶせにして(表を下にして)”基板(例えばキャリア)上に直に取り付けた形の半導体素子である。電気接続はダイの表面に付着した導電性バンプによって実現される。マウントの際、チップは、バンプがそれぞれの目標位置に配置された基板上で反転、つまりフリップされる(これが“フリップチップ”の由来である)。フリップチップは結線を必要としないことから一般的には従来型チップよりも小型である。

図1Aおよび図1Bに先行技術によるフリップチップ10の一部分を示す。図1Aはフリップチップ10の一部分の例示的な断面図である。図1Bはフリップチップ10の一部分の例示的な平面図である。フリップチップ10は、ダイ12、絶縁膜14、UBM(under bump metal)16、導電性バンプ18、アンダーフィル材料20、および基板22を含む。ダイ12は電子回路を含むことがある。絶縁膜14はダイ12に付加される誘電材料(一般的にはポリイミドその他の材料)である。絶縁膜14は各導電性バンプ18のバンプ開口部24を含む。また絶縁膜14は応力緩衝膜(stress buffer)、平坦化媒体(planarizing medium)、パッシベーション膜(passivation layer)としての機能を果たす。

導電性バンプ18はダイ12に電気的に結合しており、ダイ12から基板22への電気接点を提供する。より具体的には、UBM16はバンプ開口部24を通して(貫通して)ダイ12に動作可能に(operatively)結合しており、導電性バンプ18はUBM16に動作可能に結合している。導電性バンプ18は基板22にも動作可能に結合している。

アンダーフィル材料20は、一般的には非導電性接着剤で、絶縁膜14と基板22との間の間隙を埋めるために使用される。アンダーフィル材料20は絶縁膜14と基板22に接着する。またアンダーフィル材料20は導電性バンプ18をダイ12と基板22との間の熱膨張の違いから保護する。アンダーフィル材料20はフリップチップ10を、湿気、イオン性汚染物質、放射線、熱的および機械的状態(例えば衝撃や振動など)といった敵性動作環境からも保護する役割を果たす。

フリップチップ10が応力を受けると、絶縁膜14とアンダーフィル材料20との間の接着結合(状態)が弱まる可能性がある。接着結合が弱まると絶縁膜14とアンダーフィル材料20との間に望ましくない層間剥離が生じる結果になりかねない。

この問題を克服する試みに用いられる1つの方法として、絶縁膜14の表面26をプラズマエッチングその他の適切な方法によって表面処理することが挙げられる。表面26を表面処理してサブミクロンの溝その他の形状をもたらすことにより絶縁膜の表面部分の粗さが増す結果となり、それが絶縁膜14をアンダーフィル材料20に接着する助けになる。しかしながら、この方法は或る応力条件下ではまだ層間剥離を起こしやすい。

別の方法では、アンダーフィル材料20の接着力は結合力を高めるように変えられることがある。しかしながら、この方法もまだ接着面結合に依存しており、或る応力条件下ではまだ層間剥離を起こしやすい。

さらに別の方法では、製造段階において洗浄工程を追加することにより絶縁膜14の表面26が洗浄されることがある。しかしながら、この方法はフリップチップ10の製造コストを増大させかねない。その上、この方法もまだ接着面結合に依存しており、或る応力条件下ではまだ層間剥離を起こしやすい。

以上のことから、絶縁膜がアンダーフィル材料に改良された方法で付着する集積回路を提供することが何よりも望まれている。

本発明の理解をより容易にするため、以下、添付図面を参照しながら本発明の実施形態を詳細に説明する。添付図面の中では類似の要素には類似の符号が付されている。

一例において、集積回路製品(IC(integrated circuit)製品)はダイと絶縁膜を含む。絶縁膜はダイに動作可能に結合している。絶縁膜は複数のバンプ開口部を含む。絶縁膜はアンダーフィルアンカー構造(underfill anchor structure)も含む。アンダーフィルアンカー構造は、後述するように位置決め可能な(locatable)開口部/突起構造部によって定められる。それらは、マスキング技術、エッチング技術その他の適切な技術によって位置決め可能である。位置決め可能な開口部/突起部は、数ミクロンの深さを持つ。アンダーフィルアンカー構造は、適切な位置に設定されるとともに所望のサイズおよび形状(shape and configuration)を持つように指定された開口および/または突起構造部を含む。例えば、それらは円錐形や円筒形その他の所望の適切な形状を持つ開口部でありうる。他の利点として、アンダーフィルアンカー構造は、表面粗化技術と比較して、アンカーリングメカニズムの整合的な位置と形状を提供することによって改善されたクォリティが得られる定義可能な構造である。アンカー構造は層間剥離を低減するのにも役立つ可能性がある。他の利点は当業者であれば認識されるであろう。

一例において、集積回路製品(IC製品)は、アンダーフィルアンカー構造に機械的に付着したアンダーフィル材料を含む。

一例において、アンダーフィルアンカー構造は、絶縁膜によって画定される少なくとも1つの開口部(aperture)を含む。別の例では、アンダーフィルアンカー構造は、突起部(protrusion)または陥凹部(recess)を含む。

一例において、集積回路製品(IC製品)は、ダイと絶縁膜との間に動作可能に結合したダミー材料(dummy material)を含む。ダミー材料は、アンダーフィルアンカー構造を画定する。

一例において、アンダーフィルアンカー構造は、絶縁膜の外周(perimeter)の少なくとも一部分に沿って設定される。別の例では、アンダーフィルアンカー構造は、複数のバンプ開口部の周りに(取り囲むように)設定される。

一例において、集積回路製品(IC製品)の製造方法は、ダイを提供する工程と、絶縁膜をダイに付加する工程とを含む。絶縁膜は、複数のバンプ開口部(bump apertures)を含む。絶縁膜は、アンダーフィルアンカー構造も含む。

一例において、複数のバンプ開口部および/またはアンダーフィルアンカー構造は、絶縁膜の一部を取り除くことによって形成される。別の例では、絶縁膜の該一部は、複数のバンプ開口部および/またはアンカー構造を画定するマスクを絶縁膜に適用することによって取り除かれる。マスクと絶縁膜とに電磁放射線が照射される。そして、絶縁膜は、現像され、硬化される。マスクによって絶縁膜の電磁放射線が照射されなかった部分が除去される。

一例において、アンダーフィルアンカー構造は、絶縁膜によって画定される少なくとも1つの開口部を含む。別の例では、アンダーフィルアンカー構造は、突起部または陥凹部を含む。

一例において、アンダーフィルアンカー構造は、絶縁膜の外周の少なくとも一部分に沿って設定される。別の例では、アンダーフィルアンカー構造は、複数のバンプ開口部の周りに(取り囲むように)設定される。

一例において、絶縁膜の付加に先立って、ダミー材料がダイ表面に動作可能に結合される。ダミー材料は、アンダーフィルアンカー構造を画定する。

一例において、複数の導電性バンプが、複数のバンプ開口部を通してダイに動作可能に結合される。複数の導電性バンプに基板が動作可能に結合される。ダイと基板との間の間隙がアンダーフィル材料で充填される。アンダーフィル材料は、アンダーフィルアンカー構造に機械的に付着している。

一例において、集積回路製品(IC製品)は、ダイ、絶縁膜、複数の導電性バンプ、基板、およびアンダーフィル材料を含む。絶縁膜はダイに動作可能に結合している。絶縁膜は、複数のバンプ開口部とアンダーフィルアンカー構造とを含む。複数の導電性バンプは、複数のバンプ開口部を通してダイに動作可能に結合している。基板は、複数の導電性バンプに動作可能に結合している。アンダーフィル材料は、ダイと基板との間の間隙を埋めている。アンダーフィル材料は、アンダーフィルアンカー構造に機械的に付着している。

一例において、アンダーフィルアンカー構造は、絶縁膜によって画定される少なくとも1つの開口部を含む。別の例では、アンダーフィルアンカー構造は、突起部または陥凹部を含む。

一例において、アンダーフィルアンカー構造は、絶縁膜の外周の少なくとも一部分に沿って設定される。別の例では、アンダーフィルアンカー構造は、複数のバンプ開口部の周りに(取り囲むように)設定される。

一例において、デバイスは集積回路製品(IC製品)を含む。集積回路製品は、ダイ、絶縁膜、複数の導電性バンプ、基板、およびアンダーフィル材料を含む。絶縁膜はダイに動作可能に結合している。絶縁膜は、複数のバンプ開口部とアンダーフィルアンカー構造を含む。複数の導電性バンプは、複数のバンプ開口部を通してダイに動作可能に結合している。基板は、複数の導電性バンプに動作可能に結合している。アンダーフィル材料は、ダイと基板との間の間隙を埋めている。アンダーフィル材料は、アンダーフィルアンカー構造に機械的に付着している。

一例において、集積回路製品(IC製品)にディスプレイが動作可能に結合している。ダイはプロセッサを含む。

ここで使用される、モジュール、回路および/またはステージという用語は、限定はされないが、1以上のソフトウェアまたはファームウェアプログラムを実行する1以上のプロセッサ(例えば、コア(cores)、共有、専用、または一群のプロセッサ(例えば、限定はされないが、マイクロプロセッサ、グラフィックプロセッサ、DSP、または中央処理装置など))およびメモリ、組み合わせ論理回路、アナログ・デジタル回路、および/または記述される機能性を実現する他の適切なコンポーネントを含む任意の適切な電子回路を含みうる。

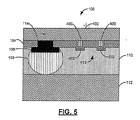

図2は、本発明の実施の一形態によるフリップチップ100の例示的な断面図である。フリップチップ100は、ダイ102、絶縁膜104、UBM(under bump metal)106、導電性バンプ108、アンダーフィル材料110、および基板112を含む。ダイ102、絶縁膜104、UBM106、および導電性バンプ108は、しばしばまとめてバンプ付ダイ(bumped die)と呼ばれる。

ダイ102は、1以上の電子回路を含みうる。絶縁膜104は、ダイ102に付加される誘電材料(誘電体)であり、一般的にはポリイミド(polymide)である。一部の態様では、絶縁膜104は5〜6ミクロンの厚みがある。また、絶縁膜104は、応力緩衝膜(stress buffer)、平坦化媒体(planarizing medium)、パッシベーション膜(passivation layer)としての機能を果たす。絶縁膜104は、バンプ開口部114とアンカー構造116とを含む。アンカー構造116は、絶縁膜104によって画定される開口部118を含みうる。

例えば、Sn/Pb共晶バンプその他の既知の材料から成る導電性バンプ108は、ダイ102と基板112とに動作可能に結合している。より具体的には。UBM106は、既知の技術を用いてバンプ開口部114を通してダイ102に結合しており、導電性バンプ108は、当該分野で周知のようにUBM106に結合している。

アンダーフィル材料110は、一般的には非導電性接着剤、例えばNamics8439などであり、絶縁膜104と基板112との間の間隙を埋めるために使用される。アンダーフィル材料110は、ダイ102と基板112との間の熱膨張の違いから導電性バンプ108を保護する。アンダーフィル材料110は、湿気、イオン性汚染物質、放射線、熱的および機械的状態(例えば、衝撃や振動など)といった厳しい動作環境からもフリップチップ10を保護する役割を果たす。

アンダーフィル材料110を絶縁膜104に付着する。より具体的には、アンカー構造116は、アンダーフィル材料110に機械的に付着して機械的なロックを生み出す。この機械的なロックに加えて、絶縁膜104とアンダーフィル材料110とは、アンダーフィル材料からの接着結合によっても付着する。機械的なロックと接着結合とを組み合わせることによって、フリップチップ100は、従来のフリップチップよりも強度が増した構造を持ち、層間剥離が起こりにくくなっている。

次に、図3は、(図2の)フリップチップ102の例示的な平面図を示す。一部の態様では、絶縁膜104の側縁部200は、ダイ102の側縁部202から少なくとも80ミクロンのところにある。加えて、絶縁膜104の角縁部204は、ダイ102の角(コーナー)206から少なくとも300ミクロンのところにある。しかしながら、任意の適切な距離を利用できることが理解されるであろう。

アンカー構造116は、一般に符号208で示す様にバンプ開口部114の周りに(例えば、バンプ開口部を取り囲むように)配置されうる。アンカー構造116は、一般に符号210で示すように、絶縁膜104の外周(の一部分)に沿って配置されうる。

一部の態様では、アンカー構造116の開口部118は、直径が少なくとも40ミクロンである。加えて、開口部118は、絶縁膜104の外周に沿って配置されたときに少なくとも60ミクロンの間隔を置いて離されることがある。さらに、開口部118は、一般に符号212で示す様にバンプ開口部114の縁から少なくとも25ミクロンの間隔が置かれることがある。しかしながら、任意の適切なサイズや間隔を利用できることが理解されるであろう。

次に、図4は、(図2の)フリップチップ100の第2の例示的な平面図を示す。アンカー構造116の開口部118は、任意の適切な形状およびサイズでありうる。例えば、開口部118は、一般に符号300で示す様に正方形の形をしている場合がある。開口部118は、例えば、一般に符号302で示した八角形の形をしているように一般に事実上円形をしている場合がある。開口部118は、一般に符号304で示すように、長方形または矩形をしている場合がある。加えて、開口部118は、一般に符号306で示すように、バンプ開口部114を取り囲む(または少なくとも実質的に取り囲む)ことがある。開口部118の例示的な形状を示したが、当業者であれば、開口部118は任意の適切な形状をしていてよいことが理解されるであろう。

次に、図5は、本発明の第2の実施形態によるフリップチップ100を示す。本実施形態では、アンカー構造116は、ダイ102と絶縁膜104との間のダミー材料400によって画定される。ダミー材料400は、銅、アルミニウムその他の適切な金属および/または物質から作ることができる。一部の態様では、ダミー材料400は、厚みが約5ミクロンであり、幅が約40ミクロンであるが、他の幅や厚みも考えられる。ダミー材料は、既知の技術、例えばスパッタリングやメッキその他の適切な技術を用いて付加することができる。ダミー材料400は、絶縁膜104に突起部402を形成し、これによりアンダーフィル材料110が絶縁膜104に機械的に付着してロックされることが可能となる。一部の態様では、絶縁膜104に突起部402ではなく陥凹部(recess)を形成するために、ダミー材料400は一部が取り除かれる場合がある。

次に、図6は、アンカー構造116を持つ集積回路製品を製造するために実行することができる例示的な工程を有するフローチャート500を示す。製造プロセスは工程502で始まる。工程504では、ダイ102は、例えば機械や人その他の当該分野で周知の適切な手段によってアセンブリステーション(図示せず)に提供される。一部の態様では、ダイ102は、ウェーハの形をしていることがある。アセンブリステーションは、組立の際にダイ102を所定の位置に保持するのに適したいかなる物であってもよい。工程506では、アンカー構造116を含む絶縁膜104がダイ102に付加される。既に議論したように、アンカー構造116は、開口部118、突起部402、および/または陥凹部を含みうる。

次に、図7は、開口部118を有するアンカー構造116を備えたフリップチップ100を製造するために実行することができる例示的な工程を有するフローチャート600を示す。製造プロセスは工程602で始まる。工程604では、ダイ102は、ウェーハの形であってもよく、アセンブリステーションに提供される。アンカー構造116を有する絶縁膜104は、例えば工程608〜614に示すように、ダイ102に付加することができる。しかしながら、任意の適切な処理工程を利用できる。工程606では、ダイ102の表面上に形成し、絶縁体の役割を果たす酸化膜がダイ102の選択部分から取り除かれる。

工程608では、絶縁膜104がダイ102に付加される。より具体的には、絶縁膜104は、当該分野で周知のスピン被覆によってダイ102に付加される。工程610では、バンプ開口部114と開口部118とを画定するマスクが絶縁膜104に付加される。マスクは、当該分野で既知の任意の方法により付加可能である。例えば、マスクは絶縁膜104と接触する場合があってもよく、マスクは絶縁膜104に近傍内に存在する場合があってもよく、または、マスクは絶縁膜104上に投影される場合があってもよい。

工程612では、絶縁膜104は、当該分野で周知のように電磁(EM:electromagnetic)放射線に露光、現像、そして硬化される。EM放射線は一般的には紫外線である。工程614では、バンプ開口部114と開口部118とを絶縁膜104に生成するため、絶縁膜104のマスクによりEM放射線に照射されなかった部分が当該分野で既知の技術によって取り除かれる。

工程616では、当該分野で既知の技術によってアンダーバンプ導体(underbump conductor)が絶縁膜104に付加される。工程618では、アンダーバンプ導体にフォトレジストが塗布される。工程620では、アンダーバンプ層を生成するため、当該分野で既知の技術によってフォトレジストはEM放射線に露光、現像、そして硬化される。フォトレジストがポジ型フォトレジストのときには、フォトレジストはEM放射線に露光されると(現像液に対して)より可溶性になる。しかしながら、フォトレジストがネガ型フォトレジストのときには、EM放射線に露光されたフォトレジストは逆に(現像液に対して)より不溶性になる。工程622では、UBM106を生成するため、エッチングその他の適切な技術によってアンダーバンプ層の一部が取り除かれる。工程624でフォトレジストが取り除かれる。

工程626では、導電性バンプ108がダイ102に動作可能に結合される。より具体的には、UBM106は既知技術を用いてバンプ開口部114を通してダイ102に動作可能に結合され、導電性バンプ108は既知技術を用いてUBM106に動作可能に結合される。工程628では、既知技術を用いて基板112が導電性バンプ108に動作可能に結合される。

工程630では、既知技術を用いてアンダーフィル材料110が絶縁膜104と基板112との間に充填される。このようにして、アンダーフィル材料110は、開口部118内に流れ込み、アンカー構造116に機械的に付着し、かつロックされる。この機械的なロックにより、フリップチップ100は層間剥離を起しにくくなる。工程632では、フリップチップ100が既知技術を用いて硬化される。工程634では、製造プロセスが終了する。

次に、図8は、ダミー材料400によって画定されるアンカー構造116を備えたフリップチップ100を製造するために実行することができる例示的な工程を有するフローチャート700を示す。製造プロセスは工程702で始まる。工程704では、ダイ102は、ウェーハの形であってもよく、アセンブリステーションに提供される。工程706では、ダイ102の表面上に形成する酸化膜がダイ102の選択部分から取り除かれる。工程708では、ダミー材料400は既知技術を用いてダイ102に動作可能に結合される。既に議論したように、ダミー材料400は、銅、アルミニウムその他の適切な金属および/または物質から作ることができる。

工程710では、ダイ102に絶縁膜104が付加される。より具体的には、絶縁膜104は、スピン被覆その他の適切な技術によってダイ102とダミー材料400とに付加される。工程716では、バンプ開口部114を画定するマスクが絶縁膜104に付加される。一部の態様では、マスクは、バンプ開口部114と開口部118との両方を画定する。マスクは、当該分野において既知の任意の方法で絶縁膜104に付加される。例えば、マスクは絶縁膜104と接触する場合があってもよく、マスクは絶縁膜104の近傍内に存在する場合があってもよく、または、マスクは絶縁膜104上に投影される場合があってもよい。

工程714では、絶縁膜104は、既知技術を用いて電磁放射線(EM)に露光、現像、そして硬化される。EM放射線は一般的には紫外線である。工程716では、バンプ開口部114を生成するため、マスクによって絶縁膜104のEM放射線に照射されなかった部分が取り除かれる。マスクがバンプ開口部114と開口部118との両方を画定する場合には、バンプ開口部114と開口部118とを両方とも生成するため、絶縁膜104のEM放射線に照射されなかった部分が取り除かれる。

工程718では、当該分野において既知の技術によって絶縁膜104にアンダーバンプ導体が付加される。工程720では、アンダーバンプ導体にフォトレジストが塗布される。工程722では、アンダーバンプ層を形成するため、当該分野において既知の技術によってフォトレジストがEM放射線に露光、現像、そして硬化される。フォトレジストがポジ型フォトレジストのときには、フォトレジストはEM放射線に露光されると(現像液に対して)より可溶性になる。しかしながら、フォトレジストがネガ型フォトレジストのときには、EM放射線に露光されたフォトレジストは逆により不溶性になる。工程724では、UBM106を生成するため、エッチングその他の適切な技術によってアンダーバンプ層の一部が取り除かれる。工程726でフォトレジストが取り除かれる。

工程728では、導電性バンプ108がダイ102に動作可能に結合される。より具体的には、UBM106は既知技術を用いてバンプ開口部114を通してダイ102に動作可能に結合され、導電性バンプ108は既知技術を用いてUBM106に動作可能に結合される。工程730では、既知技術を用いて基板112が導電性バンプ108に動作可能に結合される。工程732では、アンダーフィル材料110が、絶縁膜104と基板112との間に充填される。このようにして、アンダーフィル材料110は、突起部402の間に(または陥凹部に)流れ込み、アンカー構造116に機械的に付着し、かつロックされる。この機械的なロックにより、フリップチップ100は層間剥離を起しにくくなる。工程734では、フリップチップ100が既知技術を用いて硬化される。工程736では、製造プロセスが終了する。

上記の工程は任意の適切な順序で実行することが許され、要望に応じて他の製造技術を利用できることが理解されるであろう。

次に、図9を参照して説明すると、フリップチップ100は、例えば、無線電話機、移動型および/もしくは固定型コンピュータ、プリンタ、LANインタフェース(無線および/もしくは有線)、メディアプレイヤ、ビデオ復号器および/もしくは符号器、並びに/または他の適切なデバイスといった、デバイス800に実装可能である。デバイス800は、何よりも、グラフィックプロセッサ(あるいは単一コア)および/または1以上の中央演算処理装置(あるいは単複数コア)その他の適切な回路といった、プロセッサ802を含みうる。プロセッサ802は、フリップチップ100に実装されうる。より具体的には、フリップチップ100のダイ102はプロセッサ802を含みうる。

デバイス800は、RAM、ROM、スタティック、個別論理、ダイナミック、低遅延不揮発性メモリ(例えばフラッシュメモリなど)および/または1以上のプロセッサ802によって実行することが許される実行可能な命令を格納する任意の適切な光磁気または電子データストレージなどの、メモリ804も含みうる。メモリ804は、インタネットサーバを介して利用可能なネットワークメモリ、インタネットサーバその他の適切なノンローカル・メモリなど、ノンローカル・メモリも含みうる。図示されてはいないが、メモリ804もフリップチップ100に実装されうる。

デバイス800は、ディスプレイ806および/または任意の他の適切な回路、インタフェース、構造もしくは機能操作も含みうる。プロセッサ802、メモリ804、および/またはディスプレイ806は、バス808および/または任意の他の適切な通信メカニズムを介して、そのバスがローカル、無線、ネットワーク接続その他の適切なリンクのいずれであっても、通信することができる。

既に指摘したように、フリップチップ100は何よりも、アンカー構造を含む改良された絶縁膜を有する。アンダーフィル材料は、機械的なロックを生み出すアンカー構造に機械的に付着する。機械的なロックは、フリップチップ100の構造をより強固にし、従って層間剥離を起きにくくする。アンカー構造の開口部、陥凹部または突起部は、絶縁膜の例えばマスク層で決定される所定の位置に配置される。また、開口部、陥凹部または突起部のサイズは、サブミクロンレベルとは対照的に数ミクロンレベルである。

本開示は、本発明の実施形態の特定例を含むが、本開示に限定されないと理解されたい。本願に添付した図面、明細書、特許請求の範囲の請求項の研究を通して、当業者は、本発明の精神および範囲を逸脱することなく、数々の変更、変形、置換および均等形態を考えつくことであろう。

Claims (25)

- ダイと、

複数のバンプ開口部およびアンダーフィルアンカー構造を含み、前記ダイに動作可能に結合した絶縁膜と

を備えてなる集積回路製品。 - 前記アンダーフィルアンカー構造に機械的に付着したアンダーフィル材料を更に含んでいる請求項1に記載の集積回路製品。

- 前記アンダーフィルアンカー構造は、前記絶縁膜によって画定される少なくとも1つの開口部を含んでいる請求項1または2に記載の集積回路製品。

- 前記アンダーフィルアンカー構造は、突起部と陥凹部との少なくとも一方を含んでいる請求項1または2に記載の集積回路製品。

- 前記ダイと前記絶縁膜との間に動作可能に結合したダミー材料を更に含み、該ダミー材料は前記アンダーフィルアンカー構造を画定している請求項1乃至4のいずれか1項に記載の集積回路製品。

- 前記アンダーフィルアンカー構造は、前記絶縁膜の外周の少なくとも一部分に沿って配置されている請求項1乃至5のいずれか1項に記載の集積回路製品。

- 前記アンダーフィルアンカー構造は、前記複数のバンプ開口部の周りに配置されている請求項1乃至5のいずれか1項に記載の集積回路製品。

- ダイを提供する工程と、

複数のバンプ層およびアンダーフィルアンカー構造を含む絶縁膜を前記ダイに付加する工程と

を含んでなる、集積回路製品の製造方法。 - 前記複数のバンプ開口部と前記アンダーフィルアンカー構造との少なくとも一方は、前記絶縁膜の一部を取り除くことによって形成されている請求項8に記載の集積回路製品の製造方法。

- 前記複数のバンプ開口部と前記アンダーフィルアンカー構造との少なくとも一方を画定するマスクを前記絶縁膜に付加し、

前記マスクと前記絶縁膜とに電磁放射線を照射し、

前記絶縁膜を現像し、

前記絶縁膜を硬化し、

前記絶縁膜の前記マスクを介して電磁放射線に照射されなかった部分を取り除く

ことによって、前記絶縁膜の一部を取り除くものである請求項9に記載の集積回路製品の製造方法。 - 前記アンダーフィルアンカー構造は、前記絶縁膜によって画定される少なくとも1つの開口部を含んでいる請求項8乃至10のいずれか1項に記載の集積回路製品の製造方法。

- 前記アンダーフィルアンカー構造は、突起部と陥凹部との少なくとも一方を含んでいる請求項8乃至10のいずれか1項に記載の集積回路製品の製造方法。

- 前記アンダーフィルアンカー構造は、前記絶縁膜の外周の少なくとも一部分に沿って配置されている請求項8乃至12のいずれか1項に記載の集積回路製品の製造方法。

- 前記アンダーフィルアンカー構造は、前記複数のバンプ開口部の周りに配置されている請求項8乃至12のいずれか1項に記載の集積回路製品の製造方法。

- 前記絶縁膜を前記ダイに付加する前に、前記アンダーフィルアンカー構造を画定するダミー材料を前記ダイ表面に動作可能に結合させる工程を更に含む請求項8乃至14のいずれか1項に記載の集積回路製品の製造方法。

- 前記複数のバンプ開口部を通して複数の導電性バンプを前記ダイに動作可能に結合させる工程を更に含む請求項8乃至15のいずれか1項に記載の集積回路製品の製造方法。

- 前記複数の導電性バンプに基板を動作可能に結合させる工程を更に含む請求項16に記載の集積回路製品の製造方法。

- 前記ダイと前記基板との間の間隙をアンダーフィル材料で埋める工程を更に含み、この工程によって前記アンダーフィル材料は前記アンダーフィルアンカー構造に機械的に付着するものである請求項17に記載の集積回路製品の製造方法。

- ダイと、

複数のバンプ開口部およびアンダーフィルアンカー構造を含み、前記ダイに動作可能に結合した絶縁膜と、

前記複数のバンプ開口部を通して前記ダイに動作可能に結合した複数の導電性バンプと、

前記複数の導電性バンプに動作可能に結合した基板と、

前記ダイと前記基板との間の間隙を埋め、前記アンダーフィルアンカー構造に機械的に付着したアンダーフィル材料と

を備えてなる集積回路製品。 - 前記アンダーフィルアンカー構造は、前記絶縁膜によって画定される少なくとも1つの開口部を含んでいる請求項19に記載の集積回路製品。

- 前記アンダーフィルアンカー構造は、突起部と陥凹部との少なくとも一方を含んでいる請求項19に記載の集積回路製品。

- 前記アンダーフィルアンカー構造は、前記絶縁膜の外周の少なくとも一部分に沿って配置されている請求項19乃至21のいずれか1項に記載の集積回路製品。

- 前記アンダーフィルアンカー構造は、前記複数のバンプ開口部の周りに配置されている請求項19乃至21のいずれか1項に記載の集積回路製品。

- ダイと、

複数のバンプ開口部およびアンダーフィルアンカー構造を含み、前記ダイに動作可能に結合した絶縁膜と、

前記複数のバンプ開口部を通して前記ダイに動作可能に結合した複数の導電性バンプと、

前記複数の導電性バンプに動作可能に結合した基板と、

前記ダイと前記基板との間の間隙を埋め、前記アンダーフィルアンカー構造に機械的に付着したアンダーフィル材料と

を備えてなる集積回路製品を含むデバイス。 - 前記集積回路製品に動作可能に結合したディスプレイを更に備え、前記ダイはプロセッサを含んでいる請求項24に記載のデバイス。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/623,532 US20080169555A1 (en) | 2007-01-16 | 2007-01-16 | Anchor structure for an integrated circuit |

| PCT/IB2008/000091 WO2008087530A1 (en) | 2007-01-16 | 2008-01-15 | Underfill anchor structure for an integrated circuit |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010516063A true JP2010516063A (ja) | 2010-05-13 |

Family

ID=39284094

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009546014A Withdrawn JP2010516063A (ja) | 2007-01-16 | 2008-01-15 | 集積回路用アンダーフィルアンカー構造 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20080169555A1 (ja) |

| EP (1) | EP2122674A1 (ja) |

| JP (1) | JP2010516063A (ja) |

| KR (1) | KR20090110855A (ja) |

| CN (1) | CN101681846A (ja) |

| WO (1) | WO2008087530A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012518282A (ja) * | 2009-02-18 | 2012-08-09 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | 補強層を伴う半導体チップ |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102005009358B4 (de) * | 2005-03-01 | 2021-02-04 | Snaptrack, Inc. | Lötfähiger Kontakt und ein Verfahren zur Herstellung |

| DE102007044620A1 (de) * | 2007-09-19 | 2009-04-16 | Semikron Elektronik Gmbh & Co. Kg | Anordnung mit einer Verbindungseinrichtung und mindestens einem Halbleiterbauelement |

| US20110222256A1 (en) * | 2010-03-10 | 2011-09-15 | Topacio Roden R | Circuit board with anchored underfill |

| US8058108B2 (en) | 2010-03-10 | 2011-11-15 | Ati Technologies Ulc | Methods of forming semiconductor chip underfill anchors |

| US8617926B2 (en) | 2010-09-09 | 2013-12-31 | Advanced Micro Devices, Inc. | Semiconductor chip device with polymeric filler trench |

| US8772083B2 (en) * | 2011-09-10 | 2014-07-08 | Ati Technologies Ulc | Solder mask with anchor structures |

| US9287191B2 (en) * | 2011-10-12 | 2016-03-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device package and method |

| US9478509B2 (en) | 2014-03-06 | 2016-10-25 | GlobalFoundries, Inc. | Mechanically anchored backside C4 pad |

| US9466547B1 (en) | 2015-06-09 | 2016-10-11 | Globalfoundries Inc. | Passivation layer topography |

| US11094625B2 (en) | 2019-01-02 | 2021-08-17 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor package with improved interposer structure |

| US11171104B2 (en) | 2019-10-24 | 2021-11-09 | Marvell Asia Pte, Ltd. | IC chip package with dummy solder structure under corner, and related method |

| US20230420314A1 (en) * | 2022-06-27 | 2023-12-28 | Taiwan Semiconductor Manufacturing Company Limited | Anchor-containing underfill structures for a chip package and methods of forming the same |

| US20240243098A1 (en) * | 2023-01-18 | 2024-07-18 | Mediatek Inc. | Semiconductor package and fabrication method thereof |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6011301A (en) * | 1998-06-09 | 2000-01-04 | Stmicroelectronics, Inc. | Stress reduction for flip chip package |

| US6246124B1 (en) * | 1998-09-16 | 2001-06-12 | International Business Machines Corporation | Encapsulated chip module and method of making same |

| US6103134A (en) * | 1998-12-31 | 2000-08-15 | Motorola, Inc. | Circuit board features with reduced parasitic capacitance and method therefor |

| US6400016B2 (en) * | 2000-01-14 | 2002-06-04 | I-Ming Chen | Method for mounting a semiconductor chip on a substrate and semiconductor device adapted for mounting on a substrate |

| US6501170B1 (en) * | 2000-06-09 | 2002-12-31 | Micron Technology, Inc. | Substrates and assemblies including pre-applied adhesion promoter |

| US6528417B1 (en) * | 2001-09-17 | 2003-03-04 | Taiwan Semiconductor Manufacturing Company | Metal patterned structure for SiN surface adhesion enhancement |

| US20030170450A1 (en) * | 2002-03-05 | 2003-09-11 | Stewart Steven L. | Attachment of surface mount devices to printed circuit boards using a thermoplastic adhesive |

| US6906425B2 (en) * | 2002-03-05 | 2005-06-14 | Resolution Performance Products Llc | Attachment of surface mount devices to printed circuit boards using a thermoplastic adhesive |

| JP2004349440A (ja) * | 2003-05-22 | 2004-12-09 | Renesas Technology Corp | フリップチップ実装方法 |

| DE10345247B4 (de) * | 2003-09-29 | 2007-10-04 | Infineon Technologies Ag | Verwendung von Leiterbahnen als Krallkörper |

| DE10352349B4 (de) * | 2003-11-06 | 2006-11-16 | Infineon Technologies Ag | Halbleiterchip mit Flip-Chip-Kontakten und Verfahren zur Herstellung desselben |

| TWI275187B (en) * | 2005-11-30 | 2007-03-01 | Advanced Semiconductor Eng | Flip chip package and manufacturing method of the same |

| US7600667B2 (en) * | 2006-09-29 | 2009-10-13 | Intel Corporation | Method of assembling carbon nanotube reinforced solder caps |

-

2007

- 2007-01-16 US US11/623,532 patent/US20080169555A1/en not_active Abandoned

-

2008

- 2008-01-15 KR KR1020097017065A patent/KR20090110855A/ko not_active Withdrawn

- 2008-01-15 JP JP2009546014A patent/JP2010516063A/ja not_active Withdrawn

- 2008-01-15 WO PCT/IB2008/000091 patent/WO2008087530A1/en not_active Ceased

- 2008-01-15 EP EP08702253A patent/EP2122674A1/en not_active Withdrawn

- 2008-01-15 CN CN200880007806A patent/CN101681846A/zh active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012518282A (ja) * | 2009-02-18 | 2012-08-09 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | 補強層を伴う半導体チップ |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080169555A1 (en) | 2008-07-17 |

| EP2122674A1 (en) | 2009-11-25 |

| CN101681846A (zh) | 2010-03-24 |

| WO2008087530A1 (en) | 2008-07-24 |

| KR20090110855A (ko) | 2009-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010516063A (ja) | 集積回路用アンダーフィルアンカー構造 | |

| US9595496B2 (en) | Integrated device package comprising silicon bridge in an encapsulation layer | |

| CN101499445B (zh) | 半导体器件及其制造方法 | |

| CN103782382B (zh) | 具有锚固结构的焊接掩模 | |

| CN110828394B (zh) | 半导体封装件 | |

| JPH08213423A (ja) | 半導体素子上に導電バンプを形成する方法 | |

| JP2001110831A (ja) | 外部接続突起およびその形成方法、半導体チップ、回路基板ならびに電子機器 | |

| JP2004214501A (ja) | ウエハーレベル・チップサイズ・パッケージおよびその製造方法 | |

| CN111613538A (zh) | 制造半导体芯片的连接结构和制造半导体封装件的方法 | |

| JP2002231854A (ja) | 半導体装置およびその製造方法 | |

| US9524944B2 (en) | Method for fabricating package structure | |

| KR20130112736A (ko) | 땜납 실장 기판과 그 제조방법, 및 반도체 장치 | |

| KR102226190B1 (ko) | 반도체 패키지 및 그 제조 방법 | |

| JP3568869B2 (ja) | 半導体集積回路装置及びその製造方法 | |

| JP2001077231A (ja) | 半導体装置、半導体ウエハ及び半導体装置の製造方法 | |

| JP3800298B2 (ja) | バンプの形成方法及び半導体装置の製造方法 | |

| KR20010105641A (ko) | 웨이퍼 레벨 칩 스케일 패키지 및 그 제조방법 | |

| US7910478B2 (en) | Method of manufacturing semiconductor devices | |

| JP2001118956A (ja) | 半導体装置およびその製造方法 | |

| JP3928729B2 (ja) | 半導体装置 | |

| CN107611112A (zh) | 一种扇出型封装器件 | |

| KR101023950B1 (ko) | 전도성 폴리머 범프를 갖는 칩 및 그 제조방법과, 칩을 구비한 전자부품 및 그 제조방법 | |

| JP2000031191A (ja) | 半導体装置 | |

| CN111162007B (zh) | 半导体器件及其制造方法 | |

| JP4359785B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Application deemed to be withdrawn because no request for examination was validly filed |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20110405 |