JP2010103484A - 半導体デバイス、その製造装置及び製造方法 - Google Patents

半導体デバイス、その製造装置及び製造方法 Download PDFInfo

- Publication number

- JP2010103484A JP2010103484A JP2009186634A JP2009186634A JP2010103484A JP 2010103484 A JP2010103484 A JP 2010103484A JP 2009186634 A JP2009186634 A JP 2009186634A JP 2009186634 A JP2009186634 A JP 2009186634A JP 2010103484 A JP2010103484 A JP 2010103484A

- Authority

- JP

- Japan

- Prior art keywords

- gas

- based gas

- semiconductor device

- wafer

- chamber

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/34—Nitrides

- C23C16/345—Silicon nitride

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3402—Deposited materials, e.g. layers characterised by the chemical composition

- H10P14/3414—Deposited materials, e.g. layers characterised by the chemical composition being group IIIA-VIA materials

- H10P14/3416—Nitrides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/63—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the formation processes

- H10P14/6326—Deposition processes

- H10P14/6328—Deposition from the gas or vapour phase

- H10P14/6334—Deposition from the gas or vapour phase using decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H10P14/6336—Deposition from the gas or vapour phase using decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/66—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials

- H10P14/668—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials

- H10P14/6681—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials the precursor containing a compound comprising Si

- H10P14/6682—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the type of materials the materials being characterised by the deposition precursor materials the precursor containing a compound comprising Si the compound being a silane, e.g. disilane, methylsilane or chlorosilane

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/69—Inorganic materials

- H10P14/694—Inorganic materials composed of nitrides

- H10P14/6943—Inorganic materials composed of nitrides containing silicon

- H10P14/69433—Inorganic materials composed of nitrides containing silicon the material being a silicon nitride not containing oxygen, e.g. SixNy or SixByNz

Landscapes

- Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Formation Of Insulating Films (AREA)

- Chemical Vapour Deposition (AREA)

Abstract

【解決手段】処理対象に対して窒素系ガス(窒素(N2)ガス、アンモニア(NH3)ガス、ジアジン(N2H2)ガス、ヒドラジン(N2H4)ガスなど)を供給する手段と、前記処理対象に対してシリコン系ガス(アミノ基、ジメチルアミノ基又はエチルアミノ基を有するもの。シランガス、ジシランガス、ジシラザンガスなど)を供給する手段と、前記各ガスの供給時に前記処理対象を減圧環境とする手段とを備える。

【選択図】 図2

Description

処理対象に対して水素成分を含むシリコン系ガスを供給する手段と、

前記シリコン系ガスを供給した後に前記処理対象に対して窒素系ガスを供給する手段とを備える。

上記課題を解決するために、本発明の半導体デバイスの製造装置は、処理対象に対して水素成分又はハロゲン成分を含むシリコン系ガスを供給する手段と、前記シリコン系ガスを供給した後に前記処理対象に対して窒素系ガスを供給する手段とを備える。

さらに、前記窒素系ガス或いはシリコン系ガスの、励起処理(減圧パルスCVD法又は、減圧パルスプラズマ法(リモートプラズマ法含む)など)、紫外光の照射処理又は加温処理などを含む、励起又は分解手段を備えるとよい。窒素系ガス或いはシリコン系ガスは、プラズマ励起処理によってプラズマ状態に励起されるか、プラズマ状態を経て分解されるかであり、また、紫外光の照射処理によって励起状態となるか励起状態を経て分解されるかであり、加温により熱分解される。また、加温処理は、励起処理を補助するために備えられてもよい。加温処理のみを分解手段とする場合は、ヒドラジンガス、アルキルヒドラジン(RNHNH2、R2NNH2等)ガス、アンモニアガス等のように450℃以下で分解される窒素系ガスを選択するとよい。

また、紫外光の照射処理の効果の補助をするために加温手段を併用してもよいが、その温度は、450℃以下とする。加温処理の併用により、SiN膜形成反応の促進、SiN膜の緻密化の効果がある。

2 ウェハアライメント

3 ロードロックチャンバー

4 トランスファーチャンバー

5 第一チャンバー

6 第二チャンバー

(実施形態1)

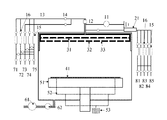

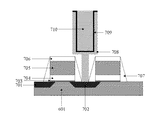

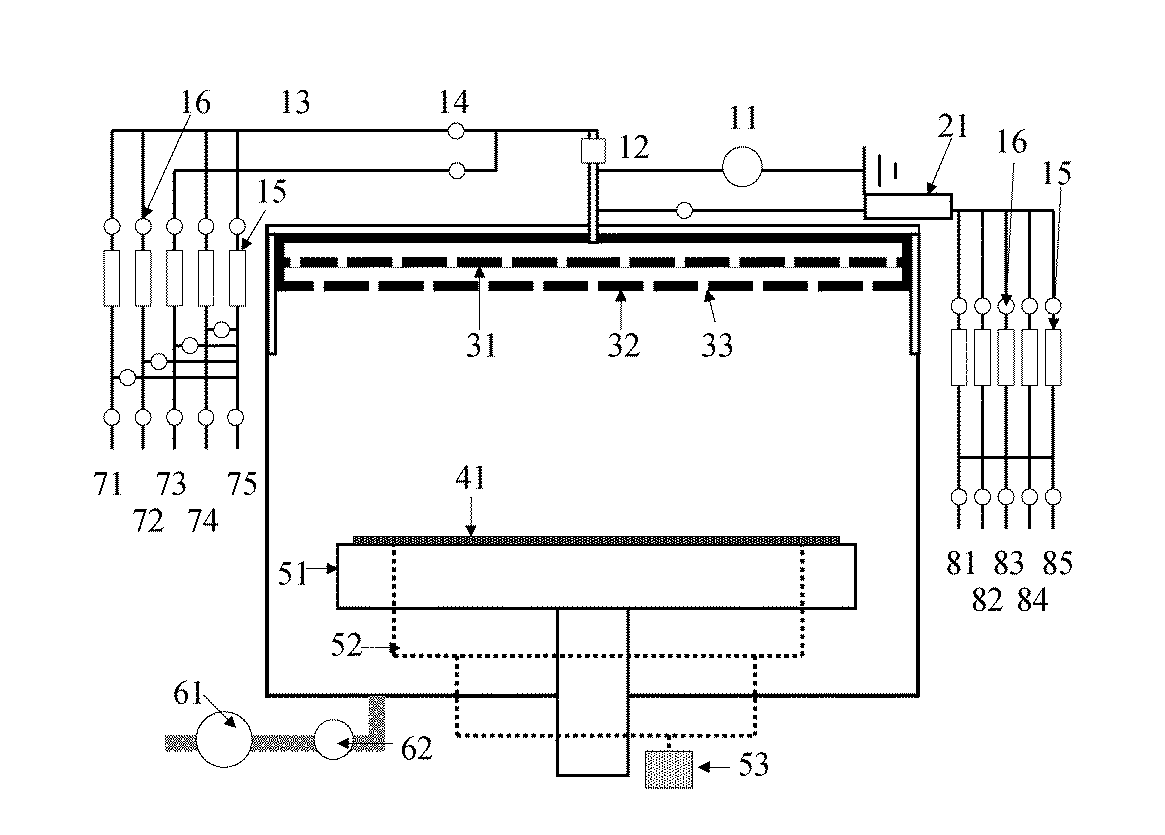

図1は、本発明の実施形態1の半導体デバイスの製造装置の模式的な構成図である。図1には、ウェハが収容されるカセット1と、カセット1から取り出されたウェハの位置決めを行うウェハアライメント2と、ロードロック機構を有するロードロックチャンバー3と、ウェハに絶縁物を形成するための第一チャンバー5と、第一チャンバー5において絶縁物が形成されたウェハに対して紫外光アニール処理を施す第二チャンバー6と、ロードロックチャンバー3,第一チャンバー5,第二チャンバー6相互間でウェハを搬送するロボットアームを有するトランスファーチャンバー4とを示している。

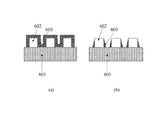

本発明の実施形態では、図1等に示した装置を用いて、実施形態1で説明したガスとは異なるガスを用いて、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態1の場合と同様である。

本発明の実施形態では、図1等に示した製造装置を用いて、実施形態1で説明したガスとは異なるガスを用いて、ガラス基板上にSiN膜603を形成する。製造条件は、以下の点を除き、実施形態1の場合と同様である。

本発明の実施形態では、図1等に示した製造装置を用いて、実施形態1で説明した手法とは異なる手法で、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態1の場合と同様である。

本発明の実施形態では、図1等に示した製造装置を用いて、実施形態1で説明した手法とは異なる手法で、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態1の場合と同様である。

本発明の実施形態では、図1等に示した製造装置を用いて、実施形態1で説明した手法とは異なる手法で、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態1の場合と同様である。

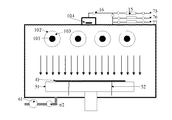

図7は、本発明の実施形態7に係る第一チャンバー5の模式的な構成図である。図7に示す第一チャンバー5は、端的に言えば、リモートプラズマ装置21の配置を変更した点と、内部にランプ101を設けている点と、複数の開口を有する石英板111と石英板112とを設けている点とが、図2に示したものとは相違する。

図8は、本発明の実施形態8に係る減圧CVD装置の模式的な構成図である。図8に示す減圧CVD装置は、実施形態7までに説明したいわゆるクラスタタイプのチャンバーではなく、バッチタイプのチャンバーである。この種のチャンバーを用いると、1回の処理で複数のウェハ41にSiN膜603を形成することができるという利点がある。

図8等に示した装置を用いて、実施形態8で説明したガスとは異なるガスを用いて、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態6の場合と同様である。

図8等に示した装置を用いて、実施形態8で説明したガスとは異なるガスを用いて、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態6の場合と同様である。

図8等に示した装置を用いて、実施形態8で説明したガスとは異なるガスを用いて、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態6の場合と同様である。

図7に示した第一チャンバー5を用いて、実施形態7で説明した方法とは異なる方法を用いて、ウェハ41のゲート電極上にSiN膜を形成する方法について説明する。製造条件は、以下の点を除き、実施形態7の場合と同様である。

図7に示した第一チャンバー5を用いて、実施形態7で説明した方法とは異なる方法で、ウェハ41のゲート電極上にSiN膜を形成する方法について説明する。製造条件は、以下の点を除き、実施形態7の場合と同様である。

図7に示した第一チャンバー5を用いて、実施形態7で説明した方法とは異なる方法で、ウェハ41のゲート電極上にSiN膜を形成する方法について説明する。製造条件は、以下の点を除き、実施形態7の場合と同様である。

図8等に示した装置を用いて、実施形態8で説明したガスとは異なるガスで、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態6の場合と同様である。

図8等に示した装置を用いて、実施形態8で説明したガスとは異なるガスで、ウェハ41のゲート電極602上にSiN膜603を形成する方法について説明する。製造条件は、以下の点を除き、実施形態6の場合と同様である。

Claims (13)

- 処理対象に対して水素成分又はハロゲン成分を含むシリコン系ガスを供給する手段と、前記シリコン系ガスを供給した後に前記処理対象に対して窒素系ガスを供給する手段とを備える半導体デバイスの製造装置。

- 前記シリコン系ガス又は窒素系ガスを励起又は分解する手段を備える、請求項1記載の半導体デバイスの製造装置。

- 前記励起又は分解する手段が、加温処理、プラズマ励起処理または紫外光の照射処理から選ばれる少なくとも1種の手段である請求項2記載の半導体デバイス製造装置。

- (追加)

前記窒素系ガス供給時にのみ励起又は分解する手段を備える請求項2記載の半導体デバイス製造装置。 - 前記窒素系ガスとともに水蒸気又は不活性ガスを供給する手段を有する、請求項1〜4のいずれかに記載の半導体デバイスの製造装置。

- 前記シリコン系ガスと窒素系ガスとを、交互に又は一緒に供給する手段を備える、請求項1〜5のいずれかに記載の半導体デバイスの製造装置。

- 前記処理対象を前記シリコン系ガスの沸点以下の温度条件で加熱する加熱手段を備える請求項1〜6のいずれかに記載の半導体デバイス製造装置。

- 前記紫外光の照射処理を行う紫外光の照射手段と前記処理対象との間を分離する仕切り板を備え、当該仕切り板には前記窒素系ガスを通す複数の開口部が形成されている、請求項3又は4に記載の半導体デバイスの製造装置。

- 前記紫外光の照射処理を行う紫外光の照射手段に対して不活性ガスを供給する手段を備える請求項3、4又は8記載の半導体デバイスの製造装置。

- 前記各手段によって各ガスを供給した後に、処理対象に対して紫外光、可視光又は赤外光を照射する手段を備える、請求項1〜9のいずれかに記載の半導体デバイス製造装置。

- 処理対象に対して水素成分又はハロゲン成分を含むシリコン系ガスを供給するステップと、前記シリコン系ガスを供給した後に前記処理対象に対して窒素系ガスを供給するステップとを含み、当該シリコン系ガスと当該窒素系ガスの一方又は両方を、加温処理、プラズマ励起処理または紫外光の照射処理から選ばれる少なくとも1種の手段で励起又は分解させて、処理対象に供給する半導体デバイスの製造方法。

- 窒素系ガス供給の時に励起又は分解を行う請求項11に記載の半導体デバイスの製造方法。

- デザインルールが32nm以下のデバイスであって、ソース領域とドレイン領域とが物理的に接触していない半導体デバイス。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009186634A JP2010103484A (ja) | 2008-09-29 | 2009-08-11 | 半導体デバイス、その製造装置及び製造方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008250536 | 2008-09-29 | ||

| JP2009186634A JP2010103484A (ja) | 2008-09-29 | 2009-08-11 | 半導体デバイス、その製造装置及び製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010103484A true JP2010103484A (ja) | 2010-05-06 |

Family

ID=42213867

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009186634A Pending JP2010103484A (ja) | 2008-09-29 | 2009-08-11 | 半導体デバイス、その製造装置及び製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2010103484A (ja) |

| KR (1) | KR20100036180A (ja) |

Cited By (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012067383A (ja) * | 2010-08-27 | 2012-04-05 | Tosoh Corp | 封止膜材料、封止膜及び用途 |

| JP2012160647A (ja) * | 2011-02-02 | 2012-08-23 | Taiyo Nippon Sanso Corp | シリコン窒化膜の形成方法 |

| JP2014179607A (ja) * | 2013-03-14 | 2014-09-25 | Asm Ip Holding B V | 低温でのSiNの蒸着用Si前駆体 |

| JP2015510263A (ja) * | 2012-01-26 | 2015-04-02 | ノベラス・システムズ・インコーポレーテッドNovellus Systems Incorporated | 紫外線を用いたコンフォーマルな膜蒸着の方法 |

| KR20160033057A (ko) * | 2014-09-17 | 2016-03-25 | 에이에스엠 아이피 홀딩 비.브이. | SiN 박막의 형성 방법 |

| JP2016082010A (ja) * | 2014-10-14 | 2016-05-16 | 大陽日酸株式会社 | シリコン窒化膜の製造方法及びシリコン窒化膜 |

| US9673041B2 (en) | 2010-04-15 | 2017-06-06 | Lam Research Corporation | Plasma assisted atomic layer deposition titanium oxide for patterning applications |

| WO2017154202A1 (ja) * | 2016-03-11 | 2017-09-14 | 大陽日酸株式会社 | シリコン窒化膜の製造方法及びシリコン窒化膜 |

| US9786570B2 (en) | 2012-11-08 | 2017-10-10 | Novellus Systems, Inc. | Methods for depositing films on sensitive substrates |

| US9793110B2 (en) | 2010-04-15 | 2017-10-17 | Lam Research Corporation | Gapfill of variable aspect ratio features with a composite PEALD and PECVD method |

| JP2017531920A (ja) * | 2014-10-03 | 2017-10-26 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | 高温酸化ケイ素原子層堆積技術 |

| US9875891B2 (en) | 2014-11-24 | 2018-01-23 | Lam Research Corporation | Selective inhibition in atomic layer deposition of silicon-containing films |

| US9892917B2 (en) | 2010-04-15 | 2018-02-13 | Lam Research Corporation | Plasma assisted atomic layer deposition of multi-layer films for patterning applications |

| US9997357B2 (en) | 2010-04-15 | 2018-06-12 | Lam Research Corporation | Capped ALD films for doping fin-shaped channel regions of 3-D IC transistors |

| US10037884B2 (en) | 2016-08-31 | 2018-07-31 | Lam Research Corporation | Selective atomic layer deposition for gapfill using sacrificial underlayer |

| US10043655B2 (en) | 2010-04-15 | 2018-08-07 | Novellus Systems, Inc. | Plasma activated conformal dielectric film deposition |

| US10062563B2 (en) | 2016-07-01 | 2018-08-28 | Lam Research Corporation | Selective atomic layer deposition with post-dose treatment |

| JP2018533215A (ja) * | 2015-10-22 | 2018-11-08 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | SiOおよびSiNを含む流動性膜を堆積させる方法 |

| KR20190027753A (ko) | 2017-09-07 | 2019-03-15 | 도쿄엘렉트론가부시키가이샤 | 성막 장치 및 성막 방법 |

| US10269559B2 (en) | 2017-09-13 | 2019-04-23 | Lam Research Corporation | Dielectric gapfill of high aspect ratio features utilizing a sacrificial etch cap layer |

| US10373806B2 (en) | 2016-06-30 | 2019-08-06 | Lam Research Corporation | Apparatus and method for deposition and etch in gap fill |

| US10395917B2 (en) | 2013-03-14 | 2019-08-27 | Asm Ip Holding B.V. | Si precursors for deposition of SiN at low temperatures |

| US10410857B2 (en) | 2015-08-24 | 2019-09-10 | Asm Ip Holding B.V. | Formation of SiN thin films |

| US10580645B2 (en) | 2018-04-30 | 2020-03-03 | Asm Ip Holding B.V. | Plasma enhanced atomic layer deposition (PEALD) of SiN using silicon-hydrohalide precursors |

| US20210348026A1 (en) * | 2020-05-08 | 2021-11-11 | Hansol Chemical Co., Ltd. | Silicon precursor and method of fabricating silicon-containing thin film using the same |

| CN113748226A (zh) * | 2019-04-25 | 2021-12-03 | 弗萨姆材料美国有限责任公司 | 用于氧化硅薄膜的高温原子层沉积的有机氨基二硅氮烷 |

| US11646198B2 (en) | 2015-03-20 | 2023-05-09 | Lam Research Corporation | Ultrathin atomic layer deposition film accuracy thickness control |

| US11996286B2 (en) | 2020-12-09 | 2024-05-28 | Asm Ip Holding B.V. | Silicon precursors for silicon nitride deposition |

| US12040181B2 (en) | 2019-05-01 | 2024-07-16 | Lam Research Corporation | Modulated atomic layer deposition |

| US12431349B2 (en) | 2019-06-07 | 2025-09-30 | Lam Research Corporation | In-situ control of film properties during atomic layer deposition |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020177980A (ja) * | 2019-04-16 | 2020-10-29 | 東京エレクトロン株式会社 | 成膜方法および成膜装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005019499A (ja) * | 2003-06-24 | 2005-01-20 | Tokyo Electron Ltd | 成膜装置及び成膜方法 |

| JP2008091469A (ja) * | 2006-09-29 | 2008-04-17 | Yoshimi Shiotani | 半導体製造装置、半導体製造方法及び電子機器 |

| JP2008140864A (ja) * | 2006-11-30 | 2008-06-19 | Tokyo Electron Ltd | シリコン窒化膜の形成方法、形成装置、形成装置の処理方法及びプログラム |

-

2009

- 2009-08-11 JP JP2009186634A patent/JP2010103484A/ja active Pending

- 2009-09-18 KR KR1020090088379A patent/KR20100036180A/ko not_active Withdrawn

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005019499A (ja) * | 2003-06-24 | 2005-01-20 | Tokyo Electron Ltd | 成膜装置及び成膜方法 |

| JP2008091469A (ja) * | 2006-09-29 | 2008-04-17 | Yoshimi Shiotani | 半導体製造装置、半導体製造方法及び電子機器 |

| JP2008140864A (ja) * | 2006-11-30 | 2008-06-19 | Tokyo Electron Ltd | シリコン窒化膜の形成方法、形成装置、形成装置の処理方法及びプログラム |

Cited By (66)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9892917B2 (en) | 2010-04-15 | 2018-02-13 | Lam Research Corporation | Plasma assisted atomic layer deposition of multi-layer films for patterning applications |

| US9793110B2 (en) | 2010-04-15 | 2017-10-17 | Lam Research Corporation | Gapfill of variable aspect ratio features with a composite PEALD and PECVD method |

| US10559468B2 (en) | 2010-04-15 | 2020-02-11 | Lam Research Corporation | Capped ALD films for doping fin-shaped channel regions of 3-D IC transistors |

| US10043655B2 (en) | 2010-04-15 | 2018-08-07 | Novellus Systems, Inc. | Plasma activated conformal dielectric film deposition |

| US9997357B2 (en) | 2010-04-15 | 2018-06-12 | Lam Research Corporation | Capped ALD films for doping fin-shaped channel regions of 3-D IC transistors |

| US12261038B2 (en) | 2010-04-15 | 2025-03-25 | Lam Research Corporation | Gapfill of variable aspect ratio features with a composite PEALD and PECVD method |

| US9673041B2 (en) | 2010-04-15 | 2017-06-06 | Lam Research Corporation | Plasma assisted atomic layer deposition titanium oxide for patterning applications |

| US10361076B2 (en) | 2010-04-15 | 2019-07-23 | Lam Research Corporation | Gapfill of variable aspect ratio features with a composite PEALD and PECVD method |

| US11133180B2 (en) | 2010-04-15 | 2021-09-28 | Lam Research Corporation | Gapfill of variable aspect ratio features with a composite PEALD and PECVD method |

| US10043657B2 (en) | 2010-04-15 | 2018-08-07 | Lam Research Corporation | Plasma assisted atomic layer deposition metal oxide for patterning applications |

| US11011379B2 (en) | 2010-04-15 | 2021-05-18 | Lam Research Corporation | Capped ALD films for doping fin-shaped channel regions of 3-D IC transistors |

| JP2012067383A (ja) * | 2010-08-27 | 2012-04-05 | Tosoh Corp | 封止膜材料、封止膜及び用途 |

| JP2012160647A (ja) * | 2011-02-02 | 2012-08-23 | Taiyo Nippon Sanso Corp | シリコン窒化膜の形成方法 |

| JP2015510263A (ja) * | 2012-01-26 | 2015-04-02 | ノベラス・システムズ・インコーポレーテッドNovellus Systems Incorporated | 紫外線を用いたコンフォーマルな膜蒸着の方法 |

| US10008428B2 (en) | 2012-11-08 | 2018-06-26 | Novellus Systems, Inc. | Methods for depositing films on sensitive substrates |

| US10741458B2 (en) | 2012-11-08 | 2020-08-11 | Novellus Systems, Inc. | Methods for depositing films on sensitive substrates |

| US9786570B2 (en) | 2012-11-08 | 2017-10-10 | Novellus Systems, Inc. | Methods for depositing films on sensitive substrates |

| JP2024023223A (ja) * | 2013-03-14 | 2024-02-21 | エーエスエム・アイピー・ホールディング・ベー・フェー | 低温でのSiNの堆積用Si前駆体 |

| US11587783B2 (en) | 2013-03-14 | 2023-02-21 | Asm Ip Holding B.V. | Si precursors for deposition of SiN at low temperatures |

| US11289327B2 (en) | 2013-03-14 | 2022-03-29 | Asm Ip Holding B.V. | Si precursors for deposition of SiN at low temperatures |

| JP2023027062A (ja) * | 2013-03-14 | 2023-03-01 | エーエスエム アイピー ホールディング ビー.ブイ. | 低温でのSiNの堆積用Si前駆体 |

| US11069522B2 (en) | 2013-03-14 | 2021-07-20 | Asm Ip Holding B.V. | Si precursors for deposition of SiN at low temperatures |

| JP7383106B2 (ja) | 2013-03-14 | 2023-11-17 | エーエスエム・アイピー・ホールディング・ベー・フェー | 低温でのSiNの堆積用Si前駆体 |

| US10424477B2 (en) | 2013-03-14 | 2019-09-24 | Asm Ip Holding B.V. | Si precursors for deposition of SiN at low temperatures |

| JP7663657B2 (ja) | 2013-03-14 | 2025-04-16 | エーエスエム・アイピー・ホールディング・ベー・フェー | 低温でのSiNの堆積用Si前駆体 |

| US10395917B2 (en) | 2013-03-14 | 2019-08-27 | Asm Ip Holding B.V. | Si precursors for deposition of SiN at low temperatures |

| JP2014179607A (ja) * | 2013-03-14 | 2014-09-25 | Asm Ip Holding B V | 低温でのSiNの蒸着用Si前駆体 |

| US11367613B2 (en) | 2014-09-17 | 2022-06-21 | Asm Ip Holding B.V. | Deposition of SiN |

| KR102243442B1 (ko) | 2014-09-17 | 2021-04-23 | 에이에스엠 아이피 홀딩 비.브이. | SiN 박막의 형성 방법 |

| KR20210129625A (ko) * | 2014-09-17 | 2021-10-28 | 에이에스엠 아이피 홀딩 비.브이. | SiN 박막의 형성 방법 |

| KR20160033057A (ko) * | 2014-09-17 | 2016-03-25 | 에이에스엠 아이피 홀딩 비.브이. | SiN 박막의 형성 방법 |

| US10262854B2 (en) | 2014-09-17 | 2019-04-16 | Asm Ip Holding B.V. | Deposition of SiN |

| KR20210045970A (ko) * | 2014-09-17 | 2021-04-27 | 에이에스엠 아이피 홀딩 비.브이. | SiN 박막의 형성 방법 |

| US10741386B2 (en) | 2014-09-17 | 2020-08-11 | Asm Ip Holding B.V. | Deposition of SiN |

| KR102546225B1 (ko) | 2014-09-17 | 2023-06-21 | 에이에스엠 아이피 홀딩 비.브이. | SiN 박막의 형성 방법 |

| KR102317181B1 (ko) | 2014-09-17 | 2021-10-26 | 에이에스엠 아이피 홀딩 비.브이. | SiN 박막의 형성 방법 |

| JP2017531920A (ja) * | 2014-10-03 | 2017-10-26 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | 高温酸化ケイ素原子層堆積技術 |

| JP2016082010A (ja) * | 2014-10-14 | 2016-05-16 | 大陽日酸株式会社 | シリコン窒化膜の製造方法及びシリコン窒化膜 |

| US10804099B2 (en) | 2014-11-24 | 2020-10-13 | Lam Research Corporation | Selective inhibition in atomic layer deposition of silicon-containing films |

| US9875891B2 (en) | 2014-11-24 | 2018-01-23 | Lam Research Corporation | Selective inhibition in atomic layer deposition of silicon-containing films |

| US11646198B2 (en) | 2015-03-20 | 2023-05-09 | Lam Research Corporation | Ultrathin atomic layer deposition film accuracy thickness control |

| US12354871B2 (en) | 2015-03-20 | 2025-07-08 | Lam Research Corporation | Ultrathin atomic layer deposition film accuracy thickness control |

| US11784043B2 (en) | 2015-08-24 | 2023-10-10 | ASM IP Holding, B.V. | Formation of SiN thin films |

| US10410857B2 (en) | 2015-08-24 | 2019-09-10 | Asm Ip Holding B.V. | Formation of SiN thin films |

| US11133181B2 (en) | 2015-08-24 | 2021-09-28 | Asm Ip Holding B.V. | Formation of SiN thin films |

| JP2018533215A (ja) * | 2015-10-22 | 2018-11-08 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | SiOおよびSiNを含む流動性膜を堆積させる方法 |

| WO2017154202A1 (ja) * | 2016-03-11 | 2017-09-14 | 大陽日酸株式会社 | シリコン窒化膜の製造方法及びシリコン窒化膜 |

| US10559459B2 (en) | 2016-03-11 | 2020-02-11 | Taiyo Nippon Sanso Corporation | Method for producing silicon nitride film and silicon nitride film |

| US10957514B2 (en) | 2016-06-30 | 2021-03-23 | Lam Research Corporation | Apparatus and method for deposition and etch in gap fill |

| US10373806B2 (en) | 2016-06-30 | 2019-08-06 | Lam Research Corporation | Apparatus and method for deposition and etch in gap fill |

| US10062563B2 (en) | 2016-07-01 | 2018-08-28 | Lam Research Corporation | Selective atomic layer deposition with post-dose treatment |

| US10679848B2 (en) | 2016-07-01 | 2020-06-09 | Lam Research Corporation | Selective atomic layer deposition with post-dose treatment |

| US10037884B2 (en) | 2016-08-31 | 2018-07-31 | Lam Research Corporation | Selective atomic layer deposition for gapfill using sacrificial underlayer |

| KR20190027753A (ko) | 2017-09-07 | 2019-03-15 | 도쿄엘렉트론가부시키가이샤 | 성막 장치 및 성막 방법 |

| US10559460B2 (en) | 2017-09-07 | 2020-02-11 | Tokyo Electron Limited | Film forming apparatus and film forming method |

| US10269559B2 (en) | 2017-09-13 | 2019-04-23 | Lam Research Corporation | Dielectric gapfill of high aspect ratio features utilizing a sacrificial etch cap layer |

| US10580645B2 (en) | 2018-04-30 | 2020-03-03 | Asm Ip Holding B.V. | Plasma enhanced atomic layer deposition (PEALD) of SiN using silicon-hydrohalide precursors |

| CN113748226A (zh) * | 2019-04-25 | 2021-12-03 | 弗萨姆材料美国有限责任公司 | 用于氧化硅薄膜的高温原子层沉积的有机氨基二硅氮烷 |

| US12480206B2 (en) | 2019-04-25 | 2025-11-25 | Versum Materials Us, Llc | Organoaminodisilazanes for high temperature atomic layer deposition of silicon oxide thin films |

| US12040181B2 (en) | 2019-05-01 | 2024-07-16 | Lam Research Corporation | Modulated atomic layer deposition |

| US12451346B2 (en) | 2019-05-01 | 2025-10-21 | Lam Research Corporation | Modulated atomic layer deposition |

| US12431349B2 (en) | 2019-06-07 | 2025-09-30 | Lam Research Corporation | In-situ control of film properties during atomic layer deposition |

| US20210348026A1 (en) * | 2020-05-08 | 2021-11-11 | Hansol Chemical Co., Ltd. | Silicon precursor and method of fabricating silicon-containing thin film using the same |

| JP2021177550A (ja) * | 2020-05-08 | 2021-11-11 | ハンソル ケミカル カンパニー リミテッドHansol Chemical Co., Ltd. | シリコン前駆体およびこれを用いたシリコン含有薄膜の製造方法 |

| JP7196228B2 (ja) | 2020-05-08 | 2022-12-26 | ハンソル ケミカル カンパニー リミテッド | シリコン前駆体およびこれを用いたシリコン含有薄膜の製造方法 |

| US11996286B2 (en) | 2020-12-09 | 2024-05-28 | Asm Ip Holding B.V. | Silicon precursors for silicon nitride deposition |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20100036180A (ko) | 2010-04-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010103484A (ja) | 半導体デバイス、その製造装置及び製造方法 | |

| CN103843110B (zh) | 双重图案化蚀刻工艺 | |

| US7651953B2 (en) | Method to form ultra high quality silicon-containing compound layers | |

| JP7524442B2 (ja) | 基板処理方法、半導体装置の製造方法、プログラムおよび基板処理装置 | |

| JP6086942B2 (ja) | 半導体装置の製造方法、基板処理装置およびプログラム | |

| US10910214B2 (en) | Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium | |

| CN111656510A (zh) | 处理掩模基板以实现更佳的膜质量的方法 | |

| CN101199044A (zh) | 硅基电介质的化学气相沉积方法 | |

| US9136114B2 (en) | Method of manufacturing semiconductor device, substrate processing method, computer-readable medium with program for executing a substrate processing method, and substrate processing apparatus | |

| CN114250452A (zh) | 基板处理装置、半导体装置的制造方法以及基板处理方法 | |

| CN108780743A (zh) | 基板处理装置、半导体装置的制造方法以及记录介质 | |

| JP2010103495A (ja) | 半導体デバイス、その製造装置及び製造方法 | |

| JP7688716B2 (ja) | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム | |

| JP7579959B2 (ja) | 基板処理方法、半導体装置の製造方法、基板処理装置、およびプログラム | |

| TWI897028B (zh) | 基板處理方法、半導體裝置之製造方法、程式及基板處理裝置 | |

| CN113355653B (zh) | 清洁方法、半导体装置的制造方法、基板处理装置以及存储介质 | |

| KR20240043091A (ko) | 기판 처리 방법, 반도체 장치의 제조 방법, 기판 처리 시스템 및 프로그램 | |

| CN115810542A (zh) | 衬底处理方法、半导体器件的制造方法、衬底处理装置、及程序 | |

| WO2022085498A1 (ja) | 成膜方法及び成膜装置 | |

| CN114121714A (zh) | 清洁方法、半导体器件的制造方法、衬底处理装置及记录介质 | |

| TWI893447B (zh) | 基板處理方法、半導體裝置之製造方法、基板處理系統及程式 | |

| TWI831204B (zh) | 半導體裝置之製造方法、基板處理方法、基板處理裝置及程式 | |

| TW202520380A (zh) | 基板處理方法、半導體裝置之製造方法、程式及基板處理裝置 | |

| JP2026010499A (ja) | 処理方法、半導体装置の製造方法、処理装置、およびプログラム | |

| JP2025180516A (ja) | 処理方法、半導体装置の製造方法、処理装置、およびプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120809 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120907 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20130110 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20130201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130308 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130528 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20131001 |