JP2010088056A - 周波数シンセサイザ - Google Patents

周波数シンセサイザ Download PDFInfo

- Publication number

- JP2010088056A JP2010088056A JP2008257768A JP2008257768A JP2010088056A JP 2010088056 A JP2010088056 A JP 2010088056A JP 2008257768 A JP2008257768 A JP 2008257768A JP 2008257768 A JP2008257768 A JP 2008257768A JP 2010088056 A JP2010088056 A JP 2010088056A

- Authority

- JP

- Japan

- Prior art keywords

- frequency

- signal

- vector

- voltage

- unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

- H03L7/18—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/091—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector using a sampling device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/095—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using a lock detector

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/10—Details of the phase-locked loop for assuring initial synchronisation or for broadening the capture range

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Abstract

【解決手段】電圧制御発振部に入力される制御電圧を監視し、監視された制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断してアンロック検出信号を出力する。回転ベクトルに対して、設定周波数に応じて粗刻みに決められた周波数で逆回転する逆回転ベクトルを乗算して回転ベクトルを減速する構成においては、減速された回転ベクトルの長さ(スカラー量)またはゲイン制御用の補正信号が予め設定した範囲から外れているか否かの判定結果を更に考慮する。

【選択図】図1

Description

前記電圧制御発振部に入力される制御電圧を監視する監視手段と、

この監視手段により監視された制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断し、外れているときにアンロック検出信号を出力する手段と、を備えたことを特徴とする。

本発明はまた次のような態様としてもよい。

前記監視手段は、前記制御電圧を監視する代わりに前記アナログ/ディジタル変換部の入力信号の信号レベルを監視するものであり、

アンロック検出信号を出力する手段は、制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断する代わりに、前記入力信号のレベルが予め定めた設定範囲から外れているか否かを判断するものである。

PLLロックした後、PLLロックから外れているときに周波数引き込み用の電圧を前記ディジタル/アナログ変換部からのアナログ電圧に加えて制御電圧として前記電圧制御発振部に供給するための周波数の引き込み手段を備え、

前記監視手段は、前記制御電圧を監視する代わりに周波数引き込み用の電圧を監視するものであり、

前記アンロック検出信号を出力する手段は、制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断する代わりに、前記周波数引き込み用の電圧のレベルが予め定めた設定範囲から外れているか否かを判断するものである。

前記減速されたベクトルの長さを検出するベクトル検出手段と、このベクトル検出手段にて検出されたベクトルの長さに基づいてゲイン制御用の補正信号を出力する手段と、前記アナログ/ディジタル変換部の後段であって前記直交検波を行う前の信号にゲイン制御用の補正信号を乗算する乗算手段と、前記検出されたベクトルの長さまたはゲイン制御用の補正信号が予め設定した範囲から外れたときに異常信号を出力する手段と、を更に設け、

前記アンロック検出信号を出力する手段は、前記監視手段により監視された制御電圧あるいは信号のレベルが予め定めた設定範囲から外れている状態と前記異常信号が出力されている状態とのうちの少なくとも一方の状態が発生しているときにアンロック検出信号を出力するように構成されている。

そして他の発明によれば、回転ベクトルに対して、設定周波数に応じて粗刻みに決められた周波数で逆回転する逆回転ベクトルを乗算して回転ベクトルを減速する構成においては、減速された回転ベクトルの長さ(スカラー量)またはゲイン制御用の補正信号が予め設定した範囲から外れているか否かの判定結果を更に考慮しているため、アンロックを瞬時にあるいは事前に検出でき、しかも確実に検出できる。

=1/2・Acosθ+1/2{cos(2ω0t)・cosθ+sin(2ω0t)・sinθ}……(1)

Acos(ω0t+θ)・−sin(ω0t)

=1/2・Asinθ−1/2{sin(2ω0t)・cosθ+cos(2ω0t)・sinθ}……(2)

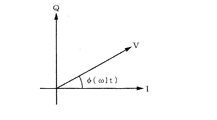

そこで掛け算部41aの出力及び掛け算部41bの出力を夫々ローパスフィルタ42a及び42bを通すことにより、2ω0tの周波数信号は除去されるので、結局ローパスフィルタ42a、42bからは夫々1/2・Acosθと1/2・Asinθとが取り出される。図3はこうして取り出されたベクトルVを表した図であり、このベクトルVは長さがAであり、回転速度がω1t(=φ)である(周波数がω1t/2π)。

I+jQ={I(n)・I`(n)−Q(n)・Q`(n)}+j{I(n)・Q`(n)+I`(n)・Q(n)} ……(3)

逆ベクトルV`を発生するとは、実際には複素平面上におけるベクトルが逆回転するように当該ベクトルの実数部分及び虚数部分の値つまり逆ベクトルV`の位相をφ`とすると、cosφ`とsinφ`との値を発生させることである。より具体的にはベクトルのcosφ`とsinφ`との組がベクトルの回転方向に沿って順番には配列されたテーブルを例えばパラメータ出力部6内に用意し、そのテーブルのアドレスを、指示された電圧制御発振器1の設定周波数に応じて決定されるインクリメント数またはデクリメント数で読み出すことで実現できる。

ここでI値(ベクトルVの実数部分)及びQ値(ベクトルVの虚数部分)についてn番目のサンプリングに対応する値を夫々I(n)及びQ(n)とすれば、ΔV及びconj{V(n)}は複素表示すると夫々(5)式及び(6)式で表される。

conj{V(n)}=I(n)−jQ(n) ……(6)

ただしΔIはI(n)−I(n−1)であり、ΔQはQ(n)−Q(n−1)である。(5)式及び(6)式を(4)式に代入して整理すると、Δφは(7)式で表されることになる。

前記第1の位相差検出部71は、このように近似式を用いてΔφを求める機能を備えている。このΔφは、逆ベクトル乗算部5にて減速されたベクトルVの周波数に対応する値である

ここでパラメータ出力部6は、外部より設定周波数が入力されており、また設定周波数に応じて粗刻みに決められた周波数つまり逆回転ベクトルV`の速度(周波数)も分かっていることから、電圧制御発振部1における出力周波数が設定周波数になったときに第2の位相差検出部71から得られるベクトルVの周波数

(Δφ)の値も予め分かっている。この値を周波数微調整分と呼ぶことにすると、第1の位相差検出部71の後段に設けられた加算部72にて、パラメータ出力部6から出力される周波数微調整分と第2の位相差検出部71との差分を取り出される。取り出された差分(周波数差)は位相差の累積加算部73にて累積加算され、ループフィルタ8を介して第1のD/A変換部80に与えられる。D/A変換部80にて得られたアナログ電圧は結合器11を介して電圧制御発振部1に制御電圧として供給される。位相差の累積加算部73及びループフィルタ8は、この例では周波数差を積分する手段に相当する。なお12は、コンデンサ及び抵抗からなるフィルタであり、電圧制御発振部1に印加される制御電圧の高い周波数でのノイズをよくあるするローパスフィルタの役割を持っている。

図5は、電圧制御発振部1に入力される制御電圧と出力周波数との関係を示す特性図であり、この関係が直線領域から外れるとPLL制御が異常状態となって出力周波数が設定周波数から外れてしまう。このようなPLLのアンロック状態を避けるために制御電圧としてはマージンをみて例えばE1からE2の間で使用することが好ましく、制御電圧がE1〜E2の範囲から外れたときにはアンロック検出信号を出力して、例えばこの周波数シンセサイザをシステムから切り離し、冗長側の周波数シンセサイザに切り替えるなどの処置を速やかに行う必要がある。このため監視手段9により制御電圧の信号レベルを検出するようにしている。

そしてまた本発明では、監視手段9が監視する電圧は、結合器11の後段に限らず、第2のD/A変換部84にて得られたアナログ電圧であってもよい。既述のようにPLLロックが成立した後、第1のD/A変換部80からのアナログ電圧が予め設定した範囲から外れたときに、アンロックにならないようにパラメータ出力部82から出力された定数の積分値に対応する電圧が第2のD/A変換部84から出力され、これにより電圧制御発振部1の制御電圧を高く(あるいは低く)している。従って第2のD/A変換部84にて得られたアナログ電圧であるいわば制御電圧の補償値を監視手段9により監視し、詳しくは図1のバッファアンプ91の入力を第2のD/A変換部84と結合器11との間から取り込む構成セとすることによっても同様の効果が得られる。

更にまた監視手段9により監視する電圧をこれらの例に代えてA/D変換部3の入力側としてもよい。この場合にもA/D変換部3の入力電圧が大きく変わり、その信号レベルが予め定めた設定範囲から外れたときに論理「L」を出力することで同様の効果が得られる。即ちこの場合にもアナログ電圧を検出しているので、速やかにアンロック状態を検出できる。

なお本発明において、分周器2の分周比Nは「1」であってもよく、この場合には、実質分周器を用いない場合と同等である。

11 結合器

2 分周器

3 A/D変換部

31 基準クロック発生部

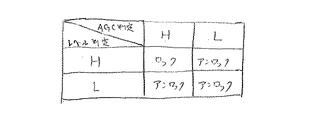

32 AGC回路部

33 補正値判定部

34 ロック/アンロック判定部

4 キャリアリムーブ

5 逆ベクトル演算部

6 パラメータ出力部

71 位相差検出部

72 加算部

73 位相差の累積加算部

8 ループフィルタ

9

Claims (4)

- 制御電圧に応じて電圧制御発振部から出力される周波数信号を分周し、分周された周波数信号である正弦波信号をアナログ/ディジタル変換部を介してディジタル化し、ディジタル化された周波数信号に対して、ディジタル信号である検波用の周波数信号による直交検波を行って、両周波数信号の周波数差に相当する周波数で回転するベクトルを複素表示したときの実数部分及び虚数部分をベクトル取り出し手段にて取り出し、前記電圧制御発振部の出力周波数が設定周波数になったときの前記ベクトルの周波数とベクトル取り出し手段にて取り出されたベクトルの周波数との周波数差を積分してディジタル/アナログ変換部を介して制御電圧として前記電圧制御発振部に供給する周波数シンセサイザにおいて、

前記電圧制御発振部に入力される制御電圧を監視する監視手段と、

この監視手段により監視された制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断し、外れているときにアンロック検出信号を出力する手段と、を備えたことを特徴とする周波数シンセサイザ。 - 前記監視手段は、前記制御電圧を監視する代わりに前記アナログ/ディジタル変換部の入力信号の信号レベルを監視するものであり、

アンロック検出信号を出力する手段は、制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断する代わりに、前記入力信号のレベルが予め定めた設定範囲から外れているか否かを判断するものであることを特徴とする請求項1記載の周波数シンセサイザ。 - PLLロックした後、PLLロックから外れているときに周波数引き込み用の電圧を前記ディジタル/アナログ変換部からのアナログ電圧に加えて制御電圧として前記電圧制御発振部に供給するための周波数の引き込み手段を備え、

前記監視手段は、前記制御電圧を監視する代わりに周波数引き込み用の電圧を監視するものであり、

前記アンロック検出信号を出力する手段は、制御電圧のレベルが予め定めた設定範囲から外れているか否かを判断する代わりに、前記周波数引き込み用の電圧のレベルが予め定めた設定範囲から外れているか否かを判断するものであることを特徴とする請求項1記載の周波数シンセサイザ。 - 周波数差を取り出す手段は、ベクトル取り出し手段にて取り出されたベクトルに対して、設定周波数に応じて粗刻みに決められた周波数で逆回転する逆回転ベクトルを乗算する手段と、この手段により減速されたベクトルについてサンプリング時間毎の位相差を検出する位相差検出部と、前記粗刻みに決められた周波数と設定周波数との差分の周波数で回転するベクトルについてのサンプリング時間毎の位相差と前記位相差検出部にて検出された位相差との差分を取り出す手段と、を備え、

前記減速されたベクトルの長さを検出するベクトル検出手段と、このベクトル検出手段にて検出されたベクトルの長さに基づいてゲイン制御用の補正信号を出力する手段と、前記アナログ/ディジタル変換部の後段であって前記直交検波を行う前の信号にゲイン制御用の補正信号を乗算する乗算手段と、前記検出されたベクトルの長さまたはゲイン制御用の補正信号が予め設定した範囲から外れたときに異常信号を出力する手段と、を更に設け、

前記アンロック検出信号を出力する手段は、前記監視手段により監視された制御電圧あるいは信号のレベルが予め定めた設定範囲から外れている状態と、前記異常信号が出力されている状態と、のうちの少なくとも一方の状態が発生しているときにアンロック検出信号を出力するように構成されていることを特徴とする請求項1ないし3のいずれか一つに記載の周波数シンセサイザ。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008257768A JP4787870B2 (ja) | 2008-10-02 | 2008-10-02 | 周波数シンセサイザ |

| BRPI0919585-8A BRPI0919585B1 (pt) | 2008-10-02 | 2009-09-30 | Sintetizador de frequência |

| KR1020117007663A KR101250571B1 (ko) | 2008-10-02 | 2009-09-30 | 주파수 신시사이저 |

| PCT/JP2009/005053 WO2010038456A1 (ja) | 2008-10-02 | 2009-09-30 | 周波数シンセサイザ |

| CN2009801394173A CN102171930B (zh) | 2008-10-02 | 2009-09-30 | 频率合成器 |

| EP09817497.2A EP2330743B1 (en) | 2008-10-02 | 2009-09-30 | Frequency synthesizer |

| US12/998,086 US8466717B2 (en) | 2008-10-02 | 2009-09-30 | Frequency synthesizer |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008257768A JP4787870B2 (ja) | 2008-10-02 | 2008-10-02 | 周波数シンセサイザ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010088056A true JP2010088056A (ja) | 2010-04-15 |

| JP2010088056A5 JP2010088056A5 (ja) | 2011-07-07 |

| JP4787870B2 JP4787870B2 (ja) | 2011-10-05 |

Family

ID=42073236

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008257768A Active JP4787870B2 (ja) | 2008-10-02 | 2008-10-02 | 周波数シンセサイザ |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8466717B2 (ja) |

| EP (1) | EP2330743B1 (ja) |

| JP (1) | JP4787870B2 (ja) |

| KR (1) | KR101250571B1 (ja) |

| CN (1) | CN102171930B (ja) |

| BR (1) | BRPI0919585B1 (ja) |

| WO (1) | WO2010038456A1 (ja) |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05227017A (ja) * | 1992-02-10 | 1993-09-03 | Nec Corp | 収束モード切り換え式ディジタルpll装置 |

| JPH06164381A (ja) * | 1992-11-20 | 1994-06-10 | Fujitsu Ltd | Pllの同期はずれ検出回路 |

| JPH11317663A (ja) * | 1998-05-07 | 1999-11-16 | Sony Corp | Pll回路 |

| JP2006180349A (ja) * | 2004-12-24 | 2006-07-06 | Sharp Corp | 位相同期ループ回路および半導体集積回路 |

| JP2007158472A (ja) * | 2005-11-30 | 2007-06-21 | Kenwood Corp | フェーズロックループ発振器 |

| JP2008035483A (ja) * | 2006-06-29 | 2008-02-14 | Nippon Dempa Kogyo Co Ltd | 周波数シンセサイザ |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4789996A (en) * | 1988-01-28 | 1988-12-06 | Siemens Transmission Systems, Inc. | Center frequency high resolution digital phase-lock loop circuit |

| JP2806239B2 (ja) * | 1993-12-28 | 1998-09-30 | 三菱電機株式会社 | 周波数シンセサイザ |

| US5444420A (en) * | 1994-09-29 | 1995-08-22 | Harris Corporation | Numerically controlled phase lock loop synthesizer/modulator and method |

| US5872486A (en) * | 1997-04-01 | 1999-02-16 | Trimble Navigation Limited | Wide-range fine-step vector modulator frequency synthesizer |

| US6252464B1 (en) * | 1999-10-06 | 2001-06-26 | Cubic Defense Systems, Inc. | Numerically-controlled nyquist-boundary hopping frequency synthesizer |

| US6603362B2 (en) * | 2000-03-14 | 2003-08-05 | Intersil Americas Inc. | Subsampling digitizer-based frequency synthesizer |

| JP4064338B2 (ja) * | 2003-12-10 | 2008-03-19 | 松下電器産業株式会社 | デルタシグマ型分数分周pllシンセサイザ |

| CN100412646C (zh) | 2004-05-08 | 2008-08-20 | 凛宜股份有限公司 | 光源装置 |

| CN1815892B (zh) | 2005-01-31 | 2011-09-28 | 瑞昱半导体股份有限公司 | 一种检测相位误差并产生控制信号的电路 |

| US7949072B2 (en) * | 2005-10-11 | 2011-05-24 | St-Ericsson Sa | Local oscillator with injection pulling suppression and spurious products filtering |

| US7764207B2 (en) * | 2006-03-31 | 2010-07-27 | Nihon Dempa Kogyo Co., Ltd. | Digital processor |

| CN101873135B (zh) * | 2006-03-31 | 2012-11-21 | 日本电波工业株式会社 | 频率合成器 |

| CN101098141B (zh) | 2006-06-29 | 2012-05-30 | 日本电波工业株式会社 | 频率合成器 |

-

2008

- 2008-10-02 JP JP2008257768A patent/JP4787870B2/ja active Active

-

2009

- 2009-09-30 KR KR1020117007663A patent/KR101250571B1/ko active Active

- 2009-09-30 EP EP09817497.2A patent/EP2330743B1/en active Active

- 2009-09-30 WO PCT/JP2009/005053 patent/WO2010038456A1/ja not_active Ceased

- 2009-09-30 BR BRPI0919585-8A patent/BRPI0919585B1/pt active IP Right Grant

- 2009-09-30 US US12/998,086 patent/US8466717B2/en active Active

- 2009-09-30 CN CN2009801394173A patent/CN102171930B/zh active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05227017A (ja) * | 1992-02-10 | 1993-09-03 | Nec Corp | 収束モード切り換え式ディジタルpll装置 |

| JPH06164381A (ja) * | 1992-11-20 | 1994-06-10 | Fujitsu Ltd | Pllの同期はずれ検出回路 |

| JPH11317663A (ja) * | 1998-05-07 | 1999-11-16 | Sony Corp | Pll回路 |

| JP2006180349A (ja) * | 2004-12-24 | 2006-07-06 | Sharp Corp | 位相同期ループ回路および半導体集積回路 |

| JP2007158472A (ja) * | 2005-11-30 | 2007-06-21 | Kenwood Corp | フェーズロックループ発振器 |

| JP2008035483A (ja) * | 2006-06-29 | 2008-02-14 | Nippon Dempa Kogyo Co Ltd | 周波数シンセサイザ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102171930A (zh) | 2011-08-31 |

| KR20110048589A (ko) | 2011-05-11 |

| CN102171930B (zh) | 2013-10-16 |

| EP2330743A1 (en) | 2011-06-08 |

| KR101250571B1 (ko) | 2013-04-03 |

| US8466717B2 (en) | 2013-06-18 |

| BRPI0919585A2 (pt) | 2015-12-08 |

| BRPI0919585B1 (pt) | 2020-03-17 |

| EP2330743B1 (en) | 2019-04-24 |

| US20110169533A1 (en) | 2011-07-14 |

| WO2010038456A1 (ja) | 2010-04-08 |

| JP4787870B2 (ja) | 2011-10-05 |

| EP2330743A4 (en) | 2016-12-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5006417B2 (ja) | Pll発振回路 | |

| US7869554B2 (en) | Phase/frequency estimator-based phase locked loop | |

| CN102291131B (zh) | 频率合成器 | |

| US9853807B2 (en) | Automatic detection of change in PLL locking trend | |

| EP2003780B1 (en) | Pll device | |

| JP4231532B2 (ja) | 周波数シンセサイザ | |

| JP4843704B2 (ja) | 周波数シンセサイザ | |

| US6891413B2 (en) | Periodic signal controller | |

| JP4644302B2 (ja) | 周波数シンセサイザ | |

| JP4787870B2 (ja) | 周波数シンセサイザ | |

| JP5066466B2 (ja) | 周波数シンセサイザ | |

| JP5560781B2 (ja) | 周波数シンセサイザ及び周波数シンセサイザの調整方法 | |

| JP5189436B2 (ja) | 周波数シンセサイザ | |

| JP2007166003A (ja) | Pll回路 | |

| JP2010088056A5 (ja) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110523 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20110523 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110524 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20110610 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110705 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110715 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4787870 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140722 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140722 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |