JP2010056499A - 多層配線基板の製造方法及び多層配線基板 - Google Patents

多層配線基板の製造方法及び多層配線基板 Download PDFInfo

- Publication number

- JP2010056499A JP2010056499A JP2008246431A JP2008246431A JP2010056499A JP 2010056499 A JP2010056499 A JP 2010056499A JP 2008246431 A JP2008246431 A JP 2008246431A JP 2008246431 A JP2008246431 A JP 2008246431A JP 2010056499 A JP2010056499 A JP 2010056499A

- Authority

- JP

- Japan

- Prior art keywords

- film

- electric circuit

- forming

- plating

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Production Of Multi-Layered Print Wiring Board (AREA)

- Manufacturing Of Printed Wiring (AREA)

Abstract

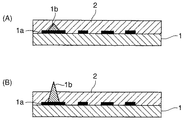

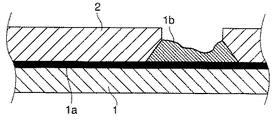

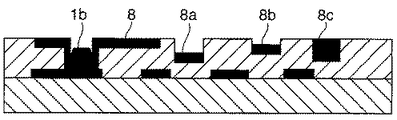

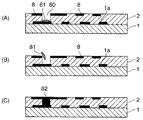

【解決手段】第一電気回路1aに突設された導体柱1bを埋設させるように絶縁層2が形成されてなる導体柱含有回路基板の表面に樹脂皮膜3を形成する皮膜形成工程と、樹脂皮膜の外表面側からレーザー加工することにより、回路溝4を形成及び導体柱1bを露出させる導体柱露出工程と、外表面全体にメッキ触媒6を付着させる触媒付着工程と、樹脂皮膜3を除去する皮膜除去工程と、メッキ触媒6が残留する部位に無電解メッキ膜を形成させることにより、第二電気回路8を形成するとともに導体柱1bにより第一電気回路1aと第二電気回路8との層間接続を形成するメッキ処理工程と、を備える。

【選択図】図1

Description

図1は本実施形態を説明するための工程図である。図1中、1,2は絶縁層(絶縁基材)、1aは第一電気回路、3は樹脂皮膜、4は回路溝、5は貫通孔、6はメッキ触媒、7は無電解メッキ膜、である。また、第一電気回路1aの表面の所定の位置には、略円錐状の導体バンプ(導体柱)1bが形成されている。

第2実施形態では、第一電気回路の所定位置に突設された導体柱を埋設させるように絶縁層が形成されてなる、導体柱含有回路基板の他の製造方法について説明する。なお、導体柱含有回路基板の製造以外の各工程は、第1実施形態と同様の工程が用いられうるので、詳しい説明は省略する。

第3実施形態では、第1実施形態及び第2実施形態で説明したように、樹脂皮膜3を形成する前に形成された導電柱を用いる代わりに、樹脂皮膜を剥離して第二電気回路を形成した後に、層間接続部となる導体柱を形成する方法について説明する。なお、第1実施形態及び第2実施形態で説明したと同様の工程については、詳しい説明は省略する。

「膨潤度SW=(m−m’)/m’×100(%)」の式から、膨潤度を算出する。なお、その他の条件は、JIS L1015 8.27(アルカリ膨潤度の測定方法)に準じて行う。このとき、得られる膨潤度は約750%である。

1a 第一電気回路

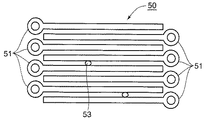

8,8a,8b,8c,51 第二電気回路

1b,62,82 導体柱(導体バンプ)

3 樹脂皮膜

4,202 回路溝

5,60,80,101,203,304 スルーホール(貫通孔)

6,102,204 メッキ触媒

7 無電解メッキ膜

9,69,79 導体柱含有回路基板

10 多層配線基板

50 回路

53 樹脂皮膜の残渣

61,81,305 スミア

103,306 フォトレジスト層

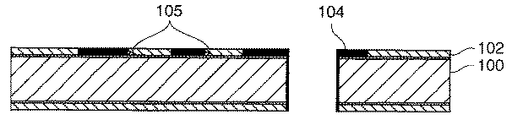

104 金属配線

105 余分なメッキ膜

110 フォトマスク

200,302 絶縁樹脂層

201 保護膜

205 導電層

Claims (15)

- 第一電気回路の所定位置に突設された導体柱を埋設させるように絶縁層が形成されてなる導体柱含有回路基板の、前記導体柱の突設側の絶縁層表面に樹脂皮膜を形成する皮膜形成工程と、

前記樹脂皮膜の外表面側からレーザー加工することにより、少なくとも前記樹脂皮膜の厚み分以上の深さの回路溝を形成する回路溝形成工程と、

前記樹脂皮膜の外表面側からレーザー加工することにより、前記導体柱を露出させる導体柱露出工程と、

前記露出した導体柱,前記回路溝表面及び前記樹脂皮膜の外表面全体にメッキ触媒を付着させる触媒付着工程と、

前記樹脂皮膜を除去する皮膜除去工程と、

前記皮膜除去工程の後に、前記メッキ触媒が残留する部位に無電解メッキ膜を形成させることにより、第二電気回路を形成するとともに前記導体柱により前記第一電気回路と前記第二電気回路との層間接続を形成するメッキ処理工程と、を備えることを特徴とする多層配線基板の製造方法。 - 前記導体柱の露出がレーザー加工により導体柱の頂部の一部を除去させるものである請求項1に記載の多層配線基板の製造方法。

- 前記回路溝が前記樹脂皮膜を通過して、前記絶縁層を掘り込むように形成される請求項1または2に記載の多層配線基板の製造方法。

- 前記樹脂皮膜が蛍光性物質を含有するものであり、前記皮膜除去工程の後、前記蛍光性物質からの発光を用いて皮膜除去不良を検査するための検査工程をさらに備える請求項1〜3の何れか1項に記載の多層配線基板の製造方法。

- 前記樹脂皮膜の厚みが10μm以下である請求項1〜4のいずれか1項に記載の多層配線基板の製造方法。

- 前記樹脂皮膜が、所定の液体に膨潤されることにより前記絶縁層表面から剥離されるような膨潤性樹脂皮膜である請求項1〜5の何れか1項に記載の多層配線基板の製造方法。

- 前記導体柱含有回路基板が、前記第一電気回路の所定位置に予め突設された導体柱の形成面に絶縁層を積層一体化するようにして得られた基板である請求項1〜6の何れか1項に記載の多層配線基板の製造方法。

- 前記導体柱含有回路基板が、前記第一電気回路の所定位置に予め突設された導体柱の形成面に樹脂溶液を塗布した後、硬化させることにより絶縁層を形成して得られた基板である請求項1〜6の何れか1項に記載の多層配線基板の製造方法。

- 前記導体柱含有回路基板が、第一電気回路の表面に絶縁層を形成した後、前記絶縁層の前記第一電気回路の形成面に対する反対面から穴あけ加工することにより、前記第一電気回路を露出させ、露出した前記第一電気回路からメッキ膜を成長形成させることにより穴あけ加工された部分に導体柱を形成することにより得られた基板である請求項1〜6の何れか1項に記載の多層配線基板の製造方法。

- メッキ膜を成長形成させる工程が、穴あけ加工後にデスミア処理した後、露出した前記第一電気回路を電極として、電解メッキによりメッキ膜を成長形成させる工程である請求項9に記載の多層配線基板の製造方法。

- メッキ膜を成長形成させる工程が、穴あけ加工後にデスミア処理した後、露出した前記第一電気回路をメッキ核として、無電解メッキによりメッキ膜を成長形成させる工程である請求項9に記載の多層配線基板の製造方法。

- 基板上に形成された第一電気回路の形成面に絶縁層を形成する絶縁層形成工程と、

前記絶縁層表面に樹脂皮膜を形成する皮膜形成工程と、

前記樹脂皮膜の外表面側からレーザー加工することにより、少なくとも前記樹脂皮膜の厚み分以上の深さの回路溝を形成する回路溝形成工程と、

前記回路溝表面及び前記樹脂皮膜の外表面全体にメッキ触媒を付着させる触媒付着工程と、

前記樹脂皮膜を除去する皮膜除去工程と、

前記皮膜除去工程の後に、前記メッキ触媒が残留する部位に無電解メッキ膜を形成させることにより第二電気回路を形成するメッキ処理工程と、

前記第二電気回路の所定の部分において穴あけ加工することにより、前記第一電気回路を露出させる穴あけ工程と、

露出した前記第一電気回路の表面からメッキ膜を成長形成させることにより穴あけ加工された部分に導体柱を形成することにより前記第一電気回路と前記第二電気回路との層間接続部を形成する層間接続部形成工程と、を備えることを特徴とする多層配線基板の製造方法。 - メッキ膜を成長形成させる工程が、穴あけ加工後にデスミア処理した後、露出した前記第一電気回路を電極として、電解メッキによりメッキ膜を成長形成させる工程である請求項12に記載の多層配線基板の製造方法。

- メッキ膜を成長形成させる工程が、穴あけ加工後にデスミア処理した後、露出した前記第一電気回路の表面をメッキ核として、無電解メッキによりメッキ膜を成長形成させる工程である請求項12に記載の多層配線基板の製造方法。

- 請求項1〜14の何れか1項に記載の製造方法により得られた多層配線基板。

Priority Applications (17)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008246431A JP5172565B2 (ja) | 2008-07-28 | 2008-09-25 | 多層配線基板の製造方法及び多層配線基板 |

| US12/326,169 US8240036B2 (en) | 2008-04-30 | 2008-12-02 | Method of producing a circuit board |

| US12/431,950 US8272126B2 (en) | 2008-04-30 | 2009-04-29 | Method of producing circuit board |

| KR1020117029872A KR20110137408A (ko) | 2008-04-30 | 2009-04-30 | 애디티브법에 의해 회로 기판를 제조하는 방법 및 이 방법에 의해 얻어진 회로 기판과 다층 회로 기판 |

| CN201210362390.8A CN102917550B (zh) | 2008-04-30 | 2009-04-30 | 用加成法制造电路板的方法、以及用该方法获得的电路板和多层电路板 |

| EP13000238.9A EP2592912A1 (en) | 2008-04-30 | 2009-04-30 | Method of producing circuit board by additive method, and circuit board and multilayer circuit board obtained by the method |

| PCT/JP2009/058794 WO2009133969A2 (en) | 2008-04-30 | 2009-04-30 | Method of producing circuit board by additive method, and circuit board and multilayer circuit board obtained by the method |

| KR1020117029869A KR101268727B1 (ko) | 2008-04-30 | 2009-04-30 | 애디티브법에 의해 회로 기판를 제조하는 방법 및 이 방법에 의해 얻어진 회로 기판과 다층 회로 기판 |

| TW098114358A TWI362239B (en) | 2008-04-30 | 2009-04-30 | Method of producing circuit board by additive method, and circuit board and multilayer circuit board obtained by the method |

| HK11101052.0A HK1147013B (en) | 2008-04-30 | 2009-04-30 | Method of producing circuit board by additive method |

| EP12001246.3A EP2469990B1 (en) | 2008-04-30 | 2009-04-30 | Method of producing ciruit board by additive method. |

| CN2009801118173A CN101982024B (zh) | 2008-04-30 | 2009-04-30 | 用加成法制造电路板的方法、以及用该方法获得的电路板和多层电路板 |

| KR1020117029871A KR101183376B1 (ko) | 2008-04-30 | 2009-04-30 | 애디티브법에 의해 회로 기판를 제조하는 방법 및 이 방법에 의해 얻어진 회로 기판과 다층 회로 기판 |

| EP09738906A EP2255601B1 (en) | 2008-04-30 | 2009-04-30 | Method of producing circuit board by additive method |

| KR1020107021143A KR101286867B1 (ko) | 2008-04-30 | 2009-04-30 | 애디티브법에 의해 회로 기판를 제조하는 방법 및 이 방법에 의해 얻어진 회로 기판과 다층 회로 기판 |

| US13/494,417 US9332650B2 (en) | 2008-04-30 | 2012-06-12 | Method of producing multilayer circuit board |

| US13/562,500 US20120292083A1 (en) | 2008-04-30 | 2012-07-31 | Method of producing circuit board by additive method, and circuit board and multilayer circuit board obtained by the method |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008193931 | 2008-07-28 | ||

| JP2008193931 | 2008-07-28 | ||

| JP2008246431A JP5172565B2 (ja) | 2008-07-28 | 2008-09-25 | 多層配線基板の製造方法及び多層配線基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010056499A true JP2010056499A (ja) | 2010-03-11 |

| JP5172565B2 JP5172565B2 (ja) | 2013-03-27 |

Family

ID=42072058

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008246431A Expired - Fee Related JP5172565B2 (ja) | 2008-04-30 | 2008-09-25 | 多層配線基板の製造方法及び多層配線基板 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5172565B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109413872A (zh) * | 2018-11-21 | 2019-03-01 | 奥士康精密电路(惠州)有限公司 | 一种减少pcb板内层短路、残铜的加工方法 |

| WO2020250660A1 (ja) * | 2019-06-14 | 2020-12-17 | ローム株式会社 | 半導体装置及び半導体装置の製造方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63183445A (ja) * | 1987-01-27 | 1988-07-28 | Okuno Seiyaku Kogyo Kk | 水溶性レジストフイルム用剥離剤 |

| JP2000059026A (ja) * | 1998-08-13 | 2000-02-25 | Sony Chem Corp | 両面回路板の製造方法 |

| JP2004048030A (ja) * | 2002-07-15 | 2004-02-12 | Toshiba Corp | 電子回路の製造方法および電子回路の製造装置 |

| JP2007013208A (ja) * | 2006-09-19 | 2007-01-18 | Dainippon Printing Co Ltd | プリント配線基板の製造方法 |

| JP2007088288A (ja) * | 2005-09-22 | 2007-04-05 | Sumitomo Electric Ind Ltd | 回路基板、その製造方法及び多層回路基板 |

-

2008

- 2008-09-25 JP JP2008246431A patent/JP5172565B2/ja not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63183445A (ja) * | 1987-01-27 | 1988-07-28 | Okuno Seiyaku Kogyo Kk | 水溶性レジストフイルム用剥離剤 |

| JP2000059026A (ja) * | 1998-08-13 | 2000-02-25 | Sony Chem Corp | 両面回路板の製造方法 |

| JP2004048030A (ja) * | 2002-07-15 | 2004-02-12 | Toshiba Corp | 電子回路の製造方法および電子回路の製造装置 |

| JP2007088288A (ja) * | 2005-09-22 | 2007-04-05 | Sumitomo Electric Ind Ltd | 回路基板、その製造方法及び多層回路基板 |

| JP2007013208A (ja) * | 2006-09-19 | 2007-01-18 | Dainippon Printing Co Ltd | プリント配線基板の製造方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109413872A (zh) * | 2018-11-21 | 2019-03-01 | 奥士康精密电路(惠州)有限公司 | 一种减少pcb板内层短路、残铜的加工方法 |

| WO2020250660A1 (ja) * | 2019-06-14 | 2020-12-17 | ローム株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP7544696B2 (ja) | 2019-06-14 | 2024-09-03 | ローム株式会社 | 半導体装置及び半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5172565B2 (ja) | 2013-03-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8240036B2 (en) | Method of producing a circuit board | |

| CN1282404C (zh) | 叠层用双面电路板的制法及用其的多层印刷电路板 | |

| KR101183376B1 (ko) | 애디티브법에 의해 회로 기판를 제조하는 방법 및 이 방법에 의해 얻어진 회로 기판과 다층 회로 기판 | |

| TWI400024B (zh) | 配線基板及其製造方法 | |

| US20140166355A1 (en) | Method of manufacturing printed circuit board | |

| TWI481329B (zh) | 貫通孔形成方法及配線電路基板的製造方法 | |

| JPH1187931A (ja) | プリント配線板の製造方法 | |

| JP5172565B2 (ja) | 多層配線基板の製造方法及び多層配線基板 | |

| JP2000036660A (ja) | ビルドアップ多層配線板の製造方法 | |

| JP2013093359A (ja) | 半導体チップ搭載用基板及びその製造方法 | |

| JP4137279B2 (ja) | プリント配線板及びその製造方法 | |

| JP4127213B2 (ja) | 半導体装置用両面配線テープキャリアおよびその製造方法 | |

| JP2010050435A (ja) | 配線基材の製造方法及び該製造方法により得られた配線基材 | |

| JP2009239184A (ja) | 多層印刷配線板 | |

| JPS5922393A (ja) | プリント配線板およびその製造方法 | |

| JP2000036661A (ja) | ビルドアップ多層配線板の製造方法 | |

| JP4045120B2 (ja) | 多層プリント配線板とその製造方法 | |

| JP3716613B2 (ja) | プリント配線板及びその製造方法 | |

| JP2005057077A (ja) | 配線基板の製造方法 | |

| JP2000036662A (ja) | ビルドアップ多層配線板の製造方法 | |

| JP2005333050A (ja) | プリント配線板およびビアフィルめっきを用いたビアホールの形成方法 | |

| JP2002299386A (ja) | 両面配線フィルムキャリア及びその製造方法 | |

| JP2002217536A (ja) | プリント配線板の非貫通孔や貫通孔へのめっき前処理方法 | |

| JP2005294873A (ja) | プリント配線板の製造方法 | |

| JP4144439B2 (ja) | 配線板、多層配線板及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110121 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20120111 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20120427 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20120515 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120814 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120925 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121219 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121226 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5172565 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |