JP2010050847A - 光伝送用並列直列変換器、光伝送システム、及び電子機器 - Google Patents

光伝送用並列直列変換器、光伝送システム、及び電子機器 Download PDFInfo

- Publication number

- JP2010050847A JP2010050847A JP2008214605A JP2008214605A JP2010050847A JP 2010050847 A JP2010050847 A JP 2010050847A JP 2008214605 A JP2008214605 A JP 2008214605A JP 2008214605 A JP2008214605 A JP 2008214605A JP 2010050847 A JP2010050847 A JP 2010050847A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- optical transmission

- parallel

- input terminal

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B6/00—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings

- G02B6/24—Coupling light guides

- G02B6/42—Coupling light guides with opto-electronic elements

- G02B6/43—Arrangements comprising a plurality of opto-electronic elements and associated optical interconnections

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M9/00—Parallel/series conversion or vice versa

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B10/00—Transmission systems employing electromagnetic waves other than radio-waves, e.g. infrared, visible or ultraviolet light, or employing corpuscular radiation, e.g. quantum communication

- H04B10/80—Optical aspects relating to the use of optical transmission for specific applications, not provided for in groups H04B10/03 - H04B10/70, e.g. optical power feeding or optical transmission through water

- H04B10/801—Optical aspects relating to the use of optical transmission for specific applications, not provided for in groups H04B10/03 - H04B10/70, e.g. optical power feeding or optical transmission through water using optical interconnects, e.g. light coupled isolators, circuit board interconnections

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Theoretical Computer Science (AREA)

- Electromagnetism (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Optical Communication System (AREA)

- Optical Couplings Of Light Guides (AREA)

Abstract

【解決手段】本発明のシリアライザー15は、複数の2値信号がそれぞれ並列に入力される複数の入力端子15a・15bを備え、入力された複数の2値信号を、直列の2値信号に変換し、光伝送モジュール1へ伝送するものであり、複数の入力端子15a・15bには、直列の2値信号について、同一の値が所定のビット数連続しないように、“1”信号または“0”信号を挿入するためのビット連続防止用入力端子15aが割り当てられているので、コスト及びサイズの増加なしに、簡単な構成で、ビットの連続防止を実現できる。

【選択図】図1

Description

n<R/fmin …(1)

を満たすものであることが好ましい。

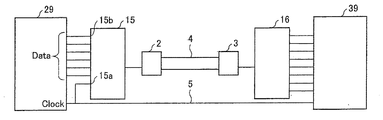

次に図1及び図3を参照して上記光伝送モジュール1の構成について説明する。図3は、本実施の形態に係る携帯電話機40における、光伝送モジュール1の概略構成を示すブロック図である。

次に、光伝送路4の詳細について図4(a)及び図4(b)を用いて説明する。図4(a)は、光伝送路4の側面図を示している。同図に示すように、光伝送路4は、光伝送方向を軸とする柱状形状のコア部4αと、コア部4αの周囲を囲むように設けられたクラッド部4βとを備えた構成となっている。コア部4α及びクラッド部4βは透光性を有する材料によって構成されているとともに、コア部4αの屈折率は、クラッド部4βの屈折率よりも高くなっている。これにより、コア部4αに入射した光信号は、コア部4α内部で全反射を繰り返すことによって光伝送方向に伝送される。

次に、本体部42と蓋部43との間、すなわち主制御基板20とアプリケーション回路基板30との間での情報伝送について、図1、図3を用いて説明すれば、以下の通りである。

光伝送モジュール1の信号伝送は、該モジュールに搭載される光通信用IC(IF回路21、発光駆動部22、検出回路32、増幅部33、I/F回路34)の帯域特性の制約を受けており、信号伝送レートの限界値(以下、伝送可能レートfminとする)が存在する。仕様以外の伝送レートよりも低い、すなわち、光伝送モジュール1の信号伝送レートが伝送可能レートfmin以下である場合、図6に示されるような不具合が生じる。図6は、光伝送モジュール1における、信号伝送レートとエラーレートとの関係を示したグラフである。なお、同図に示された波形図は、光伝送モジュール1の光受信処理部3から出力される信号の波形を示し、6角形で示した領域がエラーレートの規格を示す。すなわち、波形図に示された波形が、上記6角形の領域に重複すると、伝送規格のエラーレート仕様を満たさず、信号伝送レートが悪化することになる。なお、このエラーレートの規格を示す領域は、マスクパターンといわれている。また、マスクパターンは、図6に示される6角形に限定されず、エラーレートの規格に応じて適宜設定されうる。例えば、マスクパターンとしては、図6に示す6角形以外に、ひし形などが挙げられる。

n<R/fmin …(1)

を満たすように、シリアライザー15の入力端子部分にビット連続防止用入力端子が割り当てられている。

信号伝送レートR;450Mbit/s

伝送可能レートfmin;30Mbit/s(低域カットオフ周波数;6MHz)

なお、伝送可能レートfminは、光伝送モジュール1の低域カットオフ周波数の表現で仕様化される場合がある。この伝送可能レートfminと低域カットオフ周波数との関連については、後述する。

n<R/fmin …(1)

を満たすように制限されると、伝送規格のエラーレート仕様を満たし、光伝送モジュール1による信号伝送が成り立つことがわかる。

伝送可能レートfmin=低域カットオフ周波数×m

ここで、mは、光伝送モジュール1に搭載される光通信用ICにおける、低域カットオフ周波数特性を決定するフィルタ構成により決定される。

本実施形態の光伝送システム100の構成において、図1、及び図8に示す構成の他の変形例について説明する。

以下、ビット連続防止用入力端子の割り当ての一例について、説明する。

本実施形態の光伝送システム100の構成において、図1、及び図8に示す構成の他の変形例について説明する。図13は、この変形例2の光伝送システムに備えられたシリアライザー15の構成を示すブロック図である。

なお、本実施形態の光伝送システム100は、例えば以下のような応用例に適用することが可能である。上述した実施形態では、応用例として携帯電話機40に適用した例を用いて説明したが、これに限定されるものではなく、折り畳み式PHS(Personal Handyphone System)、折り畳み式PDA(Personal Digital Assistant)、折り畳み式ノートパソコン等の折り畳み式の電子機器のヒンジ部等にも適用することができる。

2 光送信処理部

21 I/F回路

22 発光駆動部(光変換器)

23 発光部

29 CPU(信号発生部)

3 光受信処理部

31 受光部

32 検出回路

33 増幅部

34 I/F回路

4 光伝送路

5 電気伝送路(電気信号線)

15 シリアライザー(光伝送用並列直列変換器。)

15a ビット連続防止用入力端子

15b データ入力端子

16 デシリアライザー

100 光伝送システム

Claims (17)

- 複数の2値信号がそれぞれ並列に入力される複数の入力端子を備え、入力された複数の2値信号を、直列の2値信号に変換し、光伝送モジュールへ伝送する光伝送用並列直列変換器であって、

上記複数の入力端子には、

上記直列の2値信号について、同一の値が所定のビット数連続しないように、“1”信号または“0”信号を挿入するためのビット連続防止用入力端子が割り当てられていることを特徴とする光伝送用並列直列変換器。 - 上記光伝送モジュールの信号伝送レートの最小値をfminとし、上記直列の2値信号の信号伝送レートをRとしたとき、

上記所定のビット数nは、下記式(1)

n<R/fmin …(1)

を満たすものであることを特徴とする請求項1に記載の光伝送用並列直列変換器。 - 上記ビット連続防止用入力端子として、

“0”の値が所定のビット数連続しないように“1”信号を挿入するための第1のビット連続防止用入力端子、または、

“1”の値が所定のビット数連続しないように“0”信号を挿入するための第2のビット連続防止用入力端子が割り当てられていることを特徴とする請求項1に記載の光伝送用並列直列変換器。 - 上記第1のビット連続防止用入力端子、及び上記第2のビット連続防止用入力端子の両方が割り当てられていることを特徴とする請求項3に記載の光伝送用並列直列変換器。

- 上記複数の入力端子において、上記第1のビット連続防止用入力端子、及び上記第2のビット連続防止用入力端子は、互いに等間隔であり、かつ交互になるように割り当てられていることを特徴とする請求項4に記載の光伝送用並列直列変換器。

- 上記第1のビット連続防止用入力端子、及び上記第2のビット連続防止用入力端子が隣接していることを特徴とする請求項4に記載の光伝送用並列直列変換器。

- 上記第1のビット連続防止用入力端子には、電源電圧が入力されており、

上記第2のビット連続防止用入力端子には、接地電圧が入力されていることを特徴とする請求項3に記載の光伝送用並列直列変換器。 - 電源用端子及び接地用端子をさらに備えており、

上記第1のビット連続防止用入力端子は、上記電源用端子に近接して配置されて接続されており、

上記第2のビット連続防止用入力端子は、上記接地用端子に近接して配置されて接続されていることを特徴とする請求項7に記載の光伝送用並列直列変換器。 - 大部分の期間“0”の値となる上記2値信号が入力される端子を、上記第2のビット連続防止用入力端子として割り当て、

大部分の期間“1”の値となる上記2値信号が入力される端子を、上記第1のビット連続防止用入力端子として割り当てることを特徴とする請求項3に記載の光伝送用並列直列変換器。 - 上記複数の入力端子には、データ信号が入力されるデータ信号入力端子が割り当てられており、

上記ビット連続防止用入力端子には、クロック信号が入力されていることを特徴とする請求項1に記載の光伝送用並列直列変換器。 - 上記クロック信号が、上記データ信号よりも低速であることを特徴とする請求項10に記載の光伝送用並列直列変換器。

- 上記クロック信号が、上記データ信号よりも高速または同速であることを特徴とする請求項10に記載の光伝送用並列直列変換器。

- 上記複数の入力端子には、上記クロック信号の反転信号がさらに入力されていることを特徴とする請求項10に記載の光伝送用並列直列変換器。

- 複数の2値信号をそれぞれ並列に出力する信号発生部と、

上記複数の2値信号を入力し、直列の2値信号に変換する、請求項1に記載の光伝送用並列直列変換器と、

上記光伝送用並列直列変換器から出力した直列の2値信号を光信号に変換する光変換器を有し、該光変換器により変換された光信号を、光伝送路を介して伝送させる光伝送モジュールとを備えたことを特徴とする光伝送システム。 - 上記信号発生部から出力されるデータ信号に対し、該信号発生部から出力されるクロック信号に基づいて制御を行う制御部を備え、

上記信号発生部は、上記データ信号及びクロック信号を、並列の2値信号として出力し、

上記クロック信号を上記信号発生部から上記制御部に伝送する電気信号線をさらに備えており、

上記光伝送用並列直列変換器は、上記電気信号線からの上記クロック信号が上記ビット連続防止用入力端子に入力されていることを特徴とする請求項14に記載の光伝送システム。 - 上記信号発生部から出力されるデータ信号に対し、該信号発生部から出力されるクロック信号に基づいて制御を行う制御部を備え、

上記信号発生部は、上記データ信号及びクロック信号を、並列の2値信号として出力し、

上記光伝送モジュールは、上記光変換器により、少なくともクロック信号を光信号に変換し、該光信号を、光伝送路を介して伝送させ、上記制御部へ出力することを特徴とする請求項14に記載の光伝送システム。 - 請求項14に記載の光伝送システムを備えた電子機器。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008214605A JP4609552B2 (ja) | 2008-08-22 | 2008-08-22 | 光伝送用並列直列変換器、光伝送システム、及び電子機器 |

| EP09808100.3A EP2317655B1 (en) | 2008-08-22 | 2009-02-25 | Parallel-serial converter for optical transmission, optical transmission system, and electronic apparatus |

| PCT/JP2009/053438 WO2010021164A1 (ja) | 2008-08-22 | 2009-02-25 | 光伝送用並列直列変換器、光伝送システム、及び電子機器 |

| CN200980128884.6A CN102106089B (zh) | 2008-08-22 | 2009-02-25 | 用于光传输的并行串行变换器、光传输系统以及电子设备 |

| KR1020107026393A KR101194451B1 (ko) | 2008-08-22 | 2009-02-25 | 광전송용 병렬직렬 변환기, 광전송 시스템, 및 전자 기기 |

| US13/055,746 US8467689B2 (en) | 2008-08-22 | 2009-02-25 | Parallel-serial converter for optical transmission, optical transmission system, and electronic apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008214605A JP4609552B2 (ja) | 2008-08-22 | 2008-08-22 | 光伝送用並列直列変換器、光伝送システム、及び電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010050847A true JP2010050847A (ja) | 2010-03-04 |

| JP4609552B2 JP4609552B2 (ja) | 2011-01-12 |

Family

ID=41707047

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008214605A Expired - Fee Related JP4609552B2 (ja) | 2008-08-22 | 2008-08-22 | 光伝送用並列直列変換器、光伝送システム、及び電子機器 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8467689B2 (ja) |

| EP (1) | EP2317655B1 (ja) |

| JP (1) | JP4609552B2 (ja) |

| KR (1) | KR101194451B1 (ja) |

| CN (1) | CN102106089B (ja) |

| WO (1) | WO2010021164A1 (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014522204A (ja) * | 2011-08-16 | 2014-08-28 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524698A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524699A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524697A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524700A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 送信装置および信号を送信するための方法 |

| JP2014526211A (ja) * | 2011-08-16 | 2014-10-02 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014529932A (ja) * | 2011-08-16 | 2014-11-13 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8578222B2 (en) * | 2011-02-17 | 2013-11-05 | Qualcomm Incorporated | SerDes power throttling as a function of detected error rate |

| JP2013050651A (ja) * | 2011-08-31 | 2013-03-14 | Omron Corp | 光導波路、光伝送モジュールおよび電子機器 |

| CN103454734A (zh) * | 2012-06-05 | 2013-12-18 | 鸿富锦精密工业(深圳)有限公司 | 光传输模组及其传输组件 |

| CN102707226A (zh) * | 2012-07-06 | 2012-10-03 | 电子科技大学 | 一种红外焦平面读出电路的行控制电路的检测电路 |

| CN104813341B (zh) | 2012-10-22 | 2018-04-03 | 李汶基 | 图像处理系统以及图像处理方法 |

| RU2568341C1 (ru) * | 2014-06-05 | 2015-11-20 | Акционерное общество "Концерн радиостроения "Вега" | Способ образования канала для передачи оптического сигнала между компонентами электронного модуля |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001268039A (ja) * | 2000-03-22 | 2001-09-28 | Mitsubishi Electric Corp | Sdh伝送システム |

| JP2005064888A (ja) * | 2003-08-13 | 2005-03-10 | Fuji Xerox Co Ltd | 誤り訂正符号付き信号伝送システム |

| JP2005311523A (ja) * | 2004-04-19 | 2005-11-04 | Fuji Electric Systems Co Ltd | 光通信制御装置 |

| JP2006114987A (ja) * | 2004-10-12 | 2006-04-27 | Seiko Epson Corp | トランシーバ、データ転送制御装置及び電子機器 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09307457A (ja) * | 1996-05-14 | 1997-11-28 | Sony Corp | パラレルシリアル変換回路 |

| US6081360A (en) | 1997-08-20 | 2000-06-27 | Fujitsu Limited | Method and apparatus for optimizing dispersion in an optical fiber transmission line in accordance with an optical signal power level |

| JP3497435B2 (ja) * | 2000-02-18 | 2004-02-16 | 日本電信電話株式会社 | データ伝送誤り監視システム、データ送信装置、データ受信装置およびデータ伝送誤り監視方法 |

| US7170870B2 (en) * | 2002-05-07 | 2007-01-30 | Microsoft Corporation | Data packet transmission for channel-sharing collocated wireless devices |

| JP4192802B2 (ja) * | 2003-08-07 | 2008-12-10 | セイコーエプソン株式会社 | デジタル映像通信装置 |

| DE60322082D1 (de) * | 2003-12-17 | 2008-08-21 | Alcatel Lucent | Optimierte Codeverschachtelung digitaler Signale |

| JP3822632B2 (ja) * | 2004-04-16 | 2006-09-20 | ザインエレクトロニクス株式会社 | 送信回路、受信回路及びクロック抽出回路並びにデータ伝送方法及びデータ伝送システム |

-

2008

- 2008-08-22 JP JP2008214605A patent/JP4609552B2/ja not_active Expired - Fee Related

-

2009

- 2009-02-25 EP EP09808100.3A patent/EP2317655B1/en not_active Not-in-force

- 2009-02-25 WO PCT/JP2009/053438 patent/WO2010021164A1/ja active Application Filing

- 2009-02-25 US US13/055,746 patent/US8467689B2/en not_active Expired - Fee Related

- 2009-02-25 KR KR1020107026393A patent/KR101194451B1/ko not_active IP Right Cessation

- 2009-02-25 CN CN200980128884.6A patent/CN102106089B/zh not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001268039A (ja) * | 2000-03-22 | 2001-09-28 | Mitsubishi Electric Corp | Sdh伝送システム |

| JP2005064888A (ja) * | 2003-08-13 | 2005-03-10 | Fuji Xerox Co Ltd | 誤り訂正符号付き信号伝送システム |

| JP2005311523A (ja) * | 2004-04-19 | 2005-11-04 | Fuji Electric Systems Co Ltd | 光通信制御装置 |

| JP2006114987A (ja) * | 2004-10-12 | 2006-04-27 | Seiko Epson Corp | トランシーバ、データ転送制御装置及び電子機器 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014522204A (ja) * | 2011-08-16 | 2014-08-28 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524698A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524699A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524697A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014524700A (ja) * | 2011-08-16 | 2014-09-22 | シリコン・ライン・ゲー・エム・ベー・ハー | 送信装置および信号を送信するための方法 |

| JP2014526211A (ja) * | 2011-08-16 | 2014-10-02 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

| JP2014529932A (ja) * | 2011-08-16 | 2014-11-13 | シリコン・ライン・ゲー・エム・ベー・ハー | 回路装置および信号を送信するための方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2317655B1 (en) | 2014-05-07 |

| EP2317655A1 (en) | 2011-05-04 |

| US8467689B2 (en) | 2013-06-18 |

| KR101194451B1 (ko) | 2012-10-25 |

| US20110123201A1 (en) | 2011-05-26 |

| EP2317655A4 (en) | 2012-06-20 |

| CN102106089A (zh) | 2011-06-22 |

| CN102106089B (zh) | 2013-03-20 |

| WO2010021164A1 (ja) | 2010-02-25 |

| KR20110009176A (ko) | 2011-01-27 |

| JP4609552B2 (ja) | 2011-01-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4609552B2 (ja) | 光伝送用並列直列変換器、光伝送システム、及び電子機器 | |

| JP4968330B2 (ja) | 光伝送モジュールおよび電子機器 | |

| JP5136374B2 (ja) | 光伝送システム及びそれを備えた電子機器 | |

| US8428402B2 (en) | Optical transmission module, electronic device, and method for manufacturing optical transmission module | |

| JP4894917B2 (ja) | 光伝送モジュール | |

| KR20120091320A (ko) | 반도체 장치 및 메모리 시스템 | |

| JP5454641B2 (ja) | 光伝送モジュール | |

| US8457455B2 (en) | Optical waveguide, optical waveguide module, and electronic apparatus | |

| JP4965135B2 (ja) | 光伝送路、光伝送モジュール、および電子機器 | |

| US8639068B2 (en) | Optical transmission module, electronic instrument, method for assembling optical transmission module, and optical transmission method | |

| US10761282B2 (en) | Optical-electrical hybrid module | |

| KR102586479B1 (ko) | 디스플레이를 위한 데이터 구동 장치 | |

| JPWO2008114676A1 (ja) | 光伝送システム及び電子機器 | |

| JP2010081267A (ja) | データ伝送装置、送信器および受信器 | |

| JP2003069654A (ja) | データ伝送方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100511 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100722 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20100818 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100914 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100927 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees | ||

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D04 |