JP2010045566A - 非可逆回路素子 - Google Patents

非可逆回路素子 Download PDFInfo

- Publication number

- JP2010045566A JP2010045566A JP2008207836A JP2008207836A JP2010045566A JP 2010045566 A JP2010045566 A JP 2010045566A JP 2008207836 A JP2008207836 A JP 2008207836A JP 2008207836 A JP2008207836 A JP 2008207836A JP 2010045566 A JP2010045566 A JP 2010045566A

- Authority

- JP

- Japan

- Prior art keywords

- ferrite

- circuit board

- electrode

- resistor

- nonreciprocal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Abstract

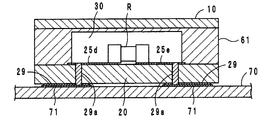

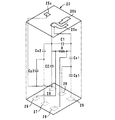

【解決手段】平板状ヨーク10と、永久磁石41と、該永久磁石41により直流磁界が印加されるフェライト32と、該フェライト32に配置された第1中心電極及び第2中心電極と、回路基板20とを備えた非可逆回路素子(2ポート型アイソレータ)。終端抵抗Rはチップ型素子であり、回路基板20上の端子電極25d,25eに接続されている。端子電極25d,25eは回路基板20の裏面に形成した放熱用電極29とスルーホール導体29aを介して接続されている。放熱用電極29は終端抵抗R以外の素子には接続されていない。

【選択図】図1

Description

永久磁石と、

前記永久磁石により直流磁界が印加されるフェライトと、

前記フェライトに互いに電気的に絶縁状態で交差して配置された第1中心電極及び第2中心電極と、

前記永久磁石及び前記フェライトを実装した回路基板と、

を備え、

前記第1中心電極は、一端が入力ポートに電気的に接続され、他端が出力ポートに電気的に接続され、

前記第2中心電極は、一端が出力ポートに電気的に接続され、他端がグランドポートに電気的に接続され、

前記入力ポートと前記出力ポートとの間に第1整合容量が電気的に接続され、

前記出力ポートと前記グランドポートとの間に第2整合容量が電気的に接続され、

前記入力ポートと前記出力ポートとの間に抵抗が電気的に接続され、

前記抵抗の両端部は前記回路基板の実装面に設けた放熱用電極に接続されて、該放熱用電極は前記抵抗以外の素子には接続されていないこと、

を特徴とする。

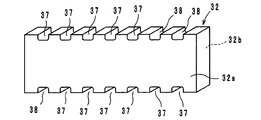

本発明に係る非可逆回路素子の第1実施例である2ポート型アイソレータの分解斜視図を図1に示す。この2ポート型アイソレータは、集中定数型アイソレータであり、概略、平板状ヨーク10と、回路基板20と、フェライト32と永久磁石41とからなるフェライト・磁石素子30とで構成されている。なお、図1において、斜線を付した部分は導電体である。

第2実施例であるアイソレータは、図8に示すように、回路基板20の表面に設けた端子電極25d,25eと裏面に設けた放熱用電極29とを、回路基板20の角部に設けたスルーホール導体29aを介して接続したものである。

第3実施例であるアイソレータは、図10に示すように、回路基板20の裏面(実装面)に放熱用電極29を対角線上に配置したものである。放熱用電極29を互いに遠ざけて配置することにより、むらのない放熱が期待できる。

なお、前記終端抵抗Rはチップ型素子を回路基板20の表面に外付けする以外に、回路基板20の表面又は内部に形成された抵抗体膜であってもよい。このような抵抗体膜で形成された終端抵抗であっても、回路基板20の裏面(実装面)に設けた放熱用電極にスルーホール導体を介して接続することにより、放熱性を改善することができる。

なお、本発明に係る非可逆回路素子は前記実施例に限定するものではなく、その要旨の範囲内で種々に変更することができる。

20…回路基板

25d,25e…端子電極

29…放熱用電極

29a…スルーホール導体

30…フェライト・磁石素子

32…フェライト

35…第1中心電極

36…第2中心電極

41…永久磁石

45,46…抵抗体膜

61…樹脂材

R…終端抵抗

P1…入力ポート

P2…出力ポート

P3…グランドポート

Claims (11)

- 永久磁石と、

前記永久磁石により直流磁界が印加されるフェライトと、

前記フェライトに互いに電気的に絶縁状態で交差して配置された第1中心電極及び第2中心電極と、

前記永久磁石及び前記フェライトを実装した回路基板と、

を備え、

前記第1中心電極は、一端が入力ポートに電気的に接続され、他端が出力ポートに電気的に接続され、

前記第2中心電極は、一端が出力ポートに電気的に接続され、他端がグランドポートに電気的に接続され、

前記入力ポートと前記出力ポートとの間に第1整合容量が電気的に接続され、

前記出力ポートと前記グランドポートとの間に第2整合容量が電気的に接続され、

前記入力ポートと前記出力ポートとの間に抵抗が電気的に接続され、

前記抵抗の両端部は前記回路基板の実装面に設けた放熱用電極に接続されて、該放熱用電極は前記抵抗以外の素子には接続されていないこと、

を特徴とする非可逆回路素子。 - 前記抵抗はチップ型素子であって前記回路基板の表面に実装されていることを特徴とする請求項1に記載の非可逆回路素子。

- 前記抵抗は前記回路基板の表面又は内部に形成された抵抗体膜であることを特徴とする請求項1に記載の非可逆回路素子。

- 前記放熱用電極は前記回路基板の実装面にほぼ対角線上に配置されていることを特徴とする請求項1ないし請求項3に記載の非可逆回路素子。

- 前記抵抗と前記放熱用電極とは前記回路基板に設けたスルーホール導体によって接続されていることを特徴とする請求項1ないし請求項4のいずれかに記載の非可逆回路素子。

- 前記スルーホール導体はスルーホールに充填されていることを特徴とする請求項5に記載の非可逆回路素子。

- 前記スルーホール導体は前記回路基板の角部に設けられていることを特徴とする請求項5又は請求項6に記載の非可逆回路素子。

- 前記フェライトと前記永久磁石は、前記第1及び第2中心電極が配置されたフェライトの主面に永久磁石が固着されたフェライト・磁石素子を構成していること、を特徴とする請求項1ないし請求項7のいずれかに記載の非可逆回路素子。

- 前記フェライト・磁石素子は、前記回路基板上に実装されるとともにその直上にヨークが配置され、かつ、樹脂材にて覆われていること、を特徴とする請求項8に記載の非可逆回路素子。

- 前記フェライト・磁石素子は、前記回路基板上に、フェライトの主面が回路基板の表面に対して垂直方向に配置されていること、を特徴とする請求項8又は請求項9に記載の非可逆回路素子。

- 前記第2中心電極は前記フェライトの両主面に少なくとも2ターン巻回されていることを特徴とする請求項1ないし請求項10のいずれかに記載の非可逆回路素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008207836A JP5083113B2 (ja) | 2008-08-12 | 2008-08-12 | 非可逆回路素子 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008207836A JP5083113B2 (ja) | 2008-08-12 | 2008-08-12 | 非可逆回路素子 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010045566A true JP2010045566A (ja) | 2010-02-25 |

| JP5083113B2 JP5083113B2 (ja) | 2012-11-28 |

Family

ID=42016584

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008207836A Expired - Fee Related JP5083113B2 (ja) | 2008-08-12 | 2008-08-12 | 非可逆回路素子 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5083113B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2015093273A1 (ja) * | 2013-12-18 | 2015-06-25 | 株式会社村田製作所 | 非可逆回路素子 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62293806A (ja) * | 1986-06-12 | 1987-12-21 | Nec Corp | 超高周波電圧制御発振器のバラクタダイオード取付け構造 |

| JPH0887788A (ja) * | 1994-09-14 | 1996-04-02 | Matsushita Electric Ind Co Ltd | 磁気記録再生装置 |

| JPH10284907A (ja) * | 1997-04-10 | 1998-10-23 | Murata Mfg Co Ltd | 非可逆回路素子 |

| JP2004088743A (ja) * | 2002-06-27 | 2004-03-18 | Murata Mfg Co Ltd | 2ポート型アイソレータおよび通信装置 |

| JP2004241944A (ja) * | 2003-02-04 | 2004-08-26 | Murata Mfg Co Ltd | 非可逆回路素子、非可逆回路素子の実装構造および通信装置 |

-

2008

- 2008-08-12 JP JP2008207836A patent/JP5083113B2/ja not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62293806A (ja) * | 1986-06-12 | 1987-12-21 | Nec Corp | 超高周波電圧制御発振器のバラクタダイオード取付け構造 |

| JPH0887788A (ja) * | 1994-09-14 | 1996-04-02 | Matsushita Electric Ind Co Ltd | 磁気記録再生装置 |

| JPH10284907A (ja) * | 1997-04-10 | 1998-10-23 | Murata Mfg Co Ltd | 非可逆回路素子 |

| JP2004088743A (ja) * | 2002-06-27 | 2004-03-18 | Murata Mfg Co Ltd | 2ポート型アイソレータおよび通信装置 |

| JP2004241944A (ja) * | 2003-02-04 | 2004-08-26 | Murata Mfg Co Ltd | 非可逆回路素子、非可逆回路素子の実装構造および通信装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2015093273A1 (ja) * | 2013-12-18 | 2015-06-25 | 株式会社村田製作所 | 非可逆回路素子 |

| US10033079B2 (en) | 2013-12-18 | 2018-07-24 | Murata Manufacturing Co., Ltd. | Non-reciprocal circuit element |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5083113B2 (ja) | 2012-11-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2184802B1 (en) | Irreversible circuit element | |

| JP4656186B2 (ja) | 非可逆回路素子及び複合電子部品の製造方法 | |

| JP4858543B2 (ja) | 非可逆回路素子及びその製造方法 | |

| JP4692679B2 (ja) | 非可逆回路素子 | |

| JP4155342B1 (ja) | 非可逆回路素子 | |

| JP5018790B2 (ja) | 非可逆回路素子 | |

| JP4793350B2 (ja) | 2ポート型非可逆回路素子 | |

| JP4858542B2 (ja) | 非可逆回路素子 | |

| JP5083113B2 (ja) | 非可逆回路素子 | |

| JP2009302742A (ja) | 非可逆回路素子 | |

| JP2011055222A (ja) | 非可逆回路素子 | |

| JP5098813B2 (ja) | 非可逆回路素子及び複合電子部品 | |

| JP4760981B2 (ja) | 非可逆回路素子 | |

| JP4831234B2 (ja) | 非可逆回路素子 | |

| JP4844625B2 (ja) | 非可逆回路素子 | |

| JP4915366B2 (ja) | 非可逆回路素子 | |

| JP4929488B2 (ja) | 非可逆回路素子 | |

| JP4811519B2 (ja) | 非可逆回路素子 | |

| JP2010034776A (ja) | 非可逆回路素子 | |

| JP5652116B2 (ja) | 非可逆回路素子 | |

| JP2009296051A (ja) | フェライト・磁石素子、非可逆回路素子及び複合電子部品 | |

| JP4807457B2 (ja) | 非可逆回路素子 | |

| JP2010183130A (ja) | 非可逆回路部品及びその製造方法 | |

| WO2011083792A1 (ja) | 回路モジュール | |

| JP2010147853A (ja) | 非可逆回路素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110711 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120704 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120807 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120820 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5083113 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |