JP2010010371A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2010010371A JP2010010371A JP2008167620A JP2008167620A JP2010010371A JP 2010010371 A JP2010010371 A JP 2010010371A JP 2008167620 A JP2008167620 A JP 2008167620A JP 2008167620 A JP2008167620 A JP 2008167620A JP 2010010371 A JP2010010371 A JP 2010010371A

- Authority

- JP

- Japan

- Prior art keywords

- pmosfet

- active region

- film

- nmosfet

- compressive stress

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/12—Static random access memory [SRAM] devices comprising a MOSFET load element

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

- H10D30/792—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions comprising applied insulating layers, e.g. stress liners

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

- H10D30/795—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions being in lateral device isolation regions, e.g. STI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0167—Manufacturing their channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0188—Manufacturing their isolation regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H10P14/69433—

-

- H10W20/075—

-

- H10W74/147—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0212—Manufacture or treatment of FETs having insulated gates [IGFET] using self-aligned silicidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0223—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate

- H10D30/0227—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate having both lightly-doped source and drain extensions and source and drain regions self-aligned to the sides of the gate, e.g. lightly-doped drain [LDD] MOSFET or double-diffused drain [DDD] MOSFET

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Semiconductor Memories (AREA)

- Chemical Vapour Deposition (AREA)

- Element Separation (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

Abstract

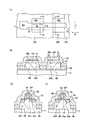

【解決手段】半導体装置は、NMOSFET用活性領域AR1、PMOSFET用活性領域AR2を画定する素子分離溝STと、素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜OXと、NMOSFET領域AR1に形成されたNMOSFETと、PMOSFET領域AR2に形成されたPMOSFETと、NMOSFET構造を覆い、NMOSFET用活性領域AR1の周囲における凹部上及びPMOSFET用活性領域AR2のゲート幅方向外側における凹部上に延在して形成された引張応力膜TSFと、PMOSFET構造を覆い、PMOSFET用活性領域AR2のチャネル長方向外側における凹部上に延在して形成された圧縮応力膜CSFとを有する。

【選択図】図1

Description

半導体基板と、

前記半導体基板表面部に形成され、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝と、

前記素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜と、

前記NMOSFET用活性領域に形成され、絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造と、

前記PMOSFET用活性領域に形成され、絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造と、

前記NMOSFET構造を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のゲート幅方向外側における前記凹部上に延在して形成された引張応力膜と、

前記PMOSFET構造を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在して形成された圧縮応力膜と、

を有する半導体装置

が提供される。

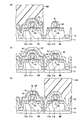

(a)半導体基板表面部に、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝を形成する工程と;

(b)前記素子分離溝に圧縮応力を有する酸化シリコン膜を埋め込む工程と、

(c)NMOSFET用活性領域に絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造、前記PMOSFET用活性領域に絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造を形成する工程と;

(d)前記素子分離溝に埋め込まれた酸化シリコン膜の上部を除去し、凹部を形成する工程と、

(e)前記NMOSFET用活性領域を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のチャネル幅方向外側における前記凹部上に延在する引張応力絶縁膜を形成する工程と、

(f)前記PMOSFET用活性領域を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在する圧縮応力絶縁膜を形成する工程と、

を含む半導体装置の製造方法

が提供される。

12 酸化シリコン膜、

13 窒化シリコン膜、

14 酸化シリコン膜、

AR 活性領域、

ST 素子分離溝、

TSF 引張応力膜、

CSF 圧縮応力膜、

EX エクステンション領域、

SD ソース/ドレイン領域、

PW p型ウェル、

NW n型ウェル、

15 ゲート絶縁膜、

16 ゲート電極(多結晶シリコン膜)、

18 引張応力窒化シリコン膜、

19 酸化シリコン膜、

20 圧縮応力窒化シリコン膜、

21 エクステンション領域、

22 ソース/ドレイン拡散層、

SW サイドウォール、

SL シリサイド領域、

Claims (10)

- 半導体基板と、

前記半導体基板表面部に形成され、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝と、

前記素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜と、

前記NMOSFET用活性領域に形成され、絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造と、

前記PMOSFET用活性領域に形成され、絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造と、

前記NMOSFET構造を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のゲート幅方向外側における前記凹部上に延在して形成された引張応力膜と、

前記PMOSFET構造を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在して形成された圧縮応力膜と、

を有する半導体装置。 - 前記NMOSFET構造と前記PMOSFET構造とが平行なチャネル長方向を有し、前記引張応力膜、前記圧縮応力膜が前記チャネル長方向に沿ったストライプ状に形成されている請求項1記載の半導体装置。

- 前記凹部の深さは、前記ソース/ドレイン領域より深く、前記素子分離溝の深さの半分以下である請求項1または2記載の半導体装置。

- 前記引張応力膜、前記圧縮応力膜が接している請求項1〜3のいずれか1項記載の半導体装置。

- 前記引張応力膜、圧縮応力膜が窒化シリコン膜である請求項1〜4のいずれか1項記載の半導体装置。

- (a)半導体基板表面部に、NMOSFET用活性領域、PMOSFET用活性領域を画定する素子分離溝を形成する工程と;

(b)前記素子分離溝に圧縮応力を有する酸化シリコン膜を埋め込む工程と、

(c)NMOSFET用活性領域に絶縁ゲート電極構造、n型ソース/ドレイン領域を有するNMOSFET構造、前記PMOSFET用活性領域に絶縁ゲート電極構造、p型ソース/ドレイン領域を有するPMOSFET構造を形成する工程と;

(d)前記素子分離溝に埋め込まれた酸化シリコン膜の上部を除去し、凹部を形成する工程と、

(e)前記NMOSFET用活性領域を覆い、前記NMOSFET用活性領域周囲の前記凹部上及び前記PMOSFET用活性領域のチャネル幅方向外側における前記凹部上に延在する引張応力絶縁膜を形成する工程と、

(f)前記PMOSFET用活性領域を覆い、前記PMOSFET用活性領域のチャネル長方向外側における前記凹部上に延在する圧縮応力絶縁膜を形成する工程と、

を含む半導体装置の製造方法。 - 前記工程(e)が、前記半導体基板上に引張応力絶縁膜を堆積し、前記PMOSFET用活性領域、および前記PMOSFET用活性領域のチャネル長方向外側における前記凹部の上から前記引張応力絶縁膜を除去し、

前記工程(f)が、前記半導体基板上に圧縮応力絶縁膜を堆積し、前記NMOSFET用活性領域、前記NMOSFET用活性領域周囲の前記凹部及び前記PMOSFET用活性領域のチャネル幅方向外側における前記凹部の上から前記圧縮応力絶縁膜を除去する、

請求項6記載の半導体装置の製造方法。 - 前記工程(e)における引張応力膜、前記工程(f)における圧縮応力膜が、窒化シリコン膜である請求項7記載の半導体装置の製造方法。

- 前記工程(e)が、前記引張応力膜を熱CVDで形成し、前記工程(f)が前記圧縮応力膜をプラズマCVDで形成する請求項8記載の半導体装置の製造方法。

- 前記工程(e)、(f)の内、先に行われる工程が前記窒化シリコン膜の上に酸化シリコンカバー膜を堆積し、前記酸化シリコンカバー膜を前記窒化シリコン膜と同一パターンにエッチングし、前記工程(e)、(f)の内、後に行われる工程が前記酸化シリコンカバー膜をエッチングストッパとして使用する請求項8又は9記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008167620A JP5163311B2 (ja) | 2008-06-26 | 2008-06-26 | 半導体装置及びその製造方法 |

| US12/411,602 US8030710B2 (en) | 2008-06-26 | 2009-03-26 | Strained semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008167620A JP5163311B2 (ja) | 2008-06-26 | 2008-06-26 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010371A true JP2010010371A (ja) | 2010-01-14 |

| JP5163311B2 JP5163311B2 (ja) | 2013-03-13 |

Family

ID=41446347

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008167620A Expired - Fee Related JP5163311B2 (ja) | 2008-06-26 | 2008-06-26 | 半導体装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8030710B2 (ja) |

| JP (1) | JP5163311B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8218353B1 (en) * | 2009-09-16 | 2012-07-10 | Altera Corporation | Memory element circuitry with stressed transistors |

| DE102010038746B4 (de) | 2010-07-30 | 2013-11-14 | GLOBALFOUNDRIES Dresden Module One Ltd. Liability Company & Co. KG | Verfahren zum Reduzieren der Topographie in Isolationsgebieten eines Halbleiterbauelements durch Anwenden einer Abscheide/Ätzsequenz vor der Herstellung des Zwischenschichtdielektrikums |

| US8453100B2 (en) * | 2010-09-01 | 2013-05-28 | International Business Machines Corporation | Circuit analysis using transverse buckets |

| US8378428B2 (en) * | 2010-09-29 | 2013-02-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal gate structure of a semiconductor device |

| CN102881694A (zh) | 2011-07-14 | 2013-01-16 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| CN106910739B (zh) * | 2015-12-21 | 2022-01-11 | 三星电子株式会社 | 半导体器件 |

| KR102375583B1 (ko) * | 2015-12-21 | 2022-03-16 | 삼성전자주식회사 | 반도체 장치 및 이의 제조 방법 |

| US10043903B2 (en) * | 2015-12-21 | 2018-08-07 | Samsung Electronics Co., Ltd. | Semiconductor devices with source/drain stress liner |

| US10736557B2 (en) | 2016-03-30 | 2020-08-11 | Brain F.I.T. Imaging, LLC | Methods and magnetic imaging devices to inventory human brain cortical function |

| KR102524806B1 (ko) | 2016-08-11 | 2023-04-25 | 삼성전자주식회사 | 콘택 구조체를 포함하는 반도체 소자 |

| US11337631B2 (en) | 2017-10-03 | 2022-05-24 | Brainn F.I.T. Imaging, LLC | Methods and magnetic imaging devices to inventory human brain cortical function |

| US11832966B2 (en) | 2019-04-03 | 2023-12-05 | Brain F.I.T. Imaging, LLC | Methods and magnetic imaging devices to inventory human brain cortical function |

| FR3100084B1 (fr) * | 2019-08-23 | 2021-10-01 | Commissariat Energie Atomique | procédé de fabrication de composants micro-électroniques |

| US11450573B2 (en) * | 2020-06-17 | 2022-09-20 | Globalfoundries U.S. Inc. | Structure with different stress-inducing isolation dielectrics for different polarity FETs |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003158241A (ja) * | 2001-11-26 | 2003-05-30 | Hitachi Ltd | 半導体装置及び製造方法 |

| JP2006229071A (ja) * | 2005-02-18 | 2006-08-31 | Fujitsu Ltd | 半導体装置 |

| JP2006278754A (ja) * | 2005-03-29 | 2006-10-12 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006286889A (ja) * | 2005-03-31 | 2006-10-19 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2008053518A (ja) * | 2006-08-25 | 2008-03-06 | Sony Corp | 半導体装置 |

| JP2008066484A (ja) * | 2006-09-06 | 2008-03-21 | Fujitsu Ltd | Cmos半導体装置とその製造方法 |

| JP2009527928A (ja) * | 2006-02-24 | 2009-07-30 | フリースケール セミコンダクター インコーポレイテッド | ソース/ドレインストレッサ、及び中間誘電体層ストレッサを統合する半導体の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003086708A (ja) | 2000-12-08 | 2003-03-20 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP4994581B2 (ja) | 2004-06-29 | 2012-08-08 | 富士通セミコンダクター株式会社 | 半導体装置 |

| US7600207B2 (en) * | 2006-02-27 | 2009-10-06 | Synopsys, Inc. | Stress-managed revision of integrated circuit layouts |

| US20080237733A1 (en) * | 2007-03-27 | 2008-10-02 | International Business Machines Corporation | Structure and method to enhance channel stress by using optimized sti stress and nitride capping layer stress |

-

2008

- 2008-06-26 JP JP2008167620A patent/JP5163311B2/ja not_active Expired - Fee Related

-

2009

- 2009-03-26 US US12/411,602 patent/US8030710B2/en not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003158241A (ja) * | 2001-11-26 | 2003-05-30 | Hitachi Ltd | 半導体装置及び製造方法 |

| JP2006229071A (ja) * | 2005-02-18 | 2006-08-31 | Fujitsu Ltd | 半導体装置 |

| JP2006278754A (ja) * | 2005-03-29 | 2006-10-12 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006286889A (ja) * | 2005-03-31 | 2006-10-19 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2009527928A (ja) * | 2006-02-24 | 2009-07-30 | フリースケール セミコンダクター インコーポレイテッド | ソース/ドレインストレッサ、及び中間誘電体層ストレッサを統合する半導体の製造方法 |

| JP2008053518A (ja) * | 2006-08-25 | 2008-03-06 | Sony Corp | 半導体装置 |

| JP2008066484A (ja) * | 2006-09-06 | 2008-03-21 | Fujitsu Ltd | Cmos半導体装置とその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090321840A1 (en) | 2009-12-31 |

| US8030710B2 (en) | 2011-10-04 |

| JP5163311B2 (ja) | 2013-03-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5163311B2 (ja) | 半導体装置及びその製造方法 | |

| US8102030B2 (en) | Semiconductor device with strain | |

| JP4814304B2 (ja) | 集積回路およびその製造方法 | |

| US8680576B2 (en) | CMOS device and method of forming the same | |

| US7652346B2 (en) | Semiconductor device and manufacturing method thereof | |

| CN100461456C (zh) | 半导体器件及其制造方法 | |

| CN101369598A (zh) | 半导体结构 | |

| CN101310386A (zh) | 用于高迁移率平面和多栅极mosfet的混合衬底技术 | |

| CN1956222B (zh) | 半导体装置及其制造方法 | |

| CN100576547C (zh) | 具有拉应力膜和压应力膜的cmos半导体器件 | |

| JP5268859B2 (ja) | 半導体装置 | |

| US7737495B2 (en) | Semiconductor device having inter-layers with stress levels corresponding to the transistor type | |

| JP2012160637A (ja) | 半導体装置及びその製造方法、並びにsoi基板及びその製造方法 | |

| US7692243B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP2006005294A (ja) | 半導体装置 | |

| JP2004193166A (ja) | 半導体装置 | |

| KR20090020847A (ko) | 스트레인드 채널을 갖는 모스 트랜지스터의 제조 방법 및그에 의해 제조된 모스 트랜지스터 | |

| JP4939548B2 (ja) | 半導体デバイス構造体を製造するための方法 | |

| JP2010098157A (ja) | 半導体装置の製造方法 | |

| JP2007324391A (ja) | 半導体装置及びその製造方法 | |

| JP5132943B2 (ja) | 半導体装置 | |

| JP2007173356A (ja) | 半導体装置およびその製造方法 | |

| JP4942951B2 (ja) | Mos型トランジスタの製造方法及びmos型トランジスタ | |

| JP4630235B2 (ja) | 半導体装置及びその製造方法 | |

| CN117542738A (zh) | 一种半导体器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121112 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121120 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121203 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5163311 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |