JP2010003741A - 半導体装置及び半導体装置の製造方法 - Google Patents

半導体装置及び半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2010003741A JP2010003741A JP2008159043A JP2008159043A JP2010003741A JP 2010003741 A JP2010003741 A JP 2010003741A JP 2008159043 A JP2008159043 A JP 2008159043A JP 2008159043 A JP2008159043 A JP 2008159043A JP 2010003741 A JP2010003741 A JP 2010003741A

- Authority

- JP

- Japan

- Prior art keywords

- film

- ferroelectric

- protective film

- capacitor

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Semiconductor Memories (AREA)

Abstract

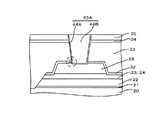

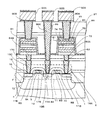

【解決手段】シリコン基板1上に強誘電体キャパシタ31を形成する際、第2電極膜25

上にハードマスクとして第1保護膜27を形成する。第1保護膜27をマスクにして第2

電極膜25をエッチングして上部電極28を形成する。この後、第1保護膜27を除去せ

ずに、第1保護膜27を膜表面側から酸化させる。これによって、第1保護膜27は、積

層方向上側の上部領域の酸素濃度が他の領域に比べて高くなり、水素や水などの還元性物

質が強誘電体キャパシタ31に透過することを防止する拡散防止膜となる。

【選択図】図1F

Description

電体キャパシタとメモリセルトランジスタとを備えた半導体装置及びその製造方法に関す

る。

ることが行われており、電子機器等に使用される半導体装置の高集積化及び高性能化が要

求されている。例えば、半導体装置の一例である半導体記憶装置においては、DRAM(

Dynamic Random Access Memory)を高集積化することが行われている。このようなDRA

Mに使用されるキャパシタの容量絶縁膜としては、従来の珪素酸化物又は珪素窒化物に代

えて、強誘電体材料又は高誘電率材料が用いられている。また、より低電圧、且つ高速で

の書き込み動作及び読み出し動作が可能な不揮発性RAMを実現するため、自発分極特性

を有する強誘電体膜を容量絶縁膜に用いている。このような半導体記憶装置は、一般に強

誘電体メモリ(FeRAM)と呼ばれている。

ャパシタを有し、強誘電体膜のヒステリシス特性を利用して情報を記憶する。強誘電体膜

は、電極間の印加電圧に応じて分極を生じ、印加電圧を取り去っても自発分極を有する性

質を持つ。印加電圧の極性を反転させれば自発分極の極性も反転するので、自発分極を検

出すれば情報を読み出すことが出来る。このようなFeRAMは、高速動作が可能で、消

費電力が小さく、書き込み/読み出しの耐久性に優れている等の特徴を有し、今後の更な

る発展が見込まれている。

かった。ここで、標準的な強誘電体キャパシタの場合、例えば、Pt膜からなる下部電極

と、PZT膜(PbZr1−XTiXO3膜)よりなる強誘電体膜と、Pt膜からなる上

部電極とを順次積層した構成を有する。このような標準的な強誘電体キャパシタは、水素

分圧が40Pa程度の雰囲気中で200℃程度に加熱すると、PZT膜の強誘電性はほぼ

失われてしまうことが知られている。

近傍に存在する状態で熱処理を行うと、強誘電体キャパシタの強誘電体膜の強誘電性が著

しく劣化してしまうことが知られている。

な限り水分の発生が少なく、且つ低温のプロセスが選択されている。また、層間絶縁膜を

成膜するプロセスには、例えば、水素の発生量が比較的少ない原料ガスを用いたCVD(

Chemical Vapor Deposition)法等が選択されている。

タを覆うように酸化アルミニウム膜を形成する技術や、強誘電体キャパシタ上に形成され

た層間絶縁膜上に酸化アルミニウム膜を形成する技術が提案されている。酸化アルミニウ

ム膜は、水素や水分の拡散を防止する機能を有している。このため、酸化アルミニウム膜

を形成することで水素や水分が強誘電体膜に達することが防止され、水素や水分による強

誘電体膜の劣化を防止できる。また、強誘電体メモリでは、強誘電体キャパシタを直接覆

う酸化アルミニウム膜を水素拡散防止膜として形成させて強誘電体キャパシタへの水素拡

散を防止していた。

成するときには、強誘電体膜が主として高エネルギのスパッタリング粒子による物理的ダ

メージを受ける。このような物理的ダメージによって強誘電体膜の結晶構造の一部が破壊

されてしまうと、強誘電体キャパシタの特性が劣化してしまう。

ために、以下に説明するような種々の処理を実施していた。

誘電体膜をパターニングしてから酸素雰囲気中で熱処理を再度行う。さらに、下部電極を

パターニングした後にも酸素雰囲気中で熱処理を行う。その後、水素拡散防止膜、例えば

、酸化アルミニウム、酸化チタン、PLZT、PZTを形成する。このような従来技術に

ついては、例えば特許文献1に開示されている。その他にも、上部電極膜及び強誘電体膜

をパターニングした後、或いは、パターニングにより強誘電体キャパシタを形成した後に

酸素雰囲気中で熱処理を行うことが知られている。これらの処理では、酸素によって強誘

電体膜の結晶性が回復させられる。

ことが知られている。より詳細には、誘電体膜を加工した後、誘電体膜の全面に酸化アル

ミニウムを形成する。さらに、酸化アルミニウムと下部電極をエッチングしてから全面に

酸化アルミニウムを形成してキャパシタを保護する。このような従来技術については、例

えば特許文献2や、特許文献3、特許文献4に開示されている。

めに、キャパシタにパターンを形成した後、層間膜を堆積させ、その上に水素バリア膜と

してTiN膜を形成してからさらに層間膜を堆積させることが知られている。このような

従来技術については、例えば特許文献5に開示されている。

れたりすることを防止するためには、誘電体キャパシタを形成した後、Ta2O5、Y2

O3、CeO2又はHfO2の絶縁膜で被覆することが知られている。この場合、さらに

その上にAl2O3膜を形成して、被覆させることも知られている。このような従来技術

については、例えば特許文献6に開示されている。

キャパシタを形成した後、酸化アルミニウムの保護膜を形成した上から窒化シリコン膜を

形成することが知られている。このような従来技術については、例えば特許文献7に開示

されている。しかしながら、この方法では、誘電体キャパシタの側壁の傾斜度が低いとき

には、集積度が低減してしまう。傾斜度が高い場合は、側壁の水素バリア膜が薄くなるの

で、水素バリア性能が低下する。

を形成した後、酸化アルミニウム保護膜を形成してから回復アニールを行い、さらに第2

層の酸化アルミニウム保護膜を形成する方法が検討されている。このような従来技術につ

いては、例えば特許文献8に開示されている。

量が異なる酸化アルミニウムで二重に覆う方法も知られている。このような従来技術につ

いては、例えば特許文献9に開示されている。

電体膜の露出部に、第1の密度を有する金属酸化膜と、第1の密度より大きい第2密度を

有する第2の金属酸化膜とを配した構成が知られている。このような集積回路素子の製造

工程では、キャパシタを形成した後、酸素と反応性があるアルミニウム前駆ガス及び不活

性ガスを各々パルシングガス及びパージガスとして原子層蒸着を行う。これにより、誘電

体膜の側面には酸化アルミニウムのみが形成される。この酸化アルミニウムは水素バリア

膜となる。この後、熱処理を行って強誘電体膜の劣化を回復させると、キャパシタと水素

バリア膜の上にカプセル膜酸化アルミニウムが形成される。このような従来技術について

は、例えば特許文献10に開示されている。

キャパシタの周縁部で下部水素バリア膜を露出させるように第1層間絶縁膜を形成し、下

部水素バリア膜の露出部分を上部水素バリア膜で覆う構成が知られている。なお、上部水

素バリア膜は下部水素バリア膜に接触するように形成され、上部水素バリア膜の側面は下

部水素バリア膜の上面と鈍角をなすように配置される。このような従来技術については、

例えば特許文献11や、特許文献12に開示されている。

バリア膜を形成し、さらに拡散バリア膜で被覆することが知られている。水素バリア膜と

しては、Alの酸化物、Alの窒化物、Alの窒化酸化物、Taの酸化物、Taの酸化窒

化物、Tiの酸化物、Zrの酸化物のうちの少なくともいずれか一つが使用される。この

ような従来技術については、例えば特許文献13に開示されている。

全表面にブロッキング膜とキャパシタ保護膜を積層させることが知れている。キャパシタ

保護膜は、水素がキャパシタ誘電膜に拡散することを防止する。ブロッキング膜はキャパ

シタ保護膜下部に形成されて、ブロッキング膜の下部に形成された物質膜とキャパシタ保

護膜とが相互反応することを防止、及び/又はキャパシタ誘電膜の揮発を防止する。例え

ば、ALD(Atomic LayerDeposition)法で成膜した酸化アルミニウム膜はカバレッジが

非常に良くなるが、成膜時にキャパシタの強誘電体膜にダメージを与えたり、誘電体膜と

反応したりしてキャパシタの性能を劣化させることがある。これを防ぐために、キャパシ

タの直上にブロッキング膜が成膜されていた。このような従来技術については、例えば特

許文献14に開示されている。

このような従来技術については、例えば特許文献15や、引用文献16に開示されている

。

側壁に再付着する不揮発性の反応生成物を除去する方法としては、Ir層上に、有機物質

膜、ハードマスクとなるTiN層を順に積層し、フォトレジスト膜をマスクとしてこの積

層膜をドライエッチングすることが知られている。この場合、Ir層のドライエッチング

は酸素を含んだガスを用いて行われる。エッチング時に有機物質膜がサイドエッチされる

ため、反応生成物からなる側壁再付着層は有機物質膜層の側壁には生じない。この後、ア

ッシング処理を行えば、有機物質膜層のみがエッチングされ、マスクの役割を果たしたT

iN層は容易に除去され、パターニングされた被エッチング材だけが残される。このよう

な従来技術については、例えば特許文献17に開示されている。

(たとえば、Al2O3)やTiOx(たとえば、TiO2)を形成するが、O2中にお

いて450℃でアニールすると除去されることが知られている。このような従来技術につ

いては、例えば特許文献18に開示されている。

SiN及びAlNから成る群から選択される材料で作製し、下部電極及び強誘電体層の側

壁、上部電極の側壁の下部をその保護膜で被覆することが知られている。このような従来

技術については、例えば特許文献19に開示されている。

、上部電極膜及び第2水素バリア膜を順次堆積させることで水素還元作用による劣化を抑

制することが試みられている。上部電極をパターニングするときには、マスクを用いて水

素バリア膜及び上部電極膜を順次エッチングする。さらに、露出した強誘電体膜を覆う第

3の水素バリア膜を堆積させ、この上に形成したマスクを用いて強誘電体膜及び下部電極

膜を順次エッチングする。これによって、強誘電体膜とこれに自己整合された下部電極の

パターンが形成される。このような従来技術については、例えば特許文献20,21,2

2,23,24,25,26に開示されている。

制するために上記した種々の構造或いは工程が採用されているが、特定劣化をさらに防止

する必要がある。

率良く製造できるようにすることを主な目的とする。

上部導電膜を積層する工程と、前記上部電極の上に還元性物質の透過を防ぐ第1保護膜を

形成する工程と、前記第1保護膜及び前記上部導電膜をパターニングすることにより上部

電極を形成する工程と、前記強誘電体膜及び前記第1保護膜を酸素雰囲気中で加熱する熱

処理工程と、前記強誘電体膜及び前記下部導電膜をパターニングして強誘電体キャパシタ

を形成する工程と、前記第1保護膜及び前記強誘電体キャパシタを覆う第2保護膜を形成

する工程と、を有し、前記熱処理は、前記第1保護膜中の酸素濃度が異なる部分を形成す

る工程を含むことを特徴とする半導体装置の製造方法とした。

導電膜を積層する工程と、前記上部電極の上に第1保護膜を形成する工程と、前記第1保

護膜及び前記上部導電膜をパターニングすることにより、前記導電膜からキャパシタの上

部電極を形成する工程と、前記強誘電体膜及び前記第1保護膜を酸素雰囲気中で加熱する

ことにより、前記第1保護膜中で酸素濃度が膜厚方向に異なる部分を形成する熱処理工程

と、前記強誘電体膜及び前記下部導電膜をパターニングすることにより、前記下部導電膜

から前記キャパシタの下部電極を形成する工程と、前記第1保護膜及び前記キャパシタを

覆う第2保護膜を形成する工程と、を有する工程を含むことを特徴とする半導体装置の製

造方法が提供される。

上部導電膜を順に積層する工程と、前記上部導電膜の上に第1のハードマスク及び第2の

ハードマスクを順番に形成する工程と、前記第1及び第2のハードマスクを用いて、前記

下部導電膜、前記強誘電体膜、及び前記上部導電膜をパターニングして強誘電体キャパシ

タを形成する工程と、前記強誘電体キャパシタを形成した後に、前記第1のハードマスク

を残して前記第2のハードマスクを除去する工程と、前記強誘電体キャパシタ及び前記第

1のハードマスクを酸素雰囲気中で加熱し、前記第1のマスクの少なくとも一部を酸化さ

せ膜厚方向で酸素濃度の分布が異なる部分を有する第1保護膜を形成する熱処理工程と、

前記第1保護膜及び前記強誘電体キャパシタを覆う第2保護膜を形成する工程と、を有す

ることを特徴とする半導体装置の製造方法が提供される。

部電極の上に設けたので、第1保護膜により強誘電体キャパシタ内への還元性物質の透過

を防止することができ、強誘電体キャパシタの性能劣化を防止できる。

た後に、第1保護膜を除去することなく、強誘電体キャパシタに還元性物質の透過を防止

する膜として残すようにしたので、従来のようにマスクを除去する工程が不要になり、微

小異物の発生を防止できる。これにより工程劣化が防止され、しかも半導体装置の歩留ま

りを向上できる。

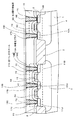

本発明の第1実施の形態について図面を参照して詳細に説明する。

。

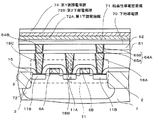

領域を画定する素子分離絶縁膜2を形成する。この実施の形態では素子分離絶縁層2とし

て、シャロートレンチアイソレーション(STI)を形成する。STIは、シリコン基板

1の素子分離領域に溝を形成し、その中に酸化シリコン等の絶縁膜を埋め込むことにより

形成される。なお、素子分離絶縁層2は、STIに限られず、LOCOS(Local Oxidat

ion of Silicon)法で形成した絶縁膜であってもよい。

物、例えばボロンを導入してpウェル3を形成する。また、周辺回路領域Bにおける所定

の活性領域にn型不純物を選択的に導入してnウェル4を形成する。この後、活性領域の

表面にゲート絶縁膜5を形成する。ゲート絶縁膜5は、熱酸化によるシリコン酸化膜が用

いられ、その厚さは約6〜7nmとする。

順番に形成し、フォトリソグラフィ技術を用いてパターニングしてゲート電極6A,6B

,6Cを形成する。ゲート電極6A,6Bはメモリセル領域Aに形成される。ゲート電極

6Cは周辺回路領域Bに形成される。非晶質シリコン膜は例えば厚さ約50nmとし、タ

ングステンシリサイド膜の厚さは約150nmとする。なお、非晶質シリコン膜の代わり

にポリシリコン膜を形成しても良い。

ド線の一部を構成する。さらに、ゲート電極6A,6Bをマスクにしたイオン注入により

、ゲート電極6A,6Bの両側のシリコン基板1の表層にn型不純物、例えばリンを導入

し、第1、第2ソース/ドレインエクステンション8A,8Bを形成する。

シリコン基板1にp型不純物を導入し、ソース/ドレインエクステンション9を形成する

。n型不純物とp型不純物の打ち分けはレジストパターンを使用して行われる。

その絶縁膜をエッチバックしてゲート電極6A〜6Cの両側部分のみを残して、絶縁性サ

イドウォール10を形成する。絶縁膜には、例えばCVD法により形成された酸化シリコ

ン膜が用いられる。

板1の表層に砒素等のn型不純物を再びイオン注入し、各ゲート電極6A,6Bの側方の

シリコン基板1に第1、第2ソース/ドレイン領域11A,11Bを形成する。

ン基板1に第1、第2ソース/ドレイン領域13A,13Bを形成する。

により形成する。金属膜は、例えば、コバルト膜等の高融点金属が好ましいが、比較的に

融点が低い金属であっても良い。そして、この金属膜を加熱してシリコンと反応させるこ

とにより、ゲート電極6A〜6Cの上面と、第1、第2ソース/ドレイン領域11A,1

1B,13A,13Bにおけるシリコン基板1上にそれぞれにコバルトシリサイド層等の

金属シリサイド層12を形成する。この熱処理によって、各ソース/ドレイン領域11A

,11B,13A,13Bが活性化されて低抵抗化する。

チングによって除去する。

B、第1、第2ソース/ドレイン領域11A,11B等によって構成されるMOSトラン

ジスタT1,T2が形成される。また、周辺回路領域BにもトランジスタT3が形成され

る。

(カバー膜)としてプラズマCVD法で酸窒化シリコン(SiON)膜を厚さ約200nm

に形成する。さらに、TEOS(tetra ethoxy silane)ガスを使用するプラズマCVD法

により、酸化防止絶縁膜15の上に第1層間絶縁膜16として酸化シリコン(SiO2)膜

を厚さ約1000nmに形成する。なお、TEOSを用いてプラズマCVD法によって形

成されるSiO2膜を以下TEOS膜という。

機械研磨)法で研磨して平坦化させ、シリコン基板1の表面から第1層間絶縁膜16の表

面までの膜厚を所定値、例えば、約785nmに調整する。

ターニングして、第1コンタクトホール17A,17B,17Cを形成する。第1コンタ

クトホール17A〜17Cの深さは第1ソース/ドレイン領域10A〜10Dのそれぞれ

の高融点金属シリサイド層11に到達するまでとし、その径は例えば0.25μmにする

。

A,11B,13A,13Bに電気的に接続される導電性プラグ18A〜18Eを形成す

る。具体的には、第1コンタクトホール17A〜17Cの内面に厚さが30nmのTi膜

と、厚さが20nmのTiN膜とを順番にスパッタ法等により形成し、2層の積層構造を

有する密着膜(グルー膜)19Aを作製する。さらに、密着膜19A上にタングステン(

W)膜19BをCVD法により成長させる。この膜厚は、第1層間絶縁膜16上で、例え

ば300nmとし、W膜19Bで第1コンタクトホール17A〜17Cの空隙を埋める。

第1層間絶縁膜16の上面上に成長した余分なW膜19Bは、CMP法で除去する。これ

により、コンタクトホール17A〜17Cには、それぞれ導電性プラグ18A〜18Cが

形成される。

それぞれに導電性プラグ18D,18Eを形成する。

第1層間絶縁膜16上及び導電性プラグ18A〜18E上に第2層間絶縁膜20を形成す

る。第2層間絶縁膜20は、例えば、SiON膜を約100nmの膜厚に形成し、さらに

TEOS膜を約130nmの膜厚で堆積させた構成を有する。第2層間絶縁膜20を形成

した後に、窒素雰囲気中で約650℃の温度で30分間程度アニールして第2層間絶縁膜

20の脱ガスを行う。

2O3)膜をスパッタ法で20nm程度の厚さに形成する。その後、急速加熱処理(RT

A)により650℃の酸素雰囲気中で下部電極密着膜21を酸化させる。

成する。第1導電膜22には、例えば、スパッタ法で形成したプラチナ膜が用いられ、そ

の厚さは約150nmとする。なお、第1導電膜22は、プラチナ膜の代りにイリジウム

膜、ルテニウム膜、酸化ルテニウム(RuO2)膜、SrRuO3膜のいずれかの単層膜

、或いはこれらの積層膜でも良い。なお、第1導電膜22を形成する前に下部電極密着膜

21を形成しているので、第1導電膜22と第2層間絶縁膜20との密着力が高められる

。

ては、例えばPZT(Pb(Zrx, Ti1-x)O3(0≦x≦1))膜が用いられ、PZTターゲットを

用いるRF(Radio Frequency)スパッタ法により厚さ約90nmに形成される。

、Ta、Ir、Wのいずれかを添加した材料から第1強誘電体膜23を形成しても良い。

さらに、(Bi1−xRx)Ti3O12(Rは希土類元素で0<x<1)、SrBi2

Ta2O9(SBT)、SrBi4Ti4O15等のBi層状化合物から第1強誘電体膜

23を形成しても良い。また、第1強誘電体膜23の成膜方法もスパッタ法に限定されず

、ゾル・ゲル法、MOD(Metal Organic Deposition)法、MOCVD(Metal Organic C

VD)法を採用しても良い。

体特性が結晶質の場合に比べて劣ることが知られている。そこで、成膜後に結晶化アニー

ルを実施して第1強誘電体膜23を結晶化させる。

整された酸素+アルゴンの雰囲気で、RTA(Rapid Thermal Anneal)により行われる。基

板温度は例えば600℃で、処理時間は90秒とする。これにより、第1強誘電体膜23

が結晶化して膜中にPZT結晶粒が多数形成される。なお、MOCVD法を採用した場合

、第1強誘電体膜23は成膜の時点で結晶化しているので結晶化アニールは不要になる。

スパッタ法で例えば厚さ10nm〜30nmに形成する。なお、第2強誘電体膜24はP

ZT膜に限定されず、PZTにCa、Sr、La、Nb、Ta、Ir、Wのいずれかを添

加した材料から第2強誘電体膜24を形成してもよい。さらに、(Bi1-xRx)Ti

3O12(Rは希土類元素で0<x<1)、SrBi2Ta2O9(SBT)や、SrB

i4Ti4O15等のBi層状化合物で第2強誘電体膜24を形成しても良い。なお、第

2強誘電体膜24は、第1強誘電体膜23と同じ材料で形成することが好ましい。

ウム膜25Aをスパッタ法により、例えば、厚さ約50nmに形成する。その後に、酸素

含有雰囲気中において第2強誘電体膜24に対する結晶化アニールを行って非晶質の第2

強誘電体膜24を結晶化させると共に、第2強誘電体膜24の下の第1強誘電体膜23の

結晶性をさらに高める。アニールの条件は、例えば、基板温度710℃、処理時間を12

0秒とする。アニールを行う酸素含有雰囲気には、酸素濃度が1流量%に調整された酸素

ガスとアルゴンガスとの混合雰囲気が用いられる。

り、膜を構成する酸化イリジウムが第2強誘電体膜24の結晶粒界に入り込むのを防止で

きる。これによって、酸化イリジウムによって第2強誘電体膜24にリークパスが形成さ

れることを抑制できる。また、このアニールにより、第1酸化イリジウム膜25Aを透過

して酸素が第2強誘電体膜24に供給され、第2強誘電体膜24の酸素欠損が補われると

いう利点も有する。

ように薄く、例えば10nm〜100nmとするのが好ましい。しかしながら、このよう

に薄い第2導電膜25を第2強誘電体膜24上に形成しただけでは、後のエッチング工程

等において第2導電膜25で吸収しきれなかったダメージが第1、2強誘電体膜23,2

4に影響を及ぼす可能性がある。

して、第2酸化イリジウム膜25Bを第1酸化イリジウム膜25Aの上にスパッタ法で厚

さ約200nmに形成する。この第2酸化イリジウム膜25B及び第1酸化イリジウム膜

25Aとで第2導電膜25が形成される。

などの還元性物質の透過を防止する拡散防止膜として機能する第1保護膜27を形成する

。第1保護膜27としては、例えばTiN膜が用いられ、スパッタ法で30〜100nm

の膜厚に形成される。TiN膜は、基板温度を200℃、Arを50sccm、N2を9

0sccmの混合ガス雰囲気中でTiのターゲットを用いて成膜する。

スク(第1のマスク)としても使用される。本実施の形態ではTIN膜の膜厚を50nm

とした。なお、第1保護膜27はTiN膜に限定されず、Ti、TiN、Ta、TaN、

TiAl、TaAl、TiAlN、TaAlN、TiSiN、TaSiN、TiSi、T

aSiのいずれかから形成しても良い。

図1Dに示すように、第2のマスクであるフォトレジスト膜38を所定の平面形状、即ち

強誘電体キャパシタの上部電極の平面形状にパターニングする。そして、フォトレジスト

膜38のパターンを利用して第2導電膜25、酸化イリジウム膜26及び第1保護膜27

をエッチングする。この際、第1保護膜27はハードマスク(第1のハードマスク)とし

ても機能し、第2導電膜25及び第1保護膜27が確実にエッチングされる。なお、フォ

トレジスト膜38の代わりに、第2のハードマスクを形成してエッチングを行っても良い

。

エッチング後、フォトレジスト膜38は除去する。一方、ハードマスクとして使用した第

1保護膜27は除去せずに残しておく。

れるので、上部領域27Aの積層方向に平行な断面積は下部領域27Bの段面積より小さ

くなる。つまり、第1保護膜27は上面の面積が下面より狭くなっている。

温度は600〜700℃とする。本実施の形態では、その一例として650℃で40分間

熱処理を行った。この熱処理は、プロセス中に強誘電体膜23,24が受けたダメージを

回復させるもので、このようなアニールは回復アニールとも呼ばれる。

領域及び側部領域)のTiNは殆ど酸化される。TiNの酸化度は膜厚方向、且つ基板方

向に徐々に低くなる。一方、第2酸化イリジウム膜25A中の酸素はその真上にある第1

保護膜27の下部領域のTiNへ拡散する。つまり、第1保護膜27が上下方向及び側方

のそれぞれから酸化されて、酸素が膜中心へ拡散する。これにより、酸化されたTiN膜

の上部領域及び下部領域並びに側部領域のそれぞれの酸化度が中心より高くなる。

い上部領域27A及び下部領域27Bと、積層方向で上部領域27A及び下部領域27B

に挟まれ、これら2つの領域27A,27Bよりも酸素濃度が相対的に低い膜中心領域2

7Cとが形成される。つまり、第1保護膜27は、膜厚方向(積層方向)に酸素濃度が異

なる部分を有する。膜厚方向の酸素濃度プロファイルは、例えば、図2(b)に示すよう

に上側が最も高く、次いで下側が高くなっており、中央部分が最も低くなっている。

形成され、略同じ酸素濃度になる。即ち、第1保護膜27は、膜中心領域27Cの酸素濃

度が上部領域27A及び下部領域27B及び側部領域27Dのそれぞれの酸素濃度より低

くなっている。例えば、第1保護膜27の厚さが約50nmのとき、上部領域27Aの厚

さは約30nm、側部領域27Dの幅は約30nm、下部領域27Bの厚さは5〜10n

m程度になっている。特に上部領域27Aを最も厚くすることで還元物質の透過を効率的

に防止することが可能になる。

できる。さらに、第1保護膜27の表面が貴金属膜である場合、第1保護膜27を表面側

から酸化させたときの酸化度、即ち酸素の組成比は上部領域27Aから下部領域27Bに

向かって徐々に低くなる。したがって、この熱処理により、第1保護膜27が下から順に

(又は上から順に)TiOx、TiON、TiOy(x>y)の層構造、又はTiOx、

TiOy、TiON(x>y)の層構造、又はTiOx、TiON、TiOxの層構造を

持つようになる。一般に、TiNよりもTiOの方が水分や水素を透過し難いことが知ら

れているので、このような構成にすることで、確実に水分等の透過を防止できるようにな

り、強誘電体膜23,24の還元が防止される。

x、TaON、TiAlOx、TaAlOx、TiAlON、TaAlON、TiSiO

N、TaSiON、TiSiOx、TaSiOx、AlOx、ZrOxなどでも良い。

ト膜を例えばスピンコート法によって形成し、フォトリソグラフィ法によってフォトレジ

スト膜を強誘電体膜23,24の平面形状にパターニングする。続いて、パターニングさ

れたフォトレジストマスクを使用して強誘電体膜23,24をエッチングする。その後、

フォトレジスト膜を除去する。次いで、酸素雰囲気で例えば300℃〜400℃、30分

間〜120分間、熱処理を行う。なお、強誘電体膜23,24は、複数の上部電極28の

下を通る長方形の平面形状を有している。

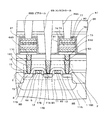

の上に第2保護膜30を例えばスパッタ法又はCVD法、或いはALD法により形成する

。第2保護膜30としては、例えば膜厚が20nm〜50nmの酸化アルミニウム膜が用

いられる。第2保護膜30の形成後は酸素雰囲気で熱処理を行う。熱処理条件は、例えば

400℃〜600℃、30分〜120分間である。

に水素又は水が強誘電キャパシタ31に拡散することを防止する拡散防止膜である。また

、第2保護膜30は、酸化アルミニウム膜に限定されず、TiOx、TaOx、AlOx

、ZrOx、HfOx、NbOx、VOx、ZnOx膜や、PZTからなる群から選択さ

れる材料から形成された膜であっても良い。

フォトリソグラフィ法でフォトレジスト膜を所定の平面形状、即ち強誘電体キャパシタの

下部電極の平面形状にパターニングする。続いて、フォトレジスト膜をマスクにして第2

保護膜30及び第1導電膜22及び下部電極密着膜21をエッチングすることによって第

1導電膜22からなる下部電極29を形成する。下部電極29の平面形状は、複数の上部

電極28を含む略長方形であり、その端部は誘電体膜23,24からはみ出す大きさであ

る。

29によって、強誘電体キャパシタ31が構成される。

ように残存する。エッチングが終了したら残ったフォトレジスト膜(不図示)を除去する

。次いで、例えば300℃〜400℃の酸素雰囲気で、30分間〜120分間の熱処理を

行う。

ッタ法又はCVD法、或いはALD法により形成する。第3保護膜32は、例えば膜厚が

20nmの酸化アルミニウム膜からなる。

〜120分間の熱処理を行う。この結果、強誘電体膜23,24に酸素が供給され、強誘

電体キャパシタ31の電気的特性が回復する

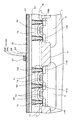

次に、図1Hに示す断面構造を得るまでの工程について説明する。

CVD法により膜厚が1400nmのシリコン酸化物を形成する。この後、例えばCMP

法により、第3層間絶縁膜33の表面を平坦化する。

0℃、2分間の熱処理を行う。熱処理の結果、第3層間絶縁膜33中の水分が除去される

と共に、第3層間絶縁膜33の膜質が変化して膜中に水分が入り難くなる。この熱処理に

よって、第3層間絶縁膜33の表面が窒化されてSiON膜が形成される。

、例えばスパッタ法又はCVD法で成膜した膜厚20nm〜50nmの酸化アルミニウム

膜からなる。さらに、第4保護膜34の全面に、第4層間絶縁膜35として例えば膜厚が

300nmのシリコン酸化物をTEOSを用いるプラズマCVD法で形成する。

レジスト膜をマスクにしてエッチングを行い、第4保護膜34、第3層間絶縁膜33、第

3保護膜32を経て強誘電体キャパシタ31の上部電極28まで達する第2コンタクトホ

ール41を形成する。

1は第1保護膜27を貫通して上部電極28に至る深さにしている。しかしながら、第1

保護膜27が導電性を有する材料から形成され、第1保護膜27を介して上部電極28と

電気的な接続が可能な場合には、第2コンタクトホール41は第1保護膜27に至る深さ

にすれば良い。

し、強誘電体キャパシタ31の下部電極29まで達する第2コンタクトホール42を形成

する。

行う。この結果、強誘電体膜23,24に酸素が供給され、強誘電体キャパシタ31の電

気的特性が回復する。なお、この熱処理を、酸素雰囲気中ではなく、オゾン雰囲気中で行

っても良い。オゾン雰囲気中で熱処理を行った場合にも、強誘電体膜23,24に酸素が

供給されて強誘電体キャパシタ31の電気的特性が回復する。

膜16,20を貫通し、導電性プラグ18A〜18Eまで達するビアホール43A〜43

Eをフォトリソグラフィ及びエッチングにより形成する。

iN膜と順番に例えばスパッタ法により形成する。これらのTi膜及びTiN膜によって

、第2コンタクトホール41に密着膜44Aが形成される。さらに、密着膜44A上にW

膜44BをCVD法により成長させ、W膜44Bで第2コンタクトホール41,42、ビ

アホール43A〜43Eの空隙を埋めて導電性プラグ45A〜44Gを形成する。第4層

間絶縁膜35上に形成された余分な密着膜44A及びW膜44BはCMP法により除去す

る。これにより、各導電性プラグ45C〜45Gがその下の導電性プラグ18A〜18E

を介してソース/ドレイン領域11A,11B,13A,13Bに電気的に接続される。

去する。プラズマ洗浄には、例えばアルゴンガスが用いられる。

導体膜46は、例えば膜厚が150nmのTiN膜と、膜厚が550nmのAlCu合金

膜と、膜厚が5nmのTi膜と、膜厚が150nmのTiN膜とを順次積層することによ

って形成される。

パターニングして第1層目の金属配線層を形成する。これにより、導電体プラグ45Aを

介して上部電極28に電気的に接続された配線47Aと、導電体プラグ45Bを介して下

部電極29に電気的に接続された配線47Bと導電体プラグ18A〜18E,45C〜4

5Gを介してソース/ドレイン領域11A,11B,13A,13Bに電気的に接続され

る配線47Cとが形成される。

ターニング方法によって3層配線や5層配線を行うと、この実施の形態に係る半導体装置

の基本構造が完成する。

タ31の回復アニールによって上部領域27A及び下部領域27Bの酸素濃度が膜中心領

域27Cに比べて高くなるような構造を有する。このような第1保護膜27は、上部電極

28をパターニングする際のメタルマスクになると共に、還元性物質の透過を防止する機

能を備える。即ち、強誘電体キャパシタ31をパターニングした後に、除去されることな

く上部電極28上に残されて、還元性物質が強誘電体キャパシタ31に透過することを防

止する還元元素バリア膜として機能する。上部電極28をパターニングするときの第1保

護膜27は、酸化前の金属膜の状態であるので、酸化膜に比べてエッチングレートが大き

く、エッチングプロセスに要する時間を短縮できる。

ハードマスクをパターニング後に除去していた。ハードマスクの除去はウェットやドライ

エッチングの二種類の方法があるが、ウェット方法で除去する場合、シリコン基板の周辺

やベベル部分に膜剥がれが発生し易くなり、剥がれた膜がシリコン基板に再付着して、コ

ンタクト不良の原因となっていた。

ングすると同時に、微小異物(0.2μm以下)が上部電極の表面に残される。上部電極

28の上に微小異物が残ったままで第2保護膜30を形成すると、図6の破線で囲まれた

部分に例示するように、微小異物が介在する第2保護膜30と上部電極29の密着性が悪

くなったり、膜に欠陥が生じたりしていた。これにより、導電性プラグ45Aを形成する

際に、WF6を含む反応ガスを構成するタングステン、フッ素、水素が第2保護膜30の

欠陥を通ってキャパシタに侵入し、強誘電体膜23,24を劣化するおそれがある。

去する必要がなくなるので、従来のような微小異物が発生することがない。したがって、

膜剥がれや強誘電体膜の劣化を防止でき、高品質の半導体装置が得られる。さらに、第1

保護膜27の除去工程が不要になることで、プロセスを簡略化することができ、作業効率

を向上できる。

間領域、下部領域27の順に徐々に酸素濃度が低下する構成であっても良い。つまり、図

3(b)に膜厚方向の酸素濃度プロファイルの一例を示すように、上部流域27から下部

領域27Bに向かって酸素濃度が漸次低下するような構成であっても同様の効果が得られ

る。なお、この場合も側部は酸化によって酸素濃度が高められている。

積層した二層構造でも良い。第2保護膜30を構成する材料としては、例えばTiOx、

TaOx、AlOx、ZrOx、HfOx、NbOx、VOx、ZnOxや、PZTなど

があげられる。第1層30Aと第2層30Bとは、同一成分から構成しても良いし、異な

る成分にしても良い。いずれの場合でも水素や水が強誘電体キャパシタ31に拡散するこ

とを防止する拡散防止膜として機能する。そして、2層の積層構造を有することから、よ

り確実に水素等の拡散を防止できる。また、第1層30Aを第2層30Bより薄くするこ

とにより、第1層30Aを形成した後に回復アニールを行えば強誘電体膜23,24への

酸素添加が容易になる。

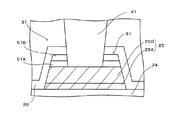

接する下部領域となる下層保護膜51Aと、上部領域になる上層保護膜51Bとからなる

。上層保護膜51Bは酸素含有量が略均一で、下層保護膜51Aより高い。下層保護膜5

1Aは、膜内の酸素含有量の分布が積層方向で異なり、より具体的には上部から下部にか

けて漸次酸素含有量が低下している。このような第1保護膜51であっても前記と同様の

効果が得られる。なお、上層保護膜51Bは、成膜時に金属酸化膜として形成される。下

層保護膜51Aの側部も酸化によって酸素濃度を高められる。また、第1保護膜51を1

層構造とし、成膜後の熱処理で酸化させることによって下層保護膜51A及び上層保護膜

51Bを形成しても良い。

を有する第1保護膜52が3層構造になっている。具体的には、第1保護膜52は、積層

方向に順番に積層された下層保護膜52Aと、中間保護膜52Bと、上層保護膜52Cと

を有する。下層保護膜52Aは下部領域に相当し、中間保護膜52Bは膜中心領域に相当

する。上層保護膜52Cは上部領域に相当する。さらに、第2保護膜53が第1保護膜5

2の上面及び側面を覆うと共に、上部電極27を含む強誘電体キャパシタ31の側面を覆

うように設けられている。

Oxや、TiON、TaOx、TaON、TiAlOx、TaAlOx、TiAlON、

TaAlON、TiSiON、TaSiON、TiSiOx、TaSiOx、AlOx、

ZrOxなどから形成される。保護膜52Aと上層保護膜52Cとは同じ材料から構成し

ても良い。中間保護膜52Bは、例えば、TiONや、TaON、TiAlON、TaA

lON、TiSiON、TaSiONなどから形成される。中間保護膜52Bは、その直

下の下層保護膜52A及び直上に上層保護膜52Cのそれぞれより酸素含有量が低い。こ

の第1保護膜52を作製するときは、下層保護膜52A、中間保護膜52B、上層保護膜

52Cの順番に膜を形成する。中間保護膜52Bの酸素量を相対的に少なくしている理由

は、酸素が少ないほどパターニング時のエッチングレートを速くできるからである。

に向上される。なお、積層構造を有する第1保護膜52は、4層以上、でも良い。そのよ

うな場合でも中間保護膜の酸素含有量を下部領域の保護膜及び上部領域の保護膜より低く

することが好ましい。

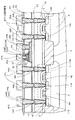

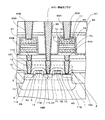

(第2実施の形態)

本発明の第2実施の形態について図面を参照して詳細に説明する。なお、第1実施の形

態と同じ構成要素には同じ符号を付し、重複する説明は省略する。

モリ)である。

士、即ちpウェル3同士を区画し、トランジスタT1,T2を形成する。さらに、各ソー

ス/ドレイン領域11A,11Bの位置に対応して第1層間絶縁膜16にコンタクトホー

ル17A〜17Eを利用した導電性プラグ18A〜18Cを形成する。ここまでの工程の

詳細は、第1実施の形態と同様である。

1として、SiON膜を例えばプラズマCVD法により130nmの膜厚に形成する。さ

らに、第1酸化防止膜61の上に第2層間絶縁膜62として、シリコン酸化膜を例えばT

EOSを原料とするプラズマCVD法によって300nmの膜厚で形成する。なお、Si

ON膜の代わりにSiN膜やAlO膜を形成しても良い。

の両側寄りの導電性プラグ18A,18Cの上に開口を有している。そして、レジストパ

ターンをマスクに用いて第2層間絶縁膜62及び第1酸化防止膜61をドライエッチング

し、第2ソース/ドレイン領域11A,11Bに達するビアホール63を形成する。ビア

ホール63には、導電性プラグ64A,64Bが埋め込まれる。導電性プラグ64A,6

4Bは、第1の実施の形態と同様のプロセスで作製される密着層65AとW層65Bとか

ら形成される。

による研磨で除去される。CMP法では、研磨対象である密着層65A及びW層65Bの

研磨速度が下地の第1絶縁膜よりも速くなるようなスラリ、例えばキャボット・マイクロ

エレクトロニクス社製のSSW2000を使用することができる。そして、第1層間絶縁

膜16上に研磨残を残さないために、このCMPの研磨量は密着層65A及びW層65B

の合計膜厚よりも厚く設定する。即ち、ここでのCMP研磨はオーバー研磨となる。

低くなってリセスが発生する。このリセスの深さは20〜50nmであり、典型的には約

50nm程度である。

ことにより、表面の酸素原子にNH基を結合させる。これによって、第2層間絶縁膜62

上にTi原子をさらに堆積させてもTi原子が酸素原子に捕獲されてしまうことがなく、

第2層間絶縁膜62の表面を自在に移動できるようになる。このようにして第2層間絶縁

膜62上に(002)配向に自己組織化されたTi膜は、その上面の平坦性が改善される

。

ils)離間した位置に対向電極を有する平行平板型のプラズマ処理装置を使いて実施す

る。処理条件は、例えば、266Pa(2Torr)の圧力下、400℃の基板温度に保

持された処理容器中にアンモニアガスを350sccmの流量で供給し、シリコン基板1

側に13.56MHzの高周波を100Wのパワーで、また対向電極に350kHzの高

周波を55Wのパワーで、60秒間供給することにより実行する。

、0.15PaのAr雰囲気下、20℃の基板温度で2.6kWのスパッタDCパワーを

35秒間供給する。これによって、強い(002)配向のTi膜が約100nmの厚さに

形成される。

)配向のTiN膜からなる下地導電膜70を形成する。この下地導電膜70の厚さは10

0nm〜300nmで、より好ましくは約100nmである。下地導電膜70は窒化チタ

ン膜に限定されず、タングステン膜、シリコン膜、及び銅膜のいずれかを下地導電膜70

として形成しても良い。但し、結晶性を向上するために、下地導電膜70はTi膜をアン

モニアプラズマ処理することにより作製したTiN膜であることが好ましい。

が形成されるので、CMP法で下地導電膜70の上面を研磨して平坦化されることで凹部

を除去する。CMPで使用されるスラリは特に限定されないが、例えば、キャボット・マ

イクロエレクトロニクス社製のSSW2000を使用できる。ところで、CMP後の下地

導電膜70の厚さは、研磨誤差に起因して、シリコン基板1の面内や、複数のシリコン基

板1間でばらつきが生じる。そのようなばらつきを考慮して研磨時間を制御すれば、CM

P後の下地導電膜70の厚さの目標値を50nm〜100nm、より好ましくは50nm

にする。

の結晶が研磨によって歪んだ状態となっている。このように結晶に歪を有する下地導電膜

70の上方にキャパシタの下部電極を形成すると、その歪みの影響が下部電極に及んで下

部電極の結晶性が劣化し、下地導電膜70の上の強誘電体膜の強誘電体特性が劣化するこ

とがある。

に曝すことで、下地導電膜70の結晶の歪みを解消させ、これ以降に堆積させる膜に影響

を与えないようにする。

性導電密着膜71としてTi膜をスパッタ法により厚さ約20nmに形成する。結晶性導

電密着膜71を形成した後、窒素雰囲気中で650℃、60秒間の処理条件でRTAを行

い、(111)配向のTiN膜を形成する。結晶性導電密着膜71は、自身の配向の作用

によって、その上に後に堆積される膜の配向を高める機能に加え、密着膜としての機能も

有する。

ましい)貴金属Ir、Ptなどでも良い。

する。

パッタにより100nmの厚さに形成される。成膜条件は、例えばArを40SCCM及

び窒素を10SCCMの流量で供給した混合雰囲気において、253.3Paの圧力、4

00℃の基板温度、1.0kWのスパッタパワーに設定する。

0.11Paの圧力下、500℃の基板温度、0.5kWのスパッタパワーで100nm

の厚さに形成する。

Oや、IrOx、SrRuO3などの導電性酸化物を用いることもできる。さらに、これ

らの金属あるいは金属酸化物の積層膜でも良い。

には、Pb(DPM)2、Zr(dmhd)4およびTi(O−iOr)2(DPM)2

をTHF溶媒中に、いずれも0.3mol/lの濃度で溶解し、Pb,ZrおよびTiの

各液体原料を形成する。さらにこれらの液体原料を、MOCVD装置の気化器に、流量が

0.474ml/分のTHF溶媒と共に、それぞれ0.326ml/分、0.200ml

/分、及び0.200ml/分の流量で供給する。

、MOCVD装置中に、665Pa(5Torr)の圧力下、620℃の基板温度で、P

b,Zr及びTiの原料ガスをMOCVD装置に620秒間供給する。これにより、第2

の下部電極膜72B上に所望のPZT膜が、例えば100nmの厚さに形成される。

パッタ法により形成する。第2強誘電体膜75は、例えば膜厚が1nm〜30nm(より

好ましくは20nm)とする。MOCVDで成膜する場合、鉛(Pb)供給用の有機ソー

スとしては、Pb(DPM)2(Pb(C11H19O2)2)をTHF(tetrahydrofu

ran:C4H8O)液に溶かした材が用いられる。また、ジルコニウム(Zr)供給用の

有機ソースとしては、Zr(DMHD)4(Zr((C9H15O2)4)をTHF液に

溶かした材料が用いられる。チタン(Ti)供給用の有機ソースとしては、Ti(O−i

Pr)2(DPM)2(Ti(C3H7O)2(C11H19O2)2)をTHF液に溶

かした材料が用いられる。

6Aの形成に当たっては、先ず、第2強誘電体膜75上に、厚さが50nmで成膜の時点

で結晶化したIrOx膜をスパッタ法により形成する。例えば、このときの成膜温度を3

00℃とし、成膜ガスとしてAr及びO2を用い、これらの流量をいずれも100scc

mとする。また、スパッタパワーは、例えば1kW〜2kW程度とする。

た雰囲気中で60秒間熱処理を行う。この熱処理によって第2強誘電体膜75が完全に結

晶化すると共に、第1上部電極膜76Aのプラズマダメージが回復し、第1強誘電体膜7

4中の酸素欠損が補償される。

例えば200nm形成する。IrOY膜は、例えば、Ar雰囲気中、且つ0.8Paの圧

力下、1.0kWのスパッタパワーで79秒間堆積させる。

成にすると、水素に対して触媒作用を生じることがなく、第2強誘電体膜75が水素ラジ

カルにより還元される問題が抑制され、キャパシタの水素耐性が向上する。

、Os、Pd、これらの酸化物、SrRuO3などの導電性酸化物や、これらの積層構造

を用いても良い。

r雰囲気中、1Paの圧力下、1.0kWのスパッタパワーで100nmの厚さに堆積す

る。なお、水素バリア膜77は、Ir膜に限定されず、Pt膜やSrRuO3膜を使用し

ても良い。

、第1、第2強誘電体膜74,75、第1、第2下部電極膜72A,72Bなどをパター

ニングする際にハードマスクとして用いる第1保護膜78とマスク材料層79とを順次形

成する。

iNからなる。第1保護膜78は、TiAlNや、TaAlN、TaN膜及びこれらの積

層膜でも良い。

CVD法で成膜された酸化シリコン膜からなる。

光、現像してキャパシタ平面形状のレジストパターンを形成する。

使用してマスク材料層79を島状にパターニングし、マスク材料層79をマスクにして第

1保護膜78をエッチングする。これにより、マスク材料層79(第2のマスク)と、第

1保護膜78(第1のマスク)とからなるハードマスクがキャパシタ形成領域に島状に形

成される。その後、マスク材料層79上のレジストパターンを除去する。

ングにより、ハードマスクで覆われていない部分の第1、第2上部電極膜76A,76B

、第1、第2強誘電体膜74、75、第2下部電極膜72A、72Bをドライエッチング

する。

極80が形成され、同様に下部電極膜72A、72Bがパターニングされてキャパシタ用

の下部電極73が形成される。

81が形成される。

電膜70をエッチングにより除去し、これらの膜を強誘電体キャパシタ81の下のみに島

状に残す。

第1保護膜78は除去せずに残される。

ラズマエッチングにより行われる。その条件として、チャンバ内に流量比で5%のCF4

ガスと95%のO2ガスとの混合ガスをエッチングガスとして供給すると共に、チャンバ

の上部電極に周波数2.45GHzでパワーが1400Wの高周波電力を供給して、基板

温度を200℃にする。

下部領域78Bと、積層方向で上部領域78A及び下部領域78Bに挟まれ、これら2つ

の領域78A,78Bよりも酸素濃度が相対的に低い膜中心領域78Cとが形成される。

つまり、第1保護膜78は、積層方向に酸素濃度が異なる部分を有する。

一体に形成され、略同じ酸素濃度になる。即ち、第1保護膜78は、側部領域78Dを除

いて、酸素濃度が積層方向に異なる。より詳細には、側部領域78Dを除いて、膜中心領

域78Cの酸素濃度が上部領域78A及び下部領域78Bのそれぞれの酸素濃度より低く

なっている。各領域の膜厚の割合は第1の実施の形態と同様であることが好ましい。

層構造、又はTiOx、TiOy、TiON(x>y)の層構造、又はTiOx、TiO

N、TiOxの層構造を持つようになる。

l、TaAl、TiAlN、TaAlN、TiSiN、TaSiN、TiSi、TaSi

のいずれかから形成しても良い。つまり、酸化後の第1保護膜78は、TaN、TiON

、TiOx、TaOx、TaON、TiAlOx、TaAlOx、TiAlON、TaA

lON、TiSiON、TaSiON、TiSiOx、TaSiOx、AlOx、ZrO

xなどの材料から形成しても良い。

れるので、膜厚方向の上部領域の面積が下部領域の面積より小さくなる。

3をスパッタ法により20nmの膜厚に形成する。或いは、MOCVD法又はALD法で

2nm〜5nmのAlOを形成する。

復アニールを施す。回復アニールの条件は特に限定されないが、例えば炉内において基板

温度550℃〜700℃で実施する。また、強誘電体膜74,75がPZTの場合、60

0℃酸素の雰囲気中で60分アニールを行うことが好ましい。この熱処理により、ハード

マスクである第1保護膜78中のTiNが酸化する。酸化されたTiN膜の酸素含有量は

、膜の縦方向(積層方向)における上部領域の方が下部領域より多くなる。

てAl2O3をCVD法により約38nmの膜厚に形成する。

ることを阻止する機能に優れている。このため、強誘電体膜74,75の強誘電体特性が

還元性物質により劣化されるのを防止する。

の形成前に酸素を含む炉内でアニールを行っても良い。アニール条件としては、例えば基

板温度350℃、処理時間1時間とする。第3保護膜83は、酸化アルミニウム以外に、

チタン酸化膜、タンタル酸化膜、ジルコニウム酸化膜、アルミニウム窒化膜、タンタル窒

化膜及びアルミニウム酸窒化膜でも良い。なお、第2、第3保護膜82,83は、第1実

施の形態の第2保護膜30に相当し、同様の材料から形成しても良い。

ラズマTEOSCVD法により膜厚1500nmで形成する。第3層間絶縁膜85として

シリコン酸化膜を形成する場合には、原料ガスとして、例えば、TEOSガスと酸素ガス

とヘリウムガスとの混合ガスを用いる。なお、第3層間絶縁膜85として、例えば、絶縁

性を有する無機膜等を形成しても良い。第3層間絶縁膜85を形成したら、その表面を例

えばCMPで平坦化する。

って第3層間絶縁膜85中の水分を除去する。この際、第3層間絶縁膜85の膜質が改善

されて膜中に水分が入り難くなる。

より形成する。バリア膜86としては、例えば、膜厚が20nm〜100nmの酸化アル

ミニウム膜が用いられる。平坦化された第3層間絶縁膜85上にバリア膜86が形成され

るため、バリア膜86の表面は平坦になる。

により形成する。第4層間絶縁膜87としては、例えば膜厚が800nm〜1000nm

のシリコン酸化膜が用いられる。なお、第4層間絶縁膜87として、SiON膜又はシリ

コン窒化膜等を形成しても良い。第4層間絶縁膜87を形成したら、その表面を例えばC

MPで平坦化する。

形成する。ビアホール88A,88Bを形成する際には、キャパタ81の上部電極80を

覆う水素バリア膜77を露出させた後、550℃で酸素雰囲気中において熱処理を行う。

これによって、ビアホール88A,88Bの形成時に第1強誘電体膜74中に生じた酸素

欠損が回復される。また、この後に、pウェル3の中央の導電性プラグ18Bの上にビア

ホール89を形成する。

ホール88,89の内面にTiN膜を単層で密着層として形成することが好ましい。なお

、密着層は、Ti膜をスパッタにより形成し、その上にTiN膜をMOCVD法により形

成した積層構造でも良い。この場合、TiN膜から炭素除去を行うため、窒素と水素の混

合ガスプラズマ中での処理が必要になるが、上部電極80にIrよりなる水素バリア膜7

7をそれぞれ形成しているため、上部電極80の還元は防止される。

77に至るまで形成されているが、水素バリア膜77を絶縁材から形成する場合には、ビ

アホール88A,88Bは上部電極80に達する深さに形成する。

を形成する。即ち、例えばスパッタ法により、膜厚が60nmのTi膜と、膜厚が30n

mのTiN膜と、膜厚が360nmのAlCu合金膜と、膜厚が5nmのTi膜と、膜厚

が70nmのTiN膜とを順次形成する。これにより、Ti膜、TiN膜、AlCu合金

膜、Ti膜及びTiN膜からなる積層膜を形成する。

からなる配線(第1金属配線層)92A,92Bが形成される。これにより、導電性プラ

グ90A,90Bを介して強誘電体キャパシタ81の上部電極膜80と配線92Aとが電

気的に接続される。同様に、導電性プラグ18B,90Cを介して第1ソース/ドレイン

領域11Aと配線92Bとが電気的に接続される。

2〜5層目以降の配線の形成等を行う。そして、例えばTEOS酸化膜及びSiN膜から

なるカバー膜を形成すると、強誘電体キャパシタを有する強誘電体メモリが完成する。

81の回復アニールによって上部領域78A及び下部領域78Bの酸素濃度が膜中心領域

78Cに比べて高くなるような構造を有する。このような第1保護膜78は、上部電極8

0をパターニングする際のメタルマスクになると共に、還元性物質の透過を防止する機能

を備える。即ち、強誘電体キャパシタ81のパターニングを行った後に、除去されること

なく上部電極80上に残されて、還元性物質が強誘電体キャパシタ81に透過することを

防止するバリア膜として機能する。これにより、半導体装置の製造工程を簡略化できると

共に、不良の発生が抑制されて生産効率が向上する。さらに、強誘電体メモリ(半導体装

置)の信頼性を向上できる。

、ゾル−ゲル法や、有機金属分解(MOD)法、CSD(Chemical Solution Deposition

)法、化学気相蒸着(CVD)法、エピタキシャル成長法等があげられる。

又はペロブスカイト構造となる膜を形成することができる。このような膜としては、PZ

T膜の他、La、Ca、Sr及び/又はSi等を微量ドープしたPZT、SBT、BLT

並びにBi系層状化合物などの一般式ABO3で表される膜が挙げられる。

ム、ロジウム、レニウム、オスミウム及び/又はパラジウムを含むターゲットを用いたス

パッタリングを、これらの貴金属元素の酸化が生じる条件下で行うことができる。特に、

Ir酸化膜を形成する場合には、成膜温度を20℃乃至400℃、例えば300℃とする

ことが好ましい。また、スパッタガスを構成する酸素ガス及び不活性ガスの圧力に対する

酸素ガスの分圧は10%乃至60%が好ましい。膜厚さは10nm乃至75nmとするこ

とが好ましい。

えば700℃とすることが好ましく、熱処理雰囲気は酸素含有量を1%乃至50%とする

ことが好ましい。

なく、白金(Pt)、イリジウム(Ir)、ルテニウム(Ru)、ロジウム(Rh)、レ

ニウム(Re)、オスミウム(Os)及び/又はパラジウム(Pd)等の貴金属元素を含

有する金属膜を形成しても良い。さらに、これらの酸化膜、例えばSrRuO3膜を形成

しても良い。また、導電膜として、2層構造以上、の膜を形成しても良い。

、図5に示すような構造にしても良い。

(付記1) 半導体基板と、

前記半導体基板上に絶縁膜を介して順次積層された下部電極、強誘電体膜及び上部電極

を有する強誘電体キャパシタと、

前記強誘電体キャパシタの積層方向において前記上部電極の上方に設けられ、膜厚方向

に酸素濃度の分布が異なる部分を有する第1保護膜と、

前記第1保護膜の上方、及び前記強誘電体キャパシタの側壁を含む領域に設けられる第

2保護膜と、

を有することを特徴とする半導体装置。(請求項1)

(付記2) 前記第1保護膜は、膜厚方向の上部領域より下部領域の前記酸素濃度が低い

部分を有することを特徴とする付記1に記載の半導体装置。(請求項2)

(付記3) 前記第1保護膜は、膜厚方向の上部領域及び下部領域より膜中心となる部分

の前記酸素濃度が低い部分を有することを特徴とする付記1に記載の半導体装置。(請求

項3)

(付記4) 前記第1保護膜は、前記上部領域の少なくとも一部が膜厚方向に均一な高い

前記酸素濃度を有し、前記下部領域が下方へ向かうほど前記酸素濃度が低くなっている部

分を有することを特徴とする付記1乃至付記3のいずれか一項に記載の半導体装置。

(付記5) 前記第1保護膜は、複数の膜を積層させた構成を有し、積層方向で最も下層

に配置される下層保護膜と、最も上側に配置される上層保護膜と、これら2つの膜に挟ま

れる中間保護膜を有し、前記中間保護膜の前記酸素濃度は、前記上層保護膜及び前記下層

保護膜のそれぞれの前記酸素濃度より低いことを特徴とする付記1に記載の半導体装置。

(付記6) 前記第1及び第2保護膜は異なる材料から形成されていることを特徴とする

付記1乃至付記5のいずれか一項に記載の半導体装置。

(付記7) 前記第2保護膜は、同一成分或いは異なる成分を有する複数の膜の積層体で

あることを特徴とする付記1乃至付記6のいずれか一項に記載の半導体装置。

(付記8) 前記第1保護膜は、TiOx、TiON、TaOx、TaON、TiAlO

x、TaAlOx、TiAlON、TaAlON、TiSiON、TaSiON、TiS

iOx、TaSiOx、AlOx、ZrOx膜からなる群から選択された1種であること

を特徴とする付記5に記載の半導体装置。

(付記9) 前記中間保護膜は、TiON、TaON、TiAlON、TaAlON、T

iSiON、TaSiON膜からなる群から選択された1種であることを特徴とする付記

5に記載の半導体装置。

(付記10) 前記第1保護膜は、上面が下面よりの面積が狭いことを特徴とする付記1

乃至付記9のいずれか一項に記載の半導体装置。

(付記11) 半導体基板の上方に下部導電膜、強誘電体膜、上部導電膜を積層する工程

と、

前記上部電極の上に第1保護膜を形成する工程と、

前記第1保護膜及び前記上部導電膜をパターニングすることにより、前記導電膜からキ

ャパシタの上部電極を形成する工程と、

前記強誘電体膜及び前記第1保護膜を酸素雰囲気中で加熱することにより、前記第1保

護膜中で酸素濃度が膜厚方向に異なる部分を形成する熱処理工程と、

前記強誘電体膜及び前記下部導電膜をパターニングすることにより、前記下部導電膜か

ら前記キャパシタの下部電極を形成する工程と、

前記第1保護膜及び前記キャパシタを覆う第2保護膜を形成する工程と、

を有する工程を含むことを特徴とする半導体装置の製造方法。(請求項4)

(付記12) 半導体基板の上方に下部導電膜、強誘電体膜、及び上部導電膜を順に積層

する工程と、

前記上部導電膜の上に第1のハードマスク及び第2のハードマスクを順番に形成する工

程と、

前記第1及び第2のハードマスクを用いて、前記下部導電膜、前記強誘電体膜、及び前

記上部導電膜をパターニングして強誘電体キャパシタを形成する工程と、

前記強誘電体キャパシタを形成した後に、前記第1のハードマスクを残して前記第2の

ハードマスクを除去する工程と、

前記強誘電体キャパシタ及び前記第1のハードマスクを酸素雰囲気中で加熱し、前記第

1のマスクの少なくとも一部を酸化させ膜厚方向で酸素濃度の分布が異なる部分を有する

第1保護膜を形成する熱処理工程と、

前記第1保護膜及び前記強誘電体キャパシタを覆う第2保護膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。(請求項5)

(付記13) 前記熱処理を行う工程を、550℃乃至700℃の温度条件下で行うこと

を特徴とする付記12に記載の半導体装置の製造方法。

(付記14) 前記上部導電膜として、貴金属の酸化物を含有する膜を形成することを特

徴とする付記12又は付記13に記載の半導体装置の製造方法。

(付記15) 前記熱処理は、前記第1のハードマスク中の前記酸素濃度を上部領域より

下部領域が低くなる部分を形成する工程を含むことを特徴とする付記12に記載の半導体

装置の製造方法。

(付記16) 前記熱処理は、前記第1のハードマスク中の前記酸素濃度を上部領域及び

下部領域よりも膜中心の方が低くなる部分を形成する工程を含むことを特徴とする付記1

2乃至付記15のいずれか一項に記載の半導体装置の製造方法。

(付記17) 前記上部導電膜と前記第1保護膜をパターニングする工程は、前記第1保

護膜の上面を下面の面積より狭くする工程を含むことを特徴とする付記12乃至付記16

のいずれか一つに記載の半導体装置の製造方法。

(付記18) 前記第1保護膜を形成する工程は、Ti、TiN、Ta、TaN、TiA

l、TaAl、TiAlN、TaAlN、TiSiN、TaSiN、TiSi、TaSi

膜からなる群から選択された1種の膜を形成する工程であることを特徴とする付記12乃

至付記17のいずれか一項に記載の半導体装置の製造方法。

(付記19) 前記第1保護膜を形成する工程は、積層方向で最も下層に配置される下層

保護膜と、前記下層保護膜上に形成される中間保護膜と、最も上側に配置される上層保護

膜とを順番に積層させる工程を含み、

前記中間保護膜は、前記上層保護膜及び前記下層保護膜のそれぞれより前記酸素濃度が

低くなるように形成することを特徴とする付記12乃至付記17に記載の半導体装置の製

造方法。

16 第1層間絶縁膜

11A 第1ソース/ドレイン領域

11B 第2ソース/ドレイン領域

17A,17B,17C 第1コンタクトホール

18A,18B,18C,18D,18E,44A,45B,45C,45D,45E

,64A,64B,90A,90B,90C 導電性プラグ

20,62 第2層間絶縁膜

22 第1導電膜

23,75 第1強誘電体膜

24,75 第2強誘電体膜

25 第2導電膜

26 酸化イリジウム膜

27,51,52,78 第1保護膜(第1のマスク)

27A,51B,52C,78A 上部領域

27B,51A,52A,78B 下部領域

27C,52B,78C 膜中心領域

28,80 上部電極

29,73 下部電極

30 第2保護膜

30A 第1層

30B 第2層

31,81 強誘電体キャパシタ

33,85 第3層間絶縁膜

35,87 第4層間絶縁膜

38 フォトレジスト膜

41,42,43,88,89 コンタクトホール

72A 第1下部電極膜

72B 第2下部電極膜

76A 第1上部電極膜

76B 第2上部電極膜

79 マスク材料層(第2のマスク)

Claims (5)

- 半導体基板と、

前記半導体基板上に絶縁膜を介して順次積層された下部電極、強誘電体膜及び上部電極

を有する強誘電体キャパシタと、

前記強誘電体キャパシタの積層方向において前記上部電極の上方に設けられ、膜厚方向

に酸素濃度の分布が異なる部分を有する第1保護膜と、

前記第1保護膜の上方、及び前記強誘電体キャパシタの側壁を含む領域に設けられる第

2保護膜と、

を有することを特徴とする半導体装置。 - 前記第1保護膜は、膜厚方向の上部領域より下部領域の前記酸素濃度が低い部分を有す

ることを特徴とする請求項1に記載の半導体装置。 - 前記第1保護膜は、膜厚方向の上部領域及び下部領域より膜中心となる部分の前記酸素

濃度が低い部分を有することを特徴とする請求項1に記載の半導体装置。 - 半導体基板の上方に下部導電膜、強誘電体膜、上部導電膜を積層する工程と、

前記上部電極の上に第1保護膜を形成する工程と、

前記第1保護膜及び前記上部導電膜をパターニングすることにより、前記導電膜からキ

ャパシタの上部電極を形成する工程と、

前記強誘電体膜及び前記第1保護膜を酸素雰囲気中で加熱することにより、前記第1保

護膜中で酸素濃度が膜厚方向に異なる部分を形成する熱処理工程と、

前記強誘電体膜及び前記下部導電膜をパターニングすることにより、前記下部導電膜か

ら前記キャパシタの下部電極を形成する工程と、

前記第1保護膜及び前記キャパシタを覆う第2保護膜を形成する工程と、

を有する工程を含むことを特徴とする半導体装置の製造方法。 - 半導体基板の上方に下部導電膜、強誘電体膜、及び上部導電膜を順に積層する工程と、

前記上部導電膜の上に第1のハードマスク及び第2のハードマスクを順番に形成する工

程と、

前記第1及び第2のハードマスクを用いて、前記下部導電膜、前記強誘電体膜、及び前

記上部導電膜をパターニングして強誘電体キャパシタを形成する工程と、

前記強誘電体キャパシタを形成した後に、前記第1のハードマスクを残して前記第2の

ハードマスクを除去する工程と、

前記強誘電体キャパシタ及び前記第1のハードマスクを酸素雰囲気中で加熱し、前記第

1のマスクの少なくとも一部を酸化させ膜厚方向で酸素濃度の分布が異なる部分を有する

第1保護膜を形成する熱処理工程と、

前記第1保護膜及び前記強誘電体キャパシタを覆う第2保護膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008159043A JP5412754B2 (ja) | 2008-06-18 | 2008-06-18 | 半導体装置及び半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008159043A JP5412754B2 (ja) | 2008-06-18 | 2008-06-18 | 半導体装置及び半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010003741A true JP2010003741A (ja) | 2010-01-07 |

| JP5412754B2 JP5412754B2 (ja) | 2014-02-12 |

Family

ID=41585241

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008159043A Expired - Fee Related JP5412754B2 (ja) | 2008-06-18 | 2008-06-18 | 半導体装置及び半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5412754B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012004448A (ja) * | 2010-06-18 | 2012-01-05 | Fujitsu Semiconductor Ltd | 半導体装置の製造方法 |

| JP2016033937A (ja) * | 2014-07-31 | 2016-03-10 | セイコーエプソン株式会社 | 圧電デバイスおよび超音波デバイス並びにプローブおよび電子機器 |

| JP2016134518A (ja) * | 2015-01-20 | 2016-07-25 | 富士通セミコンダクター株式会社 | 半導体装置とその製造方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000174215A (ja) * | 1998-12-01 | 2000-06-23 | Nec Corp | 強誘電体集積回路及びその製造方法 |

| WO2007116440A1 (ja) * | 2006-03-30 | 2007-10-18 | Fujitsu Limited | 半導体装置の製造方法 |

-

2008

- 2008-06-18 JP JP2008159043A patent/JP5412754B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000174215A (ja) * | 1998-12-01 | 2000-06-23 | Nec Corp | 強誘電体集積回路及びその製造方法 |

| WO2007116440A1 (ja) * | 2006-03-30 | 2007-10-18 | Fujitsu Limited | 半導体装置の製造方法 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012004448A (ja) * | 2010-06-18 | 2012-01-05 | Fujitsu Semiconductor Ltd | 半導体装置の製造方法 |

| JP2016033937A (ja) * | 2014-07-31 | 2016-03-10 | セイコーエプソン株式会社 | 圧電デバイスおよび超音波デバイス並びにプローブおよび電子機器 |

| JP2016134518A (ja) * | 2015-01-20 | 2016-07-25 | 富士通セミコンダクター株式会社 | 半導体装置とその製造方法 |

| CN109166852A (zh) * | 2015-01-20 | 2019-01-08 | 富士通半导体股份有限公司 | 半导体器件及其制造方法 |

| US10269813B2 (en) | 2015-01-20 | 2019-04-23 | Fujitsu Semiconductor Limited | Semiconductor device and method of manufacturing the same |

| CN109166852B (zh) * | 2015-01-20 | 2023-06-23 | 富士通半导体存储方案股份有限公司 | 半导体器件及其制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5412754B2 (ja) | 2014-02-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5251864B2 (ja) | 半導体装置及びその製造方法 | |

| US8236643B2 (en) | Method of manufacturing semiconductor device including ferroelectric capacitor | |

| JP4884104B2 (ja) | キャパシタを含む半導体装置及びその製造方法 | |

| JP4952148B2 (ja) | 半導体装置及びその製造方法 | |

| JP5092461B2 (ja) | 半導体装置及びその製造方法 | |

| JP5205741B2 (ja) | 半導体装置の製造方法 | |

| JP5211558B2 (ja) | 半導体装置の製造方法 | |

| JP4882548B2 (ja) | 半導体装置及びその製造方法 | |

| JP5347381B2 (ja) | 半導体装置の製造方法 | |

| JP4845624B2 (ja) | 半導体装置とその製造方法 | |

| JP5412754B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| KR101262432B1 (ko) | 반도체 장치의 제조 방법 | |

| JP5007723B2 (ja) | キャパシタを含む半導体装置及びその製造方法 | |

| JP5326256B2 (ja) | 半導体装置の製造方法 | |

| JP4716938B2 (ja) | 半導体装置の製造方法 | |

| JP2007266023A (ja) | 半導体装置、及び半導体装置の製造方法 | |

| JP2009194215A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130228 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130430 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130723 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130924 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131015 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131028 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5412754 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |