JP2009200570A - クロック再生回路 - Google Patents

クロック再生回路 Download PDFInfo

- Publication number

- JP2009200570A JP2009200570A JP2008037088A JP2008037088A JP2009200570A JP 2009200570 A JP2009200570 A JP 2009200570A JP 2008037088 A JP2008037088 A JP 2008037088A JP 2008037088 A JP2008037088 A JP 2008037088A JP 2009200570 A JP2009200570 A JP 2009200570A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- clock

- output

- phase

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000011084 recovery Methods 0.000 title claims abstract description 75

- 230000005540 biological transmission Effects 0.000 claims abstract description 55

- 238000005070 sampling Methods 0.000 claims abstract 5

- 239000003990 capacitor Substances 0.000 claims description 9

- 230000001934 delay Effects 0.000 claims description 2

- 230000008929 regeneration Effects 0.000 claims description 2

- 238000011069 regeneration method Methods 0.000 claims description 2

- 238000012935 Averaging Methods 0.000 abstract description 23

- 238000001514 detection method Methods 0.000 description 16

- 238000010586 diagram Methods 0.000 description 16

- 238000000034 method Methods 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 101100020619 Arabidopsis thaliana LATE gene Proteins 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- 239000013307 optical fiber Substances 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 230000000630 rising effect Effects 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 230000007423 decrease Effects 0.000 description 2

- 238000003708 edge detection Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000003111 delayed effect Effects 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000013139 quantization Methods 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/087—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using at least two phase detectors or a frequency and phase detector in the loop

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/027—Speed or phase control by the received code signals, the signals containing no special synchronisation information extracting the synchronising or clock signal from the received signal spectrum, e.g. by using a resonant or bandpass circuit

- H04L7/0276—Self-sustaining, e.g. by tuned delay line and a feedback path to a logical gate

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/027—Speed or phase control by the received code signals, the signals containing no special synchronisation information extracting the synchronising or clock signal from the received signal spectrum, e.g. by using a resonant or bandpass circuit

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

- H04L7/10—Arrangements for initial synchronisation

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Abstract

【解決手段】入力データ信号101と再生クロック102との位相差を検出する位相差検出回路103、位相差検出回路103の出力を平均化する平均化回路104、位相差検出回路103の出力をサンプル/ホールドするリセット付サンプル/ホールド回路105、平均化回路104の出力の積分値とリセット付サンプル/ホールド回路105の出力値との和に相当する位相の再生クロック102を生成する再生クロック生成回路106を備える。リセット付サンプル/ホールド回路105は、バースト伝送開始信号110を受けて位相差検出回路103の出力をサンプル/ホールドし、バースト伝送終了信号111を受けてホールドしている値を初期値にリセットする。

【選択図】図1

Description

図1は、本発明の実施の形態1によるクロック再生回路において、その構成の一例を示すブロック図である。本実施の形態1によるクロック再生回路は、入力データ信号101を受けて、再生クロック102を出力する回路であり、位相差検出回路103(第1回路)と、平均化回路104(第2回路)と、リセット付サンプル/ホールド回路105(第3回路)と、再生クロック生成回路106(第4回路)と、を備えている。また、再生クロック生成回路106は、可変位相クロック生成回路113(第6回路)と、クロック位相調整回路(1)114(第7回路)と、を備えている。

図5は、本発明の実施の形態2によるクロック再生回路において、その構成の一例を示すブロック図である。本実施の形態2によるクロック再生回路は、実施の形態1におけるリセット付サンプル/ホールド回路105をリーク付サンプル/ホールド回路501(第5回路)に置き換えた構成をしている。

102 再生クロック

103 位相差検出回路

104 平均化回路

105 リセット付サンプル/ホールド回路

106 再生クロック生成回路

107 低速用位相差信号

108 高速用位相差信号

109 低速クロック位相制御信号

110 バースト伝送開始信号

111 バースト伝送終了信号

112 高速クロック位相調整信号

113 可変位相クロック生成回路

114 クロック位相調整回路(1)

201 積分回路

202 低速クロック位相調整信号

203 リファレンスクロック

204 クロック位相調整回路(2)

301 デジタル出力位相比較器

302 アナログ出力位相比較器

501 リーク付サンプル/ホールド回路

601 スイッチ

602 容量

603 抵抗

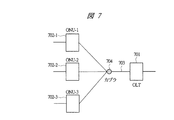

701 OLT(Optical Line Terminal)

702 ONU(Optical Network Unit)

703 光ファイバ

704 カプラ

801 バーストデータ信号

802 プリアンブル

803 ペイロード

901 位相差検出回路

902 EARLY信号

903 LATE信号

904 平均化回路

905 UP信号

906 DOWN信号

907 クロック位相調整回路

908 リファレンスクロック

1001 内部クロック発生回路

1002 内部クロック周波数制御回路

1003 制御信号

1004 エッジ検出回路

1005 内部クロック位相リセット信号

Claims (8)

- 入力データ信号から再生クロックを生成するクロック再生回路であって、

前記入力データ信号と前記再生クロックとの位相差を検出して出力する第1回路と、

前記第1回路の出力を平均化して出力する第2回路と、

前記第1回路の出力をサンプル/ホールドして出力する第3回路と、

前記第2回路の出力の積分値と前記第3回路の出力値との和に相当する位相のクロックを生成して前記再生クロックとして出力する第4回路と、を備え、

前記第3回路は、バースト伝送開始信号を受けて前記第1回路の出力をサンプル/ホールドして出力し、バースト伝送終了信号を受けてホールドしている値を初期値にリセットすることを特徴とするクロック再生回路。 - 入力データ信号から再生クロックを生成するクロック再生回路であって、

前記入力データ信号と前記再生クロックとの位相差を検出して出力する第1回路と、

前記第1回路の出力を平均化して出力する第2回路と、

前記第1回路の出力をサンプル/ホールドして出力する第5回路と、

前記第2回路の出力の積分値と前記第5回路の出力値との和に相当する位相のクロックを生成して前記再生クロックとして出力する第4回路と、を備え、

前記第5回路は、バースト伝送開始信号を受けて前記第1回路の出力をサンプル/ホールドして出力し、その後、ホールドしている値が初期値に向かって変化することを特徴とするクロック再生回路。 - 請求項2記載のクロック再生回路において、

前記第5回路は、

前記第1回路の出力と前記第5回路の出力との間を開閉するスイッチと、

前記第5回路の出力とグランドとの間に並列に接続された容量と抵抗と、を備え、

前記スイッチは、前記バースト伝送開始信号を受けて閉じることを特徴とするクロック再生回路。 - 請求項2または3記載のクロック再生回路において、

前記第5回路がホールドしている値が初期値に向かって変化する速度は、前記第2回路の動作速度に比べて遅く、かつ、前記入力データ信号の各バースト時間幅よりは短いことを特徴とするクロック再生回路。 - 請求項1〜4のいずれか1項に記載のクロック再生回路において、

前記第4回路は、

前記第2回路の積分値に相当する位相のクロックを発生する第6回路と、

前記第3回路または前記第5回路の出力に相当するだけ、入力されたクロックの位相を変化させる第7回路と、を備え、

前記第6回路と前記第7回路とが従続接続されていることを特徴とするクロック再生回路。 - 請求項5記載のクロック再生回路において、

前記第6回路は、前記第2回路の出力に相当する周波数のクロックを発生させることを特徴とするクロック再生回路。 - 請求項5記載のクロック再生回路において、

前記第6回路は、外部から供給されたクロックの位相を、前記第2回路の積分値に相当する値だけ変化させて出力することを特徴とするクロック再生回路。 - 請求項5記載のクロック再生回路において、

前記第7回路は、入力されたクロックを、前記第3回路または前記第5回路の出力に相当する値だけ遅延させる可変遅延回路であることを特徴とするクロック再生回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008037088A JP4972580B2 (ja) | 2008-02-19 | 2008-02-19 | クロック再生回路 |

| US12/320,573 US8149973B2 (en) | 2008-02-19 | 2009-01-29 | Clock recovery circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008037088A JP4972580B2 (ja) | 2008-02-19 | 2008-02-19 | クロック再生回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009200570A true JP2009200570A (ja) | 2009-09-03 |

| JP4972580B2 JP4972580B2 (ja) | 2012-07-11 |

Family

ID=40955102

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008037088A Expired - Fee Related JP4972580B2 (ja) | 2008-02-19 | 2008-02-19 | クロック再生回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8149973B2 (ja) |

| JP (1) | JP4972580B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8483579B2 (en) | 2008-08-29 | 2013-07-09 | Hitachi, Ltd. | Phase detector circuit for clock and data recovery circuit and optical communication device having the same |

| JP2014171238A (ja) * | 2014-04-25 | 2014-09-18 | Spansion Llc | 受信装置及びゲイン設定方法 |

| WO2016152438A1 (ja) * | 2015-03-24 | 2016-09-29 | ソニー株式会社 | 受信装置および受信方法 |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8630821B2 (en) * | 2011-07-25 | 2014-01-14 | Qualcomm Incorporated | High speed data testing without high speed bit clock |

| US8839020B2 (en) * | 2012-01-24 | 2014-09-16 | Qualcomm Incorporated | Dual mode clock/data recovery circuit |

| CN104221276A (zh) * | 2012-04-25 | 2014-12-17 | 赛诺菲-安万特德国有限公司 | 包括机电装置和运动检测器的设备以及用于操作设备的方法 |

| US9265458B2 (en) | 2012-12-04 | 2016-02-23 | Sync-Think, Inc. | Application of smooth pursuit cognitive testing paradigms to clinical drug development |

| US9385858B2 (en) * | 2013-02-20 | 2016-07-05 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Timing phase estimation for clock and data recovery |

| US9380976B2 (en) | 2013-03-11 | 2016-07-05 | Sync-Think, Inc. | Optical neuroinformatics |

| US9698808B1 (en) * | 2016-10-27 | 2017-07-04 | Cavium, Inc. | Phase measurement and correction circuitry |

| JP2019169779A (ja) * | 2018-03-22 | 2019-10-03 | 東芝メモリ株式会社 | クロック・データ再生装置、メモリシステム及びデータ再生方法 |

| CN112840593B (zh) * | 2018-12-21 | 2022-05-13 | 华为技术有限公司 | 一种跨时钟域处理电路 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5753192A (en) * | 1980-09-16 | 1982-03-30 | Nec Corp | Subcarrier signal reproducing circuit |

| JPS59141835A (ja) * | 1983-02-03 | 1984-08-14 | Nec Corp | バ−スト通信用位相同期回路 |

| JPS62160821A (ja) * | 1986-01-10 | 1987-07-16 | Hitachi Ltd | バ−スト信号用pll回路 |

| JPS62183292A (ja) * | 1986-02-06 | 1987-08-11 | Nec Corp | 副搬送波信号発生装置 |

| JPS6387036A (ja) * | 1986-09-30 | 1988-04-18 | Mitsubishi Electric Corp | 自動周波数制御回路 |

| JPH0256134A (ja) * | 1988-08-22 | 1990-02-26 | Nippon Telegr & Teleph Corp <Ntt> | クロック再生方式 |

| JPH0738910A (ja) * | 1993-07-24 | 1995-02-07 | Nec Corp | バースト制御発振回路 |

| JPH09148922A (ja) * | 1995-11-17 | 1997-06-06 | Fujitsu Ltd | 高速同期型水晶発振回路 |

| JP2003018229A (ja) * | 2001-07-03 | 2003-01-17 | Nec Eng Ltd | クロック再生回路 |

| JP2006211143A (ja) * | 2005-01-26 | 2006-08-10 | Ntt Electornics Corp | クロック及びデータ再生回路 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4947407A (en) * | 1989-08-08 | 1990-08-07 | Siemens-Pacesetter, Inc. | Sample-and-hold digital phase-locked loop for ask signals |

| JP4196657B2 (ja) | 2002-11-29 | 2008-12-17 | 株式会社日立製作所 | データ再生方法およびデジタル制御型クロックデータリカバリ回路 |

| US7764759B2 (en) * | 2006-06-13 | 2010-07-27 | Gennum Corporation | Linear sample and hold phase detector for clocking circuits |

-

2008

- 2008-02-19 JP JP2008037088A patent/JP4972580B2/ja not_active Expired - Fee Related

-

2009

- 2009-01-29 US US12/320,573 patent/US8149973B2/en not_active Expired - Fee Related

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5753192A (en) * | 1980-09-16 | 1982-03-30 | Nec Corp | Subcarrier signal reproducing circuit |

| JPS59141835A (ja) * | 1983-02-03 | 1984-08-14 | Nec Corp | バ−スト通信用位相同期回路 |

| JPS62160821A (ja) * | 1986-01-10 | 1987-07-16 | Hitachi Ltd | バ−スト信号用pll回路 |

| JPS62183292A (ja) * | 1986-02-06 | 1987-08-11 | Nec Corp | 副搬送波信号発生装置 |

| JPS6387036A (ja) * | 1986-09-30 | 1988-04-18 | Mitsubishi Electric Corp | 自動周波数制御回路 |

| JPH0256134A (ja) * | 1988-08-22 | 1990-02-26 | Nippon Telegr & Teleph Corp <Ntt> | クロック再生方式 |

| JPH0738910A (ja) * | 1993-07-24 | 1995-02-07 | Nec Corp | バースト制御発振回路 |

| JPH09148922A (ja) * | 1995-11-17 | 1997-06-06 | Fujitsu Ltd | 高速同期型水晶発振回路 |

| JP2003018229A (ja) * | 2001-07-03 | 2003-01-17 | Nec Eng Ltd | クロック再生回路 |

| JP2006211143A (ja) * | 2005-01-26 | 2006-08-10 | Ntt Electornics Corp | クロック及びデータ再生回路 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8483579B2 (en) | 2008-08-29 | 2013-07-09 | Hitachi, Ltd. | Phase detector circuit for clock and data recovery circuit and optical communication device having the same |

| JP2014171238A (ja) * | 2014-04-25 | 2014-09-18 | Spansion Llc | 受信装置及びゲイン設定方法 |

| WO2016152438A1 (ja) * | 2015-03-24 | 2016-09-29 | ソニー株式会社 | 受信装置および受信方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4972580B2 (ja) | 2012-07-11 |

| US8149973B2 (en) | 2012-04-03 |

| US20090207957A1 (en) | 2009-08-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4972580B2 (ja) | クロック再生回路 | |

| JP4196657B2 (ja) | データ再生方法およびデジタル制御型クロックデータリカバリ回路 | |

| US7239813B2 (en) | Bit synchronization circuit and central terminal for PON systems | |

| US8649473B2 (en) | Method and apparatus for receiving burst data without using external detection signal | |

| KR100603180B1 (ko) | 주파수 트래킹 기법을 이용한 씨모오스 버스트 모드 클럭데이터 복원 회로 | |

| US7519750B2 (en) | Linear burst mode synchronizer for passive optical networks | |

| JP5476229B2 (ja) | バーストデータ信号受信方法および装置 | |

| US8355431B2 (en) | Decision feedback equalizer having clock recovery circuit and method for recovering clock | |

| US9136949B1 (en) | Circuits and methods for data detection | |

| JP2008503931A (ja) | アイドル時間ループスタビライザを備えた電荷ポンプpllに基づいたバーストモード受信器 | |

| US5799049A (en) | Phase-independent clock circuit and method | |

| US20230259473A1 (en) | Dynamic timing calibration systems and methods | |

| US7515668B1 (en) | Data and/or clock recovery circuits with sampling offset correction | |

| US20100135666A1 (en) | Clock phase aligning apparatus for burst-mode data | |

| KR101203457B1 (ko) | 중앙제어장치를 사용한 다중채널수신기 | |

| JP5704988B2 (ja) | 通信装置 | |

| JPWO2017090207A1 (ja) | 光受信器、光通信装置および制御方法 | |

| US12052020B2 (en) | Methods and systems for controlling frequency and phase variations for PLL reference clocks | |

| KR100408753B1 (ko) | 이퀄라이징 기법을 이용한 데이터와 클럭의 스큐를보상하는 수신기 | |

| WO2020186647A1 (en) | Improved burst-mode clock-data-recovery (bm-cdr) for 10g-pon | |

| KR100646197B1 (ko) | 라인 이퀄라이저용 시간 지연회로를 포함하는 수신기 회로. | |

| US7136447B2 (en) | Clock recovery circuit | |

| JP5612499B2 (ja) | Cdr回路 | |

| JP5438055B2 (ja) | Cdr回路 | |

| JP7169781B2 (ja) | 信号処理装置および方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100909 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120305 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120313 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120409 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150413 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |