JP2009004756A - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP2009004756A JP2009004756A JP2008127915A JP2008127915A JP2009004756A JP 2009004756 A JP2009004756 A JP 2009004756A JP 2008127915 A JP2008127915 A JP 2008127915A JP 2008127915 A JP2008127915 A JP 2008127915A JP 2009004756 A JP2009004756 A JP 2009004756A

- Authority

- JP

- Japan

- Prior art keywords

- crystal semiconductor

- semiconductor layer

- single crystal

- substrate

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 432

- 238000000034 method Methods 0.000 title claims abstract description 77

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 37

- 239000013078 crystal Substances 0.000 claims abstract description 308

- 239000000758 substrate Substances 0.000 claims abstract description 179

- 239000012298 atmosphere Substances 0.000 claims abstract description 75

- 230000001678 irradiating effect Effects 0.000 claims description 26

- 239000004973 liquid crystal related substance Substances 0.000 claims description 14

- 238000005401 electroluminescence Methods 0.000 claims description 12

- 150000002500 ions Chemical class 0.000 abstract description 35

- 238000010438 heat treatment Methods 0.000 abstract description 19

- 238000003776 cleavage reaction Methods 0.000 abstract 1

- 230000007017 scission Effects 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 315

- 239000010408 film Substances 0.000 description 282

- 229910052581 Si3N4 Inorganic materials 0.000 description 32

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 32

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 28

- 229910052710 silicon Inorganic materials 0.000 description 28

- 239000010703 silicon Substances 0.000 description 28

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 20

- 229910052814 silicon oxide Inorganic materials 0.000 description 19

- 229910052739 hydrogen Inorganic materials 0.000 description 16

- 239000001257 hydrogen Substances 0.000 description 16

- 239000007789 gas Substances 0.000 description 15

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 14

- 239000000463 material Substances 0.000 description 14

- 239000001301 oxygen Substances 0.000 description 14

- 229910052760 oxygen Inorganic materials 0.000 description 14

- 238000005229 chemical vapour deposition Methods 0.000 description 11

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 10

- 238000010521 absorption reaction Methods 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 9

- 239000011521 glass Substances 0.000 description 9

- 239000012535 impurity Substances 0.000 description 9

- 239000011229 interlayer Substances 0.000 description 9

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 8

- 229910000077 silane Inorganic materials 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 229910021417 amorphous silicon Inorganic materials 0.000 description 7

- 229910052802 copper Inorganic materials 0.000 description 7

- 239000010949 copper Substances 0.000 description 7

- 239000012299 nitrogen atmosphere Substances 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- 238000001069 Raman spectroscopy Methods 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 238000001514 detection method Methods 0.000 description 5

- 230000006870 function Effects 0.000 description 5

- 238000005468 ion implantation Methods 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 5

- 230000001681 protective effect Effects 0.000 description 5

- 230000004044 response Effects 0.000 description 5

- 238000000926 separation method Methods 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- 238000002834 transmittance Methods 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 4

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- 238000011156 evaluation Methods 0.000 description 4

- 238000002474 experimental method Methods 0.000 description 4

- 150000002431 hydrogen Chemical class 0.000 description 4

- 230000031700 light absorption Effects 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 238000004140 cleaning Methods 0.000 description 3

- 238000011109 contamination Methods 0.000 description 3

- 238000002425 crystallisation Methods 0.000 description 3

- 230000008025 crystallization Effects 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 230000006872 improvement Effects 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 229960001730 nitrous oxide Drugs 0.000 description 3

- 235000013842 nitrous oxide Nutrition 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 238000002310 reflectometry Methods 0.000 description 3

- 239000010979 ruby Substances 0.000 description 3

- 229910001750 ruby Inorganic materials 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 2

- 229910018125 Al-Si Inorganic materials 0.000 description 2

- 229910018520 Al—Si Inorganic materials 0.000 description 2

- 229910018575 Al—Ti Inorganic materials 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 239000006117 anti-reflective coating Substances 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000001678 elastic recoil detection analysis Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- -1 hydrogen ions Chemical class 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 238000005499 laser crystallization Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 2

- 150000001282 organosilanes Chemical class 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000011084 recovery Methods 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- 230000003746 surface roughness Effects 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000009191 jumping Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000000376 reactant Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/268—Bombardment with radiation with high-energy radiation using electromagnetic radiation, e.g. laser radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1229—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with different crystal properties within a device or between different devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1262—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate

- H01L27/1266—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate the substrate on which the devices are formed not being the final device substrate, e.g. using a temporary substrate

Abstract

【解決手段】基板上に、単結晶半導体基板にイオンを打ち込み前記基板に貼り付けた後熱処理を加えることにより残存させた単結晶半導体層を有する第1の領域と、非単結晶半導体層を有する第2の領域と、を設ける。また、劈開単結晶半導体層に不活性雰囲気中においてレーザー光の照射を行い、非単結晶半導体層には、少なくとも一度、大気雰囲気中においてレーザー光の照射を行うとより好ましい。

【選択図】図7

Description

本実施の形態では、劈開単結晶半導体層を有する第1の領域と、非単結晶半導体層を有する第2の領域と、を有する表示装置について説明する。

本実施の形態では、劈開単結晶半導体層を有する第1の領域と、非単結晶半導体層を有する第2の領域と、を有する非接触でデータの入出力が可能である半導体装置について説明する。

本実施の形態では、図4、図5を用いて、劈開単結晶半導体層の作製方法について説明する。

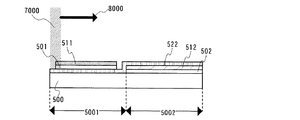

本実施の形態では、劈開単結晶半導体層を有する第1の領域5001と、非単結晶半導体層を有する第2の領域5002と、にレーザー光を照射するまでの工程について説明する。

本実施の形態では、劈開単結晶半導体層を有する第1の領域5001と、非単結晶半導体層を有する第2の領域5002と、にレーザー光を照射するまでの工程について説明する。

本実施の形態では、劈開単結晶半導体層を有する第1の領域5001と、非単結晶半導体層を有する第2の領域5002と、にレーザー光を照射するまでの工程について説明する。

本実施の形態では、半導体装置を作製する工程について説明する。

本実施の形態では、キャップ膜を用いたレーザー結晶化を含む工程について説明する。

本実施の形態では、劈開単結晶半導体層及び非単結晶半導体層の表面の平坦性、並びに、劈開単結晶半導体層及び非単結晶半導体層を用いたデバイスの特性について説明する。

本実施の形態では、レーザー照射モニター基板について説明する。

表示装置又は非接触タグを形成する場合、同一基板上にフォトICを同時に形成すると好ましい。

本実施の形態においては、本発明の半導体装置の例について説明する。

101 第1の単結晶半導体層

102 第2の単結晶半導体層

103 イオン層

104 接合層

500 基板

501 絶縁膜

502 下地膜

511 劈開単結晶半導体層

512 非単結晶半導体層

521 第1のキャップ膜

522 キャップ膜

530 ゲート絶縁膜

540 層間絶縁膜

541 ゲート電極

542 ゲート電極

551a 配線

551b 配線

552a 配線

552b 配線

1001 ソースドライバ回路

1002 ゲートドライバ回路

1011 画素部

2001 アンテナ

2002 整流回路

2003 復調回路

2004 変調回路

2006 レギュレータ

2007 VCO

2008 メモリ

2009 論理回路

5001 第1の領域

5002 第2の領域

7000 レーザー光

7001 レーザー光

7002 レーザー光

7003 レーザー光

7004 レーザー光

7005 レーザー光

7006 レーザー光

7007 レーザー光

7008 レーザー光

7009 レーザー光

8000 矢印

8001 矢印

8002 矢印

8003 矢印

8004 矢印

8005 矢印

8006 矢印

8007 矢印

8008 矢印

8009 矢印

10000 基板

20000 基板

Claims (8)

- 基板上に非単結晶半導体膜を形成し、

前記基板上の第1の領域の前記非単結晶半導体膜を除去することによって、前記基板上の第2の領域に非単結晶半導体層を形成し、

イオン種を単結晶半導体基板に注入又はドーピングして、前記単結晶半導体基板の表面から所定の深さの領域にイオン層を形成し、

前記単結晶半導体基板の表面に接合層を形成し、

前記接合層を前記第1の領域に貼り合わせ、

前記単結晶半導体基板にエネルギーを加えて、前記イオン層に亀裂を生じさせることにより、前記第1の領域に単結晶半導体層を残存させ、

前記単結晶半導体層に不活性雰囲気中でレーザー光の照射を行う工程と、前記非単結晶半導体層に大気雰囲気中でレーザー光の照射を行う工程と、を行うことを特徴とする半導体装置の作製方法。 - 基板上に非単結晶半導体膜を形成し、

前記基板上の第1の領域の前記非単結晶半導体膜を除去することによって、前記基板上の第2の領域に非単結晶半導体層を形成し、

イオン種を単結晶半導体基板に注入又はドーピングして、前記単結晶半導体基板の表面から所定の深さの領域にイオン層を形成し、

前記単結晶半導体基板の表面に接合層を形成し、

前記接合層を前記第1の領域に貼り合わせ、

前記単結晶半導体基板にエネルギーを加えて、前記イオン層に亀裂を生じさせることにより、前記第1の領域に単結晶半導体層を残存させ、

大気雰囲気において前記非単結晶半導体層に第1のレーザー光を照射し、

不活性雰囲気において前記非単結晶半導体層及び前記単結晶半導体層に第2のレーザー光を照射することを特徴とする半導体装置の作製方法。 - 基板上に非単結晶半導体膜を形成し、

大気雰囲気において前記非単結晶半導体膜に第1のレーザー光を照射し、

前記基板上の第1の領域の前記非単結晶半導体膜を除去することによって、前記基板上の第2の領域に非単結晶半導体層を形成し、

イオン種を単結晶半導体基板に注入又はドーピングして、前記単結晶半導体基板の表面から所定の深さの領域にイオン層を形成し、

前記単結晶半導体基板の表面に接合層を形成し、

前記接合層を前記第1の領域に貼り合わせ、

前記単結晶半導体基板にエネルギーを加えて、前記イオン層に亀裂を生じさせることにより、前記第1の領域に単結晶半導体層を残存させ、

不活性雰囲気において前記非単結晶半導体層及び前記単結晶半導体層に第2のレーザー光を照射することを特徴とする半導体装置の作製方法。 - 基板上に非単結晶半導体膜を形成し、

前記基板上の第1の領域の前記非単結晶半導体膜を除去することによって、前記基板上の第2の領域に非単結晶半導体層を形成し、

イオン種を単結晶半導体基板に注入又はドーピングして、前記単結晶半導体基板の表面から所定の深さの領域にイオン層を形成し、

前記単結晶半導体基板の表面に接合層を形成し、

前記接合層を前記第1の領域に貼り合わせ、

前記単結晶半導体基板にエネルギーを加えて、前記イオン層に亀裂を生じさせることにより、前記第1の領域に単結晶半導体層を残存させ、

前記非単結晶半導体層上にキャップ膜を形成し、

不活性雰囲気において、前記キャップ膜の上から前記非単結晶半導体層及び前記単結晶半導体層に第1のレーザー光を照射し、

前記キャップ膜を除去し、

大気雰囲気において、前記非単結晶半導体層に第2のレーザー光を照射することを特徴とする半導体装置の作製方法。 - 請求項4において、

前記第1のレーザー光のエネルギー密度の設定条件は、非単結晶半導体からなるレーザー照射モニターを用いて決定した最適条件を用いることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか一項において、

前記第1の領域に駆動回路を形成し、

前記第2の領域に液晶表示素子を有する画素部を形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか一項において、

前記第1の領域にエレクトロルミネッセンス表示素子を有する画素部を形成し、

前記第2の領域に駆動回路を形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項6のいずれか一項において、

前記第1の領域にアナログ回路を形成し、

前記第2の領域にデジタル回路を形成することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008127915A JP2009004756A (ja) | 2007-05-18 | 2008-05-15 | 半導体装置の作製方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007132540 | 2007-05-18 | ||

| JP2008127915A JP2009004756A (ja) | 2007-05-18 | 2008-05-15 | 半導体装置の作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014094751A Division JP2014170959A (ja) | 2007-05-18 | 2014-05-01 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009004756A true JP2009004756A (ja) | 2009-01-08 |

| JP2009004756A5 JP2009004756A5 (ja) | 2011-05-06 |

Family

ID=40027928

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008127915A Withdrawn JP2009004756A (ja) | 2007-05-18 | 2008-05-15 | 半導体装置の作製方法 |

| JP2014094751A Withdrawn JP2014170959A (ja) | 2007-05-18 | 2014-05-01 | 半導体装置の作製方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014094751A Withdrawn JP2014170959A (ja) | 2007-05-18 | 2014-05-01 | 半導体装置の作製方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7960262B2 (ja) |

| JP (2) | JP2009004756A (ja) |

| CN (1) | CN101308772B (ja) |

| TW (1) | TWI476927B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020516085A (ja) * | 2017-03-31 | 2020-05-28 | アールエヌアール ラボラトリー インコーポレイテッド | レーザを用いた間接加熱方法 |

| US10836633B2 (en) | 2015-12-28 | 2020-11-17 | Hitachi Zosen Corporation | Carbon nanotube composite material and method for producing carbon nanotube composite material |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8236668B2 (en) * | 2007-10-10 | 2012-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate |

| JP5654206B2 (ja) | 2008-03-26 | 2015-01-14 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法及び該soi基板を用いた半導体装置 |

| JP2009260315A (ja) * | 2008-03-26 | 2009-11-05 | Semiconductor Energy Lab Co Ltd | Soi基板の作製方法及び半導体装置の作製方法 |

| JP5552276B2 (ja) * | 2008-08-01 | 2014-07-16 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| SG161151A1 (en) * | 2008-10-22 | 2010-05-27 | Semiconductor Energy Lab | Soi substrate and method for manufacturing the same |

| SG162675A1 (en) * | 2008-12-15 | 2010-07-29 | Semiconductor Energy Lab | Manufacturing method of soi substrate and manufacturing method of semiconductor device |

| WO2013054823A1 (en) * | 2011-10-14 | 2013-04-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP6743752B2 (ja) | 2017-04-20 | 2020-08-19 | 三菱電機株式会社 | 半導体装置の製造方法 |

| CN107833924B (zh) * | 2017-10-26 | 2020-06-19 | 京东方科技集团股份有限公司 | 顶栅型薄膜晶体管及其制备方法、阵列基板、显示面板 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000216265A (ja) * | 1999-01-22 | 2000-08-04 | Mega Chips Corp | 半導体装置及びその製造方法 |

| JP2001318652A (ja) * | 2000-05-08 | 2001-11-16 | Matsushita Electric Ind Co Ltd | アクティブマトリクス液晶表示素子 |

| JP2003282885A (ja) * | 2002-03-26 | 2003-10-03 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2006121060A (ja) * | 2004-09-24 | 2006-05-11 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法、並びに電子機器 |

| WO2006117900A1 (ja) * | 2005-04-26 | 2006-11-09 | Sharp Kabushiki Kaisha | 半導体装置の製造方法及び半導体装置 |

| JP2007036216A (ja) * | 2005-06-24 | 2007-02-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及び無線通信システム |

| JP2007079431A (ja) * | 2005-09-16 | 2007-03-29 | Toshiba Matsushita Display Technology Co Ltd | 表示素子用アレイ基板及びその作製方法、これを用いた表示素子 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5528397A (en) * | 1991-12-03 | 1996-06-18 | Kopin Corporation | Single crystal silicon transistors for display panels |

| US5923962A (en) | 1993-10-29 | 1999-07-13 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| JP3431033B2 (ja) | 1993-10-29 | 2003-07-28 | 株式会社半導体エネルギー研究所 | 半導体作製方法 |

| TW264575B (ja) | 1993-10-29 | 1995-12-01 | Handotai Energy Kenkyusho Kk | |

| JP3067949B2 (ja) | 1994-06-15 | 2000-07-24 | シャープ株式会社 | 電子装置および液晶表示装置 |

| US6534380B1 (en) | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| JPH1197379A (ja) | 1997-07-25 | 1999-04-09 | Denso Corp | 半導体基板及び半導体基板の製造方法 |

| JPH11163363A (ja) | 1997-11-22 | 1999-06-18 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP4476390B2 (ja) | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4379943B2 (ja) | 1999-04-07 | 2009-12-09 | 株式会社デンソー | 半導体基板の製造方法および半導体基板製造装置 |

| JP4101409B2 (ja) * | 1999-08-19 | 2008-06-18 | シャープ株式会社 | 半導体装置の製造方法 |

| JP2003142402A (ja) * | 2001-08-10 | 2003-05-16 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP4772258B2 (ja) * | 2002-08-23 | 2011-09-14 | シャープ株式会社 | Soi基板の製造方法 |

| US7119365B2 (en) * | 2002-03-26 | 2006-10-10 | Sharp Kabushiki Kaisha | Semiconductor device and manufacturing method thereof, SOI substrate and display device using the same, and manufacturing method of the SOI substrate |

| US7508034B2 (en) | 2002-09-25 | 2009-03-24 | Sharp Kabushiki Kaisha | Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device |

| JP4759919B2 (ja) | 2004-01-16 | 2011-08-31 | セイコーエプソン株式会社 | 電気光学装置の製造方法 |

| JP5110772B2 (ja) | 2004-02-03 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 半導体薄膜層を有する基板の製造方法 |

| KR101299604B1 (ko) * | 2005-10-18 | 2013-08-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| CN101281912B (zh) | 2007-04-03 | 2013-01-23 | 株式会社半导体能源研究所 | Soi衬底及其制造方法以及半导体装置 |

| KR101457656B1 (ko) | 2007-05-17 | 2014-11-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치의 제조방법, 표시장치의 제조방법, 반도체장치,표시장치 및 전자기기 |

| US7745268B2 (en) | 2007-06-01 | 2010-06-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device with irradiation of single crystal semiconductor layer in an inert atmosphere |

-

2008

- 2008-03-28 TW TW097111176A patent/TWI476927B/zh not_active IP Right Cessation

- 2008-03-28 US US12/078,215 patent/US7960262B2/en not_active Expired - Fee Related

- 2008-03-31 CN CN200810088431.2A patent/CN101308772B/zh not_active Expired - Fee Related

- 2008-05-15 JP JP2008127915A patent/JP2009004756A/ja not_active Withdrawn

-

2014

- 2014-05-01 JP JP2014094751A patent/JP2014170959A/ja not_active Withdrawn

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000216265A (ja) * | 1999-01-22 | 2000-08-04 | Mega Chips Corp | 半導体装置及びその製造方法 |

| JP2001318652A (ja) * | 2000-05-08 | 2001-11-16 | Matsushita Electric Ind Co Ltd | アクティブマトリクス液晶表示素子 |

| JP2003282885A (ja) * | 2002-03-26 | 2003-10-03 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2006121060A (ja) * | 2004-09-24 | 2006-05-11 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法、並びに電子機器 |

| WO2006117900A1 (ja) * | 2005-04-26 | 2006-11-09 | Sharp Kabushiki Kaisha | 半導体装置の製造方法及び半導体装置 |

| JP2007036216A (ja) * | 2005-06-24 | 2007-02-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及び無線通信システム |

| JP2007079431A (ja) * | 2005-09-16 | 2007-03-29 | Toshiba Matsushita Display Technology Co Ltd | 表示素子用アレイ基板及びその作製方法、これを用いた表示素子 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10836633B2 (en) | 2015-12-28 | 2020-11-17 | Hitachi Zosen Corporation | Carbon nanotube composite material and method for producing carbon nanotube composite material |

| US11414321B2 (en) | 2015-12-28 | 2022-08-16 | Hitachi Zosen Corporation | Carbon nanotube composite material and method for producing carbon nanotube composite material |

| JP2020516085A (ja) * | 2017-03-31 | 2020-05-28 | アールエヌアール ラボラトリー インコーポレイテッド | レーザを用いた間接加熱方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI476927B (zh) | 2015-03-11 |

| US7960262B2 (en) | 2011-06-14 |

| CN101308772B (zh) | 2013-01-02 |

| JP2014170959A (ja) | 2014-09-18 |

| TW200903811A (en) | 2009-01-16 |

| CN101308772A (zh) | 2008-11-19 |

| US20080286911A1 (en) | 2008-11-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5331381B2 (ja) | 半導体装置の作製方法 | |

| JP2009004756A (ja) | 半導体装置の作製方法 | |

| CN101471248B (zh) | 半导体衬底的制造方法及半导体器件的制造方法 | |

| KR101558192B1 (ko) | 반도체 기판의 제작 방법 및 반도체 장치의 제작 방법 | |

| TWI450337B (zh) | 半導體裝置的製造方法 | |

| US9847355B2 (en) | Silicon nitride film, and semiconductor device | |

| US8324086B2 (en) | Method for manufacturing a semiconductor substrate by laser irradiation | |

| JP5383143B2 (ja) | 半導体基板の作製方法および半導体装置の作製方法 | |

| JP5577027B2 (ja) | 半導体装置の作製方法並びに半導体装置及び電子機器 | |

| TWI437696B (zh) | 半導體裝置及其製造方法 | |

| US8530336B2 (en) | Method for manufacturing semiconductor substrate | |

| US8569170B2 (en) | Manufacturing method of semiconductor device comprising silicide layer with varied thickness | |

| US8946820B2 (en) | Method for manufacturing semiconductor substrate, substrate for forming semiconductor substrate, stacked substrate, semiconductor substrate, and electronic device | |

| JP4627971B2 (ja) | 半導体装置の作製方法 | |

| JP5414203B2 (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110322 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110322 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130724 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130806 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140304 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20140514 |